| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AD10200BZ | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

a

AD10200

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2001

Dual Channel, 12-Bit 105 MSPS IF Sampling

A/D Converter with Analog Input

Signal Conditioning

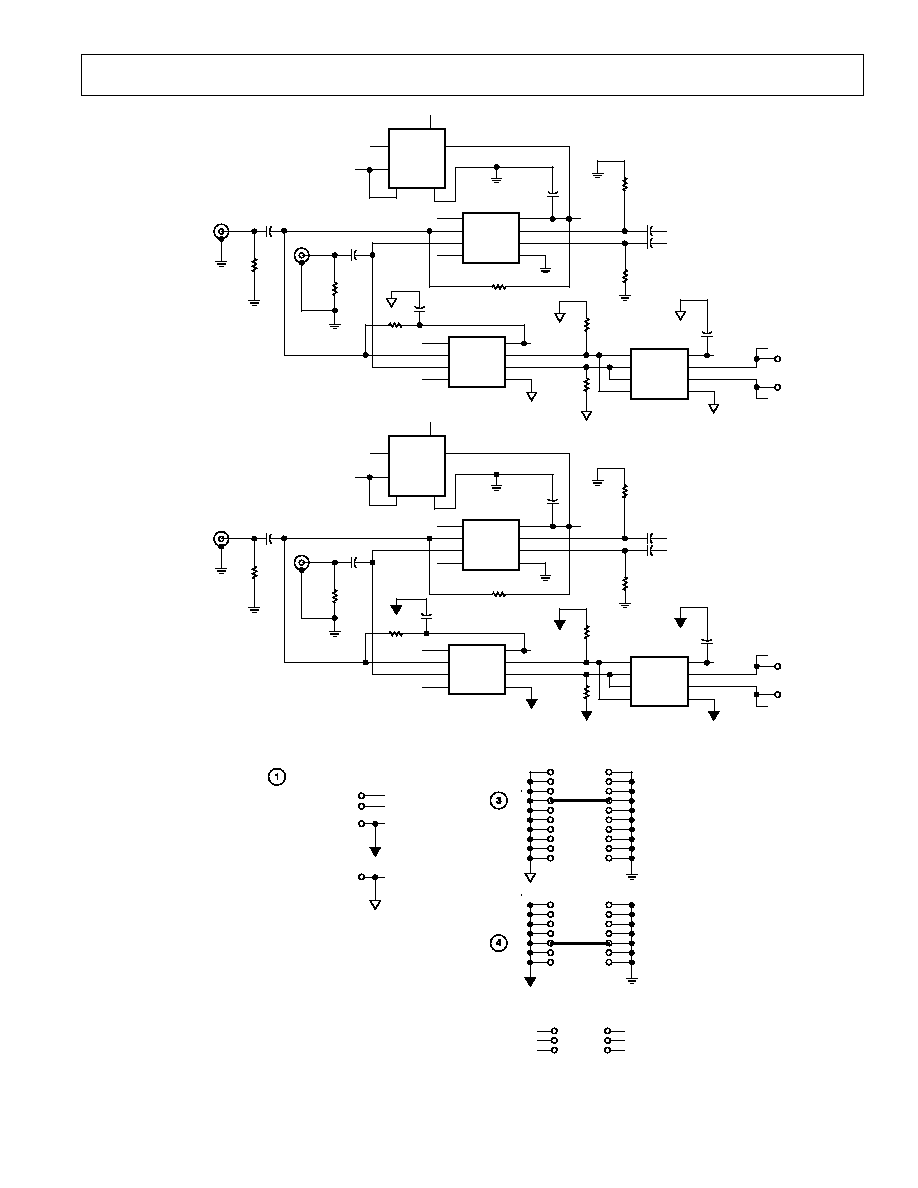

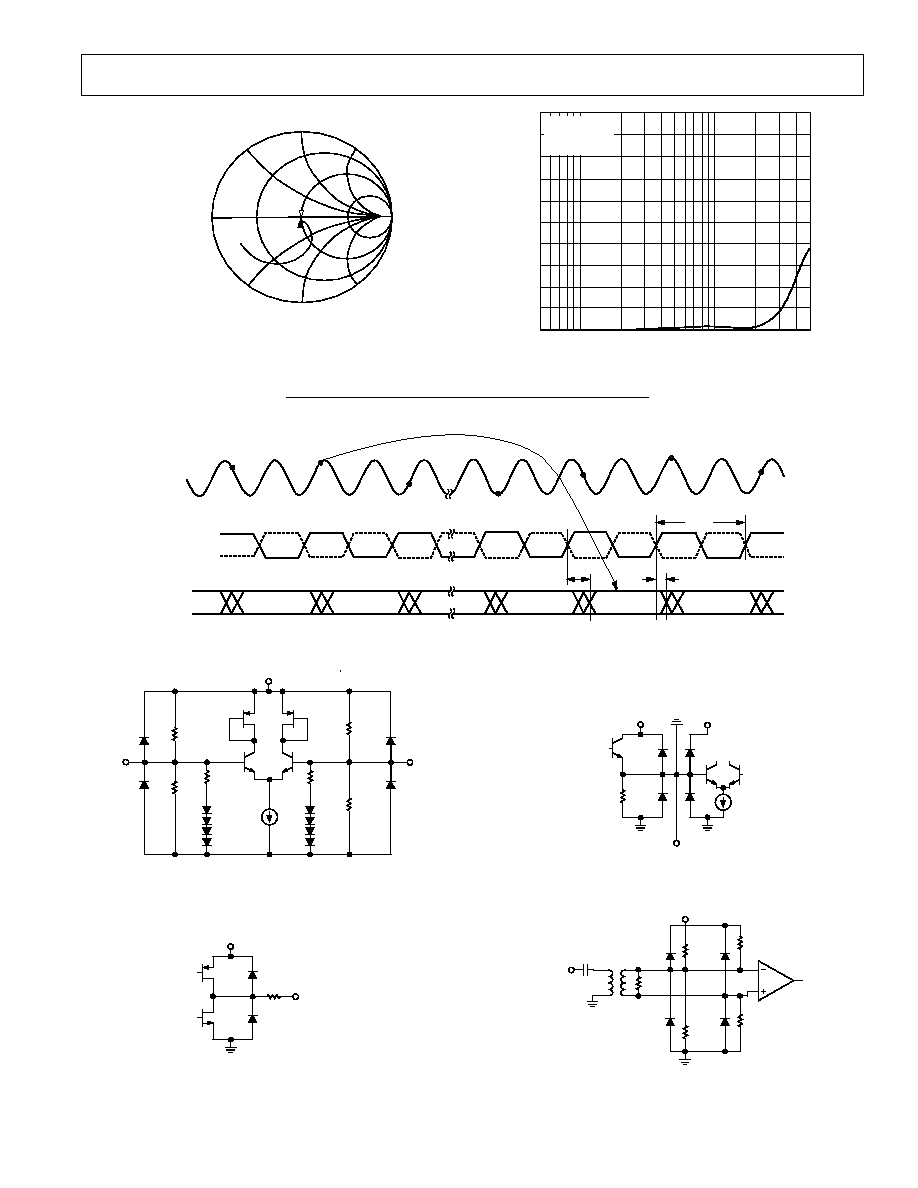

FUNCTIONAL BLOCK DIAGRAM

50

D00B

(LSB)

49

D01B

48

D02B

47

D03B

46

D04B

45

D05B

42

D06B

41

D07B

40

D08B

39

D09B

38

D10B

37

D11B

(MSB)

34

D00A

(LSB)

D01A

D02A

D03A

D04A

D05A

D06A

D07A

D08A

D09A

D10A

D11A

(MSB)

21

33

32

31

30

29

28

25

24

23

22

ADC

7

50

A

IN

A2

T1A

ADC

63

50

A

IN

B2

T1B

AD10200

OUTPUT RESISTORS

12

12

18

17

ENCODEA

ENCODEA

REF

3

REF_A_OUT

TIMING

53

54

ENCODEB

ENCODEB

REF

56

REF_B_OUT

OUTPUT RESISTORS

12

12

T/H

T/H

TIMING

FEATURES

Dual, 105 MSPS Minimum Sample Rate

Channel-Channel Isolation, >80 dB

AC-Coupled Signal Conditioning Included

Gain Flatness up to Nyquist: < 0.2 dB

Input VSWR 1.1:1 to Nyquist

80 dB Spurious-Free Dynamic Range

Two's Complement Output Format

3.3 V or 5 V CMOS-Compatible Output Levels

0.850 W per Channel

Industrial and Military Grade

APPLICATIONS

Radar IF Receivers

Phased Array Receivers

Communications Receivers

Secure Communications

GPS Antijamming Receivers

Multichannel, Multimode Receivers

PRODUCT DESCRIPTION

The AD10200 is a full channel ADC solution with on-module

signal conditioning for improved dynamic performance and

fully matched channel-to-channel performance. The module

includes two wide-dynamic range ADCs. Each ADC has a

transformer coupled front-end optimized for Direct-IF sampling.

The AD10200 has on-chip track-and-hold circuitry, and utilizes

an innovative architecture to achieve 12-bit, 105 MSPS perfor-

mance. The AD10200 uses innovative high-density circuit

design to achieve exceptional matching and performance while

still maintaining excellent isolation, and providing for significant

board area savings.

The AD10200 operates with 5.0 V supply for the analog-to-

digital conversion. Each channel is completely independent

allowing operation with independent encode and analog inputs.

The AD10200 is packaged in a 68-lead ceramic chip carrier

package. Manufacturing is done on Analog Devices, Inc. MIL-

38534 Qualified Manufacturers Line (QML) and components

are available up to Class-H (≠55

∞C to +125∞C).

PRODUCT HIGHLIGHTS

1. Guaranteed sample rate of 105 MSPS.

2. Input signal conditioning with full power bandwidth to

250 MHz.

3. Fully tested/characterized performance at 121 MHz A

IN

.

4. Optimized for IF sampling.

REV. A

≠2≠

AD10200≠SPECIFICATIONS

1

(V

DD

= 3.3 V, V

CC

= 5.0 V; ENCODE = 105 MSPS, unless otherwise noted)

Test

MIL

Parameter

Temp

Level

Subgroup

Min

Typ

Max

Unit

RESOLUTION

12

Bits

DC ACCURACY

Differential Nonlinearity

Full

IV

12

≠0.99

±0.5

+0.99

LSB

Integral Nonlinearity

Full

IV

12

≠3

±0.75

+3

LSB

No Missing Codes

Full

I

1, 2, 3

Guaranteed

Gain Error

2

Full

I

1, 2, 3

≠9

±1

+9

% FS

Output Offset

Full

I

1, 2, 3

≠12

+12

LSB

ANALOG INPUT

Input Voltage Range

25

∞C

V

2.048

V p-p

Input Impedance

25

∞C

V

50

Input VSWR

3

Full

IV

12

1.1:1

1.25:1

Ratio

Analog Input Bandwidth, High

Full

IV

12

200

250

MHz

Analog Input Bandwidth, Low

Full

IV

12

1

MHz

ANALOG REFERENCE

Output Voltage

Full

I

1, 2, 3

2.4

2.5

2.6

V

Load Current

25

∞C

V

5

mA

Tempco

Full

V

50

ppm/

∞C

SWITCHING PERFORMANCE

Maximum Conversion Rate

Full

I

4, 5, 6

105

MSPS

Minimum Conversion Rate

Full

IV

12

10

MSPS

Duty Cycle

Full

IV

12

45

50

55

%

Aperture Delay (t

A

)

25

∞C

V

1.0

ns

Aperture Uncertainty (Jitter)

25

∞C

V

0.25

ps rms

Output Valid Time (t

V

)

4

Full

IV

12

3.0

5.3

ns

Output Propagation Delay (

PD

)

4

Full

IV

12

4.5

5.5

8.0

ns

Output Rise Time (t

R

)

25

∞C

V

12

3.5

ns

Output Fall Time (t

F

)

25

∞C

V

12

3.3

ns

DIGITAL INPUTS

Encode Input Common Mode

Full

IV

12

1.2

1.6

2.0

V

Differential Input (Enc,

Enc)

Full

IV

12

0.4

5.0

V

Logic "1" Voltage

Full

IV

12

2.0

V

Logic "0" Voltage

Full

IV

12

0.8

V

Input Resistance

Full

IV

12

3

5

8

k

Input Capacitance

25

∞C

V

4.5

pF

DIGITAL OUTPUTS

Logic "1" Voltage

4

Full

VI

1, 2, 3

3.1

3.3

V

Logic "0" Voltage

4

Full

VI

1, 2, 3

0

0.2

V

Output Coding

Two's Complement

POWER SUPPLY

5

Power Dissipation

6

Full

I

1, 2, 3

1800

2200

mW

Power Supply Rejection Ratio

Full

IV

12

±0.5

±5

mV/V

I (DV

DD

) Current

Full

I

1, 2, 3

25

40

mA

I (AV

CC

) Current

Full

I

1, 2, 3

340

410

mA

DYNAMIC PERFORMANCE

Signal-to-Noise Ratio (SNR)

7

(Without Harmonics)

f

IN

= 10 MHz

25

∞C

V

67

dBFS

Full

V

66

dBFS

f

IN

= 41 MHz

25

∞C

I

4

64

66.5

dBFS

Full

II

5, 6

62

65

dBFS

f

IN

= 71 MHz

25

∞C

I

4

62.5

66.4

dBFS

Full

II

5, 6

61.5

64

dBFS

f

IN

= 121 MHz

25

∞C

I

4

61

65

dBFS

Full

II

5, 6

61

64

dBFS

REV. A

≠3≠

AD10200

Test

MIL

Parameter

Temp

Level

Subgroup

Min

Typ

Max

Unit

DYNAMIC PERFORMANCE

(Continued)

Signal-to-Noise Ratio (SINAD)

8

(With Harmonics)

f

IN

= 10 MHz

25

∞C

V

66

dBFS

Full

V

63

dBFS

f

IN

= 41 MHz

25

∞C

I

4

63

65.5

dBFS

Full

II

5, 6

60.5

63

dBFS

f

IN

= 71 MHz

25

∞C

I

4

61

63.5

dBFS

Full

II

5, 6

57

60

dBFS

f

IN

= 121 MHz

25

∞C

I

4

56

58.5

dBFS

Full

II

5, 6

53

55

dBFS

Spurious Free Dynamic Range

9

f

IN

= 10 MHz

25

∞C

V

81

dBFS

Full

V

70

dBFS

f

IN

= 41 MHz

25

∞C

I

4

73

81

dBFS

Full

II

5, 6

67.5

dBFS

f

IN

= 71 MHz

25

∞C

I

4

67

74

dBFS

Full

II

5, 6

60

dBFS

f

IN

= 121 MHz

25

∞C

I

4

61

65

dBFS

Full

II

5, 6

55.5

58

dBFS

Two-Tone Intermodulation

Distortion

10

(IMD)

f

IN

= 10 MHz; f

IN

= 12 MHz

25

∞C

V

86

dBc

Full

V

81

dBc

f

IN

= 71 MHz; f

IN

= 72 MHz

25

∞C

V

70

dBc

Full

V

65

dBc

f

IN

= 121 MHz; f

IN

= 122 MHz

25

∞C

I

4

55.5

62

dBc

Full

II

5, 6

53

57

dBc

Channel-to-Channel Isolation

11

f

IN

= 121 MHz

Full

IV

12

80

85

dB

NOTES

1

All ac specifications tested by driving ENCODE and

ENCODE differentially.

2

Gain Error measured at 2.5 MHz.

3

Input VSWR guaranteed 10 MHz to 200 MHz.

4

t

V

and t

PD

are measured from the transition points of the ENCODE input to the 50%/50% levels of the digital outputs swing. The digital output load during test is

not to exceed an ac load of 10 pF or a dc current of

± 40 mA.

5

Supply voltages should remain stable within

± 5% for normal operation.

6

Power dissipation measured with encode at rated speed and 0 dBm analog input.

7

Analog Input signal power at ≠1 dBFS; signal-to-noise ratio (SNR) is the ratio of signal level to total noise (first 5 harmonic removed). Encode = 105 MSPS. SNR

is reported in dBFS, related back to converter full scale.

8

Analog Input signal power at ≠1 dBFS; signal-to-noise and distortion (SINAD) is the ratio of signal level to total noise + harmonics. Encode = 105 MSPS. SINAD

is reported in dBFS, related back to converter full scale.

9

Analog Input signal equal ≠1 dBFS; SFDR is ratio of converter full scale to worst spur.

10

Both input tones at ≠7 dBFS; two tone intermodulation distortion (IMD) rejection is the ratio of either tone to the worst third order intermod product. f1 = x MHz

± 100 kHz, f2 = x MHz ± 100 kHz.

11

Channel-to-Channel isolation tested with A Channel/50

terminated (A

IN

A2) grounded and a full-scale signal applied to B Channel (A

IN

B2).

Specifications subject to change without notice.

REV. A

AD10200

≠4≠

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD10200 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

1, 2

V

DD

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 V

V

CC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 V

Analog Inputs . . . . . . . . . . . . . . . . . . . . . . . . 5 V

p-p(18 dBm)

Digital Inputs . . . . . . . . . . . . . . . . . . . ≠0.5 V to V

DD

+ 0.5 V

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . 20 mA

Operating Temperature . . . . . . . . . . . . . . . . ≠55

∞C to +125∞C

Storage Temperature . . . . . . . . . . . . . . . . . . ≠65

∞C to +150∞C

Maximum Junction Temperature . . . . . . . . . . . . . . . . . 175

∞C

Maximum Case Temperature . . . . . . . . . . . . . . . . . . . . 150

∞C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions outside of those indicated in the operation

sections of this specification is not implied. Exposure to absolute maximum ratings

for extended periods may affect device reliability.

2

Typical thermal impedances for "Z" package:

JC

= 2.22

∞C/W;

JA

= 24.3

∞C/W.

EXPLANATION OF TEST LEVELS

Test Level

I.

100% production tested.

II.

100% production tested at 25

∞C and sample tested at

specific temperatures.

III. Sample tested only.

IV. Parameter is guaranteed by design and characterization

testing.

V.

Parameter is a typical value only.

VI. 100% production tested at 25

∞C; guaranteed by design and

characterization testing for industrial temperature range.

Table I. Output Coding (VREF = 2.5 V) (Two's Complement)

Code

A

IN

(V)

Digital Output

+2047

+1.024

0111 1111 1111

∑

∑

∑

∑

∑

∑

0

0

0000 0000 0000

≠1

≠0.00049

1111 1111 1111

∑

∑

∑

∑

∑

∑

≠2048

≠1.024

1000 0000 0000

ORDERING GUIDE

Model

Temperature Range

Package Description

Package Option

AD10200BZ

≠40

∞C to +85∞C (Case)

68-Lead Ceramic Leaded Chip Carrier

Z-68B

5962-9961002HXA

≠40

∞C to +85∞C (Case)

68-Lead Ceramic Leaded Chip Carrier

Z-68B

5962-9961001HXA

≠55

∞C to +125∞C (Case)

68-Lead Ceramic Leaded Chip Carrier

Z-68B

AD10200/PCB

Evaluation Board with AD10200BZ

REV. A

AD10200

≠5≠

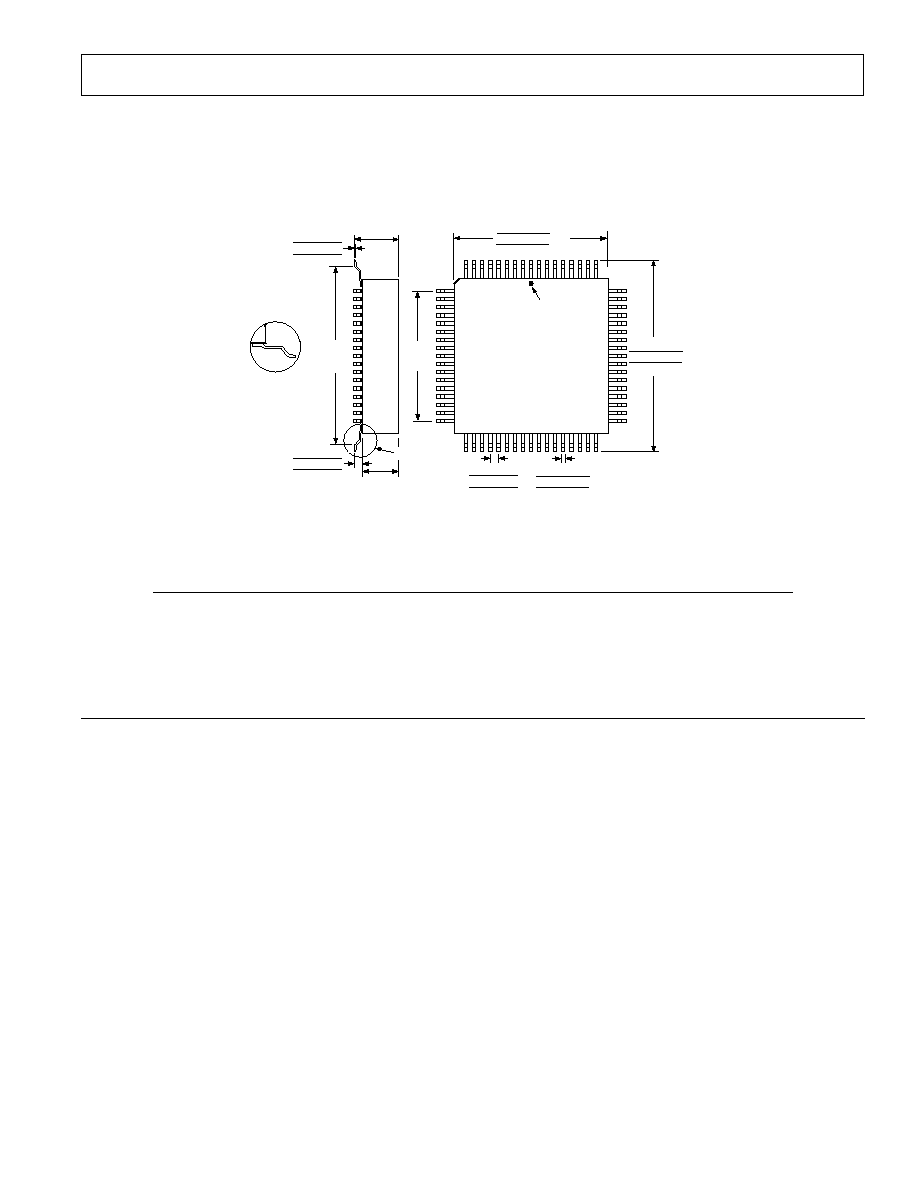

PIN CONFIGURATION

10

11

12

13

14

15

16

17

18

19

20

22

23

24

25

26

21

27

43

28 29 30 31 32 33 34 35 36 37 38 39 40 41 42

9

61

8

7

6

5

68 67 66 65 64 63 62

4

3

2

1

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

PIN 1

IDENTIFIER

TOP VIEW

(Not to Scale)

AGNDB

AGNDB

DNC

DNC

REF_B_OUT

AGNDB

ENCODEB

AGNDA

AGNDA

DNC

AGNDA

AV

CC

DNC

AGNDA

NC = NO CONNECT

ENCODEA

ENCODEA

AGNDA

DV

CC

ENCODEB

AGNDB

DV

CC

D0B (LSB)

AGNDA

AGNDA

NC

AGNDA

DNC

VREF_A_OUT

DNC

DNC

AV

CC

AGNDB

AGNDB

AD10200

DNC

A

IN

A2

AGNDB

SHIELD

NC

A

IN

B2

(MSB) D11A

D10A

D9A

D8A

D7A

DGNDA

D1B

D2B

D3B

D4B

D5B

DGNDB

DGNDA

D6A

D5A

D4A

D3A

D2A

D1A

(LSB) D0A

AGNDA

AGNDB

(MSB) D11B

D10B

D9B

D8B

D7B

D6B

DGNDB

PIN FUNCTION DESCRIPTIONS

Pin No.

Mnemonic

Function

1

SHIELD

Internal Ground Shield between Channels

2, 5, 9≠11, 13, 16, 19, 35

AGNDA

A Channel Analog Ground. A and B grounds should be connected as close to

the device as possible.

3

VREF_A_OUT

A Channel Internal Voltage Reference

6, 62

NC

No Connection

7

A

IN

A2

Analog Input for A Side ADC

4, 8, 12, 15, 57, 58, 64, 67

DNC

Do Not Connect

14, 66

AV

CC

Analog Positive Supply Voltage (Nominally 5.0 V)

17

ENCODEA

Complement of Encode

18

ENCODEA

Data conversion initiated on the rising edge of ENCODE input.

20

DV

CC

Digital Positive Supply Voltage (Nominally 3.3 V)

21≠25, 28≠34

D11A≠D7A,

Digital Outputs for ADC A. D0 (LSB)

D6A≠D0A

26, 27

DGNDA

A Channel Digital Ground

36, 52, 55, 59≠61, 65, 68

AGNDB

B Channel Analog Ground. A and B grounds should be connected as close to

the device as possible.

37≠42, 45≠50

D11B≠D6B,

Digital Outputs for ADC B. D0 (LSB)

D5B≠D0B

43, 44

DGNDB

B Channel Digital Ground

51

DV

CC

Digital Positive Supply Voltage (Nominally 3.3 V)

53

ENCODEB

Data conversion initiated on rising edge of ENCODE input.

54

ENCODEB

Complement of Encode

56

VREF_B_OUT

B Channel Internal Voltage Reference

63

A

IN

B2

Analog Input for B Side ADC

REV. A

AD10200

≠6≠

DEFINITION OF SPECIFICATIONS

Analog Bandwidth

The analog input frequency at which the spectral power of the

fundamental frequency (as determined by the FFT analysis) is

reduced by 3 dB.

Aperture Delay

The delay between the 50% point on the rising edge of the

ENCODE command and the instant at which the analog input

is sampled.

Aperture Uncertainty (Jitter)

The sample-to-sample variation in aperture delay.

Differential Nonlinearity

The deviation of any code from an ideal 1 LSB step.

Encode Pulsewidth/Duty Cycle

Pulsewidth high is the minimum amount of time that the

ENCODE pulse should be left in Logic "1" state to achieve

rated performance; pulsewidth low is the minimum time

ENCODE pulse should be left in low state. At a given clock

rate, these specs define an acceptable Encode duty cycle.

Harmonic Distortion

The ratio of the rms signal amplitude to the rms value of the

worst harmonic component.

Integral Nonlinearity

The deviation of the transfer function from a reference line

measured in fractions of 1 LSB using a "best straight line"

determined by a least square curve fit.

Minimum Conversion Rate

The encode rate at which the SNR of the lowest analog signal

frequency drops by no more that 3 dB below the guaranteed limit.

Maximum Conversion Rate

The encode rate at which parametric testing is performed.

Output Propagation Delay

The delay between the 50% point of the rising edge of ENCODE

command and the time when all output data bits are within

valid logic levels.

Overvoltage Recovery Time

The amount of time required for the converter to recover to

0.02% accuracy after an analog input signal of the specified

percentage of full scale is reduced to midscale.

Power Supply Rejection Ratio

The ratio of a change in output offset voltage to a change in

power supply voltage.

Signal-to-Noise-and-Distortion (SINAD)

The ratio of the rms signal amplitude (set a 1 dB below full scale)

to the rms value of the sum of all other spectral components,

excluding the first five harmonics and dc. [May be reported in

dBc (i.e., degrades as signal levels is lowered) or in dBFS (always

related back to converter full scale)].

Signal-to-Noise Ratio (without Harmonics)

The ratio of the rms signal amplitude (set a I dB below full

scale) to the rms value of the sum of all other spectral compo-

nents, excluding the first five harmonics and dc. [May be

reported in dBc (i.e., degrades as signal levels is lowered) or in

dBFS (always related back to converter full scale).]

Spurious-Free Dynamic Range

The ratio of the rms signal amplitude to the rms value of the

peak spurious spectral component. The peak spurious compo-

nent may or may not be a harmonic. [May be reported in dBc

(i.e., degrades as signal levels is lowered) or in dBFS (always

related back to converter full scale).]

Transient Response

The time required for the converter to achieve 0.02% accu-

racy when a one-half full-scale step function is applied to the

analog input.

Two-Tone Intermodulation Distortion Rejection

The ratio of the rms value of either input tone to the rms value of

the worst third order intermodulation product; reported in dBc.

Voltage Standing-Wave Ratio (VSWR)

The ratio of the amplitude of the elective field at a voltage maxi-

mum to that at an adjacent voltage minimum.

REV. A

≠7≠

AD10200

Typical Performance Characteristics≠

FREQUENCY ≠ MHz

0

130

dB

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 10MHz (≠1dBFS)

SNR = 66.84dBFS

SFDR = 82.28dBc

TPC 1. Single Tone @ 10 MHz

FREQUENCY ≠ MHz

0

130

dB

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 71MHz (≠1dBFS)

SNR = 66.04dBFS

SFDR = 79.71dBc

TPC 2. Single Tone @ 71 MHz

FREQUENCY ≠ MHz

0

130

dB

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 121MHz (≠6dBFS)

SNR = 66.9dBFS

SFDR = 65.57dBc

TPC 3. Single Tone @ 121 MHz

FREQUENCY ≠ MHz

0

130

dB

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 41MHz (≠1dBFS)

SNR = 66.06dBFS

SFDR = 80.59dBc

TPC 4. Single Tone @ 41 MHz

FREQUENCY ≠ MHz

0

130

dB

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 121MHz (≠1dBFS)

SNR = 64.92dBFS

SFDR = 64.73dBc

TPC 5. Single Tone @ 121 MHz

FREQUENCY ≠ MHz

0

130

dB

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 201MHz (≠10dBFS)

SNR = 66.84dBFS

SFDR = 64.57dBc

TPC 6. Single Tone @ 201 MHz

REV. A

AD10200

≠8≠

FREQUENCY ≠ MHz

0

130

dBc

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 37MHz & 38MHz (≠10dBFS)

SFDR = 79.84dBc

TPC 7. Two-Tone @ 37 MHz/38 MHz

FREQUENCY ≠ MHz

0

130

dBc

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 120MHz & 121MHz (≠7dBFS)

SFDR = 63.8dBc

TPC 8. Two-Tone @ 120 MHz/121 MHz

3

3

LSB

0

2

2

0

1

1

512

1024

1536

2048

2560

3072

3584

4096

ENCODE = 105 MSPS

INL MAX = 0.874 Codes

INL MIN = 0.895 Codes

TPC 9. Integral Nonlinearity

FREQUENCY ≠ MHz

0

130

dBc

20

80

100

110

120

40

60

0

10

30

90

50

70

5

10

15

20

25

30

35

40

45

50

ENCODE = 105 MSPS

A

IN

= 71MHz & 72MHz (≠7dBFS)

SFDR = 74.8dBc

TPC 10. Two-Tone @ 71 MHz/72 MHz

3.0

1.0

LSB

1.5

0.5

0.0

0.5

2.5

0

1.0

2.0

512

1024

1536

2048

2560

3072

3584

4096

ENCODE = 105 MSPS

DNL MAX = 0.486 Codes

DNL MIN = 0.431 Codes

TPC 11. Differential Nonlinearity

0

10

dBFS

6

9

2

3.0

8

4

32.7

62.4

92.1 121.8 151.5 181.2 210.9 240.6

MHz

270.3 300.0

1

7

3

5

ENCODE = 105 MSPS

3dB = 261MHz

TPC 12. Gain Flatness

REV. A

AD10200

≠9≠

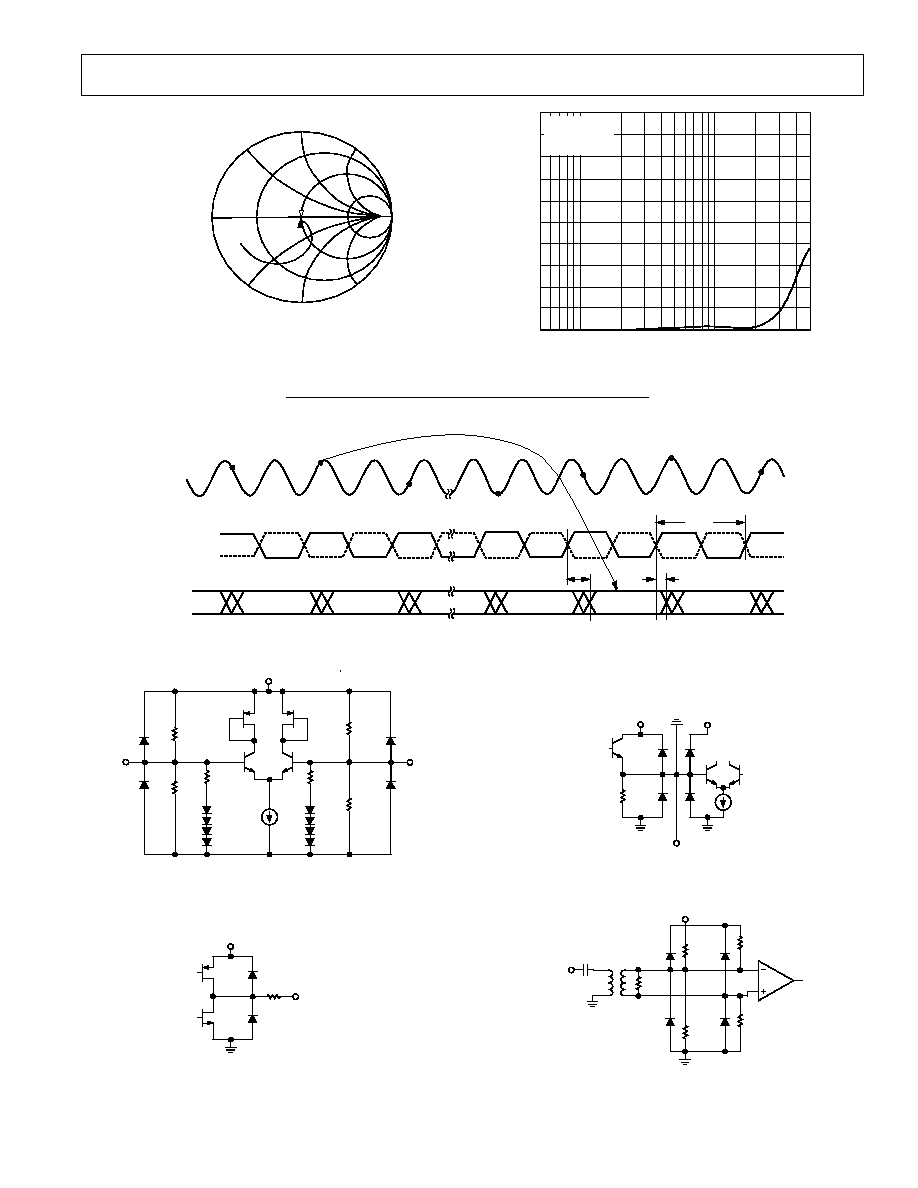

10MHz = 50.22 + j.173

50MHz = 48.79 ≠ j4.2

100MHz = 46.95 ≠ j5.9

150MHz = 48.55 ≠ j4.66

TPC 13. Input Impedance S11

1

3.0 32.7

62.4

92.1 121.8 151.5 181.2 210.9 240.6

MHz

270.3 300.0

10MHz = 1.0149

50MHz = 1.085

100MHz = 1.130

150MHz = 1.092

2

3

4

5

6

7

8

9

10

11

TPC 14. Voltage Standing Wave Ratio (VSWR)

t

PD

AIN

ENCODE

ENCODE

D11 D0

SAMPLE N≠1

SAMPLE N

SAMPLE N+10

SAMPLE N+11

SAMPLE N+9

SAMPLE N+1

1/f

S

DATA N 11

DATA N 10

N 9

DATA N 1

DATA N

DATA N + 1

t

V

N 2

Figure 1. Timing Diagram

V

CC

17k

8k

100

100

17k

8k

ENCODE

ENCODE

Figure 2. Equivalent Encode Input Circuit

V

CC

100

DIGITAL

OUTPUT

Figure 3. Equivalent Digital Output Circuit

V

CC

Q1

NPN

V

REF

OUTPUT

V

CC

Figure 4. Equivalent Voltage Reference Output Circuit

V

CC

A

IN

7k

50

7k

5k

5k

Figure 5. Equivalent Analog Input Circuit

REV. A

AD10200

≠10≠

APPLICATION NOTES

Theory of Operation

The AD10200 is a high-dynamic range dual 12-bit, 105 MHz

subrange pipeline converter that uses switched capacitor

architecture. The analog input section uses A

IN

A2/A

IN

B2 at

2.048 V p-p with an input impedance of 50

. The analog input

includes an ac-coupled wide-band 1:1 transformer, which provides

high-dynamic range and SNR while maintaining VSWR and

gain flatness. The ADC includes a high-bandwidth linear track/

hold that gives excellent spurious performance up to and beyond

the Nyquist rate. The high-bandwidth track/hold has a low jitter

of 0.25 ps rms, leading to excellent SNR and SFDR performance.

AC-coupled differential PECL/ECL encode inputs are recom-

mended for optimum performance.

USING THE AD10200

ENCODE Input

Any high speed A/D converter is extremely sensitive to the quality

of the sampling clock provided by the user. A track/hold circuit

is essentially a mixer, and any noise, distortion, or timing jitter

on the clock will be combined with the desired signal at the A/D

output. For that reason, considerable care has been taken in the

design of the ENCODE input of the AD10200, and the user is

advised to give commensurate thought to the clock source. The

ENCODE input are fully TTL/CMOS compatible. For opti-

mum performance, the AD10200 must be clocked differentially.

Note that the ENCODE inputs cannot be driven directly from

PECL level signals (V

IHD

is 3.5 V max). PECL level signals can

easily be accommodated by ac coupling as shown in Figure 6.

Good performance is obtained using an MC10EL16 in the

circuit to drive the encode inputs.

GND

510

510

0.1 F

0.1 F

PECL

GATE

ENCODE

ENCODE

AD10200

Figure 6. AC Coupling to ENCODE Inputs

ENCODE Voltage Level Definition

The voltage level definitions for driving ENCODE and

ENCODE

in differential mode are shown in Figure 7.

ENCODE Inputs

Differential Signal Amplitude (V

ID

)

500 mV min,

750 mV nom

High Differential Input Voltage (V

IHD

)

5.0 V max

Low Differential Input Voltage (V

ILD

)

0 V min

Common-Mode Input (V

ICN

)

1.25 V min, 1.6 V nom

ENCODE

0.1 F

V

IHS

V

ILS

ENCODE

ENCODE

V

ID

V

IHD

V

ILD

V

ICM

Figure 7. Differential Input Levels

Often, the cleanest clock source is a crystal oscillator producing

a pure sine wave. In this configuration, or with any roughly

symmetrical clock input, the input can be ac-coupled and biased

to a reference voltage that also provides the ENCODE. This

ensures that the reference voltage is centered on the encode signal.

Digital Outputs

The digital outputs are TTL/CMOS-compatible and a separate

output power supply pin supports interfacing with 3.3 V logic.

Analog Input

The analog input is a single ended ac-coupled high performance

1:1 transformer with an input impedance of 50

to 105 MHz.

The nominal full scale input is 2.048 V p-p.

Special care was taken in the design of the analog input section

of the AD10200 to prevent damage and corruption of data when

the input is overdriven.

Voltage Reference

A stable and accurate 2.5 V voltage reference is designed into

the AD10200 (VREFOUT). An external voltage reference is

not required.

Timing

The AD10200 provides latched data outputs, with 10 pipeline

delays. Data outputs are available one propagation delay (t

PD

)

after the rising edge of the encode command (see Figure 1). The

length of the output data lines and loads placed on them should

be minimized to reduce transients within the AD10200; these

transients can detract from the converter's dynamic performance.

The minimum guaranteed conversion rate of the AD10200 is

10 MSPS. At internal clock rates below 10 MSPS, dynamic

performance may degrade. Therefore, input clock rates below

10 MHz should be avoided.

GROUNDING AND DECOUPLING

Analog and Digital Grounding

Proper grounding is essential in any high speed, high resolution

system. Multilayer printed circuit boards (PCBs) are recom-

mended to provide optimal grounding and power schemes. The

use of ground and power planes offers distinct advantages:

1. The minimization of the loop area encompassed by a signal

and its return path.

2. The minimization of the impedance associated with ground

and power paths.

3. The inherent distributed capacitor formed by the power

plane, PCB insulation and ground plane.

These characteristics result in both a reduction of electromagnetic

interference (EMI) and an overall improvement in performance.

It is important to design a layout that prevents noise from cou-

pling to the input signal. Digital signals should not be run in

parallel with input signal traces and should be routed away from

the input circuitry. The PCB should have a ground plane covering

all unused portions of the component side of the board to pro-

vide a low impedance path and manage the power and ground

currents. The ground plane should be removed from the area

near the input pins to reduce stray capacitance.

REV. A

AD10200

≠11≠

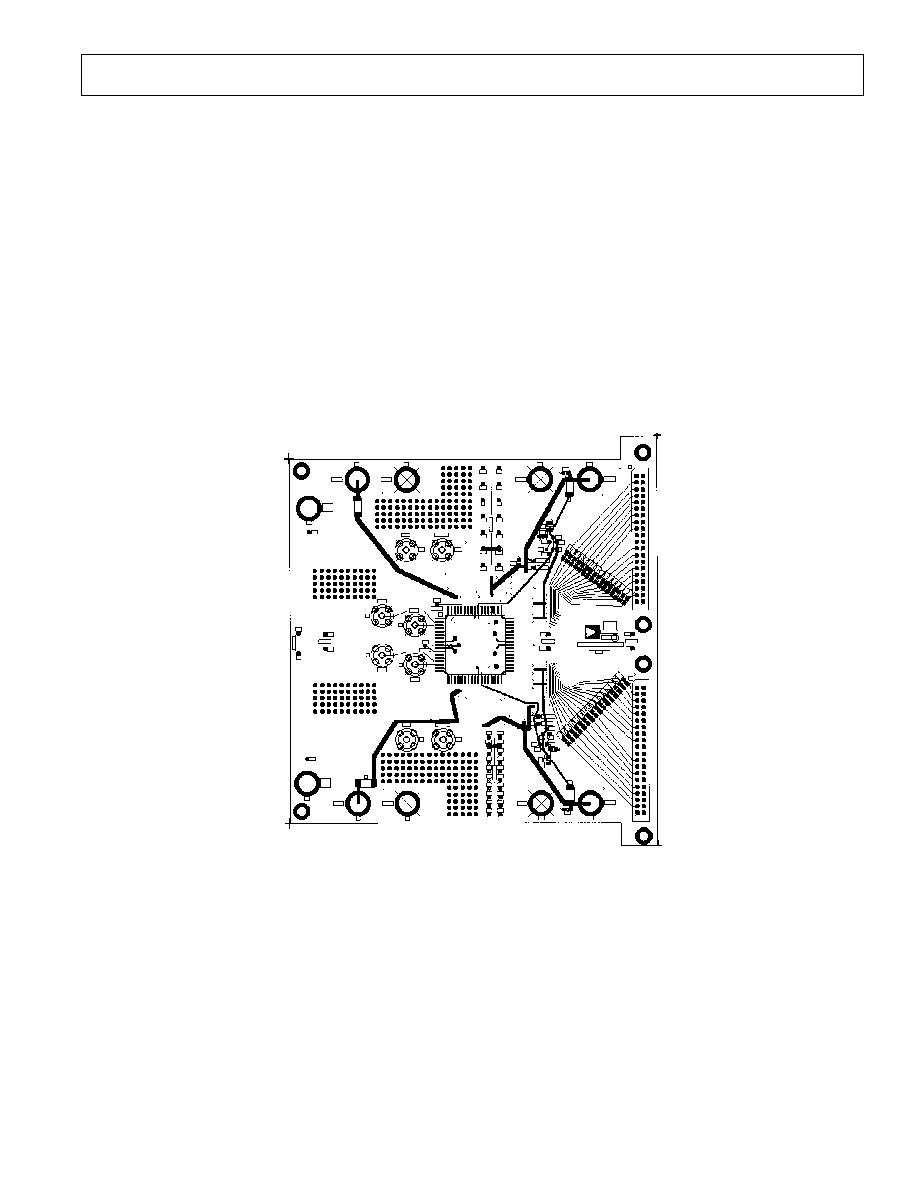

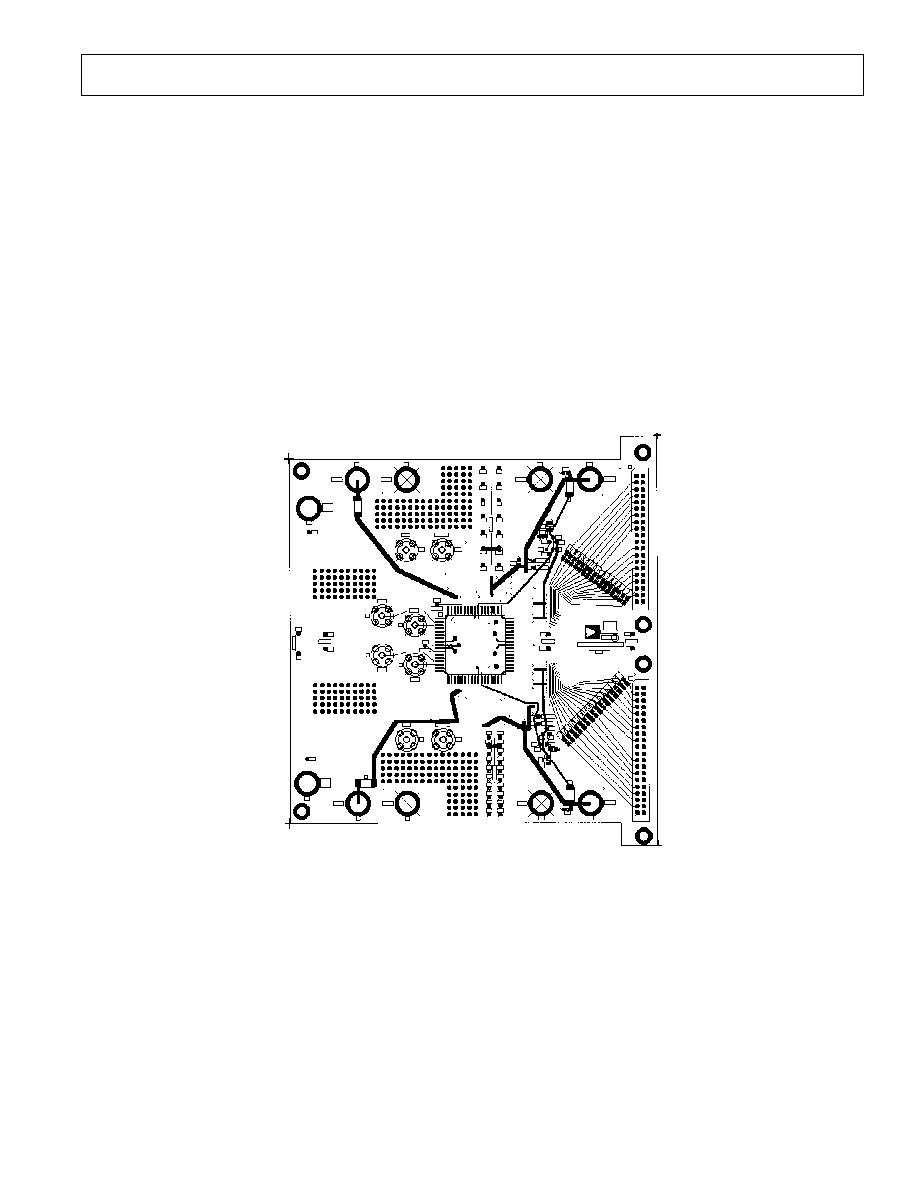

LAYOUT INFORMATION

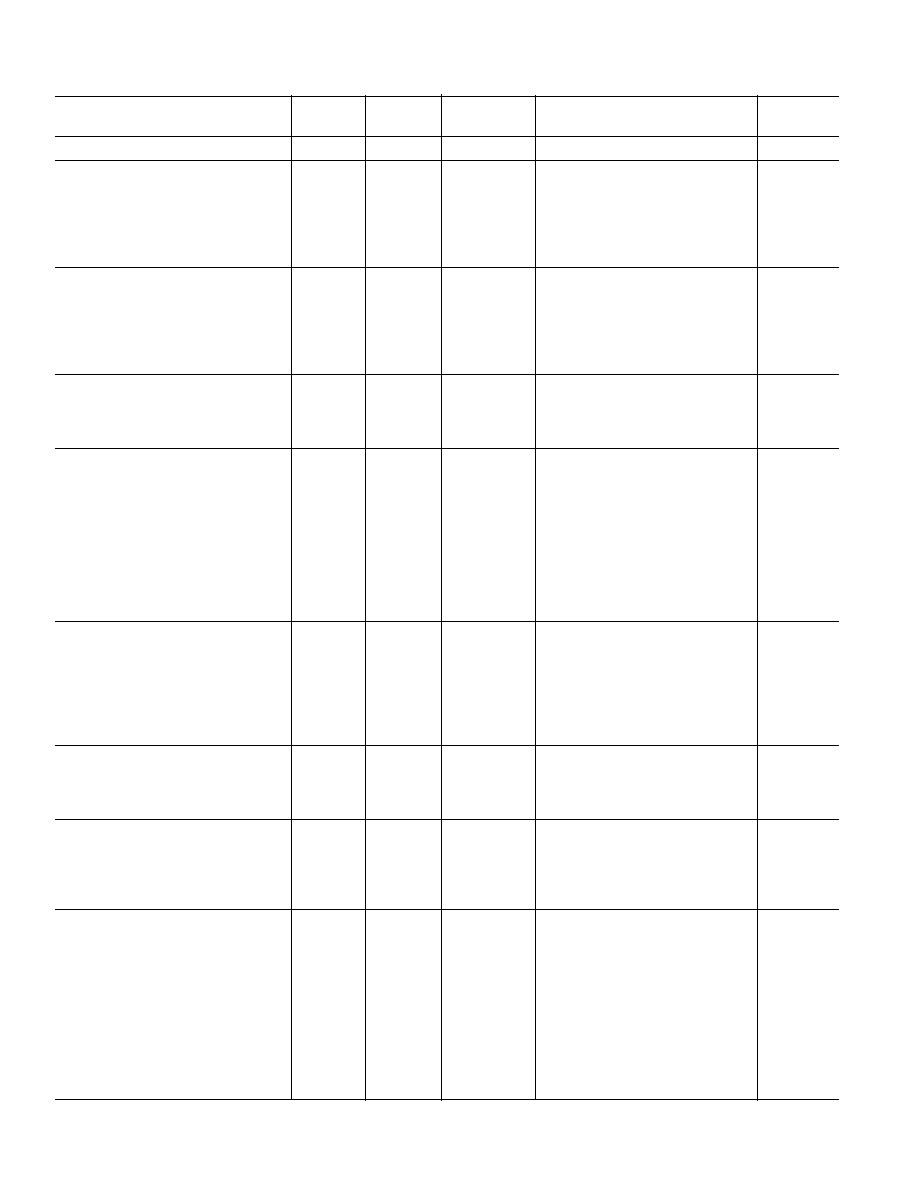

The schematic of the evaluation board (Figure 8) represents

a typical implementation of the AD10200. The pinout of the

AD10200 is very straightforward and facilitates ease of use and

the implementation of high frequency/high resolution design

practices. It is recommended that high quality ceramic chip

capacitors be used to decouple each supply pin to ground directly

at the device. All capacitors can be standard high quality ceramic

chip capacitors.

Care should be taken when placing the digital output runs.

Because the digital outputs have such a high-slew rate, the

capacitive loading on the digital outputs should be minimized.

Circuit traces for the digital outputs should be kept short and

connect directly to the receiving gate. Internal circuitry buffers

the outputs of the ADC through a resistor network to eliminate

the need to externally isolate the device from the receiving gate.

Figure 8. Evaluation Board Mechanical Layout

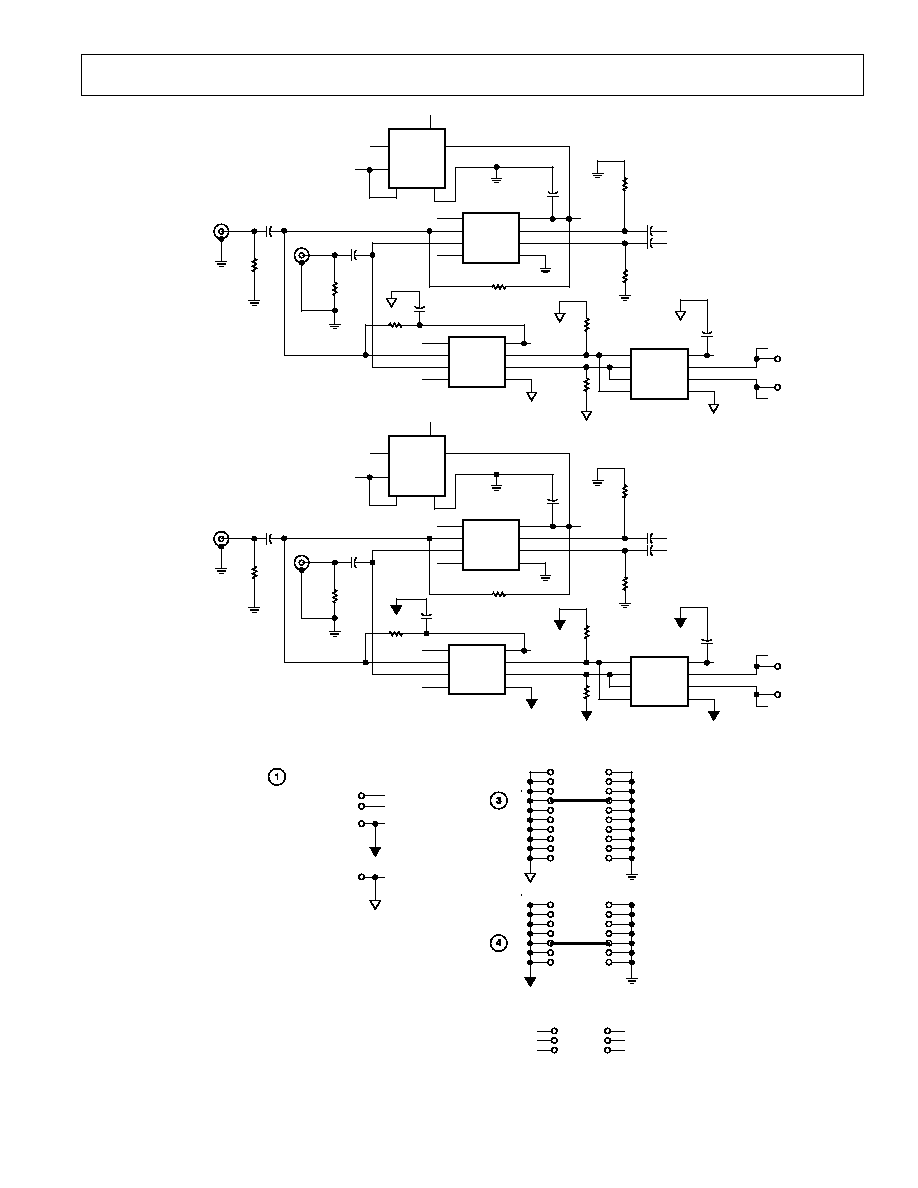

EVALUATION BOARD

The AD10200 evaluation board (Figure 9) is designed to

provide optimal performance for evaluation of the AD10200

analog-to-digital converter. The board encompasses everything

needed to ensure the highest level of performance for evaluating

the AD10200. The board requires an analog input signal, encode

clock and power supply inputs. The clock is buffered on-board

to provide clocks for the latches. The digital outputs and out

clocks are available at the standard 40-pin connectors J1 and J2.

Power to the analog supply pins is connected via banana jacks.

The analog supply powers the associated components and the

analog section of the AD10200. The digital outputs of the

AD10200 are powered via banana jacks with 3.3 V. Contact the

factory if additional layout or applications assistance is required.

REV. A

AD10200

≠12≠

Figure 9a. Evaluation Board

AGNDB

AGNDB

VFU_B

SDOUT_B

REF_B

AGNDB

ENCBB

ENCB

AGNDB

3.3VDB

D0B (LSB)

D1B

D2B

D3B

D4B

D5B

DGNDB

AGNDA

AGNDA

SDOUT_A

AGNDA

5VAA

SCLK_A

AGNDA

ENCAB

ENCA

AGNDA

3.3VDA

D11A (MSBA)

D10A

D9A

D8A

D7A

DGNDA

AGNDA

AGNDA

A

IN

A1

AGNDA

SDIN_A

REF_A

SCLK_B

SDIN_B

5VAB

AGNDB

AGNDB

VFU_A

A

IN

A2

AGNDB

SHIELD

A

IN

B1

A

IN

B2

U1

AD10200

DGNDA

D6A

D5A

D4A

D3A

D2A

D1A

D0A (LSBA)

AGNDA

AGNDB

D11B (MSBB)

D10B

D9B

D8B

D7B

D6B

DGNDB

9

5

7

6

5

4

3

2

1

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

43

C37

DNS

AGNDA

AGNDA

J4

SMA

AGNDA

J3

SMA

DNS

AGNDA

(NC)

0.1

F

C33

AGNDA

E49

AGNDA

J7

SMA

AGNDB

J6

SMA

DNS

AGNDB

(NC)

5VAB_

AGNDB

(NC)

AGNDA

LID

AGNDA

AGNDB

C36

DNS

AGNDB

AGNDB

NC

0.1

F

C35

AGNDB

E50

AGNDB

ENCBB

ENCB

AGNDB

D0B

D1B

D2B

D3B

D4B

D5B

DGNDB

C18

0.1

F

U17

DGNDB

DUT_3.3VDB

D0A

DUT_3.3VDA

C10

0.1

F

U1

DGNDA

5VAA_

C34

0.1

F

AGNDA

AGNDA

AGNDA

NC

NC

AGNDA

ENCAB

ENCA

AGNDA

D11A

D10A

D9A

D8A

D7A

DGNDA

AGNDA

AGNDA

DGNDA

D6A

D5A

D4A

D3A

D2A

D1A

D10B

D9B

D8B

D7B

D6B

DGNDB

AGNDA

AGNDB

D11B

U1

C20

0.1

F

AGNDA

5AA_

U1

C21

0.1

F

AGNDB

5AB_

L3

47

20%

@100MHz

C3

10

F

AGNDA

5AA

E6

DUT_3.3VDA

L1

47

20%

@100MHz

U1

C12

0.1

F

DGNDA

C29

10

F

3.3VDA

E25

L4

47

20%

@100MHz

C4

10

F

AGNDB

5AB

E5

DUT_3.3VDB

L2

47

20%

@100MHz

U8

C16

0.1

F

DGNDB

C30

10

F

3.3VDB

E26

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

DGNDA

H40DM

J1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

(MSB) B11A

B10A

B9A

B8A

B7A

B6A

B5A

B4A

B3A

B2A

B1A

(LSB) B0A

F3A

F2A

F1A

F0A

DGNDA

R71

50

BUFLATA

C15

10

F

DGNDA

3.3VDA

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

DGNDB

H40DM

J2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

(MSB) B11B

B10B

B9B

B8B

B7B

B6B

B5B

B4B

B3B

B2B

B1B

(LSB) B0B

F3B

F2B

F1B

F0B

DGNDB

R72

50

BUFLATB

C14

10

F

DGNDB

3.3VDB

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

R18

100

B11B (MSB)

R17

100

B10B

OE2

O15

O14

GND

O13

O12

VCC

O11

O10

GND

O9

O8

O7

O6

GND

O5

O4

VCC

O3

O2

GND

O1

O0

OE1

U17

74LCX16374

LE2

I15

I14

GND

I13

I12

VCC

I11

I10

GND

I9

I8

I7

I6

GND

I5

I4

VCC

I3

I2

GND

I1

I0

LE1

DUT_3.3VDB

DGNDB

DGNDB

DGNDB

DUT_3.3VDB

DGNDB

DGNDB

DGNDB

R16

100

B9B

R45

100

B6B

R46

100

B5B

R14

100

B3B

R40

100

B8B

R44

100

B7B

R15

100

B4B

R13

100

B2B

R24

100

B1B (LSB)

R23

100

B0B

R22

DNS

F3B

R20

DNS

F1B

R21

DNS

F2B

R19

DNS

F0B

DGNDB

DGNDB

DGNDB

DGNDB

DUT_3.3VDB

(LSB) D0A

D1A

D2A

D3A

D4A

D5A

D6A

D7A

D8A

D9A

D10A

D11A

DUT_3.3VDB

R53

0

R54

0

R49

0

R50

0

DGNDB

R8

50

LATCHB

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

R18

100

B11A (MSB)

R17

100

B10A

OE2

O15

O14

GND

O13

O12

VCC

O11

O10

GND

O9

O8

O7

O6

GND

O5

O4

VCC

O3

O2

GND

O1

O0

OE1

U16

74LCX16374

LE2

I15

I14

GND

I13

I12

VCC

I11

I10

GND

I9

I8

I7

I6

GND

I5

I4

VCC

I3

I2

GND

I1

I0

LE1

DUT_3.3VDA

DGNDA

DGNDA

DGNDA

DUT_3.3VDA

DGNDA

DGNDA

DGNDA

R16

100

B9A

R45

100

B6A

R46

100

B5A

R14

100

B3A

R40

100

B8A

R44

100

B7A

R15

100

B4A

R13

100

B2A

R24

100

B1A (LSB)

R23

100

B0A

R22

DNS

F3A

R20

DNS

F1A

R21

DNS

F2A

R19

DNS

F0A

DGNDA

DGNDA

DGNDA

DGNDA

DUT_3.3VDA

(LSB) D0A

D1A

D2A

D3A

D4A

D5A

D6A

D7A

D8A

D9A

D10A

D11A

DUT_3.3VDA

R52

0

R51

0

R47

0

R48

0

DGNDA

R7

50

LATCHA

NC = NO CONNECT

REV. A

AD10200

≠13≠

DGNDA

E42

E44

E48

E67

E70

E72

E73

E76

E81

E41

E43

E47

E68

E69

E71

E74

E75

E82

AGNDA

E65

E66

DGNDB

E36

E38

E40

E79

E84

E35

E37

E39

E80

E83

AGNDB

E29

E30

E46

E45

SO2

SO5

SO3

SO6

SO1

SO4

STAND OFFS ON THE BOARD

E33

DGNDB

DGNDB

DGNDB

E3

E4

AGNDB

AGNDA

E34

DGNDA

DGNDA

DGNDA

BANANA JACKS FOR GNDS AND PWRS

2

IN

+5VAA_

ERR

SD

NR

OUT

1

U14

3

ADP3330

5

6

SD

4

NC

D

DB

VBB

VCC

Q

QB

VEE

MC10EL16

U2

8

7

6

5

1

2

3

4

AGNDA

R56

33k

R58

33k

DGNDA

C6

0.1 F

R3

100

DGNDA

NC

D

DB

VBB

VCC

Q

QB

VEE

U3

8

7

6

5

1

2

3

4

DGNDA

+3.3VA

R4

100

DGNDA

R41

50

AGNDA

J12

SMA

C2

0.1 F

C1

0.1 F

R1

50

AGNDA

J5

ENCODE

SMA

AGNDA

C13

0.47 F

AGNDA

+3.3VA

AGNDA

R42

100

R43

100

ENCAB

ENCAB

C7

0.1 F

C8

0.1 F

AGNDA

D0

D0B

D1B

D1

VCC

Q0

Q1

VEE

MC100EPT23

8

7

6

5

1

2

3

4

DGNDA

+3.3VA

C5

0.1 F

DGNDA

E23

E19

LATCHA

BUFLATA

U4

1

2

IN

+5VAB_

ERR

SD

NR

OUT

1

U15

3

ADP3330

5

6

SD

4

NC

D

DB

VBB

VCC

Q

QB

VEE

MC10EL16

U11

8

7

6

5

1

2

3

4

AGNDB

R38

33k

R39

33k

DGNDB

C25

0.1 F

R3

100

DGNDA

NC

D

DB

VBB

VCC

Q

QB

VEE

MC10EL16

8

7

6

5

1

2

3

4

DGNDB

+3.3VDB

R66

100

DGNDB

R61

50

AGNDB

J11

SMA

C23

0.1 F

C22

0.1 F

R60

50

AGNDB

J10

ENCODE

SMA

AGNDB

C27

0.47 F

AGNDB

+3.3VB

AGNDB

R63

100

R64

100

ENCBB

ENCB

C24

0.1 F

C28

0.1 F

AGNDB

D0

D0B

D1B

D1

VCC

Q0

Q1

VEE

MC100EPT23

8

7

6

5

1

2

3

4

DGNDB

+3.3VB

C26

0.1 F

DGNDB

E24

E22

LATCHB

BUFLATB

U10

2

NC = NO CONNECT

NC = NO CONNECT

MC10EL16

U9

Figure 9b. Evaluation Board

REV. A

AD10200

≠14≠

BILL OF MATERIALS LIST FOR AD10200 EVAL BOARD

Qty.

Component Name

Ref Des

Value

Description

M/S P/Ns

2

74LCX16373MTD

U16, U17

74LCX16374MTD (Fairchild)

1

AD10200BZ

U1

AD10200BZ

2

ADP3330

U14, U15

SM 3.3 V Regulator

ADP3330ART-3.3-RL7 (Analog)

4

BRES0805

R38, R39, R56, R58

33 k

SM 0805 Resistor

ERJ6GEYJ333V (Panasonic)

4

BRES0805

R1, R41, R60,

50

SM 0805 Resistor

ERJ6GEYJ510V (Panasonic)

R61

8

BRES0805

R3, R4, R42, R43,

100

SM 0805 Resistor

ERJ6GEYJ101V (Panasonic)

R63, R64, R65, R66

23

CAP2

C1, C2, C5, C6,

0.1

µF

SM 0805 Capacitor

GRM40X7R104K025BL

C7, C8, C9, C10,

(MENA)

C12, C16, C17, C18,

C20, C21, C22, C23,

C24, C25, C26, C28,

C33, C34, C35

4

CAP2

C13, C27, C38, C39

0.47

µF

SM 1206 Capacitor

VJ1206U474MFXMB

(VITRAMON)

2

N49DM

J1, J2

2

◊20◊100 Male Connector

TSW-120-08G-D (Samtec)

4

IND2

L1, L2, L3, L4

47

Inductor

2743019447 (Fair Ride)

4

MC10EL16

U2, U3 U9, U11

MC1016EP16D (Motorola)

10

BJACK

BJ1 ≠ BJ10

POWER JACK

108-0740-001 (Johnson Comp.)

2

MC100ELT23

U4, U10

SY100ELT23L (Micrel-Synergy)

6

POLCAP2

C3, C4, C14, C15,

10

µF

SM 1812 Polar Capacitor

T491C106M016A57280

C29, C30

(KEMET)

8

RES2

R47, R48, R49,

0

SM 0805 Resistor

ERJ-6GEY0R00V (Panasonic)

R50, R51, R52,

R53, R54

4

RES4

R7, R8, R71, R72

50

SM 0805 Resistor

ERJ-6GEYJ510V (Panasonic)

24

RES2

R9, R10, R11, R12,

R13, R14, R15, R16,

R17, R18, R23, R24,

R25, R26, R27, R28,

R29, R30, R35, R36,

R40, R44, R45, R46

1

SMA

J4

A

IN

A2

142-0701-201 (Johnson Comp.)

1

SMA

J7

A

IN

B2

142-0701-201 (Johnson Comp.)

2

SMA

J11, J12

ENCODE

142-0701-201 (Johnson Comp.)

2

SMA

J5, J10

ENCODE

142-0701-201 (Johnson Comp.)

4

Stand-Off

S01≠S04

Stand-Off

313-2477-016 (Johnson Comp.)

4

Screws

Screws (Stand-Off)

MPMS 0040005PH (Building

Fasteners)

1

PCB

AD10200 Eval Board

GS03363 Rev. A

REV. A

AD10200

≠15≠

Figure 10a. Bottom View

C14

C4

C30

R72

R61

C3

C27

R38

U15

C22

R60

C23

R63

C35

U11

C33

C36

C24

C21

C20

C34

U14

C13

R56

C37

U2

R42

C7

C2

C1

R1

R41

R3

C6

R58

U4

C10

E48

R4

U3

R43

C8

U16

C9

R7

R51

R52

E40

C18

R65

C28

U9

U10

R39

R66

C25

R64

R53

R54

R49

R50

R8

C17

R48

R47

U17

C15

R71

C29

GND TIE

GND TIE

GND TIES

GND TIES

GND TIE

GND TIE

GND TIE

GND TIE

Figure 10b. Bottom Assembly

REV. A

AD10200

≠16≠

Figure 10c. Ground 1

AGNDA

DGNDB

AGNDB

DGNDA

Figure 10d. Ground 2

REV. A

AD10200

≠17≠

C14

C4

C30

R72

R61

C3

C27

R38

U15

C22

R60

C23

R63

C35

U11

C33

C36

C24

C21

C20

C34

U14

C13

R56

C37

U2

R42

C7

C2

C1

R1

R41

R3

C6

R58

U4

C10

E48

R4

U3

R43

C8

U16

C9

R7

R51

R52

E40

C18

R65

C28

U9

U10

R39

R66

C25

R64

R53

R54

R49

R50

R8

C17

R48

R47

U17

C15

R71

C29

GND TIE

GND TIE

GND TIES

GND TIES

GND TIE

GND TIE

GND TIE

GND TIE

Figure 10e. Bottom Silk

Figure 10f. Top View

REV. A

AD10200

≠18≠

E5

E63

E27

L4

C16

E33

E55

E58

E59

E60

U6

C39

E61

E62

E3

E1

E2

E26

R11

E80

E46

E37

E35

E30

E79

E45

E38

E36

E29

J10

J11

L2

E4

L3

E28

E6

E64

E11

E47

E39

E8

J6

J7

E50

E49

J5

J4

J3

PIN 1

U1

J12

E9

E10

E66

E42

E41

E65

E81

E82

C5

E56

E54

E52

U5

E53

E51

C38

R22

R21

R19

R20

E19

E23

E57

E83

E84

C26

R30

R10

E22

E24

E77

E78

R27

R28

R29

R36

R35

E7

E12

R26

R25

R9

R12

J2

R31

R32

R33

R34

R23

R44

R15

R45

R46

R40

R17

R16

R14

R13

R24

R18

L1

E25

J1

E68 E67

E75

E70

E72

E73

E74

E76

E69

E34

C12

E71

E43 E44

AINB1

AINA1

BJ1

EXTRA

BJ2

EXTRA

AINB2

REF_A

AINA2

REF_B

2/10 00

GS03363 (A)

AD10200 EVALUATION BOARD

BEL

ANALOG

DEVICES

COPYRIGHT

AGNDB

+5VAB

DGNDB

3.3VDB

ENCA

ENCABAR

3.3VDA

DGNDA

AGNDA

+5VAA

ENCB

GND TIES

GND TIES

GND TIE

GND TIE

GND TIE

LATCHA

BUFLATA

LATCHB

BUFLATB

ENCBBAR

GND TIE

Figure 10g. Top Assembly

E5

E63

E27

L4

C16

E33

E55

E58

E59

E60

U6

C39

E61

E62

E3

E1

E2

E26

R11

E80

E46

E37

E35

E30

E79

E45

E38

E36

E29

J10

J11

L2

E4

L3

E28

E6

E64

E11

E47

E39

E8

J6

J7

E50

E49

J5

J4

J3

PIN 1

U1

J12

E9

E10

E66

E42

E41

E65

E81

E82

C5

E56

E54

E52

U5

E53

E51

C38

R22

R21

R19

R20

E19

E23

E57

E83

E84

C26

R30

R10

E22

E24

E77

E78

R27

R28

R29

R36

R35

E7

E12

R26

R25

R9

R12

J2

R31

R32

R33

R34

R23

R44

R15

R45

R46

R40

R17

R16

R14

R13

R24

R18

L1

E25

J1

E68 E67

E75

E70

E72

E73

E74

E76

E69

E34

C12

E71

E43 E44

AINB1

AINA1

BJ1

EXTRA

BJ2

EXTRA

AINB2

REF_A

AINA2

REF_B

2/10 00

GS03363 (A)

AD10200 EVALUATION BOARD

BEL

ANALOG

DEVICES

COPYRIGHT

AGNDB

+5VAB

DGNDB

3.3VDB

ENCA

ENCABAR

3.3VDA

DGNDA

AGNDA

+5VAA

ENCB

GND TIES

GND TIES

GND TIE

GND TIE

GND TIE

LATCHA

BUFLATA

LATCHB

BUFLATB

ENCBBAR

GND TIE

Figure 10h. Top Silk

REV. A

≠19≠

AD10200

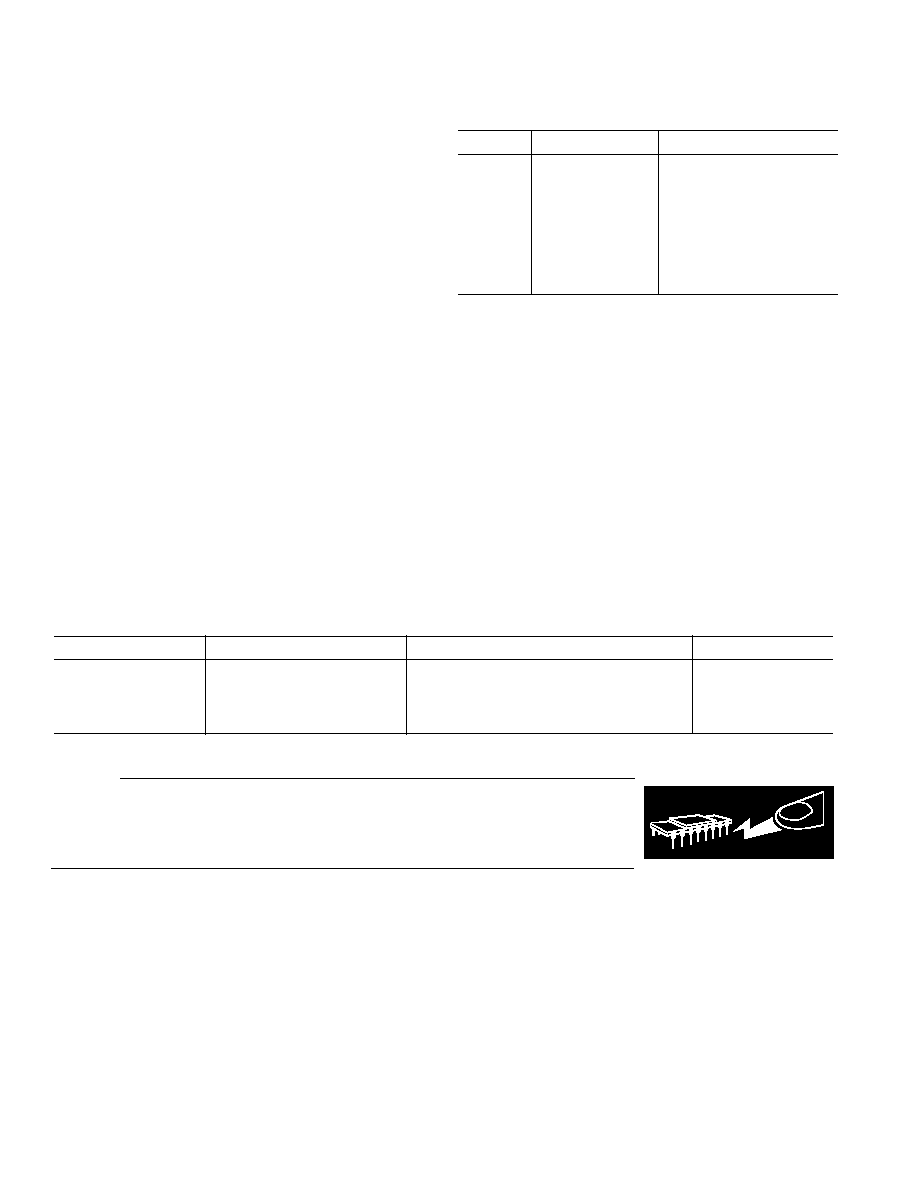

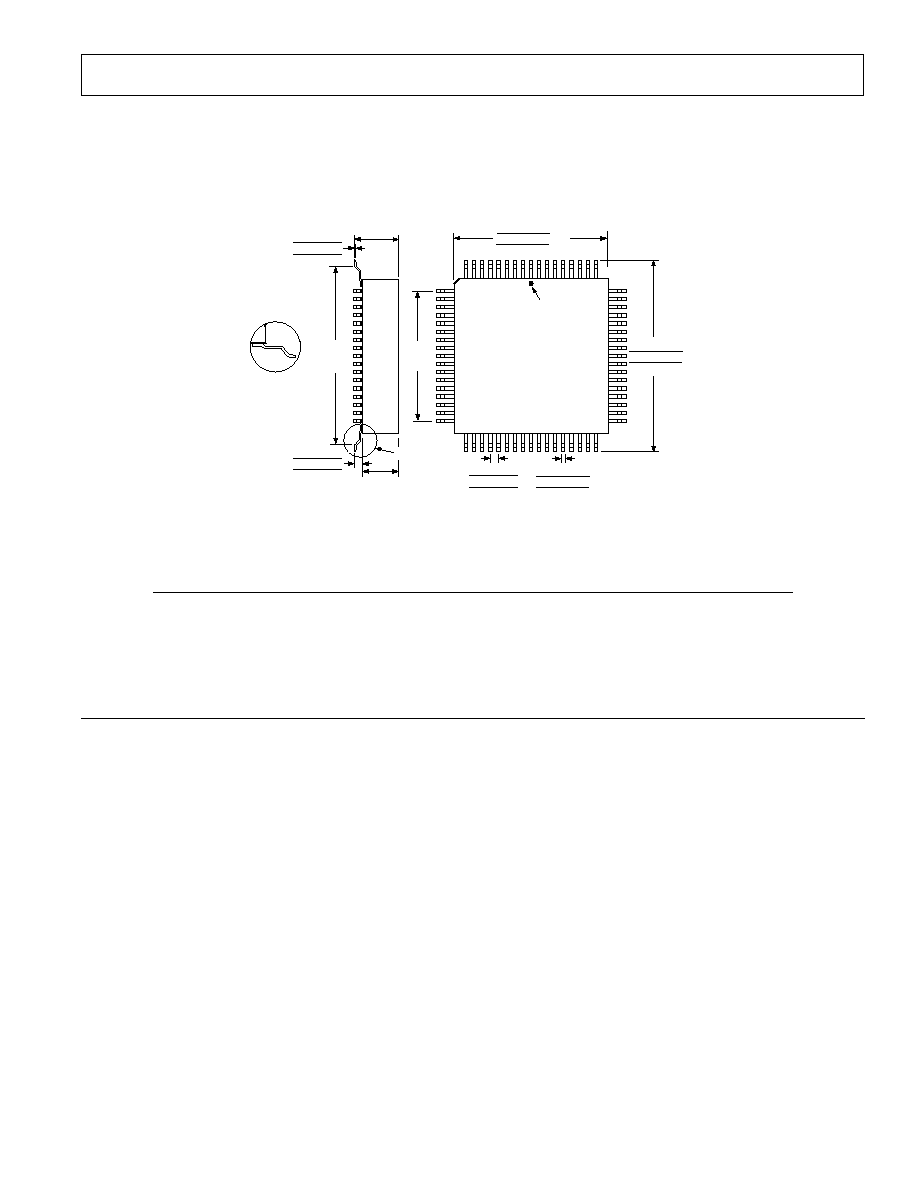

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

68-Lead Ceramic Leaded Chip Carrier

(Z-68B)

TOE DOWN

ANGLE

0≠8 DEGREES

DETAIL A

1.190 (30.23)

1.180 (29.97) SQ

1.170 (29.72)

TOP VIEW

(PINS DOWN)

PIN 1

10

26

9

61

60

43

27

44

0.800

(20.32)

BSC

0.960 (24.38)

0.950 (24.13) SQ

0.940 (23.88)

0.055 (1.40)

0.050 (1.27)

0.045 (1.14)

0.021 (0.533)

0.017 (0.432)

0.014 (0.357)

0.230 (5.84)

MAX

0.290 (7.37)

MAX

DETAIL A

0.010 (0.25)

0.008 (0.20)

0.007 (0.18)

0.060 (1.52)

0.050 (1.27)

0.040 (1.02)

1.070

(27.18)

MIN

Revision History

Location

Page

Data Sheet changed from REV. 0 to REV. A.

Edit to ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Edit to Figure 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Edit to ENCODE Inputs section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Edit to Figure 9a . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

≠20≠

C01634≠0-8/01(A)

PRINTED IN U.S.A.