| ÐлекÑÑоннÑй компоненÑ: AD5318 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© 2003 Analog Devices, Inc. All rights reserved.

AD5308/AD5318/AD5328

*

2.5 V to 5.5 V Octal Voltage Output

8-/10-/12-Bit DACs in 16-Lead TSSOP

*Protected by U.S.Patent No. 5,969,657; other patents pending.

FEATURES

AD5308: 8 Buffered 8-Bit DACs in 16-Lead TSSOP

A Version: 1 LSB INL, B Version: 0.75 LSB INL

AD5318: 8 Buffered 10-Bit DACs in 16-Lead TSSOP

A Version: 4 LSB INL, B Version: 3 LSB INL

AD5328: 8 Buffered 12-Bit DACs in 16-Lead TSSOP

A Version: 16 LSB INL, B Version: 12 LSB INL

Low Power Operation: 0.7 mA @ 3 V

Guaranteed Monotonic by Design over All Codes

Power-Down to 120 nA @ 3 V, 400 nA @ 5 V

Double-Buffered Input Logic

Buffered/Unbuffered/V

DD

Reference Input Options

Output Range: 0 V to V

REF

or 0 V to 2 V

REF

Power-On Reset to 0 V

Programmability

Individual Channel Power-Down

Simultaneous Update of Outputs (

LDAC)

Low Power, SPI

®

, QSPITM, MICROWIRETM, and DSP

Compatible 3-Wire Serial Interface

On-Chip Rail-to-Rail Output Buffer Amplifiers

Temperature Range 40 C to +105 C

APPLICATIONS

Portable Battery-Powered Instruments

Digital Gain and Offset Adjustment

Programmable Voltage and Current Sources

Optical Networking

Automatic Test Equipment

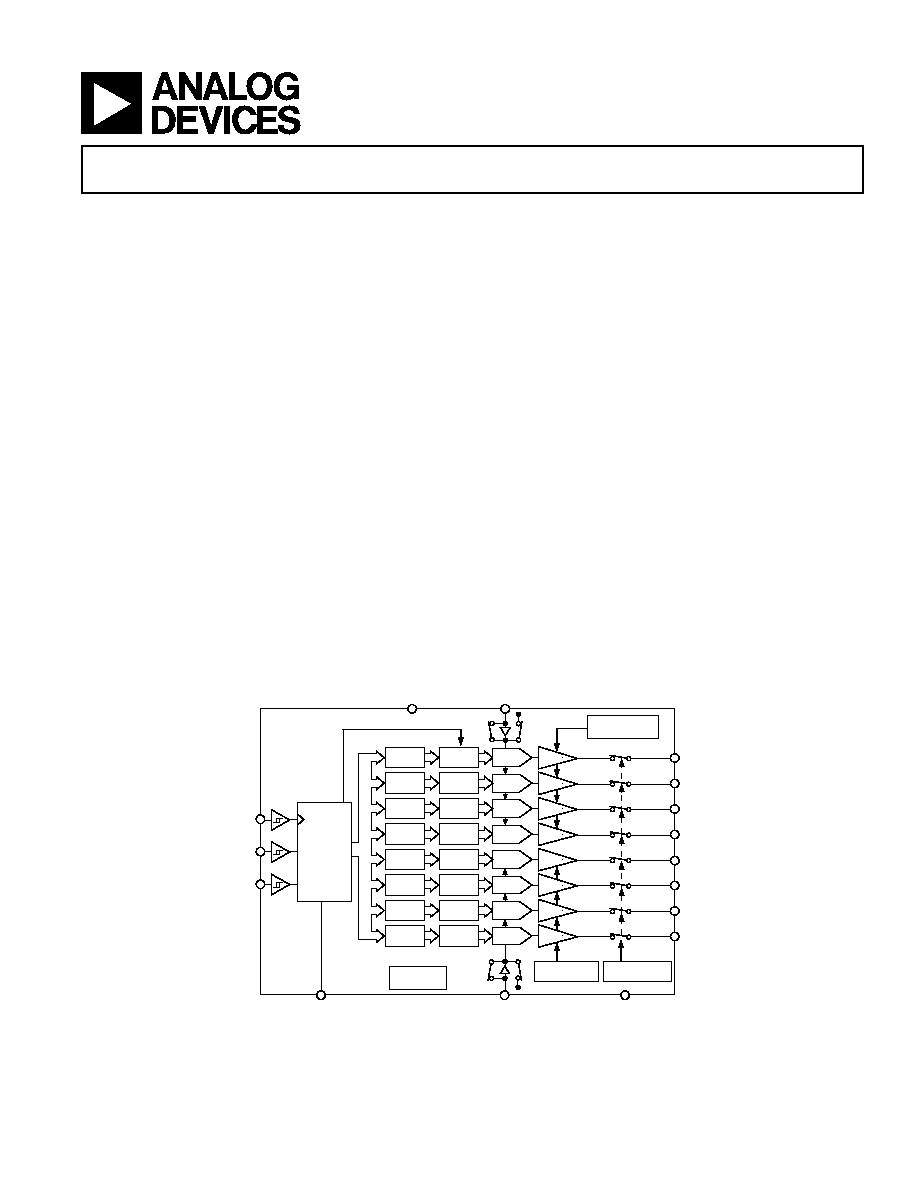

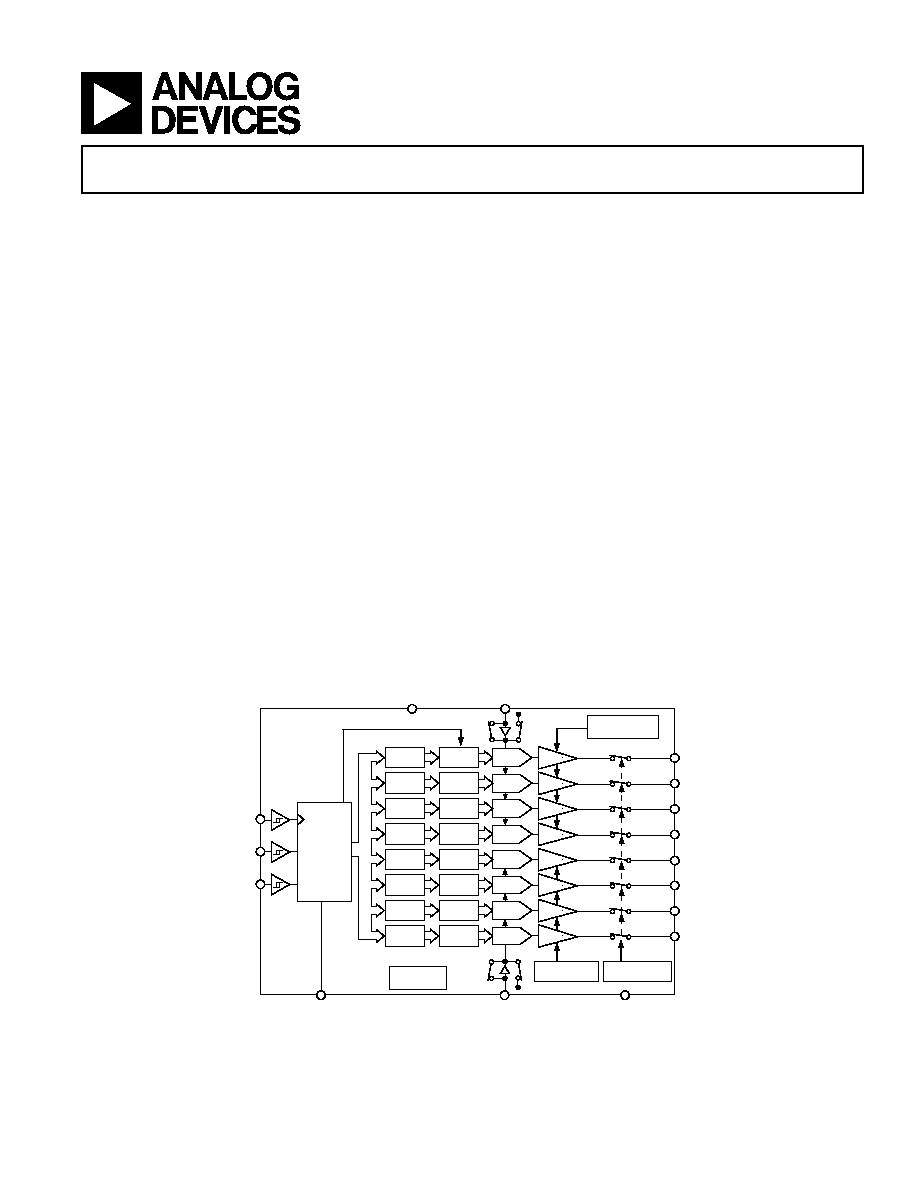

FUNCTIONAL BLOCK DIAGRAM

BUFFER

INPUT

REGISTER

DAC

REGISTER

INTERFACE

LOGIC

DIN

LDAC

GND

V

OUT

B

V

OUT

C

V

OUT

D

V

OUT

E

V

OUT

G

V

OUT

H

V

OUT

F

V

DD

POWER-ON

RESET

GAIN-SELECT

LOGIC

V

OUT

A

V

REF

EFGH

V

REF

ABCD

SYNC

SCLK

POWER-DOWN

LOGIC

GAIN-SELECT

LOGIC

STRING

DAC B

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC C

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC D

BUFFER

INPUT

REGISTER

DAC

REGISTER

STRING

DAC E

BUFFER

INPUT

REGISTER

DAC

REGISTER

BUFFER

INPUT

REGISTER

DAC

REGISTER

BUFFER

INPUT

REGISTER

DAC

REGISTER

BUFFER

INPUT

REGISTER

DAC

REGISTER

V

DD

V

DD

LDAC

STRING

DAC F

STRING

DAC G

STRING

DAC H

STRING

DAC A

GENERAL DESCRIPTION

The AD5308/AD5318/AD5328 are octal 8-, 10-, and 12-bit

buffered voltage output DACs in a 16-lead TSSOP. They operate

from a single 2.5 V to 5.5 V supply, consuming 0.7 mA typ at 3 V.

Their on-chip output amplifiers allow the outputs to swing

rail-to-rail with a slew rate of 0.7 V/

µs. The AD5308/AD5318/

AD5328 use a versatile 3-wire serial interface that operates at

clock rates up to 30 MHz and is compatible with standard

SPI, QSPI, MICROWIRE, and DSP interface standards.

The references for the eight DACs are derived from two reference

pins (one per DAC quad). These reference inputs can be

configured as buffered, unbuffered, or V

DD

inputs. The parts

incorporate a power-on reset circuit, which ensures that the DAC

outputs power up to 0 V and remain there until a valid write to

the device takes place. The outputs of all DACs may be updated

simultaneously using the asynchronous

LDAC input. The parts

contain a power-down feature that reduces the current consump-

tion of the devices to 400 nA at 5 V (120 nA at 3 V). The eight

channels of the DAC may be powered down individually.

All three parts are offered in the same pinout, which allows

users to select the resolution appropriate for their application

without redesigning their circuit board.

Mobile Communications

Programmable Attenuators

Industrial Process Control

REV. B

2

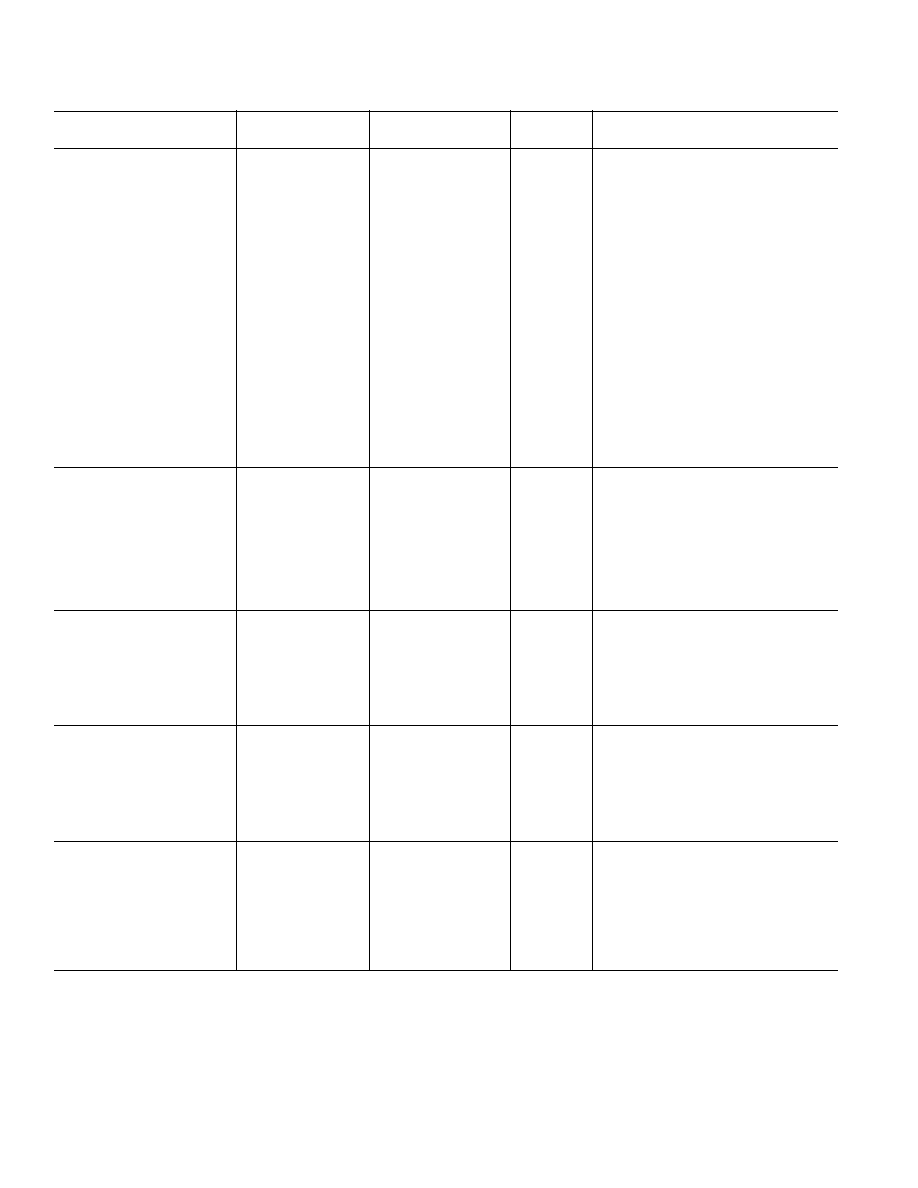

AD5308/AD5318/AD5328SPECIFICATIONS

(V

DD

= 2.5 V to 5.5 V; V

REF

= 2 V; R

L

= 2 k

to

GND; C

L

= 200 pF to GND; all specifications T

MIN

to T

MAX

, unless otherwise noted.)

A Version

2

B Version

2

Parameter

1

Min

Typ

Max

Min

Typ

Max

Unit

Conditions/Comments

DC PERFORMANCE

3, 4

AD5308

Resolution

8

8

Bits

Relative Accuracy

±0.15

±1

±0.15

±0.75 LSB

Differential Nonlinearity

±0.02

±0.25

±0.02

±0.25 LSB

Guaranteed Monotonic by Design over All Codes

AD5318

Resolution

10

10

Bits

Relative Accuracy

±0.5

±4

±0.5

±3

LSB

Differential Nonlinearity

±0.05

±0.50

±0.05

±0.50 LSB

Guaranteed Monotonic by Design over All Codes

AD5328

Resolution

12

12

Bits

Relative Accuracy

±2

±16

±2

±12

LSB

Differential Nonlinearity

±0.2

±1.0

±0.2

±1.0

LSB

Guaranteed Monotonic by Design over All Codes

Offset Error

±5

±60

±5

±60

mV

V

DD

= 4.5 V, Gain = +2. See Figures 2 and 3.

Gain Error

±0.30

±1.25

±0.30

±1.25 % of FSR

V

DD

= 4.5 V, Gain = +2. See Figures 2 and 3.

Lower Deadband

5

10

60

10

60

mV

See Figure 2. Lower deadband exists only if offset

error is negative.

Upper Deadband

5

10

60

10

60

mV

See Figure 3. Upper deadband exists only if V

REF

=

V

DD

and offset plus gain error is positive.

Offset Error Drift

6

12

12

ppm of FSR/

°C

Gain Error Drift

6

5

5

ppm of FSR/

°C

DC Power Supply Rejection Ratio

6

60

60

dB

V

DD

=

± 10%

DC Crosstalk

6

200

200

µV

R

L

= 2 k

to GND or V

DD

DAC REFERENCE INPUTS

6

V

REF

Input Range

1.0

V

DD

1.0

V

DD

V

Buffered Reference Mode

0.25

V

DD

0.25

V

DD

V

Unbuffered Reference Mode

V

REF

Input Impedance (R

DAC

)

>10.0

>10.0

M

Buffered Reference Mode and Power-Down Mode

37.0

45.0

37.0

45.0

k

Unbuffered Reference Mode. 0 V to V

REF

Output Range.

18.0

22.0

18.0

22.0

k

Unbuffered Reference Mode. 0 V to 2 V

REF

Output Range.

Reference Feedthrough

70.0

70.0

dB

Frequency = 10 kHz

Channel-to-Channel Isolation

75.0

75.0

dB

Frequency = 10 kHz

OUTPUT CHARACTERISTICS

6

Minimum Output Voltage

7

0.001

0.001

V

This is a measure of the minimum and maximum

Maximum Output Voltage

7

V

DD

0.001

V

DD

0.001

V

drive capability of the output amplifier.

DC Output Impedance

0.5

0.5

Short Circuit Current

25.0

25.0

mA

V

DD

= 5 V

16.0

16.0

mA

V

DD

= 3 V

Power-Up Time

2.5

2.5

µs

Coming Out of Power-Down Mode. V

DD

= 5 V.

5.0

5.0

µs

Coming Out of Power-Down Mode. V

DD

= 3 V.

LOGIC INPUTS

6

Input Current

±1

±1

µA

V

IL

, Input Low Voltage

0.8

0.8

V

V

DD

= 5 V

± 10%

0.8

0.8

V

V

DD

= 3 V

± 10%

0.7

0.7

V

V

DD

= 2.5 V

V

IH

, Input High Voltage

1.7

1.7

V

V

DD

= 2.5 V to 5.5 V; TTL and CMOS

Compatible

Pin Capacitance

3.0

3.0

pF

POWER REQUIREMENTS

V

DD

2.5

5.5

2.5

5.5

V

I

DD

(Normal Mode)

8

V

IH

= V

DD

and V

IL

= GND

V

DD

= 4.5 V to 5.5 V

1.0

1.8

1.0

1.8

mA

All DACs in Unbuffered Mode. In Buffered mode,

V

DD

= 2.5 V to 3.6 V

0.7

1.5

0.7

1.5

mA

extra current is typically x

µA per DAC; x = (5 µA

+ V

REF

/R

DAC

)/4.

I

DD

(Power-Down Mode)

9

V

IH

= V

DD

and V

IL

= GND

V

DD

= 4.5 V to 5.5 V

0.4

1

0.4

1

µA

V

DD

= 2.5 V to 3.6 V

0.12

1

0.12

1

µA

NOTES

1

See the Terminology section.

2

Temperature range (A, B Version): 40

°C to +105°C; typical at +25°C.

3

DC specifications tested with the outputs unloaded unless stated otherwise.

4

Linearity is tested using a reduced code range: AD5308 (Code 8 to Code 255), AD5318 (Code 28 to Code 1023), and AD5328 (Code 115 to Code 4095).

5

This corresponds to x codes. x = deadband voltage/LSB size.

6

Guaranteed by design and characterization; not production tested.

7

For the amplifier output to reach its minimum voltage, offset error must be negative; for the amplifier output to reach its maximum voltage, V

REF

= V

DD

and offset plus gain error

must be positive.

8

Interface inactive. All DACs active. DAC outputs unloaded.

9

All eight DACs powered down.

Specifications subject to change without notice.

REV. B

AD5308/AD5318/AD5328

3

AC CHARACTERISTICS

1

(V

DD

= 2.5 V to 5.5 V; R

L

= 2 k

to GND; C

L

= 200 pF to GND; all specifications T

MIN

to T

MAX

, unless

otherwise noted.)

A, B Version

3

Parameter

2

Min

Typ

Max

Unit

Conditions/Comments

Output Voltage Settling Time

V

REF

= V

DD

= 5 V

AD5308

6

8

µs

1/4 Scale to 3/4 Scale Change (0x40 to 0xC0)

AD5318

7

9

µs

1/4 Scale to 3/4 Scale Change (0x100 to 0x300)

AD5328

8

10

µs

1/4 Scale to 3/4 Scale Change (0x400 to 0xC00)

Slew Rate

0.7

V/

µs

Major-Code Change Glitch Energy

12

nV-s

1 LSB Change around Major Carry

Digital Feedthrough

0.5

nV-s

Digital Crosstalk

0.5

nV-s

Analog Crosstalk

1

nV-s

DAC-to-DAC Crosstalk

3

nV-s

Multiplying Bandwidth

200

kHz

V

REF

= 2 V

± 0.1 V p-p. Unbuffered Mode.

Total Harmonic Distortion

70

dB

V

REF

= 2.5 V

± 0.1 V p-p. Frequency = 10 kHz.

NOTES

1

Guaranteed by design and characterization; not production tested.

2

See the Terminology section.

3

Temperature range (A, B Version): 40

°C to +105°C; typical at +25°C.

Specifications subject to change without notice.

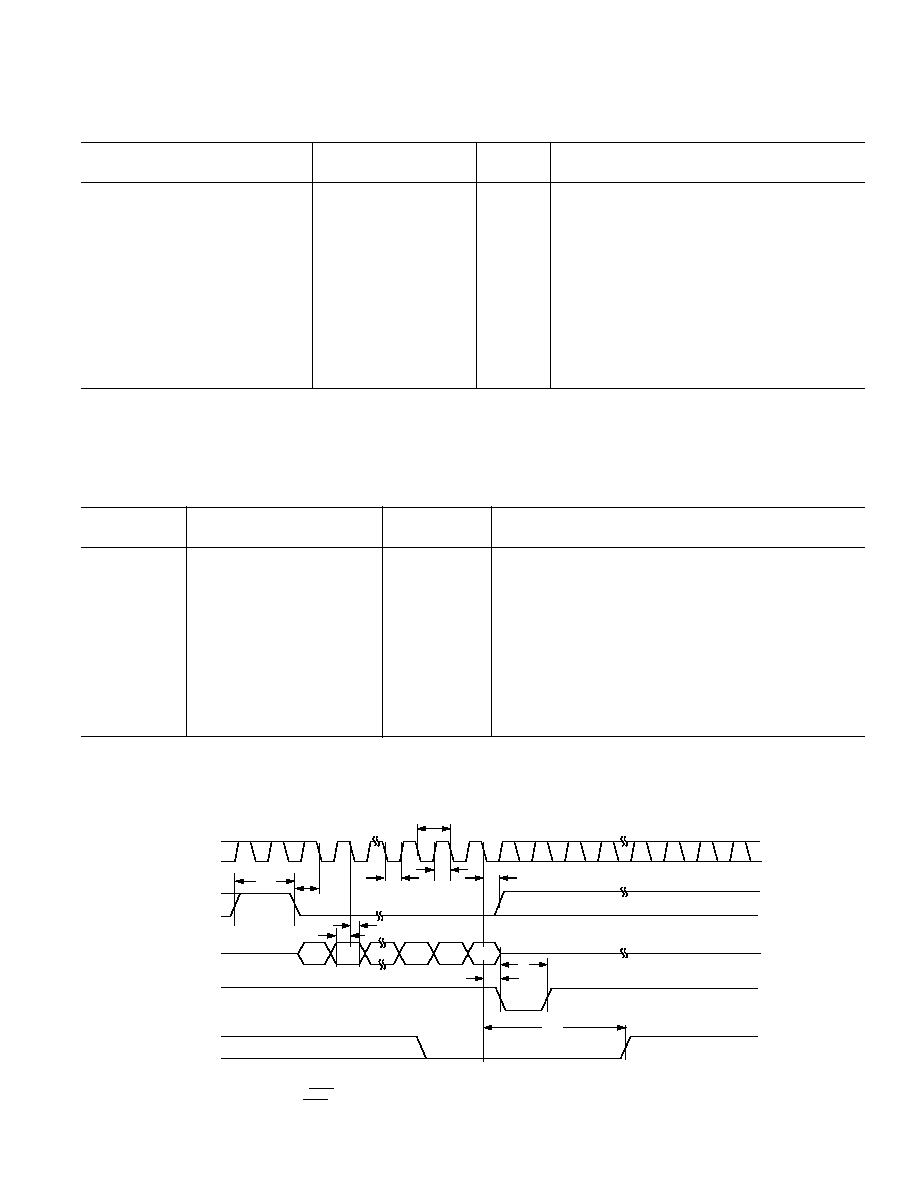

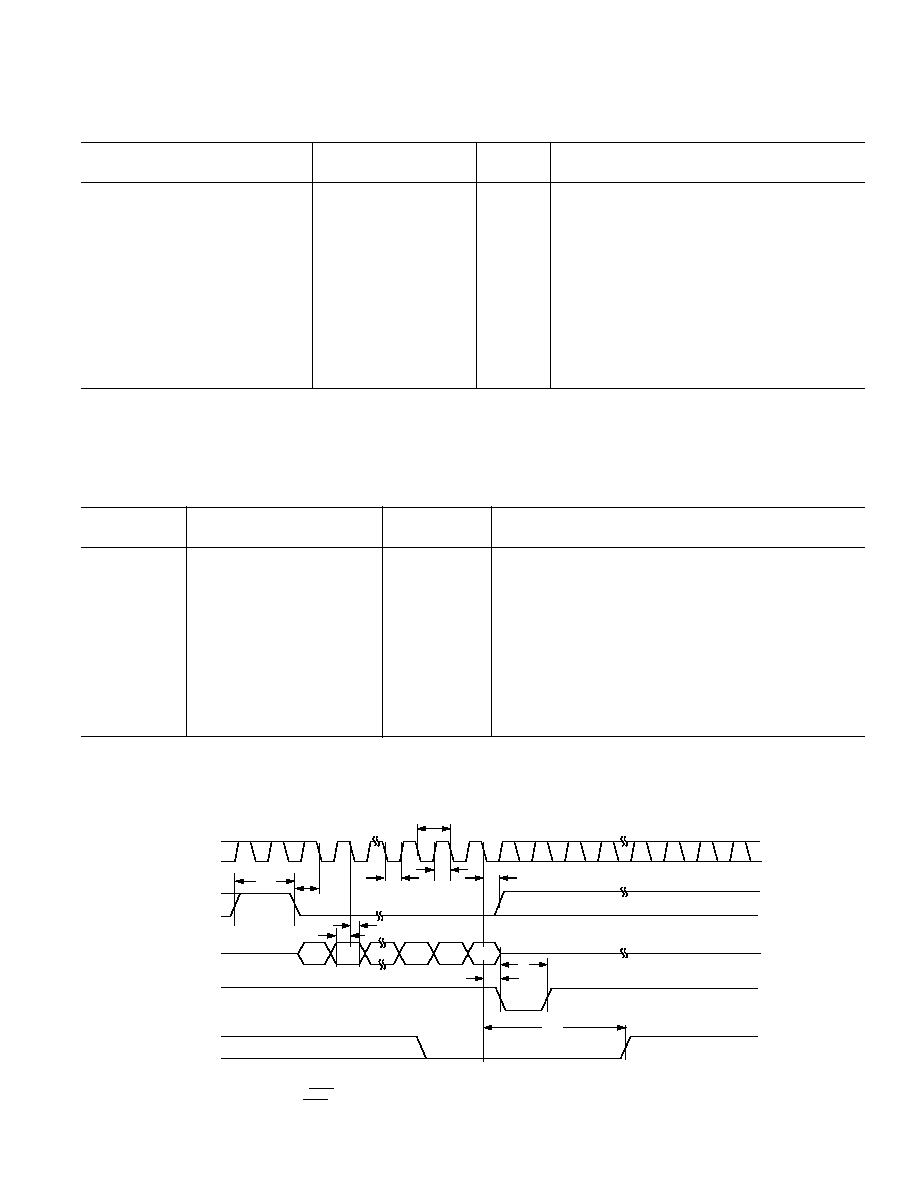

TIMING CHARACTERISTICS

1, 2, 3

A, B Version

Parameter

Limit at T

MIN

, T

MAX

Unit

Conditions/Comments

t

1

33

ns min

SCLK Cycle Time

t

2

13

ns min

SCLK High Time

t

3

13

ns min

SCLK Low Time

t

4

13

ns min

SYNC to SCLK Falling Edge Setup Time

t

5

5

ns min

Data Setup Time

t

6

4.5

ns min

Data Hold Time

t

7

0

ns min

SCLK Falling Edge to

SYNC Rising Edge

t

8

50

ns min

Minimum

SYNC High Time

t

9

20

ns min

LDAC Pulsewidth

t

10

20

ns min

SCLK Falling Edge to

LDAC Rising Edge

t

11

0

ns min

SCLK Falling Edge to

LDAC Falling Edge

NOTES

1

Guaranteed by design and characterization; not production tested.

2

All input signals are specified with tr = tf = 5 ns (10% to 90% of V

DD

) and timed from a voltage level of (V

IL

+ V

IH

)/2.

3

See Figures 2 and 3.

Specifications subject to change without notice.

SCLK

SYNC

DIN

DB15

DB0

LDAC

1

LDAC

2

NOTES

1

ASYNCHRONOUS LDAC UPDATE MODE

2

SYNCHRONOUS LDAC UPDATE MODE

t

1

t

2

t

8

t

3

t

4

t

5

t

6

t

9

t

11

t

7

t

10

Figure 1. Serial Interface Timing Diagram

REV. B

4

AD5308/AD5318/AD5328

ABSOLUTE MAXIMUM RATINGS

1, 2

(T

A

= 25

°C, unless otherwise noted.)

V

DD

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.3 V to +7 V

Digital Input Voltage to GND . . . . . . . 0.3 V to V

DD

+ 0.3 V

Reference Input Voltage to GND . . . . 0.3 V to V

DD

+ 0.3 V

V

OUT

AV

OUT

D to GND . . . . . . . . . . . 0.3 V to V

DD

+ 0.3 V

Operating Temperature Range

Industrial (A, B Version) . . . . . . . . . . . . . 40

°C to +105°C

Storage Temperature Range . . . . . . . . . . . . 65

°C to +150°C

Junction Temperature (T

J MAX

) . . . . . . . . . . . . . . . . . . . 150

°C

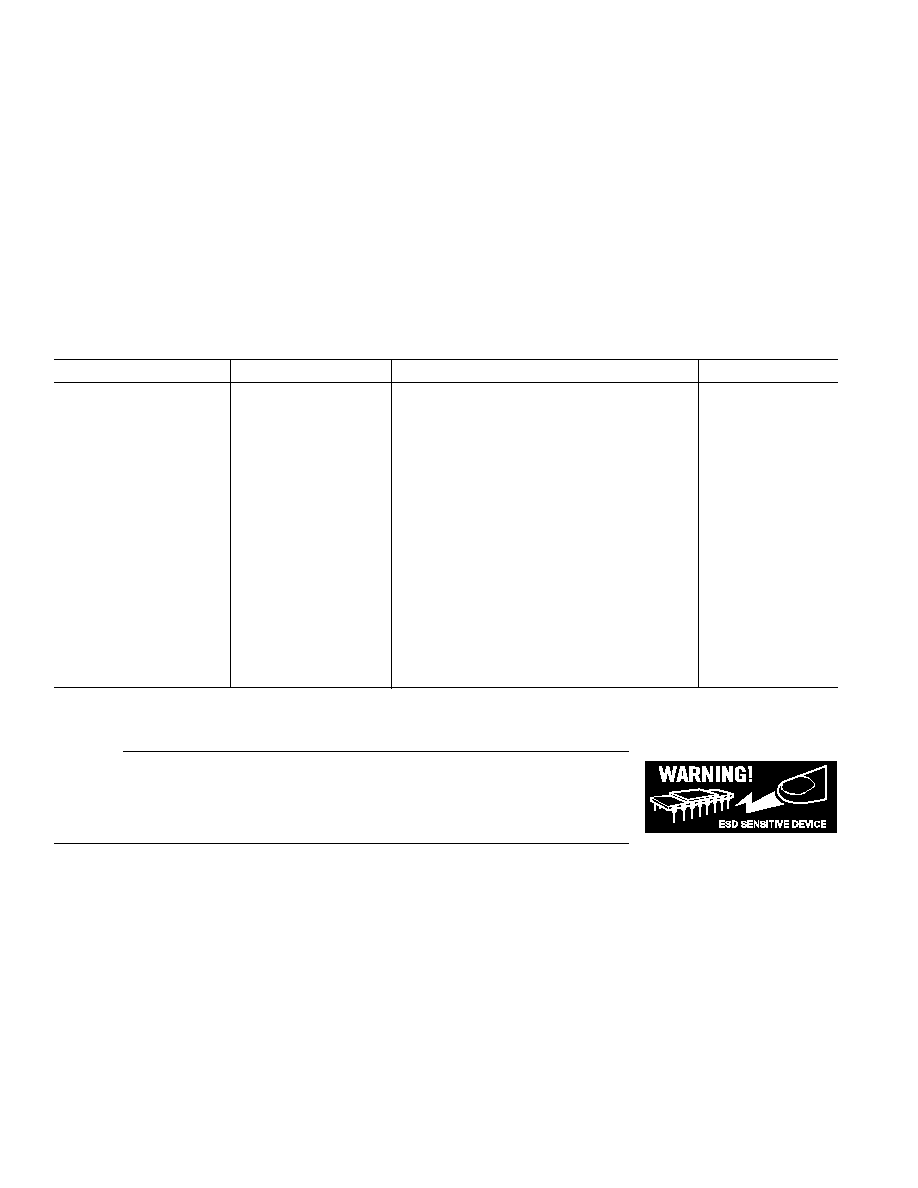

ORDERING GUIDE

Model

Temperature Range

Package Description

Package Option

AD5308ARU

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5308ARU-REEL7

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5308BRU

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5308BRU-REEL

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5308BRU-REEL7

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5318ARU

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5318ARU-REEL7

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5318BRU

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5318BRU-REEL

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5318BRU-REEL7

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5318BRUZ

*

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5318BRUZ-REEL

*

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5318BRUZ-REEL7

*

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5328ARU

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5328ARU-REEL7

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5328BRU

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5328BRU-REEL

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

AD5328BRU-REEL7

40

°C to +105°C

Thin Shrink Small Outline Package (TSSOP)

RU-16

*Z = Pb-free part.

16-Lead TSSOP

Power Dissipation . . . . . . . . . . . . . . . . . . . (T

J MAX

T

A

)/

JA

JA

Thermal Impedance . . . . . . . . . . . . . . . . . . . 150.4

°C/W

Reflow Soldering

Peak Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

°C

Time at Peak Temperature . . . . . . . . . . . . . 10 sec to 40 sec

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute maximum rating condi-

tions for extended periods may affect device reliability.

2

Transient currents of up to 100 mA will not cause SCR latch-up.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD5308/AD5318/AD5328 feature proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions

are recommended to avoid performance degradation or loss of functionality.

REV. B

AD5308/AD5318/AD5328

5

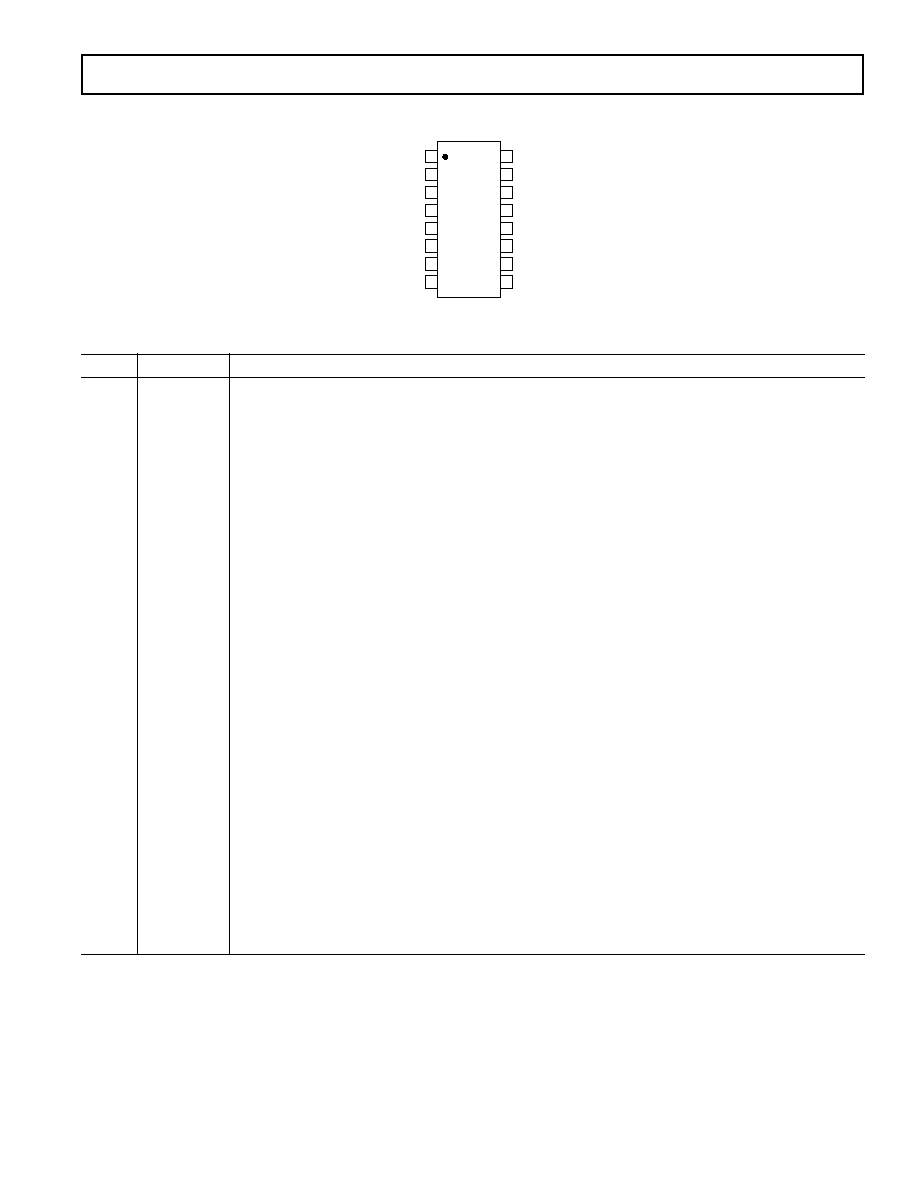

PIN CONFIGURATION

TOP VIEW

(Not to Scale)

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

SYNC

LDAC

V

DD

V

OUT

A

V

OUT

B

V

OUT

C

V

OUT

D

V

REF

ABCD

SCLK

DIN

V

OUT

E

AD5308/

AD5318/

AD5328

V

REF

EFGH

V

OUT

F

V

OUT

G

V

OUT

H

GND

PIN FUNCTION DESCRIPTIONS

Pin No.

Mnemonic

Function

1

LDAC

This active low-control input transfers the contents of the input registers to their respective DAC registers.

Pulsing this pin low allows any or all DAC registers to be updated if the input registers have new data.

This allows simultaneous update of all DAC outputs. Alternatively, this pin can be tied permanently low.

2

SYNC

Active Low-Control Input. This is the frame synchronization signal for the input data. When

SYNC goes

low, it powers on the SCLK and DIN buffers and enables the input shift register. Data is transferred in

on the falling edges of the following 16 clocks. If

SYNC is taken high before the 16th falling edge, the

rising edge of

SYNC acts as an interrupt and the write sequence is ignored by the device.

3

V

DD

Power Supply Input. These parts can be operated from 2.5 V to 5.5 V, and the supply should be

decoupled with a 10

µF capacitor in parallel with a 0.1 µF capacitor to GND.

4

V

OUT

A

Buffered Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.

5

V

OUT

B

Buffered Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.

6

V

OUT

C

Buffered Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.

7

V

OUT

D

Buffered Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.

8

V

REF

ABCD

Reference Input Pin for DACs A, B, C, and D. It may be configured as a buffered, unbuffered, or V

DD

input to the four DACs, depending on the state of the BUF and V

DD

control bits. It has an input range

from 0.25 V to V

DD

in unbuffered mode and from 1 V to V

DD

in buffered mode.

9

V

REF

EFGH

Reference Input Pin for DACs E, F, G, and H. It may be configured as a buffered, unbuffered, or V

DD

input to the four DACs, depending on the state of the BUF and V

DD

control bits. It has an input range

from 0.25 V to V

DD

in unbuffered mode and from 1 V to V

DD

in buffered mode.

10

V

OUT

E

Buffered Analog Output Voltage from DAC E. The output amplifier has rail-to-rail operation.

11

V

OUT

F

Buffered Analog Output Voltage from DAC F. The output amplifier has rail-to-rail operation.

12

V

OUT

G

Buffered Analog Output Voltage from DAC G. The output amplifier has rail-to-rail operation.

13

V

OUT

H

Buffered Analog Output Voltage from DAC H. The output amplifier has rail-to-rail operation.

14

GND

Ground Reference Point for All Circuitry on the Part.

15

DIN

Serial Data Input. This device has a 16-bit shift register. Data is clocked into the register on the falling

edge of the serial clock input. The DIN input buffer is powered down after each write cycle.

16

SCLK

Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock

input. Data can be transferred at rates up to 30 MHz. The SCLK input buffer is powered down after

each write cycle.

Document Outline

- FEATURES

- APPLICATIONS

- GENERAL DESCRIPTION

- FUNCTIONAL BLOCK DIAGRAM

- SPECIFICATIONS

- AC CHARACTERISTICS

- TIMING CHARACTERISTICS

- ABSOLUTE MAXIMUM RATINGS

- ORDERING GUIDE

- PIN CONFIGURATION

- PIN FUNCTION DESCRIPTIONS

- TERMINOLOGY

- Relative Accuracy

- Differential Nonlinearity

- Offset Error

- Gain Error

- Offset Error Drift

- Gain Error Drift

- DC Power Supply Rejection Ratio (PSRR)

- DC Crosstalk

- Reference Feedthrough

- Channel-to-Channel Isolation

- Major-Code Transition Glitch Energy

- Digital Feedthrough

- Digital Crosstalk

- Analog Crosstalk

- DAC-to-DAC Crosstalk

- Multiplying Bandwidth

- Total Harmonic Distortion

- Typical Performance Characteristics

- FUNCTIONAL DESCRIPTION

- Digital-to-Analog Section

- Resistor String

- DAC Reference Inputs

- Output Amplifier

- POWER-ON RESET

- SERIAL INTERFACE

- Input Shift Register

- DAC Write

- Control Functions

- Low Power Serial Interface

- LOAD DAC INPUT (LDAC) FUNCTION

- DOUBLE-BUFFERED INTERFACE

- POWER-DOWN MODE

- MICROPROCESSOR INTERFACING

- ADSP-2101/ADSP-2103 to AD5308/AD5318/AD5328 Interface

- 68HC11/68L11 to AD5308/AD5318/AD5328 Interface

- 80C51/80L51 to AD5308/AD5318/AD5328 Interface

- MICROWIRE to AD5308/AD5318/AD5328 Interface

- APPLICATIONS

- Typical Application Circuit

- Driving VDD from the Reference Voltage

- Bipolar Operation Using the AD5308/AD5318/AD5328

- Opto-Isolated Interface for Process Control Applications

- Decoding Multiple AD5308/AD5318/AD5328s

- OUTLINE DIMENSIONS

- Revision History