| ÐлекÑÑоннÑй компоненÑ: AD5532-1 | СкаÑаÑÑ:  PDF PDF  ZIP ZIP |

Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

AD5532*

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2000

32-Channel, 14-Bit

Voltage-Output DAC

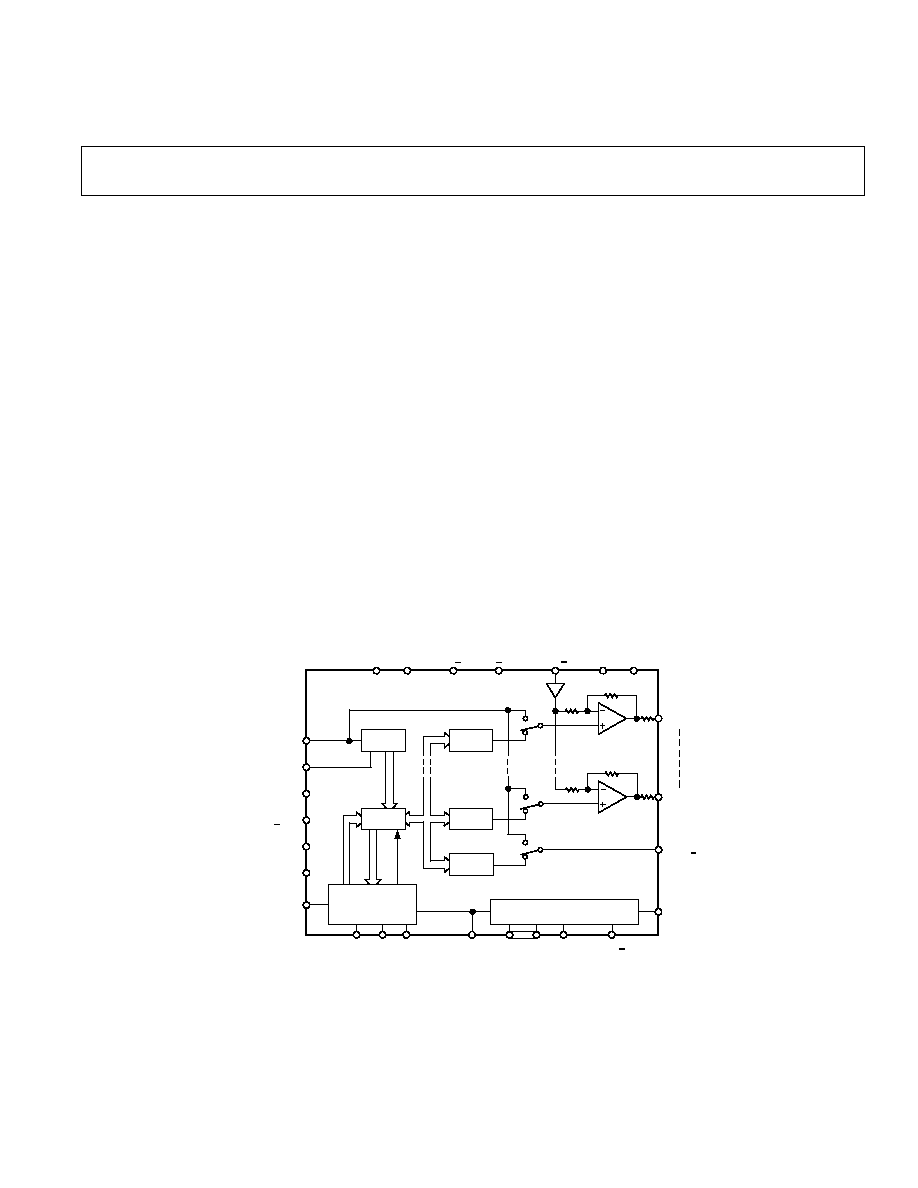

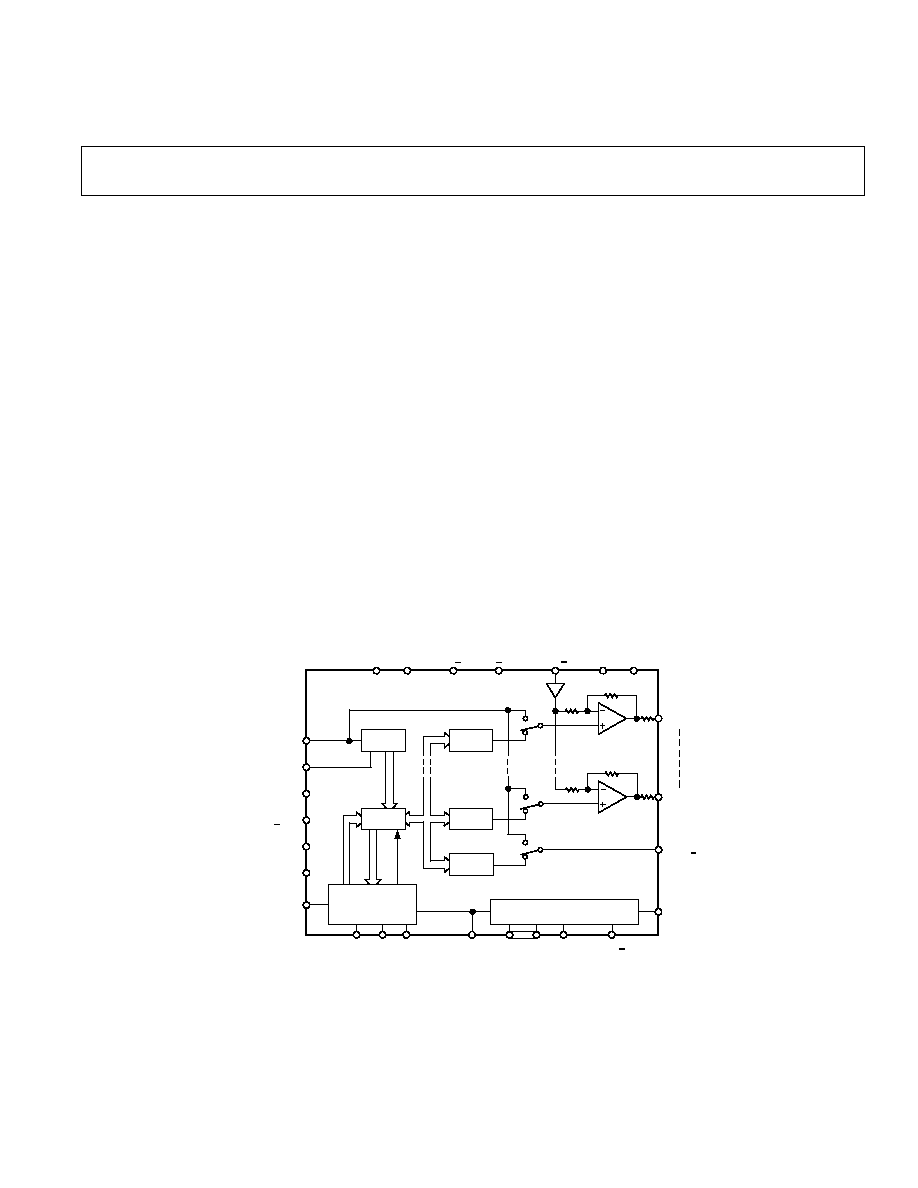

FUNCTIONAL BLOCK DIAGRAM

SYNC / CS

WR

CAL

A4 A0

SCLK

OFFSET SEL

AD5532

DV

CC

V

IN

D

IN

D

OUT

ADDRESS INPUT REGISTER

AV

CC

REF IN

REF OUT

OFFS IN

INTERFACE

CONTROL

LOGIC

OFFS OUT

V

OUT

31

V

OUT

0

TRACK / RESET

BUSY

DAC GND

AGND

DGND

SER /

PAR

V

DD

V

SS

DAC

DAC

ADC

MUX

DAC

MODE

14-BIT BUS

GENERAL DESCRIPTION

The AD5532 is a 32-channel voltage-output 14-bit DAC with

an additional infinite sample-and-hold mode. The selected DAC

register is written to via the 3-wire serial interface and V

OUT

for this DAC is then updated to reflect the new contents of the

DAC register. DAC selection is accomplished via address bits

A0A4. The output voltage range is determined by the offset

voltage at the OFFS_IN pin and the gain of the output amplifier.

It is restricted to a range from V

SS

+ 2 V to V

DD

2 V because

of the headroom of the output amplifier.

The device is operated with AV

CC

= 5 V

± 5%, DV

CC

= 2.7 V

to 5.25 V, V

SS

= 4.75 V to 16.5 V and V

DD

= 8 V to 16.5 V

and requires a stable +3 V reference on REF_IN as well as an

offset voltage on OFFS_IN.

PRODUCT HIGHLIGHTS

1. 32-channel, 14-bit DAC in one package, guaranteed

monotonic.

2. The AD5532 is available in a 74-lead LFBGA package with

a body size of 12 mm

× 12 mm.

3. Droopless/Infinite Sample-and-Hold Mode.

FEATURES

High Integration: 32-Channel DAC in 12 12 mm

2

LFBGA

Adjustable Voltage Output Range

Guaranteed Monotonic

Readback Capability

DSP-/Microcontroller-Compatible Serial Interface

Output Impedance

0.5 (AD5532-1, AD5532-2)

500 (AD5532-3)

1 k (AD5532-5)

Output Voltage Span

10 V (AD5532-1, AD5532-3, AD5532-5)

20 V (AD5532-2)

Infinite Sample-and-Hold Capability to 0.018% Accuracy

Temperature Range 40 C to +85 C

APPLICATIONS

Level Setting

Instrumentation

Automatic Test Equipment

Industrial Control Systems

Data Acquisition

Low Cost I/O

*Protected by U.S. Patent No. 5,969,657; other patents pending.

REV. 0

2

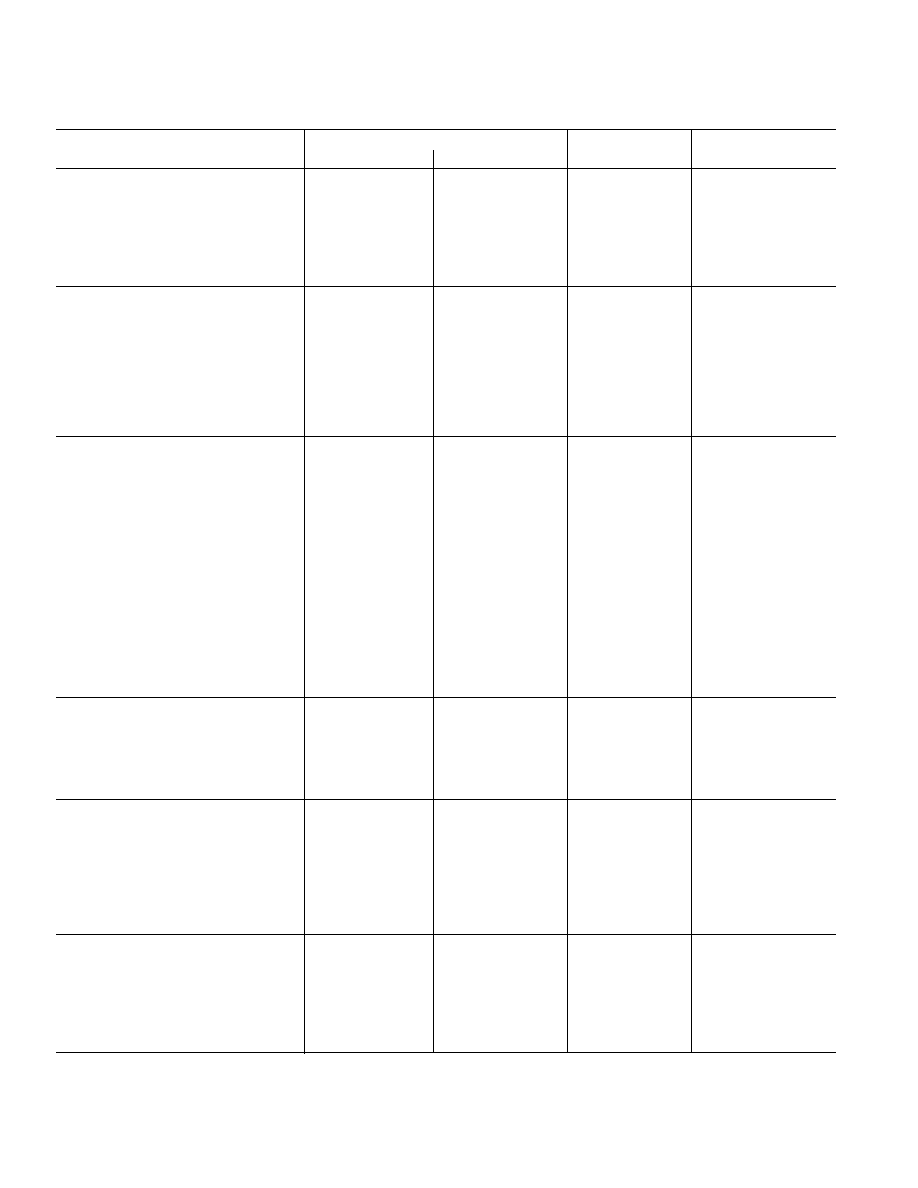

AD5532SPECIFICATIONS

(V

DD

= 8 V to 16.5 V, V

SS

= 4.75 V to 16.5 V; AV

CC

= 4.75 V to 5.25 V; DV

CC

= 2.7 V to

5.25 V; AGND = DGND = DAC_GND = 0 V; REF_IN = 3 V; Output Range from V

SS

+ 2 V to V

DD

2 V. All outputs unloaded. All specifications T

MIN

to T

MAX

unless otherwise noted.)

A Version

2

Conditions/

Parameter

1

AD5532-1/-3/-5

AD5532-2 Only

Unit

Comments

DAC DC PERFORMANCE

Resolution

14

14

Bits

Integral Nonlinearity (INL)

±0.39

±0.39

% of FSR max

± 0.15% typ

Differential Nonlinearity (DNL)

±1

±1

LSB max

± 0.5% typ, Monotonic

Offset

90/170/250

180/350/500

mV min/typ/max

See Figure 6

Gain

3.52

7

typ

Full-Scale Error

±2

±2

% of FSR max

VOLTAGE REFERENCE

REF_IN

Nominal Input Voltage

3.0

3.0

V

Input Voltage Range

3

2.85/3.15

2.85/3.15

V min/max

Input Current

1

1

µA max

< 1 nA typ

REF_OUT

Output Voltage

3

3

V typ

Output Impedance

3

280

280

k

typ

Reference Temperature Coefficient

3

60

60

ppm/

°C typ

ANALOG OUTPUTS (V

OUT

031)

Output Temperature Coefficient

3, 4

20

20

ppm/

°C typ

DC Output Impedance

3

AD5532-1

0.5

0.5

typ

AD5532-3

500

typ

AD5532-5

1

k

typ

Output Range

V

SS

+ 2/V

DD

2

V

SS

+ 2 /V

DD

2

V min/max

100

µA Output Load

Resistive Load

3, 5

5

5

k

min

Capacitive Load

3, 5

AD5532-1

500

500

pF max

AD5532-3

15

nF max

AD5532-5

40

nF max

Short-Circuit Current

3

10

10

mA typ

DC Power-Supply Rejection Ratio

3

70

70

dB typ

V

DD

= +15 V

± 5%

70

70

dB typ

V

SS

= 15 V

± 5%

DC Crosstalk

3

250

250

µV max

ANALOG OUTPUT (OFFS_OUT)

Output Temperature Coefficient

3, 4

20

20

ppm/

°C typ

DC Output Impedance

3

1.3

1.3

k

typ

Output Range

50 to REF_IN12

50 to REF_IN12

mV typ

Output Current

10

10

µA max

Source Current

Capacitive Load

100

100

pF max

DIGITAL INPUTS

3

Input Current

±10

±10

µA max

± 5 µA typ

Input Low Voltage

0.8

0.8

V max

DV

CC

= 5 V

± 5%

0.4

0.4

V max

DV

CC

= 3 V

± 10%

Input High Voltage

2.4

2.4

V min

DV

CC

= 5 V

± 5%

2.0

2.0

V min

DV

CC

= 3 V

± 10%

Input Hysteresis (

SCLK and CS Only)

200

200

mV typ

Input Capacitance

10

10

pF max

DIGITAL OUTPUTS (

BUSY, D

OUT

)

3

Output Low Voltage, DV

CC

= 5 V

0.4

0.4

V max

Sinking 200

µA

Output High Voltage, DV

CC

= 5 V

4.0

4.0

V min

Sourcing 200

µA

Output Low Voltage, DV

CC

= 3 V

0.4

0.4

V max

Sinking 200

µA

Output High Voltage, DV

CC

= 3 V

2.4

2.4

V min

Sourcing 200

µA

High Impedance Leakage Current

±1

±1

µA max

D

OUT

Only

High Impedance Output Capacitance

15

15

pF typ

D

OUT

Only

REV. 0

3

AD5532

A Version

2

Conditions/

Parameter

1

AD5532-1/-3/-5

AD5532-2 Only

Unit

Comments

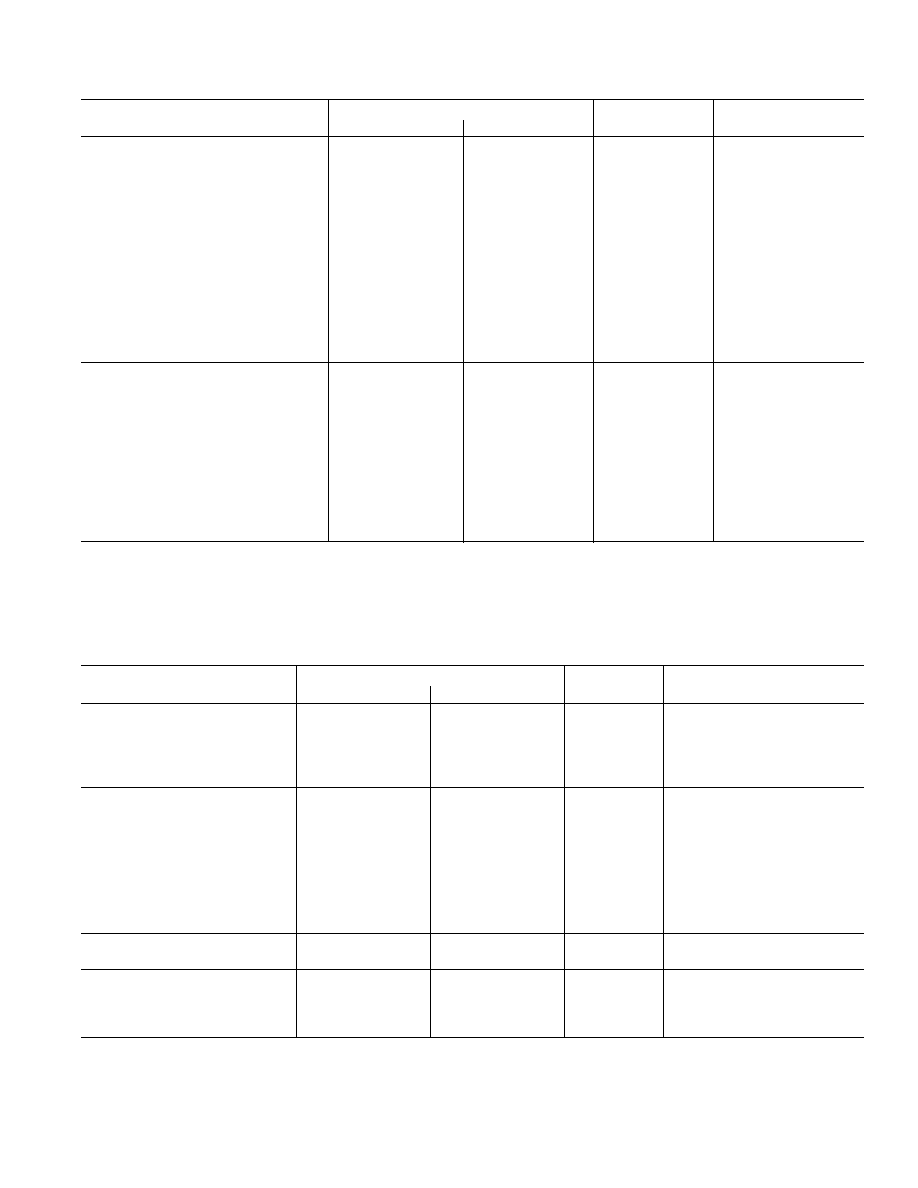

POWER REQUIREMENTS

Power-Supply Voltages

V

DD

8/16.5

8/16.5

V min/max

V

SS

4.75/16.5

4.75/16.5

V min/max

AV

CC

4.75/5.25

4.75/5.25

V min/max

DV

CC

2.7/5.25

2.7/5.25

V min/max

Power-Supply Currents

6

I

DD

15

15

mA max

10 mA typ.

All Channels Full-Scale

I

SS

15

15

mA max

10 mA typ.

All Channels Full-Scale

AICC

33

33

mA max

26 mA typ

DICC

1.5

1.5

mA max

1 mA typ

Power Dissipation

6

280

280

mW typ

V

DD

= 10 V, V

SS

= 5 V

AC CHARACTERISTICS

3

Output Voltage Settling Time

22

30

µs max

500 pF, 5 k

Load

Full-Scale Change

OFFS_IN Settling Time

10

20

µs max

500 pF, 5 k

Load;

0 V3 V Step

Digital-to-Analog Glitch Impulse

1

1

nV-s typ

1 LSB Change Around

Major Carry

Digital Crosstalk

5

5

nV-s typ

Analog Crosstalk

1

1

nV-s typ

Digital Feedthrough

0.2

0.2

nV-s typ

Output Noise Spectral Density @ 1 kHz

400

400

nV/(

Hz)

typ

NOTES

1

See Terminology.

2

A Version: Industrial temperature range 40

°C to +85°C; typical at +25°C.

3

Guaranteed by design and characterization, not production tested.

4

AD780 as reference for the AD5532.

SHA MODE

A Version

2

Conditions/

Parameter

1

AD5532-1/-3/-5

AD5532-2 Only

Unit

Comments

ANALOG CHANNEL

V

IN

to V

OUT

Nonlinearity

3

±0.018

±0.018

% max

±0.006% typ after Offset and

Gain Adjustment

Offset Error

±50

±100

mV max

±10 mV typ. See Figure 7

Gain

3.46/3.52/3.6

6.88/7/7.12

min/typ/max

See Figure 7

ANALOG INPUT (V

IN

)

Input Voltage Range

0 to 3

0 to 3

V

Nominal Input Range

Input Lower Deadband

70

70

mV max

50 mV typ. Referred to V

IN

.

See Figure 7

Input Upper Deadband

40

40

mV max

12 mV typ. Referred to V

IN

.

See Figure 7

Input Current

1

1

µA max

100 nA typ.

V

IN

Acquired on 1 Channel

Input Capacitance

4

20

20

pF typ

ANALOG INPUT (OFFS_IN)

Input Current

1

1

µA max

100 nA typ

AC CHARACTERISTICS

Output Settling Time

4

3

3

µs max

Output Unloaded

Acquisition Time

16

16

µs max

AC Crosstalk

4

5

5

nV-s typ

NOTES

1

S

ee Terminology.

2

A version: Industrial temperature range 40

°C to +85°C; typical at +25°C.

3

Input range 100 mV to 2.96 V.

4

Guaranteed by design and characterization, not production tested.

Specifications subject to change

without notice.

5

Ensure that you do not exceed T

J

(max). See Maximum Ratings.

6

Output unloaded.

Specifications subject to change without noti

ce.

REV. 0

AD5532

4

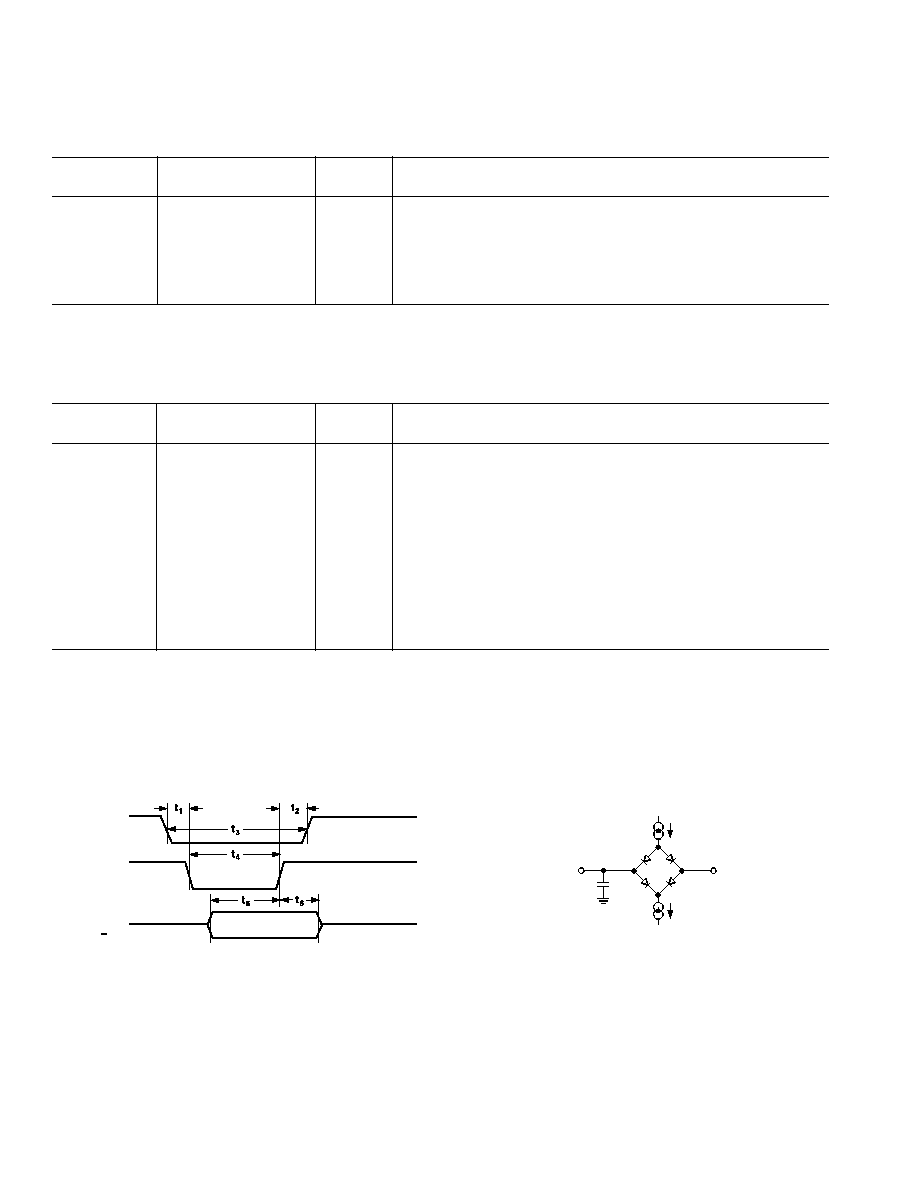

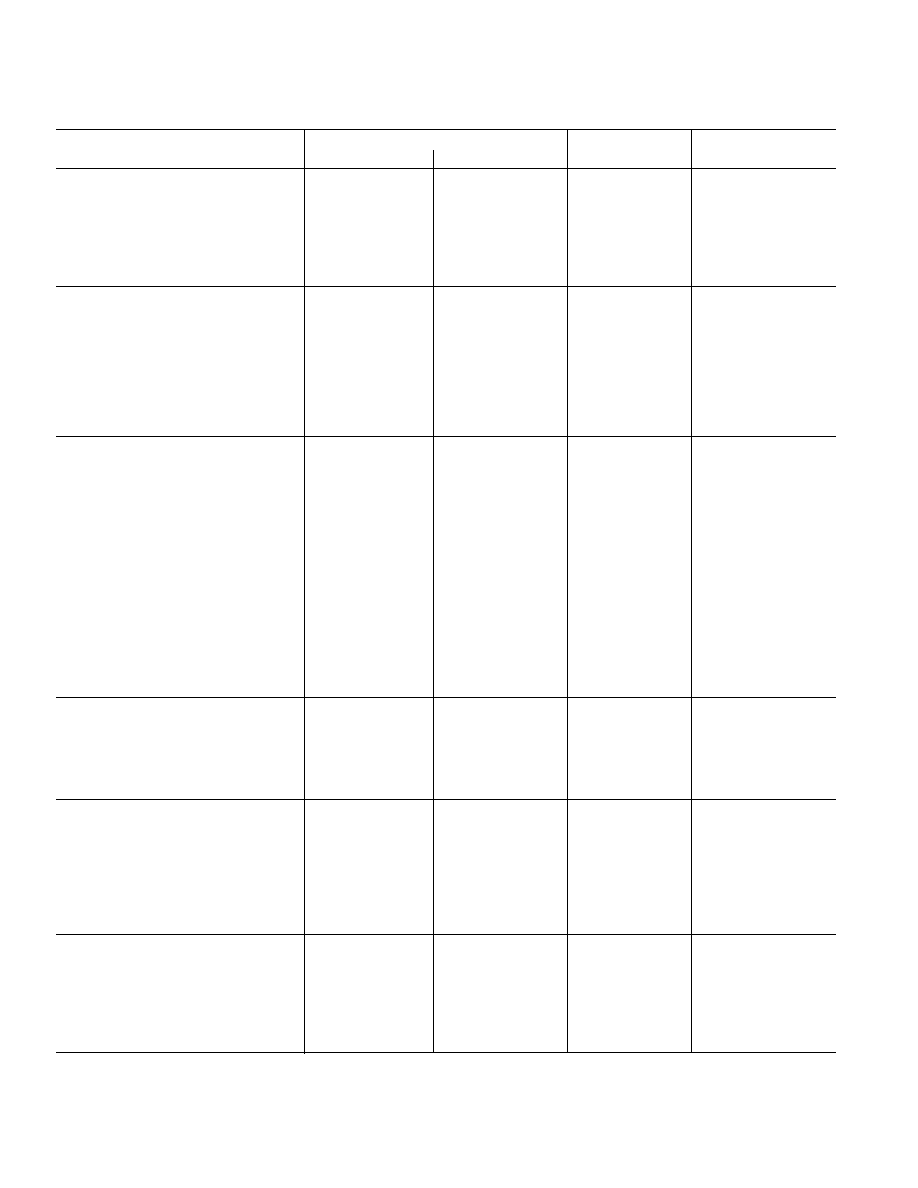

TIMING CHARACTERISTICS

PARALLEL INTERFACE

Limit at T

MIN

, T

MAX

Parameter

1, 2

(A Version)

Unit

Conditions/Comments

t

1

0

ns min

CS to WR Setup Time

t

2

0

ns min

CS to WR Hold Time

t

3

50

ns min

CS Pulsewidth Low

t

4

50

ns min

WR Pulsewidth Low

t

5

20

ns min

A4A0, CAL, OFFS_SEL to

WR Setup Time

t

6

0

ns min

A4A0, CAL, OFFS_SEL to

WR Hold Time

NOTES

1

See Interface Timing Diagram.

2

Guaranteed by design and characterization, not production tested.

Specifications subject to change without notice.

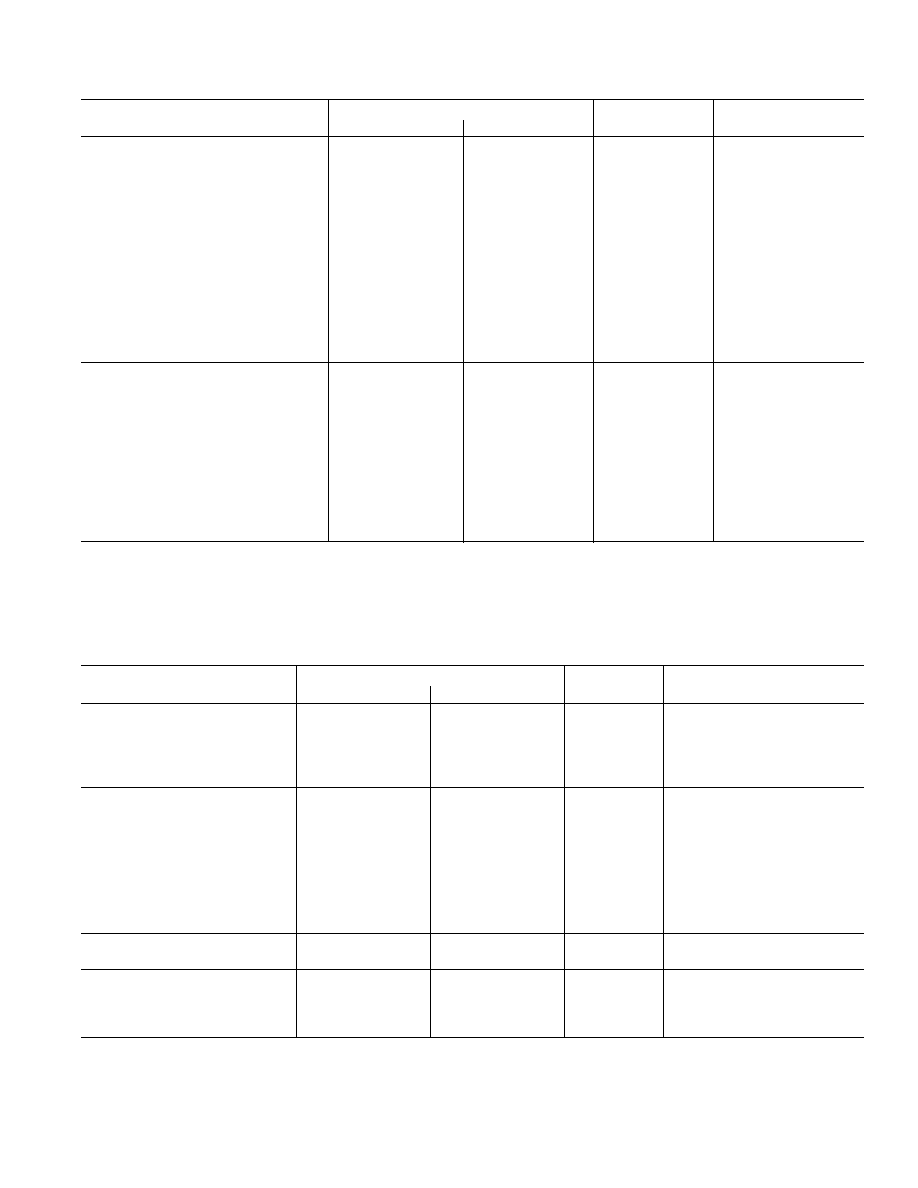

SERIAL INTERFACE

Limit at T

MIN

, T

MAX

Parameter

1, 2

(A Version)

Unit

Conditions/Comments

f

CLKIN

3

14

MHz max

SCLK Frequency

t

1

28

ns min

SCLK High Pulsewidth

t

2

28

ns min

SCLK Low Pulsewidth

t

3

10

ns min

SYNC Falling Edge to SCLK Falling Edge Setup Time

t

4

50

ns min

SYNC Low Time

t

5

10

ns min

D

IN

Setup Time

t

6

5

ns min

D

IN

Hold Time

t

7

5

ns min

SYNC Falling Edge to SCLK Rising Edge Setup Time

t

8

4

20

ns max

SCLK Rising Edge to D

OUT

Valid

t

9

4

60

ns max

SCLK Falling Edge to D

OUT

High Impedance

t

10

400

ns min

10th SCLK Falling Edge to

SYNC Falling Edge for Readback

t

11

400

ns min

24th SCLK Falling Edge to

SYNC Falling Edge for DAC Mode Write

NOTES

1

See Serial Interface Timing Diagrams.

2

Guaranteed by design and characterization, not production tested.

3

In SHA mode the maximum SCLK frequency is 20 MHz and the minimum pulsewidth is 20 ns.

4

These numbers are measured with the load circuit of Figure 2.

Specifications subject to change without notice.

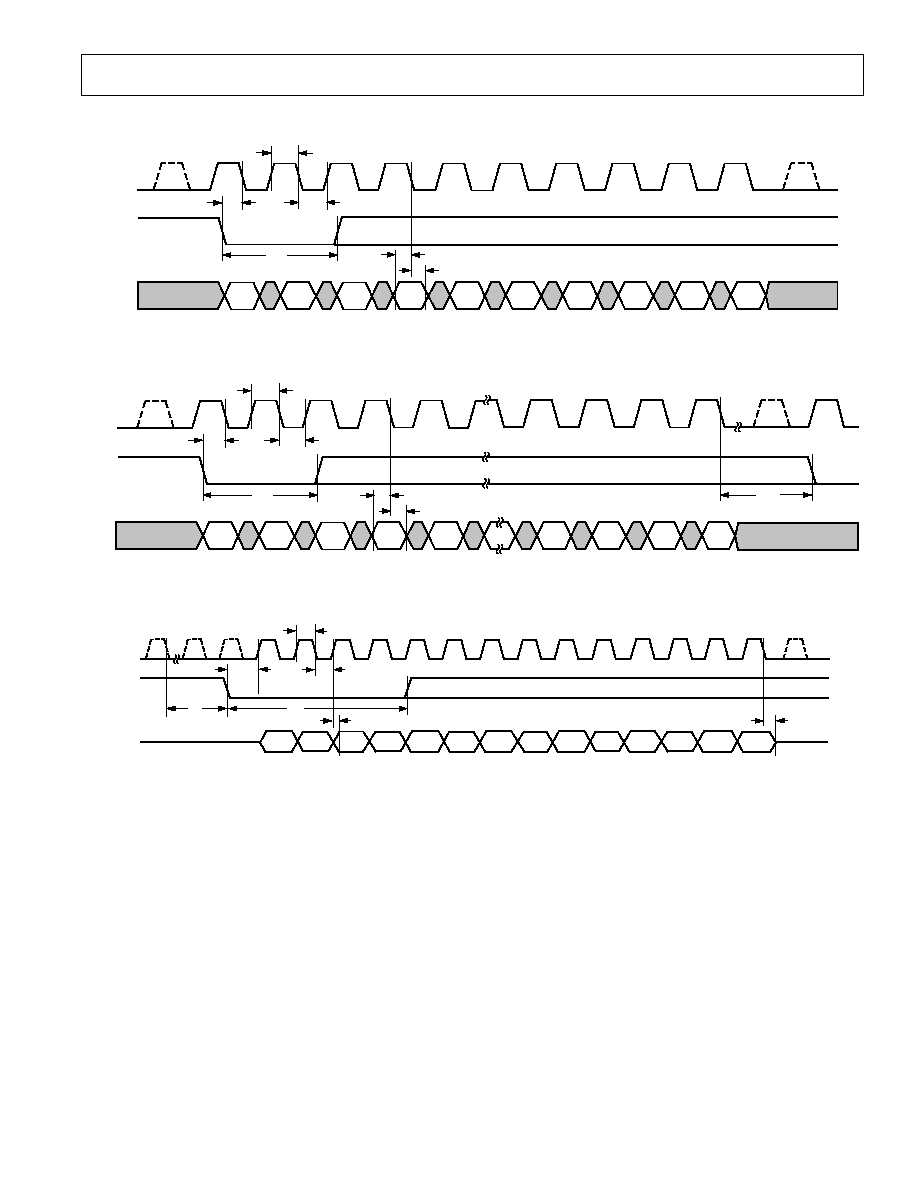

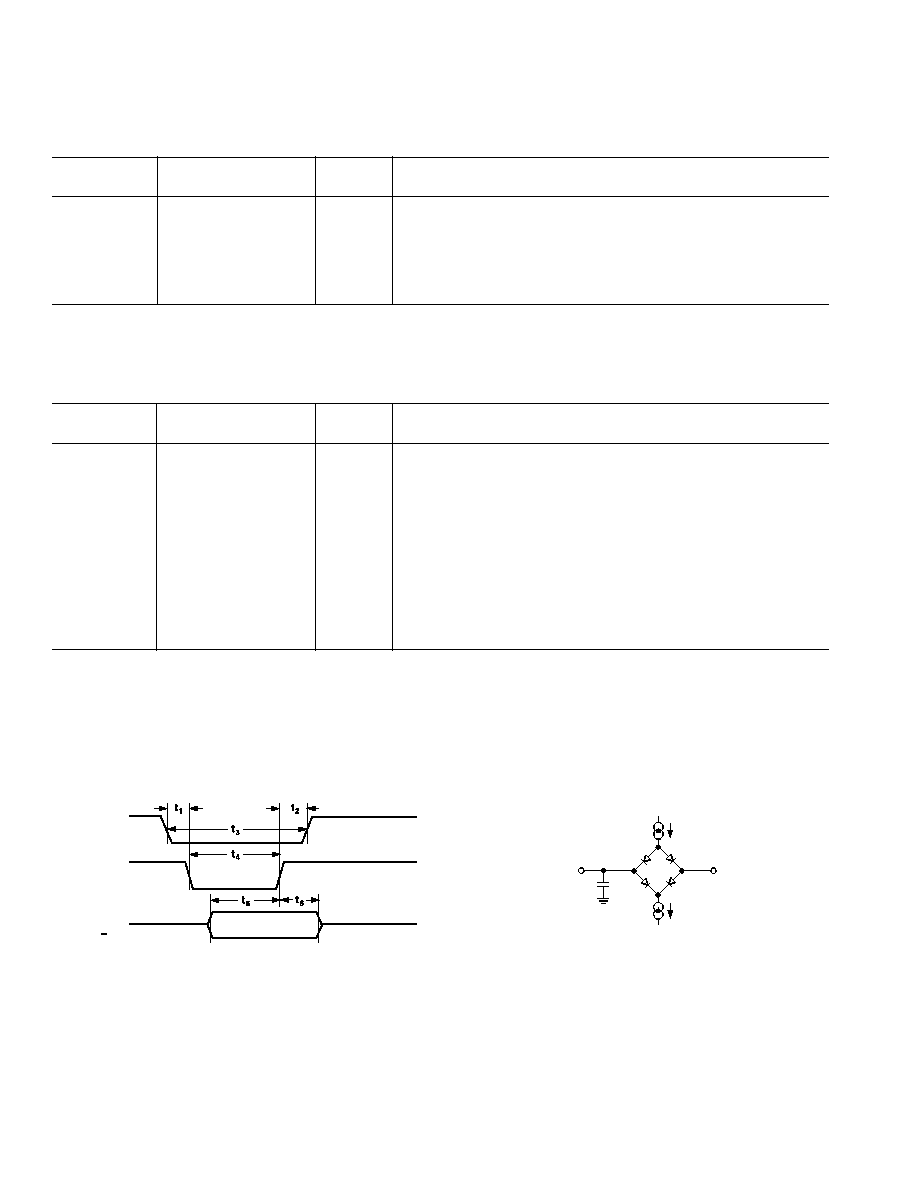

PARALLEL INTERFACE TIMING DIAGRAMS

CS

WR

A4A0, CAL,

OFFS SEL

Figure 1. Parallel Write (SHA Mode Only)

I

OL

200 A

I

OH

200 A

C

L

50pF

TO

OUTPUT

PIN

1.6V

Figure 2. Load Circuit for D

OUT

Timing Specifications

REV. 0

AD5532

5

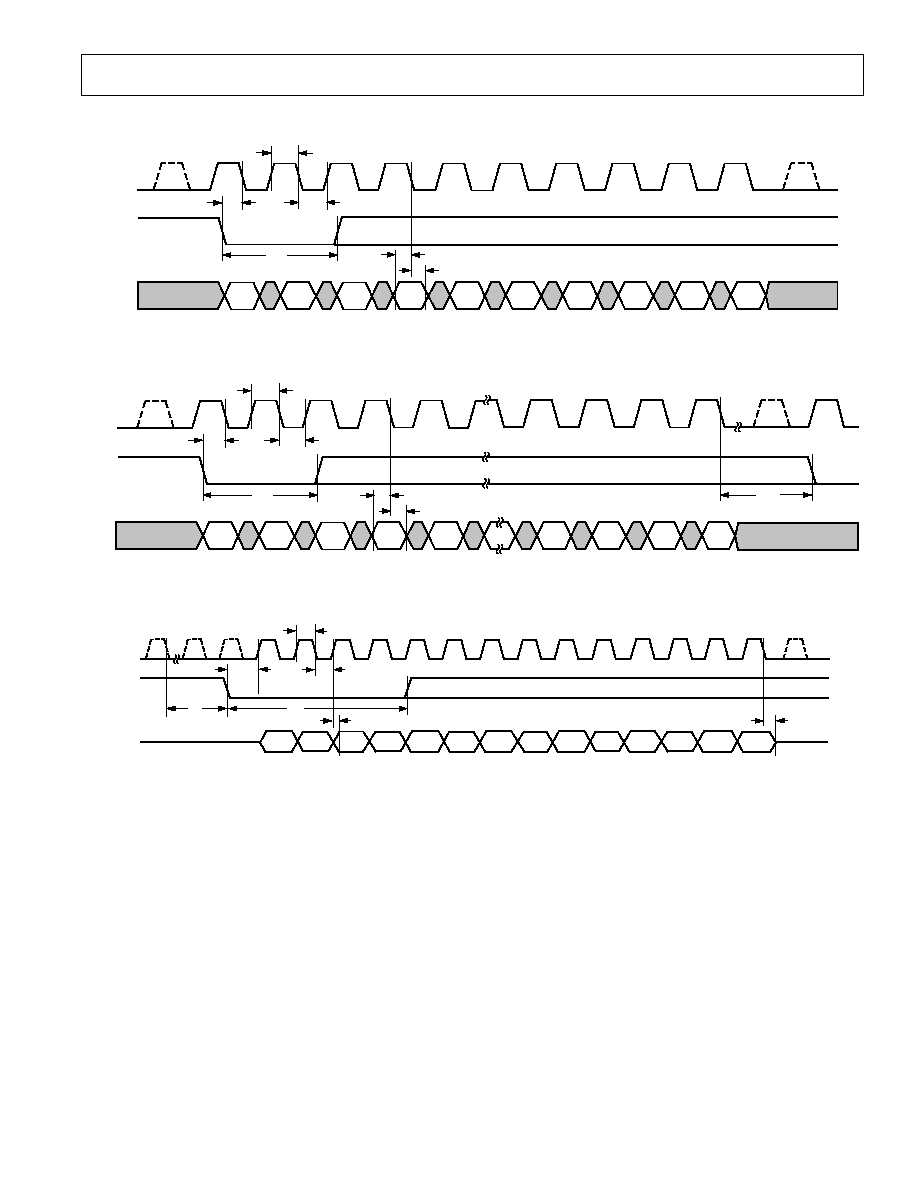

SERIAL INTERFACE TIMING DIAGRAMS

1

2

3

4

5

6

7

8

9

10

t

1

t

2

t

3

t

4

t

5

t

6

MSB

LSB

SCLK

SYNC

D

IN

Figure 3. 10-Bit Write (SHA Mode and Both Readback Modes)

1

2

3

4

5

t

1

t

2

t

3

t

4

LSB

t

5

t

6

21

22

23

24

MSB

SCLK

SYNC

D

IN

t

11

1

Figure 4. 24-Bit Write (DAC Mode)

t

10

2

t

1

t

2

1

3

4

5

6

7

8

9

10

11

12

13

14

t

7

t

4

t

8

t

9

MSB

LSB

SCLK

SYNC

D

OUT

10

Figure 5. 14-Bit Read (Both Readback Modes)