| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AK4340 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

ASAHI KASEI

AKM CONFIDENTIAL [AK4340]

Rev.0.6 2005/11

-

1

-

GENERAL DESCRIPTION

The AK4340 offers the ideal features for consumer systems that require a 2Vrms audio output. Using

AKM's multi bit architecture for its modulator the AK4340 delivers a wide dynamic range while preserving

linearity for improved THD+N performance. The AK4340 integrates the Switched Capacitor Filter (SCF)

increasing performance for systems with excessive clock jitter. The 24 Bit word length and 192kHz

sampling rate make this part ideal for a wide range of applications including Set-top-box, DVD-Audio. The

AK4340 is offered in a space saving 16pin TSSOP package.

FEATURES

Sampling Rate Ranging from 8kHz to 192kHz

128 times Oversampling (Normal Speed Mode)

64 times Oversampling (Double Speed Mode)

32 times Oversampling (Quad Speed Mode)

24-Bit 8 times FIR Digital Filter

Switched Capacitor Filter with High Tolerance to Clock Jitter

On chip Buffer with 2Vrms Single-ended output

Digital De-emphasis Filter: 32kHz, 44.1kHz or 48kHz

Soft Mute Function

Digital Attenuator (Linear 256 Step)

Audio interface format: 24Bit MSB justified, 24/20/16 LSB justified or

I

2

S compatible

Master clock: 256fs, 384fs, 512fs, 768fs or 1152fs (Normal Speed Mode)

128fs, 192fs, 256fs or 512fs (Double Speed Mode)

128fs or 192fs (Quad Speed Mode)

THD+N: -90dB

Dynamic Range: 106dB

Power supply: +4.5V to +5.5V (DAC), - 4.5V to - 13.2V (Output Buffer)

Ta = - 20 to 85

∞

C

Package: 16pin TSSOP (6.4mm x 5.0mm)

192kHz 24-Bit Stereo

DAC with 2Vrms Output

AK4340

= Preliminary =

LRCK

BICK

SDTI

Audio

Data

Interface

MCLK

PDN

Modulator

AOUTL

8X

Interpolator

SCF

LPF

AOUTR

VDD

VSS

De-emphasis

Control

P/S

µP

Interface

Clock

Divider

SMUTE/CSN

ACKS/CCLK

DIF0/CDTI

Modulator

8X

Interpolator

HVEE

SCF

LPF

ATT

ATT

GAIN

ASAHI KASEI

AKM CONFIDENTIAL [AK4340]

Rev.0.6 2005/11

-

2

-

Ordering Guide

AK4340ET -20

+85∞C 16pin TSSOP (0.65mm pitch)

AKD4340

Evaluation

board

for

AK4340

Pin Layout

1

MCLK

LRCK

BICK

SMUTE/CSN

ACKS/CCLK

DIF0/CDTI

Top

View

2

3

4

5

6

7

8

GAIN

TEST

VSS

VDD

HVEE

AOUTL

AOUTR

P/S

16

15

14

13

12

11

10

9

PDN

SDTI

ASAHI KASEI

AKM CONFIDENTIAL [AK4340]

Rev.0.6 2005/11

-

3

-

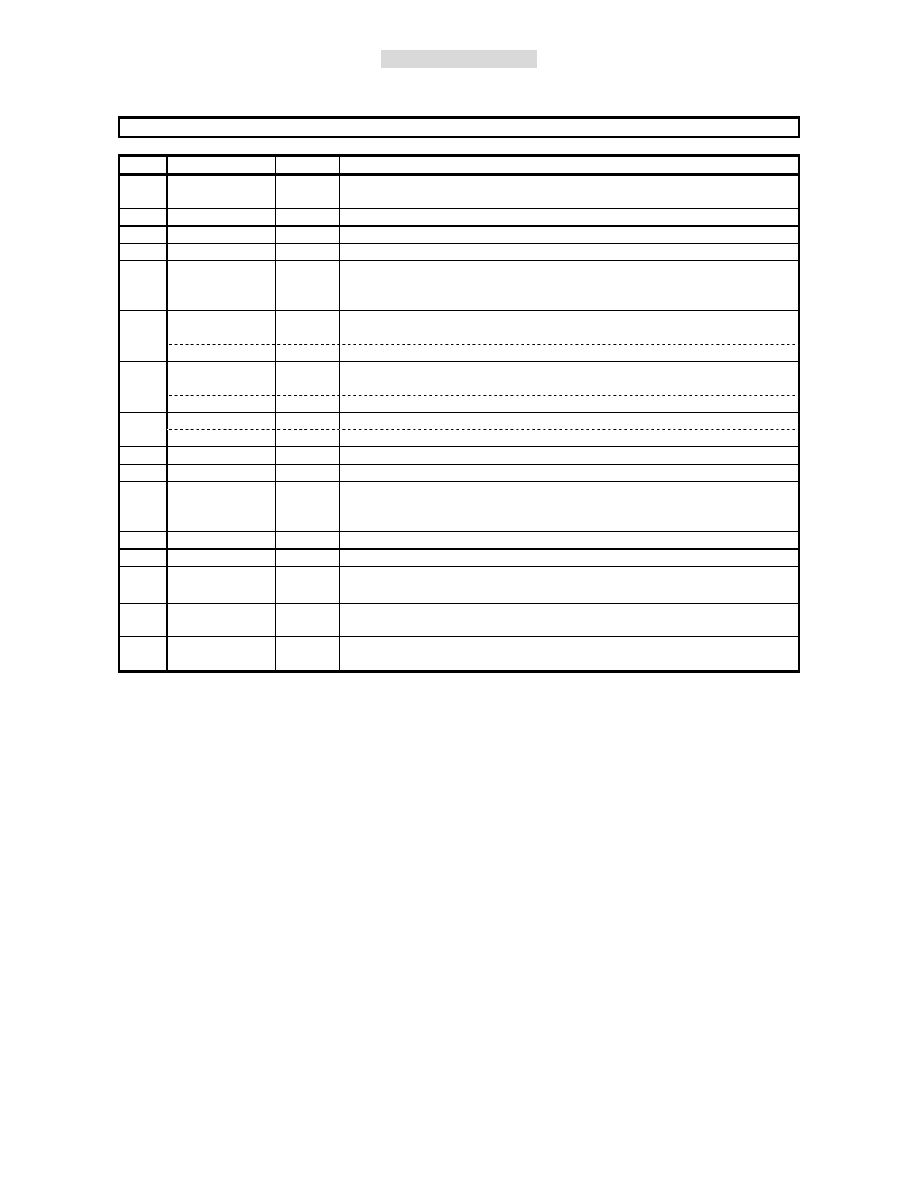

PIN / FUNCTION

No. Pin

Name

I/O Function

1 MCLK

I

Master Clock Input Pin

An external TTL clock should be input on this pin.

2

BICK

I

Audio Serial Data Clock Pin

3

SDTI

I

Audio Serial Data Input Pin

4 LRCK

I L/R

Clock

Pin

5 PDN

I

Power-Down Mode Pin

When at "L", the AK4340 is in the power-down mode and is held in reset. The

AK4340 must be reset once upon power-up.

SMUTE I

Soft Mute Pin in parallel control mode

"H": Enable, "L": Disable

6

CSN

I

Chip Select Pin in serial control mode

ACKS I

Auto Setting Mode Pin in parallel control mode

"L": Manual Setting Mode, "H": Auto Setting Mode

7

CCLK

I

Control Data Clock Pin in serial control mode

DIF0 I

Audio Data Interface Format Pin in parallel control mode

8

CDTI

I

Control Data Input Pin in serial control mode

9

AOUTR

O

Rch Analog Output Pin

10

AOUTL

O

Lch Analog Output Pin

11 HVEE

-

Output Buffer Negative Power Supply Pin

Normally connected to VSS with a 0.1

µF ceramic capacitor in parallel with a

10

µF electrolytic cap.

12 VSS

- Ground

Pin

13

VDD

-

DAC Power Supply Pin

14 P/S

I Parallel/Serial Select Pin (Internal pull-up pin)

"L": Serial control mode, "H": Parallel control mode

15 TEST

I

TEST pin

This pin should be connected to VDD.

16 GAIN

I

Output Gain Select Pin

"L": 0dB, "H": +1.94dB

Note: Do not allow digital input pins except pull-up pin to float.

ASAHI KASEI

AKM CONFIDENTIAL [AK4340]

Rev.0.6 2005/11

-

4

-

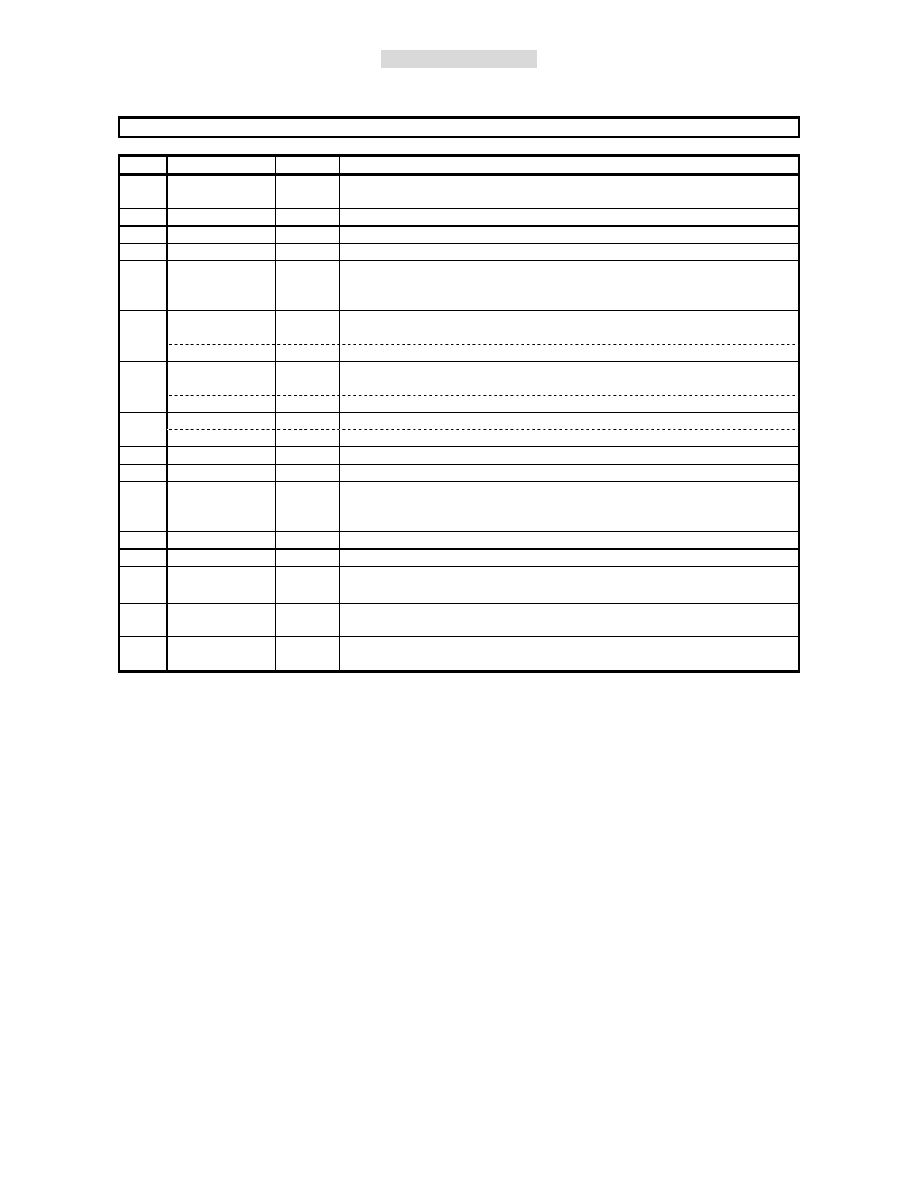

ABSOLUTE MAXIMUM RATINGS

(VSS=0V; Note 1)

Parameter Symbol

min

max

Units

Power Supply

DAC

Output Buffer

VDD

HVEE

-0.3

TBD

+6.0

TBD

V

V

Input Current (any pins except for supplies)

IIN

-

±10

mA

Input Voltage

VIND

-0.3

VDD+0.3

V

Ambient Operating Temperature

Ta

-20

85

∞C

Storage Temperature

Tstg

-65

150

∞C

Note 1. All voltages with respect to ground.

WARNING: Operation at or beyond these limits may results in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

RECOMMENDED OPERATING CONDITIONS

(VSS=0V; Note 1)

Parameter Symbol

min

typ

max

Units

Power Supply

DAC

Output Buffer

VDD

HVEE

+4.5

-13.2

+5.0

-5.0

+5.5

-4.5

V

V

Note 1. All voltages with respect to ground.

*AKM assumes no responsibility for the usage beyond the conditions in this datasheet.

ASAHI KASEI

AKM CONFIDENTIAL [AK4340]

Rev.0.6 2005/11

-

5

-

ANALOG CHARACTERISTICS

(Ta=25

∞C; VDD=+5.0VV; HVEE=-5.0V; fs=44.1kHz; BICK=64fs; Signal Frequency=1kHz; 24bit Input Data;

Measurement frequency=20Hz

20kHz; R

L

5k; unless otherwise specified)

Parameter min

typ

max

Units

Resolution

24

Bits

Dynamic Characteristics (Note 2)

fs=44.1kHz

BW=20kHz

0dBFS

-60dBFS

-90

-39

TBD

-

dB

dB

fs=96kHz

BW=40kHz

0dBFS

-60dBFS

-90

-36

-

-

dB

dB

THD+N

fs=192kHz

BW=40kHz

0dBFS

-60dBFS

-90

-36

-

-

dB

dB

Dynamic Range (-60dBFS with A-weighted) (Note 3)

TBD

106

dB

S/N (A-weighted) (Note 4)

TBD

106

dB

Interchannel Isolation (1kHz)

TBD

100

dB

Interchannel Gain Mismatch

0.2

0.5

dB

DC Accuracy

Gain Drift

100

-

ppm/

∞C

GAIN pin = "L"

TBD

2

TBD

Vrms

Output Voltage (Note 5)

GAIN pin = "H"

TBD

2.5

TBD

Vrms

Load Capacitance (Note 6)

25

pF

Load Resistance

5

k

Power Supplies

Power Supply Current: (Note 7)

Normal Operation (PDN pin = "H", fs

96kHz)

VDD

HVEE

Normal Operation (PDN pin = "H", fs=192kHz)

VDD

HVEE

Power-Down Mode (PDN pin = "L") (Note 8)

VDD

HVEE

22

8

25

8

10

10

TBD

TBD

TBD

TBD

TBD

TBD

mA

mA

mA

mA

µA

µA

Note 2. Measured by Audio Precision (System Two). GAIN pin = "L". Refer to the evaluation board manual regarding the

measurement results.

Note 3. 98dB at 16bit data

Note 4. S/N ration does not depend on the input data length

Note 5. Full-scale voltage (0dB). Output voltage is proportional to VDD voltage.

AOUT (typ.@ 0dB, GAIN = 0dB) = 2Vrms ◊ VDD/5.

Note 6. When the output pin drives a capacitive load, a resistor should be added in series between output pin and

capacitive load.

Note 7. These values are supplied to VDD pin or HVEE pin.

Note 8. P/S pin is tied to VDD and the other all digital inputs including clock pins (MCLK, BICK and LRCK) are tied to

VDD or VSS.