| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: AK6512CM | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

ASAHI KASEI

[AK6510C/12C]

DAP02E-04

2005/03

- 1 -

AK6510C / 12C

SPI bus 32K/64Kbit Serial CMOS EEPROM

Features

Advanced CMOS EEPROM Technology

Single Voltage Supply: 1.8V to 5.5V

AK6510C: 32Kbits; 4096 x 8 organization

AK6512C: 64Kbits; 8192 x 8 organization

SPI Serial Interface Compatible

Low Power Consumption

0.8

µ

A Max. (Standby mode)

High Reliability

Endurance:

1000K E/W cycles / Address

Data Retention: 10 Years

Special Features

32 byte Page Write Mode

Block Write Protection (Protect 1/4,1/2 or Entire Array)

Automatic write cycle time-out with auto-ERASE

Software and Hardware controlled Write Protection

Self timed Programming Cycle: 5msec. Max.

Ideal for Low Density Data Storage

Low cost, space saving, 8-pin SSOP/SONW package

Block Diagram

DATA

REGISTER

INSTRUCTION

DECODE,

CONTROL

AND

CLOCK

GENERATION

INSTRUCTION

REGISTER

EEPROM

AK6510C=32Kbit

SI

CS

SCK

HOLD

ADD.

BUFFERS

VREF

VPP

GENERATOR

VPP SW

DECODER

R/W AMPS

AND

AUTO ERASE

SO

STATUS REGISTER

WP

AK6512C=64Kbit

ASAHI KASEI

[AK6510C/12C]

DAP02E-04

2005/03

- 2 -

General Description

The AK6510C/12C is a 32768/65536-bit, serial, read/write, non-volatile memory device fabricated

using an advanced CMOS EEPROM technology. The AK6510C/12C has 32768-bits/65536-bits of

memory organized as 4096/8192 registers of 8 bits each. The AK6510C/12C can operate all

function under wide operating voltage range: 1.8V to 5.5V. The charge up circuit for high voltage

generation needed for write operations is integrated.

The AK6510C/12C serial interface is compatible to a SPI bus. The AK6510C/12C has 6

instructions: READ, WRITE, WREN (write enable), WRDI (write disable), RDSR (read status

register), and WRSR (write status register).

Each instruction is organized by an op-code (8bits), address (16bits), and data (8bits). When input

level of CS pin changed from high level to low level, AK6510C/12C can receive instructions.

Pin Configurations

Pin name

Functions

CS Chip

Select

input

SCK

Serial Clock input

SI

Serial Data input

SO

Serial Data output

WP

Write Protect input

HOLD Hold

input

VCC Power

Supply

GND Ground

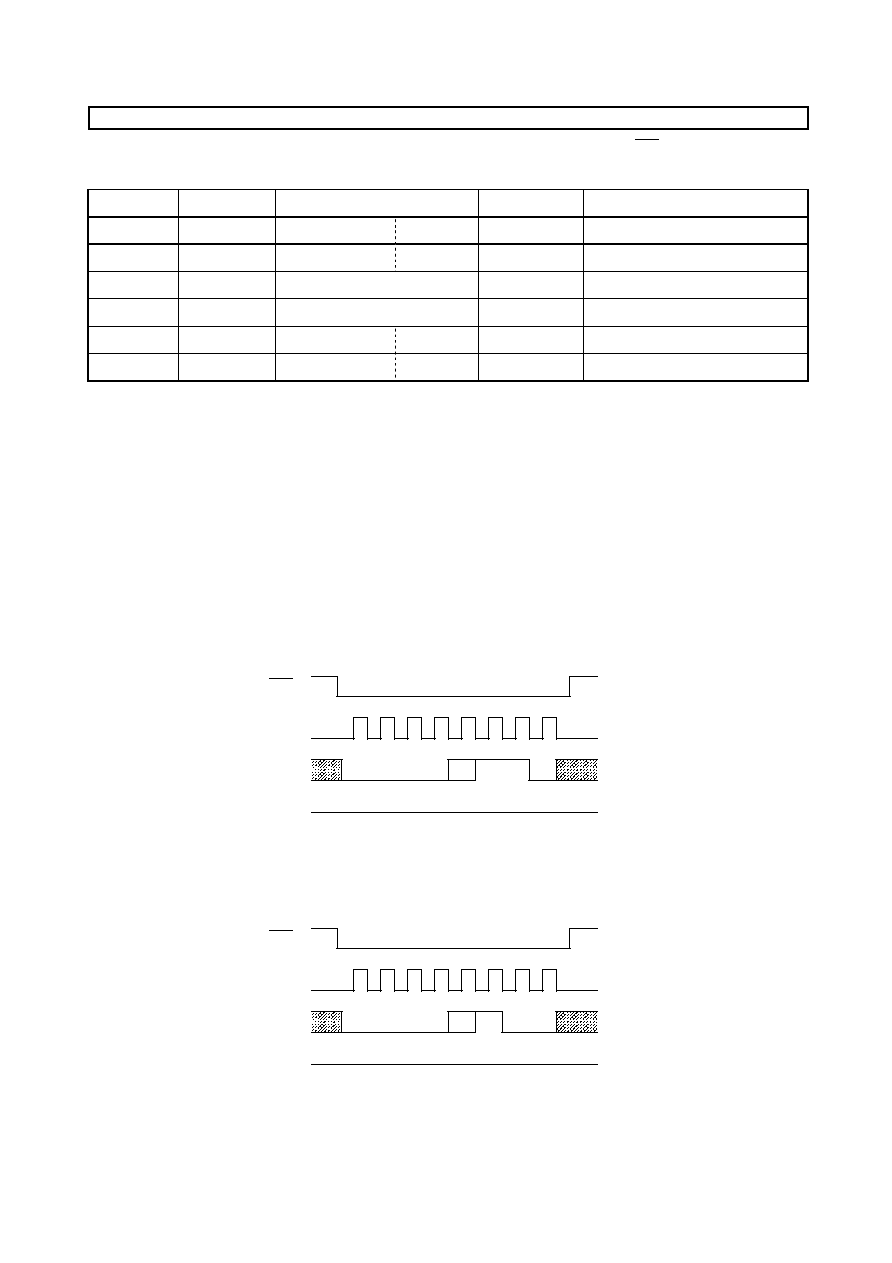

Type of Products

Model

Memory size

Temp. Range

VCC

Package

AK6510CM

-40∞C to +85∞C

1.8V to 5.5V

8pin Plastic SSOP

AK6510CL

32K bits

-40∞C to +85∞C

1.8V to 5.5V

8pin Plastic SONW

AK6512CM

-40∞C to +85∞C

1.8V to 5.5V

8pin Plastic SSOP

AK6512CL

64K bits

-40∞C to +85∞C

1.8V to 5.5V

8pin Plastic SONW

AK6510CL/12CL

8pin SONW

CS

SO

WP

GND

VCC

HOLD

SI

1

2

3

4

8

7

6

5

SCK

8

7

6

5

CS

SO

WP

GND

VCC

SI

1

2

3

4

SCK

AK6510CM/12CM

8pin SSOP

HOLD

ASAHI KASEI

[AK6510C/12C]

DAP02E-04

2005/03

- 3 -

Data Transfer

An IC that outputs the clock is called "MASTER", an IC that receives the clock is called "SLAVE".

The AK6510C/12C operates as a SLAVE. Data is written to the SI pin and read from SO pin. The

MSB is transmitted first.

After CS pin changes hi level to low level, AK6510C/12C receives the first data bit on the SI pin

synchronously with the rising edge of the input pulse of serial clock. While CS pin is high level, the

data input to the SI pin is don't care and SO pin indicates Hi-Z.

All the functions are organized 8 bits of op-code, address, and data. If there is an invalid op-code,

the AK6510C/12C ignores the address and data information and SO pin indicates Hi-Z. In order to

input new op-code, CS pin should be toggled.

Hold

AK6510C/12C has a HOLD pin that can hold the data transfer. When HOLD changes high to low

while SCK is low, the data transfer stops. After the HOLD pin changes low to High while SCK is

low, the data transfer starts again. While the data transfer is paused, AK6510C/12C ignores the

clock on the SCK line.

Write Protect

AK6510C/12C has status registers. When the WPEN bit in the status registers is "1", Write Protect

function is enabled. When WPEN bit is "1" and WP pin is low level, the status register is protected

from write function. When WP pin becomes low level while the WRITE to the status register

instruction is written, the AK6510C/12C doesn't accept the instruction. When the WP pin changes

low level while the internal programming, the programming function continues.

When the WPEN bit is "0", WP pin function is disabled. Even if WP pin is fixed to low level, the

WRITE function to the status register can be done. When the WP pin is high level, AK6510C/12C

can accept all of READ and WRITE functions.

ASAHI KASEI

[AK6510C/12C]

DAP02E-04

2005/03

- 4 -

Pin Description

CS

(Chip Select Input)

When CS changes high level to low level, the AK6510C/12C can receive the instructions.

CS should be kept low level while receiving op-code, address and data, and while outputting

data.

When CS is high level, SO indicate Hi-Z.

SCK

(Serial Clock Input)

The SCK clock pin is the synchronous clock input for input/output data.

SI

(Serial Data Input)

The op-code, address, and data are written to the SI pin.

SO

(Serial Data Output)

The SO pin outputs the data from memory array and status register.

WP

(Write Protect Input)

The WP pin controls the write function to the status register.

When the WPEN bit in the status register is "0", the function of WP pin becomes disable.

Then the status register can be programmable when the WEN bit in the status register is "1".

And it does not depend on the status of WP pin.

When the WPEN bit is "1", the function of WP is enabled. Then the status register can not

be programmable when the WEN bit is "1" and the status of WP pin is low.

When the WPEN bit is "1", WP pin is high and WEN bit is "1", AK6510C/12C can accept the

WRITE instruction to the status registers.

During the instruction input, WP pin should keep high or low level.

HOLD

(Hold Input)

The HOLD pin can hold the data transfer. When the HOLD pin changes hi to low while the

SCK is low, the data transfer is held. And the transfer starts when the HOLD pin changes

low to high while the SCK is low. While the holding the data transfer, AK6510C/12C ignores

the clock signal on SCK pin.

ASAHI KASEI

[AK6510C/12C]

DAP02E-04

2005/03

- 5 -

Function Description

AK6510C/12C has six instructions. The instruction can be input after the CS pin changes high to

low. All the instructions are MSB first.

Instruction

Op-code

Address Data

Description

READ

0000 X011

X X X A12-A8

A7-A0

D7-D0 (out)

Read from Memory Array

WRITE

0000 X010

X X X A12-A8

A7-A0

D7-D0 (in)

Write to Memory Array

WREN

0000 X110

------ ------

Write

Enable

WRDI

0000 X100

------ ------

Write

Disable

RDSR

0000 X101

Bit7-Bit0 (out)

------

------

Read Status Register

WRSR

0000 X001

Bit7-Bit0 (in)

------

------

Write Status Register

X: don't care

AK6510C: A12 is don't care

Table 1. Instruction set for AK6510C/12C

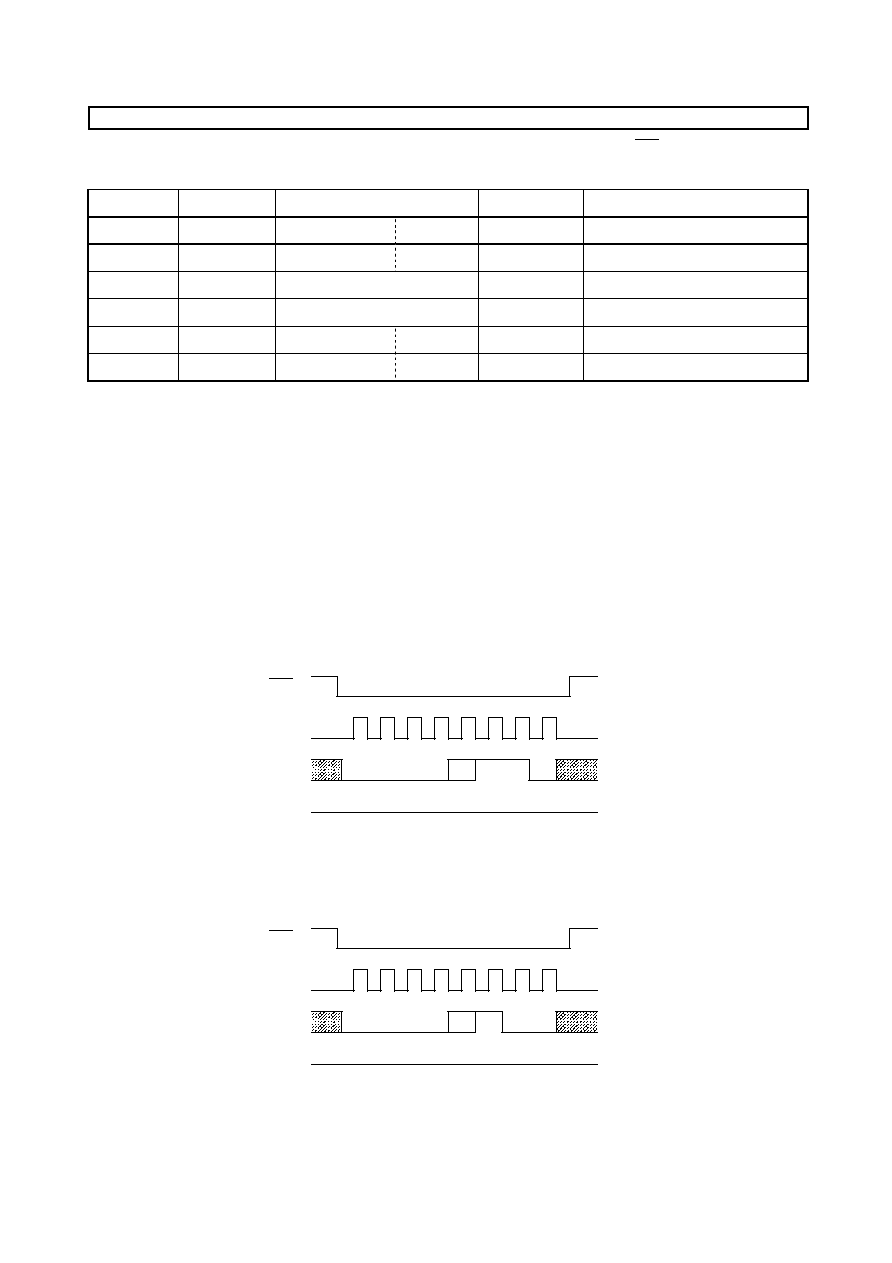

WREN (WRITE ENABLE) / WRDI (WRITE DISABLE)

The WRITE function can be accepted only in the status of Write Enable. After VCC is applied,

AK6510C/12C is in the status of Write Disable. After the function of WRDI, AK6510C/12C cannot

accept any programming function.

WREN

WRDI

0

1

2

3

4

5

6

7

1

X

0

0

0

0

0

0

Hi-Z

CS

SCK

SI

SO

X = don't care

0

1

2

3

4

5

6

7

1

X

0

0

0

0

1

0

Hi-Z

CS

SCK

SI

SO

X = don't care