Äîêóìåíòàöèÿ è îïèñàíèÿ www.docs.chipfind.ru

April 2005

Copyright © Alliance Semiconductor. All rights reserved.

®

AS7C33256NTF18B

4/13/05, v 1.3

Alliance Semiconductor

P. 1 of 18

3.3V 256K x 18 Flowthrough Synchronous SRAM with NTD

TM

Features

· Organization: 262,144 words × 18 bits

· NTD

TM

architecture for efficient bus operation

· Fast clock to data access: 7.5/8.0/10.0 ns

· Fast OE access time: 3.5/4.0 ns

· Fully synchronous operation

· Flow-through mode

· Asynchronous output enable control

· Available in 100-pin TQFP package

· Byte write enables

· Clock enable for operation hold

· Multiple chip enables for easy expansion

· 3.3V core power supply

· 2.5V or 3.3V I/O operation with separate V

DDQ

· Self-timed write cycles

· Interleaved or linear burst modes

· Snooze mode for standby operation

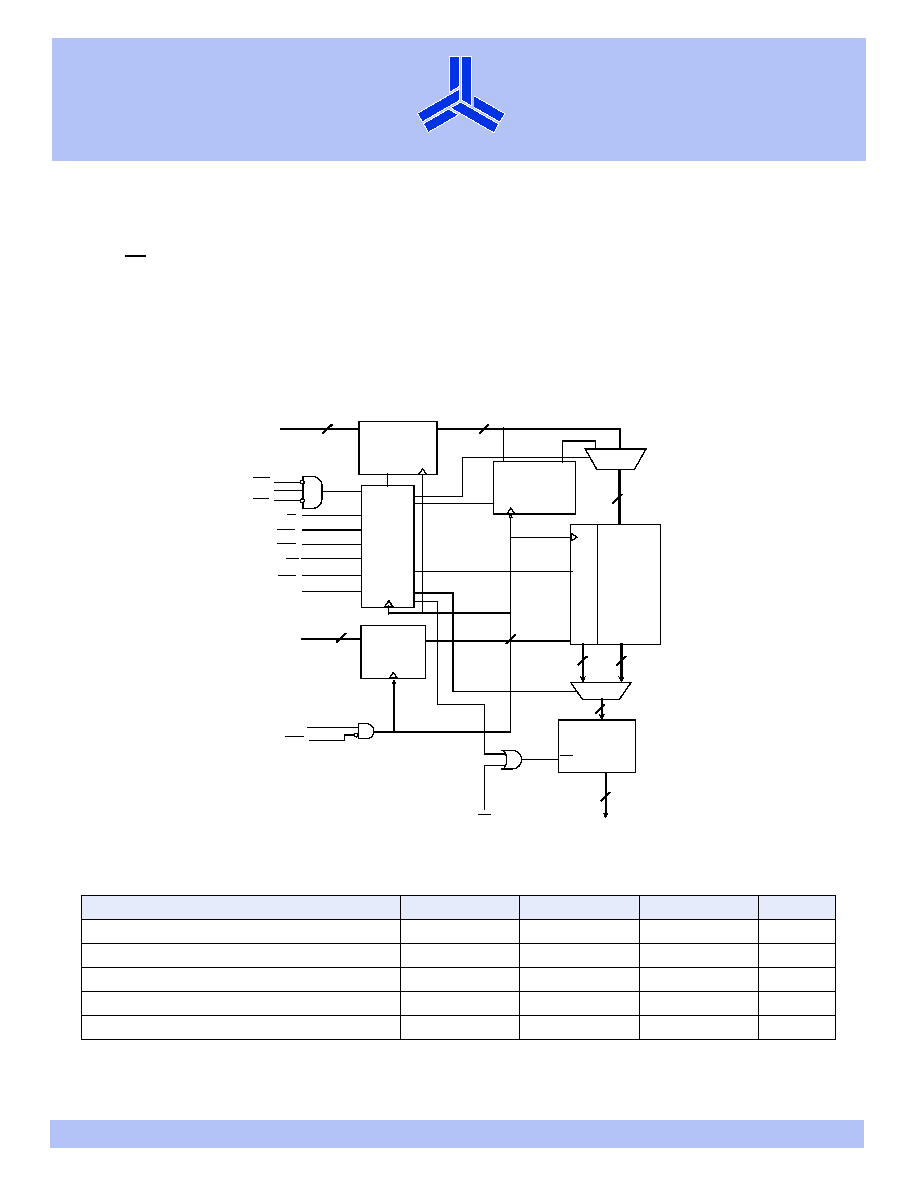

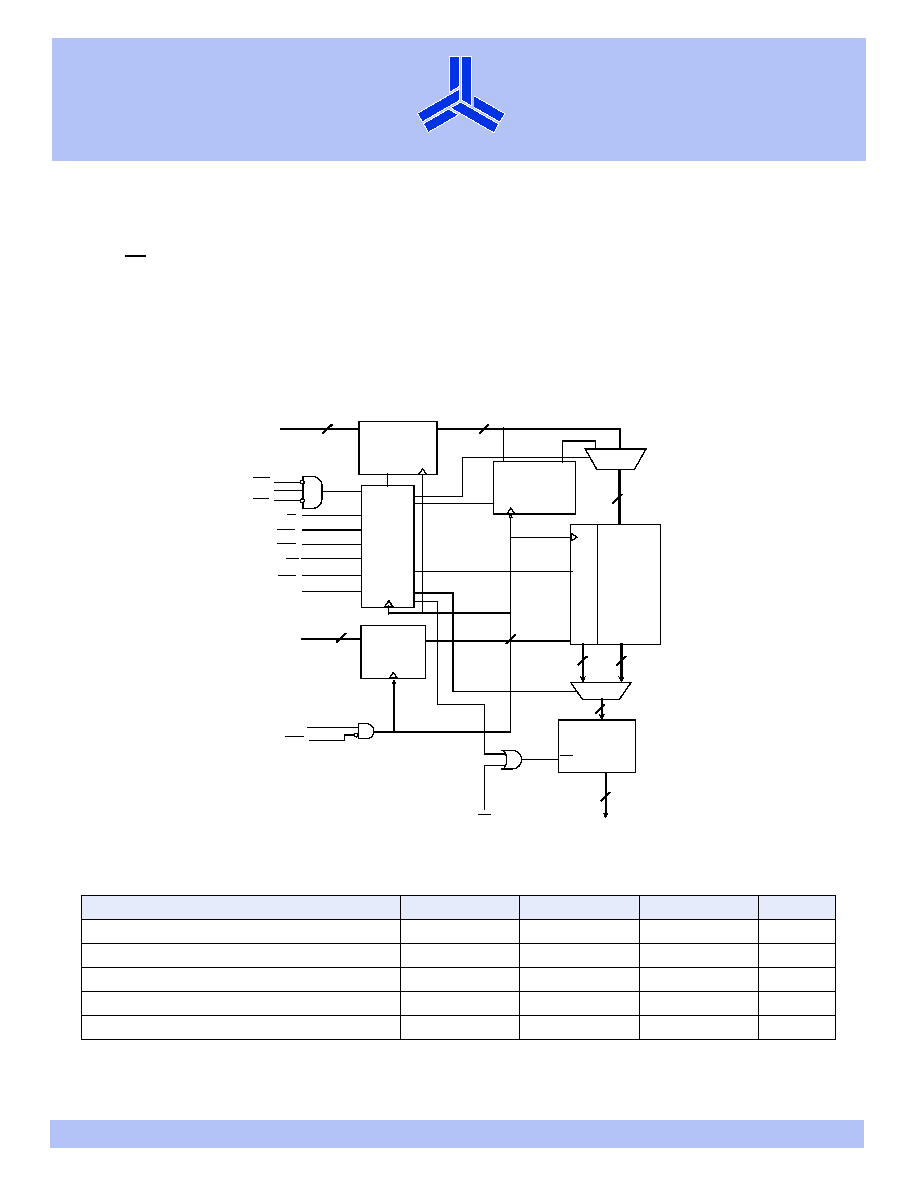

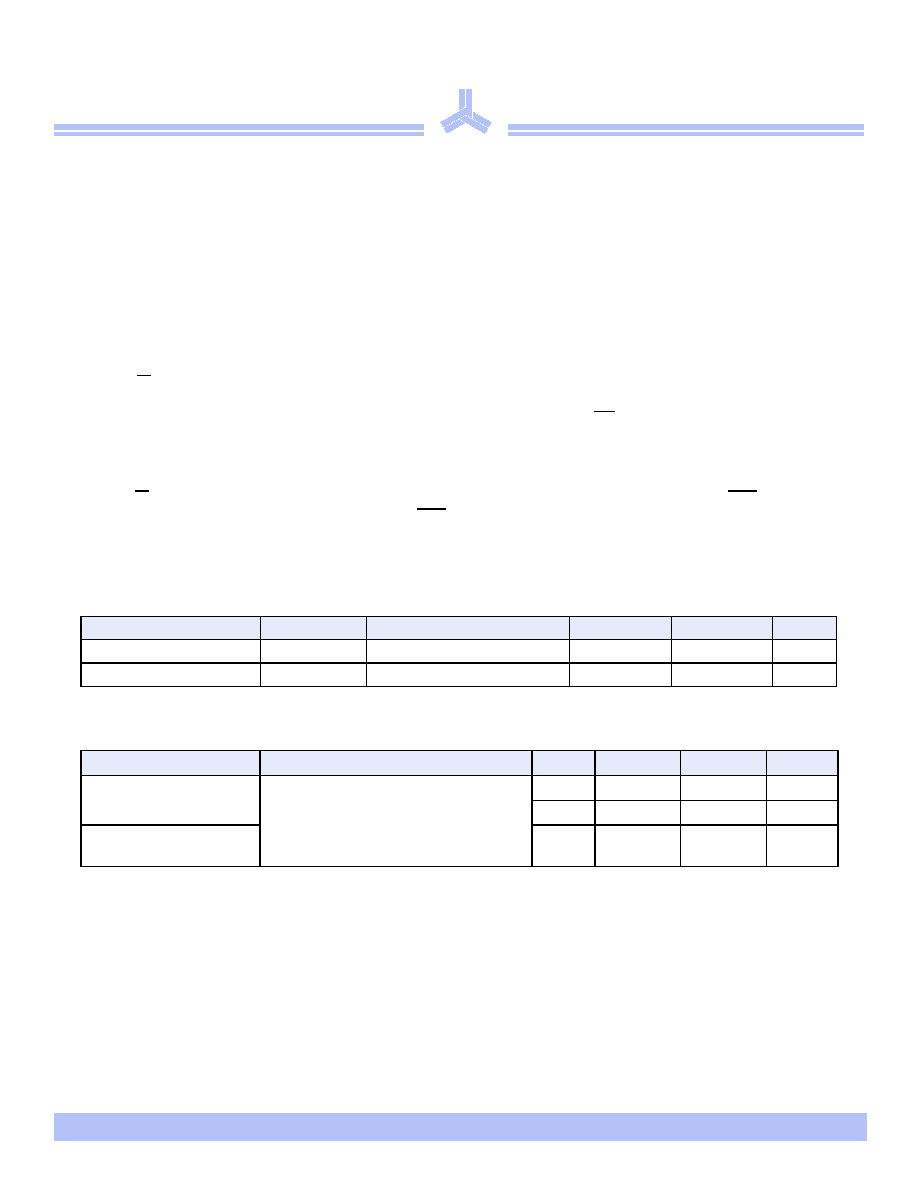

Logic block diagram

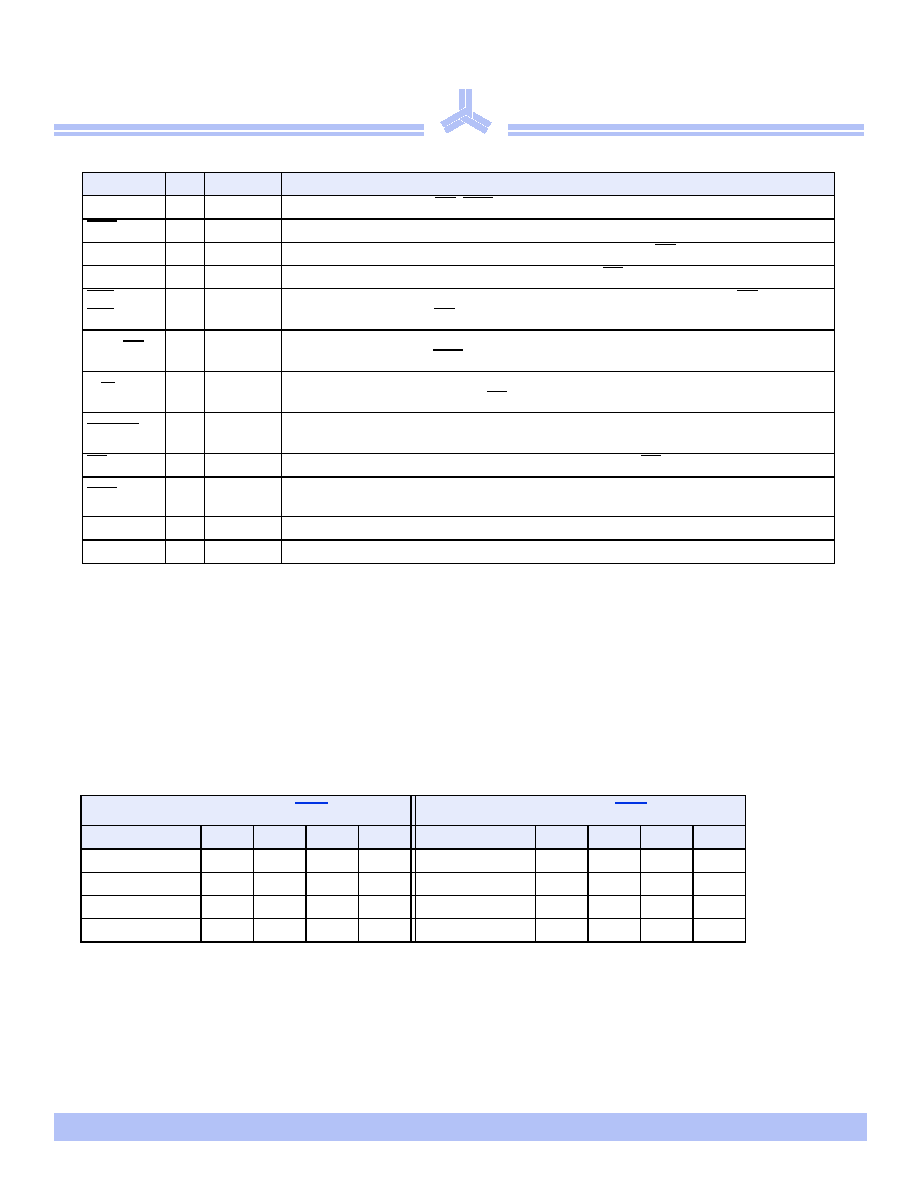

Selection guide

-75

-80

-10

Units

Minimum cycle time

8.5

10

12

ns

Maximum clock access time

7.5

8.0

10

ns

Maximum operating current

260

230

200

mA

Maximum standby current

110

100

90

mA

Maximum CMOS standby current (DC)

30

30

30

mA

W

r

it

e Buf

f

er

Address

D

Q

CLK

register

Output

buffer

DQ [a,b]

18

18

CLK

CE0

CE1

CE2

A[17:0]

OE

CEN

Control

CLK

logic

Data

D

Q

CLK

input

register

18

18

OE

256K x 18

SRAM

array

R/W

DQ [a,b]

BWa

BWb

CLK

Q

D

ADV / LD

LBO

burst logic

addr. registers

Write delay

18

ZZ

CLK

18

18

18

18

®

AS7C33256NTF18B

4/13/05, v 1.3

Alliance Semiconductor

P. 2 of 18

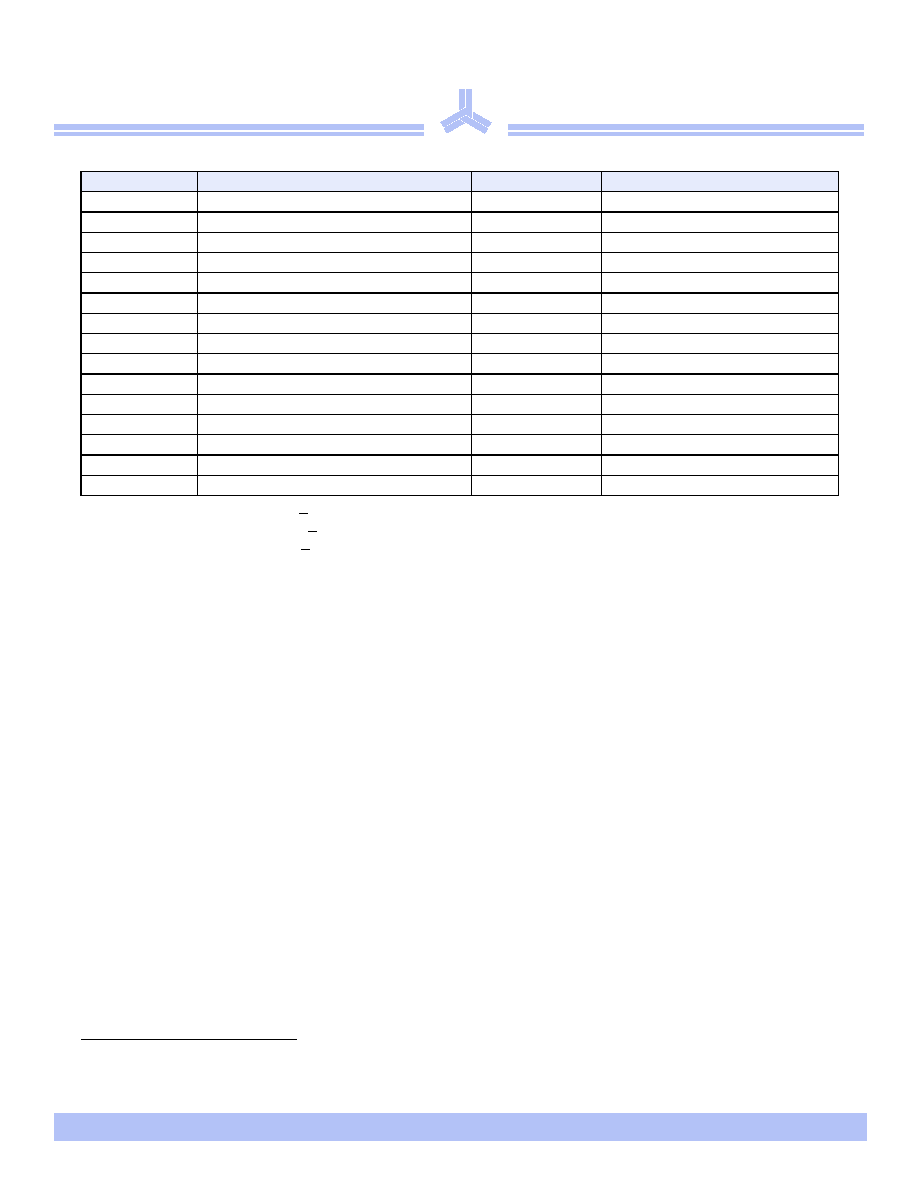

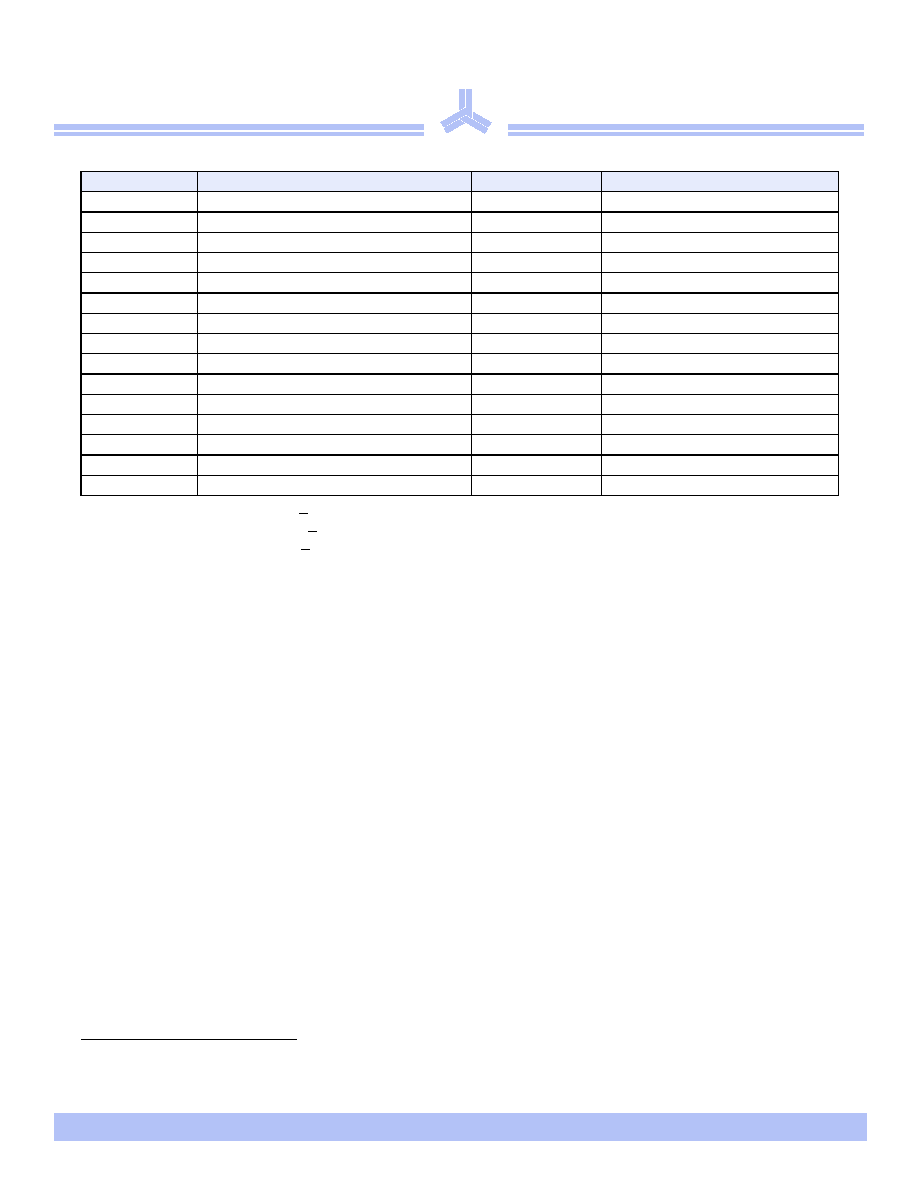

4 Mb Synchronous SRAM products list

1,2

1 Core Power Supply: VDD = 3.3V + 0.165V

2 I/O Supply Voltage: VDDQ = 3.3V + 0.165V for 3.3V I/O

VDDQ = 2.5V + 0.125V for 2.5V I/O

PL-SCD

:

Pipelined Burst Synchronous SRAM - Single Cycle Deselect

PL-DCD

:

Pipelined Burst Synchronous SRAM - Double Cycle Deselect

FT

:

Flow-through Burst Synchronous SRAM

NTD

1

-PL

:

Pipelined Burst Synchronous SRAM with NTD

TM

NTD-FT

:

Flow-through Burst Synchronous SRAM with NTD

TM

Org

Part Number

Mode

Speed

256KX18

AS7C33256PFS18B

PL-SCD

200/166/133 MHz

128KX32

AS7C33128PFS32B

PL-SCD

200/166/133 MHz

128KX36

AS7C33128PFS36B

PL-SCD

200/166/133 MHz

256KX18

AS7C33256PFD18B

PL-DCD

200/166/133 MHz

128KX32

AS7C33128PFD32B

PL-DCD

200/166/133 MHz

128KX36

AS7C33128PFD36B

PL-DCD

200/166/133 MHz

256KX18

AS7C33256FT18B

FT

7.5/8.0/10 ns

128KX32

AS7C33128FT32B

FT

7.5/8.0/10 ns

128KX36

AS7C33128FT36B

FT

7.5/8.0/10 ns

256KX18

AS7C33256NTD18B

NTD-PL

200/166/133 MHz

128KX32

AS7C33128NTD32B

NTD-PL

200/166/133 MHz

128KX36

AS7C33128NTD36B

NTD-PL

200/166/133 MHz

256KX18

AS7C33256NTF18B

NTD-FT

7.5/8.0/10 ns

128KX32

AS7C33128NTF32B

NTD-FT

7.5/8.0/10 ns

128KX36

AS7C33128NTF36B

NTD-FT

7.5/8.0/10 ns

1. NTD: No Turnaround Delay. NTD

TM

is a trademark of Alliance Semiconductor Corporation. All trademarks mentioned in this document are the property

of their respective owners.

®

AS7C33256NTF18B

4/13/05, v 1.3

Alliance Semiconductor

P. 3 of 18

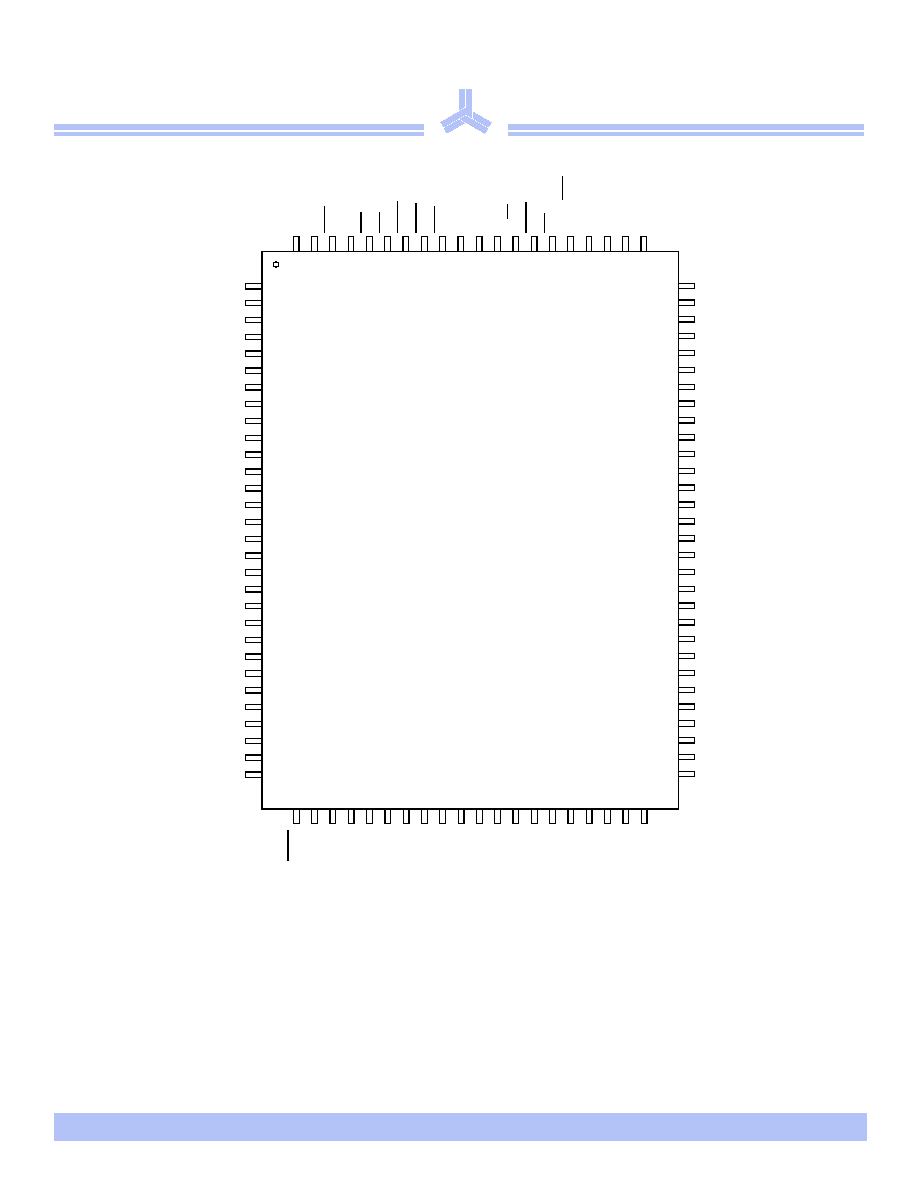

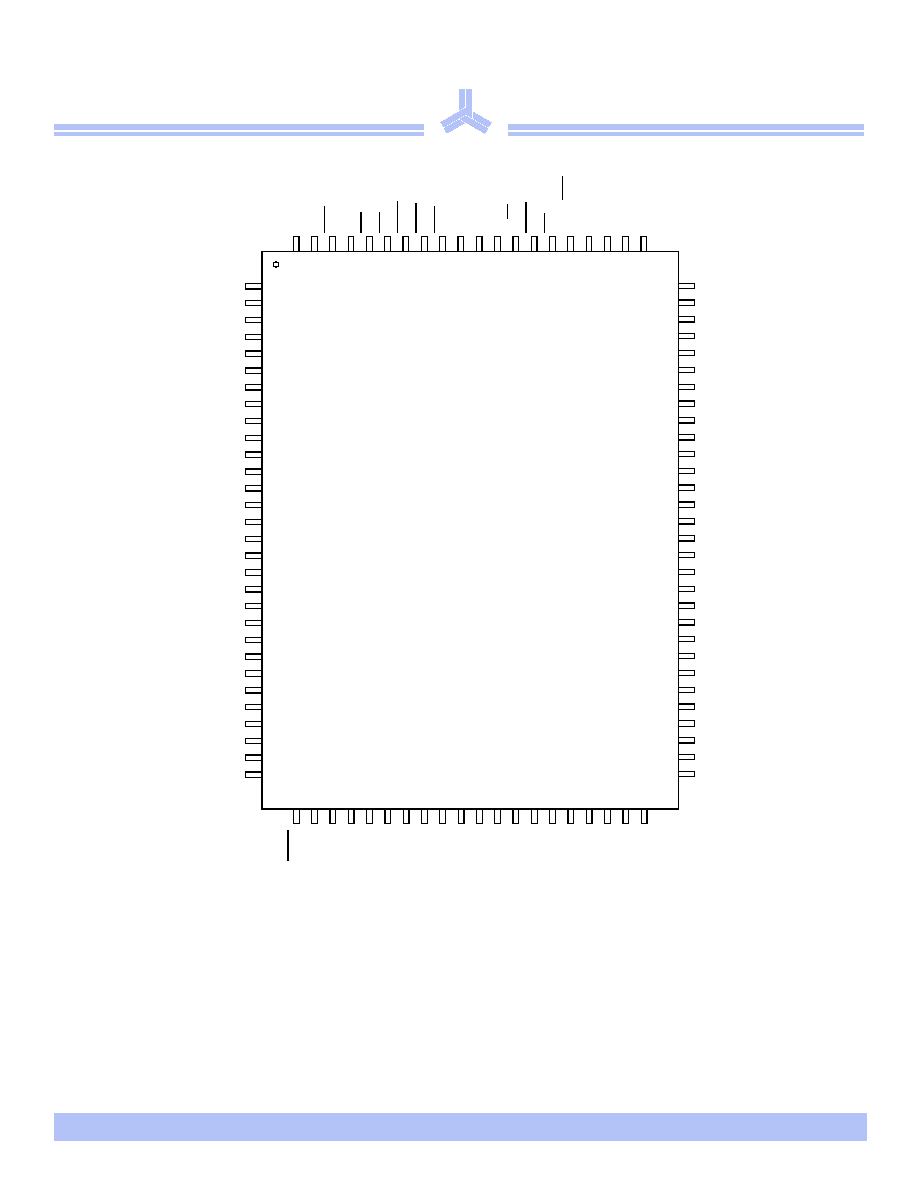

100-pin TQFP - top view

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

LBO

A

A

A

A

A1

A0

NC

NC

V

SS

V

DD

NC

NC

A

A

A

A

A

A

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

10

0

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

A A

CE0

CE1

NC

NC

BW

b

BW

a

CE2

V

DD

V

SS

CLK

R/W

CEN

OE

ADV

/

L

D

NC

NC

A

A

TQFP 14 x 20mm

A

NC

NC

NC

V

DDQ

V

SSQ

NC

NC

DQb0

DQb1

V

SSQ

V

DDQ

DQb2

DQb3

NC

V

DD

NC

V

SS

DQb4

DQb5

V

DDQ

V

SSQ

DQb6

DQb7

DQPb

NC

V

SSQ

V

DDQ

NC

NC

NC

A

NC

NC

V

DDQ

V

SSQ

NC

DQPa

DQa7

DQa6

V

SSQ

V

DDQ

DQa5

DQa4

V

SS

ZZ

DQa3

DQa2

V

DDQ

V

SSQ

DQa1

DQa0

NC

NC

V

SSQ

V

DDQ

NC

NC

NC

V

DD

NC

®

AS7C33256NTF18B

4/13/05, v 1.3

Alliance Semiconductor

P. 4 of 18

Functional Description

The AS7C33256NTF18B family is a high performance CMOS 4 Mbit synchronous Static Random Access Memory (SRAM)

organized as 262,144 words × 18 bits and incorporates a LATE Write.

This variation of the 4Mb+ synchronous SRAM uses the No Turnaround Delay (NTD

TM

) architecture, featuring an enhanced

write operation that improves bandwidth over flowthrough burst devices. In a normal flowthrough burst device, the write data,

command, and address are all applied to the device on the same clock edge. If a read command follows this write command,

the system must wait for one 'dead' cycle for valid data to become available. This dead cycle can significantly reduce overall

bandwidth for applications requiring random access or read-modify-write operations.

NTD

TM

devices use the memory bus more efficiently by introducing a write latency which matches the one-cycle flow-

through read latency. Write data is applied one cycle after the write command and address, allowing the read pipeline to clear.

With NTD

TM

, write and read operations can be used in any order without producing dead bus cycle.

Assert R/W low to perform write cycles. Byte write enable controls write access to specific bytes, or can be tied low for full 18

bit writes. Write enable signals, along with the write address, are registered on a rising edge of the clock. Write data is applied

to the device one clock cycle later. Unlike some asynchronous SRAMs, output enable OE does not need to be toggled for write

operations; it can be tied low for normal operations. Outputs go to a high impedance state when the device is de-selected by

any of the three chip enable inputs.

Use the ADV (burst advance) input to perform burst read, write and deselect operations. When ADV is high, external addresses, chip

select, R/W pins are ignored, and internal address counters increment in the count sequence specified by the LBO control. Any

device operations, including burst, can be stalled using the CEN=1, the clock enable input.

The AS7C33256NTF18B operates with a 3.3V ± 5% power supply for the device core (V

DD

). DQ circuits use a separate

power supply (V

DDQ

) that operates across 2.5V or 3.3V ranges. These devices are available in a 100-pin TQFP package.

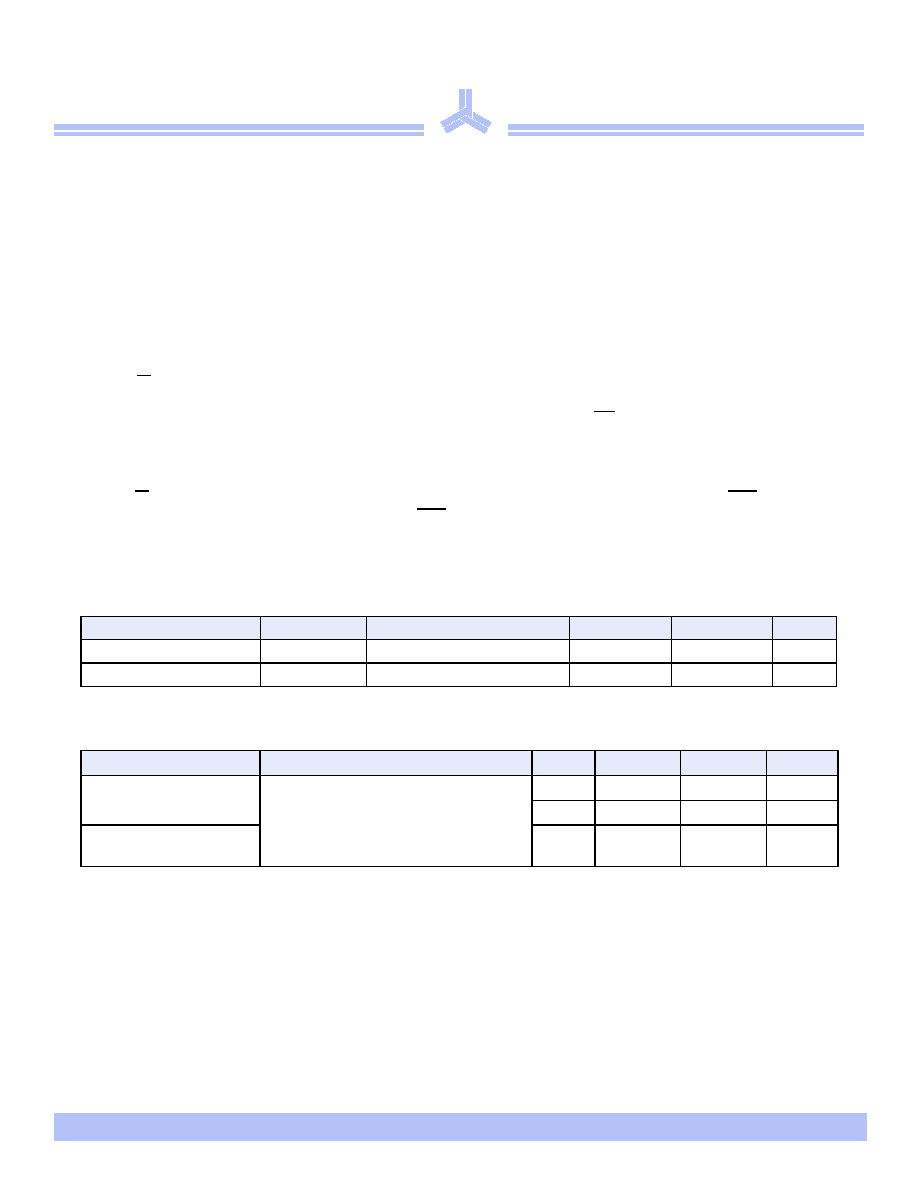

TQFP Capacitance

*Guranteed not tested

TQFP thermal resistance

Parameter

Symbol

Test conditions

Min

Max

Unit

Input capacitance

C

IN

*

V

in

= 0V

-

5

pF

I/O capacitance

C

I/O

*

V

in

= V

out

= 0V

-

7

pF

Description

Conditions

Symbol

Typical

Units

Thermal resistance

(junction to ambient)

1

1 This parameter is sampled

Test conditions follow standard test methods and

procedures for measuring thermal impedance,

per EIA/JESD51

1layer

JA

40

°C/W

4layer

JA

22

°C/W

Thermal resistance

(junction to top of case)

1

JC

8

°C/W

®

AS7C33256NTF18B

4/13/05, v 1.3

Alliance Semiconductor

P. 5 of 18

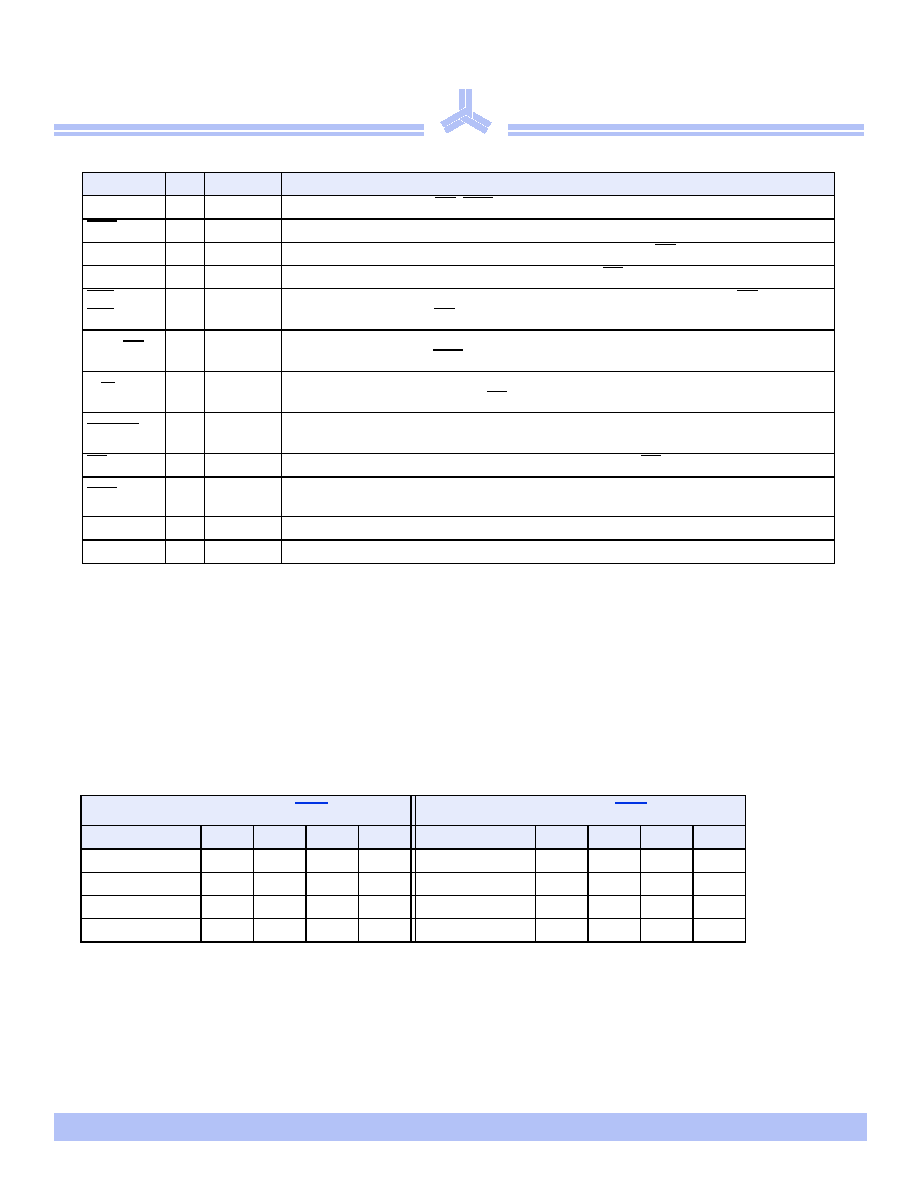

Signal descriptions

Snooze Mode

SNOOZE MODE is a low current, power-down mode in which the device is deselected and current is reduced to I

SB2

. The duration of

SNOOZE MODE is dictated by the length of time the ZZ is in a High state.

The ZZ pin is an asynchronous, active high input that causes the device to enter SNOOZE MODE.

When the ZZ pin becomes a logic High, I

SB2

is guaranteed after the time t

ZZI

is met. After entering SNOOZE MODE, all inputs except ZZ

is disabled and all outputs go to High-Z. Any operation pending when entering SNOOZE MODE is not guaranteed to successfully complete.

Therefore, SNOOZE MODE (READ or WRITE) must not be initiated until valid pending operations are completed. Similarly, when exiting

SNOOZE MODE during t

PUS

, only a DESELECT or READ cycle should be given while the SRAM is transitioning out of SNOOZE MODE.

Burst order

Signal

I/O Properties

Description

CLK

I

CLOCK

Clock. All inputs except OE, LBO, and ZZ are synchronous to this clock.

CEN

I

SYNC

Clock enable. When de-asserted high, the clock input signal is masked.

A, A0, A1

I

SYNC

Address. Sampled when all chip enables are active and ADV/LD is asserted.

DQ[a,b]

I/O

SYNC

Data. Driven as output when the chip is enabled and OE is active.

CE0, CE1,

CE2

I

SYNC

Synchronous chip enables. Sampled at the rising edge of CLK, when ADV/LD is asserted.

Are ignored when ADV/LD is high.

ADV/LD

I

SYNC

Advance or Load. When sampled high, the internal burst address counter will increment in

the order defined by the LBO input value. When low, a new address is loaded.

R/W

I

SYNC

A high during LOAD initiates a READ operation. A low during LOAD initiates a WRITE

operation. Is ignored when ADV/LD is high.

BW[a,b]

I

SYNC

Byte write enables. Used to control write on individual bytes. Sampled along with WRITE

command and BURST WRITE.

OE

I

ASYNC

Asynchronous output enable. I/O pins are not driven when OE is inactive.

LBO

I

STATIC

Selects Burst mode. When tied to V

DD

or left floating, device follows interleaved Burst order. When

driven Low, device follows linear Burst order. This signal is internally pulled High.

ZZ

I

ASYNC

Snooze. Places device in low power mode; data is retained. Connect to GND if unused.

NC

-

-

No connects.

Interleaved burst order LBO = 1

Linear burst order LBO = 0

A1A0 A1A0 A1A0 A1A0

A1A0 A1A0 A1A0 A1A0

Starting address

0 0

0 1

1 0

1 1

Starting Address

0 0

0 1

1 0

1 1

First increment

0 1

0 0

1 1

1 0

First increment

0 1

1 0

1 1

0 0

Second increment

1 0

1 1

0 0

0 1

Second increment

1 0

1 1

0 0

0 1

Third increment

1 1

1 0

0 1

0 0

Third increment

1 1

0 0

0 1

1 0

Document Outline