ASM5P2309A

September 2005

ASM5P2305A

rev 1.6

Alliance Semiconductor

2575 Augustine Drive

∑ Santa Clara, CA ∑ Tel: 408.855.4900 ∑ Fax: 408.855.4999 ∑ www.alsc.com

Notice: The information in this document is subject to change without notice.

3.3V Zero Delay Buffer

General Features

15MHz to 133MHz operating range, compatible

with CPU and PCI bus frequencies.

Zero input - output propagation delay.

Multiple

low-skew

outputs.

Output-output skew less than 250pS.

Device-device skew less than 700pS.

One input drives 9 outputs, grouped as

4 + 4 + 1(ASM5P2309A).

One input drives 5 outputs (ASM5P2305A).

Less than 200 pS cycle-to-cycle jitter is compatible

with Pentium

Æ

based systems.

Test Mode to bypass PLL (ASM5P2309A only,

Refer Select Input Decoding Table).

Available in 16pin 150-mil SOIC, 4.4 mm TSSOP

(ASM5P2309A), and in 8pin 150-mil SOIC

package (ASM5P2305A).

3.3V operation, advanced 0.35µ CMOS

technology.

Functional Description

ASM5P2309A is a versatile, 3.3V zero-delay buffer

designed to distribute high-speed clocks. It accepts one

reference input and drives out nine low-skew clocks. It is

available in a 16-pin package. The ASM5P2305A is the

eight-pin version of the ASM5P2309A. It accepts one

reference input and drives out five low-skew clocks.

The -1H version of the ASM5P23XXA operates at up to

133MHz frequencies, and has higher drive than the -1

devices. All parts have on-chip PLLs that lock to an input

clock on the REF pin. The PLL feedback is on-chip and is

obtained from the CLKOUT pad.

The ASM5P2309A has two banks of four outputs each,

which can be controlled by the Select inputs as shown in

the Select Input Decoding Table. The select input also

allows the input clock to be directly applied to the outputs

for chip and system testing purposes.

Multiple ASM5P2309A and ASM5P2305A devices can

accept the same input clock and distribute it. In this case

the skew between the outputs of the two devices is

guaranteed to be less than 700pS.

All outputs have less than 200pS of cycle-to-cycle jitter.

The input and output propagation delay is guaranteed to be

less than 350pS, and the output to output skew is

guaranteed to be less than 250pS.

The ASM5P2309A and the ASM5P2305A are available in

two different configurations, as shown in the ordering

information table. The ASM5P2305A-1/ ASM5P2309A-1 is

the base part. The ASM5P2305A-1H/ ASM5P2309A-1H is

the high drive version of the -1 and its rise and fall times

are much faster than -1 part.

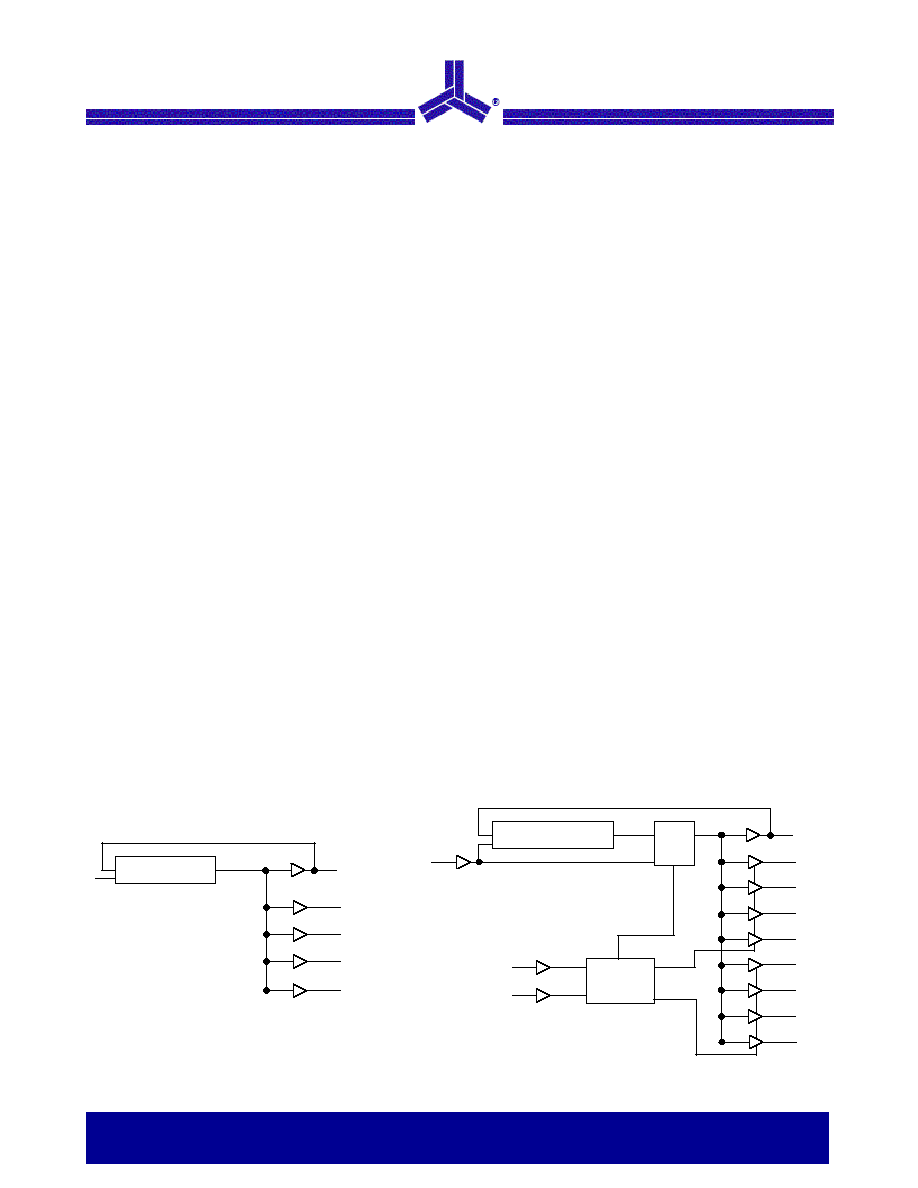

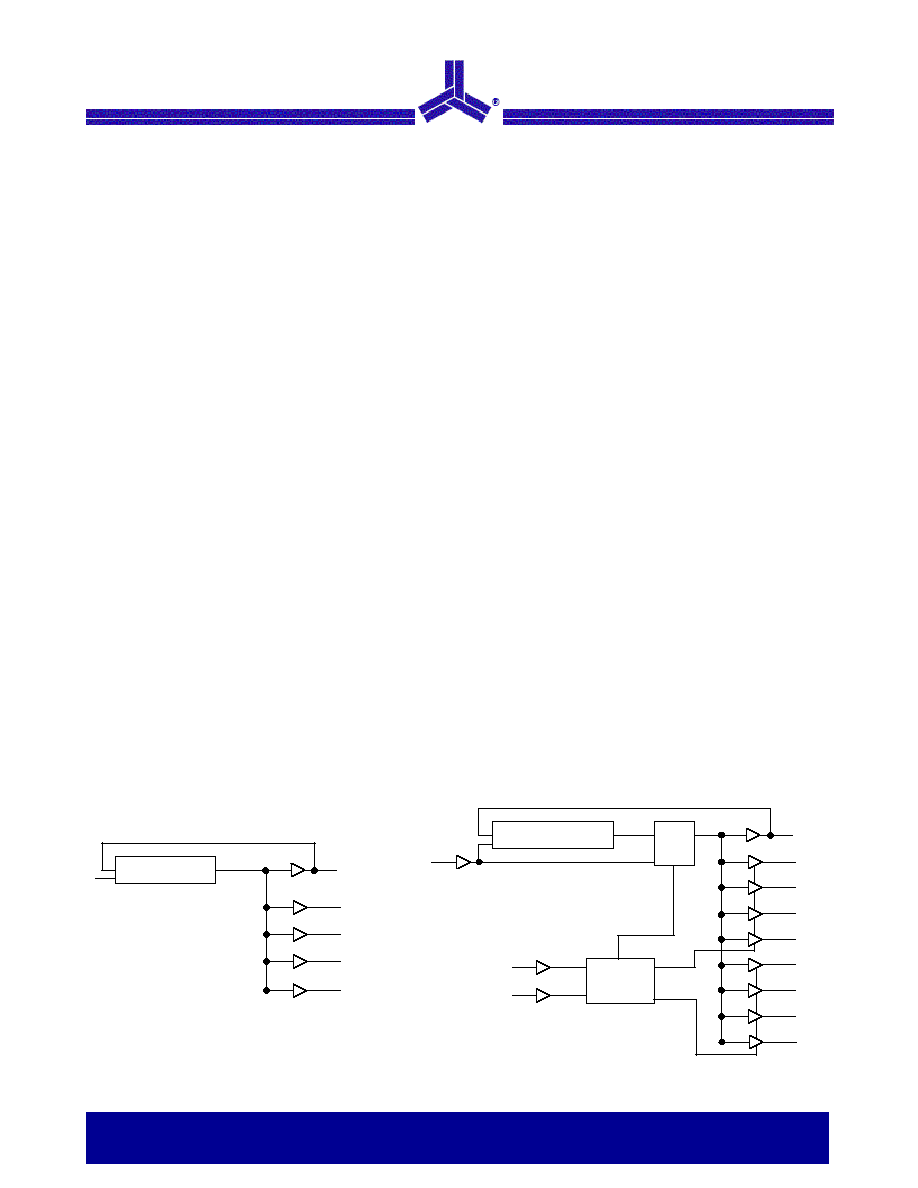

Block Diagram

ASM5P2309A

PLL

MUX

CLKOUT

CLKA1

CLKA2

CLKA3

CLKA4

CLKB1

CLKB2

CLKB3

CLKB4

Select Input

Decoding

S2

S1

REF

PLL

CLKOUT

CLK1

CLK2

CLK3

CLK4

ASM5P2305A

REF

ASM5P2309A

September 2005

ASM5P2305A

rev 1.6

3.3V Zero Delay Buffer

2 of 20

Notice: The information in this document is subject to change without notice.

Select Input Decoding for ASM5P2309A

S2

S1

Clock A1 - A4

Clock B1 - B4

CLKOUT

1

Output Source

PLL

Shut-Down

0 0 Three-state Three-state Driven

PLL

N

0 1 Driven Three-state Driven

PLL

N

1 0 Driven

Driven Driven Reference

Y

1 1 Driven

Driven Driven PLL

N

Notes:

1. This output is driven and has an internal feedback for the PLL. The load on this output can be adjusted to change the skew between the reference and the

output.

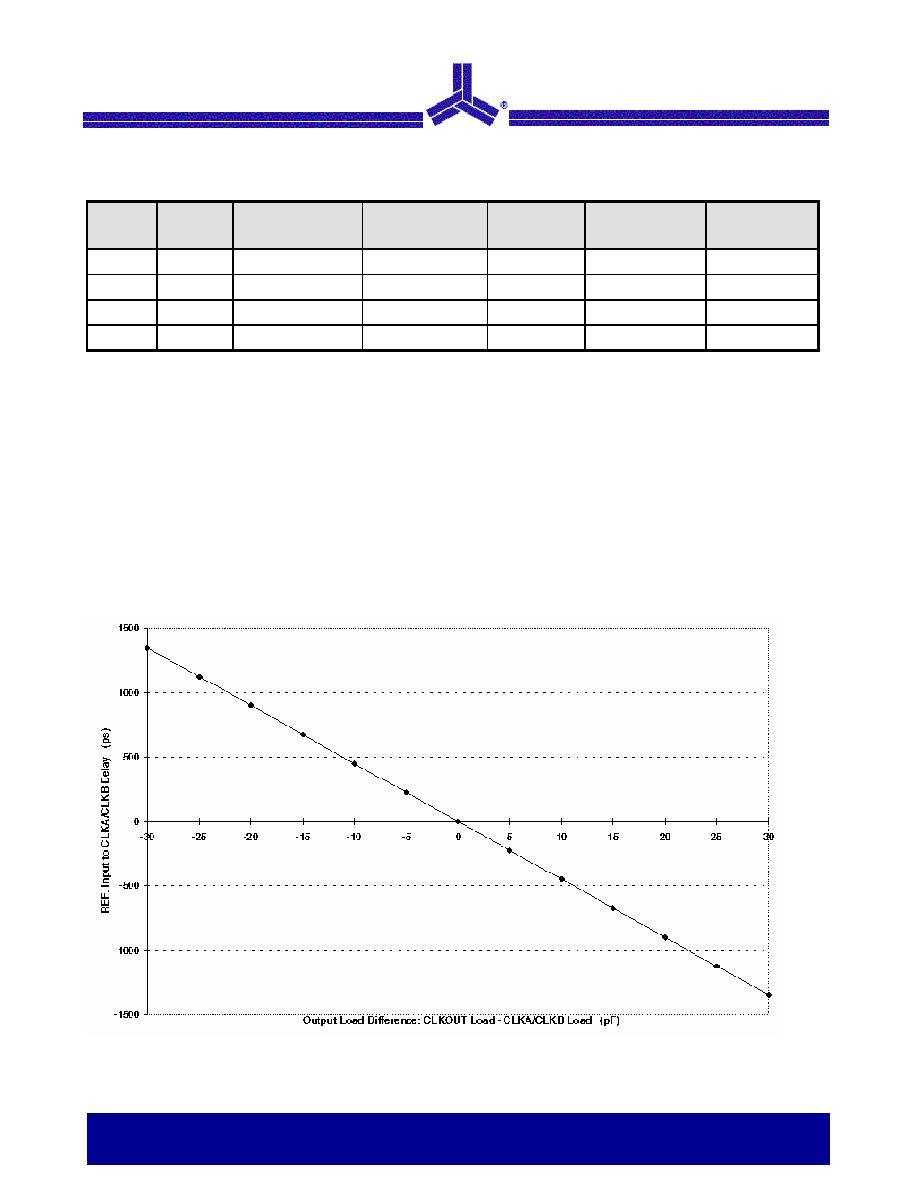

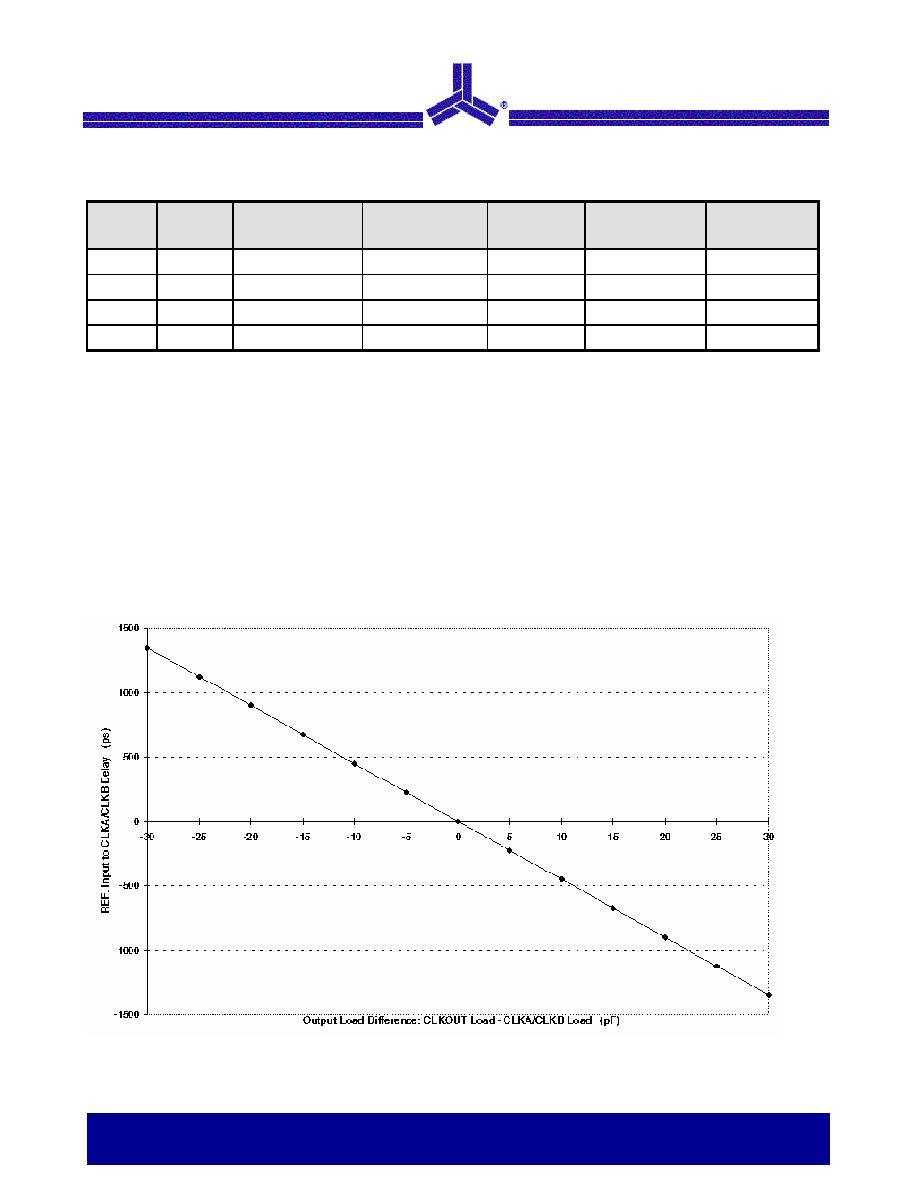

Zero Delay and Skew Control

All outputs should be uniformly loaded to achieve Zero

Delay between input and output. Since the CLKOUT pin is

the internal feedback to the PLL, its relative loading can

adjust the input-output delay.

For applications requiring zero input-output delay, all

outputs, including CLKOUT, must be equally loaded. Even

if CLKOUT is not used, it must have a capacitive load equal

to that on other outputs, for obtaining zero-input-output

delay.

ASM5P2309A

September 2005

ASM5P2305A

rev 1.6

3.3V Zero Delay Buffer

3 of 20

Notice: The information in this document is subject to change without notice.

CLK2

CLK3

1

2

3

5

6

7

8

ASM5P2305A

REF

CLK1

GND

V

DD

CLKOUT

CLK4

4

Pin Configuration

Pin Description for ASM5P2309A

Pin #

Pin Name

Description

1 REF

2

Input reference frequency, 5V tolerant input

2 CLKA1

3

Buffered clock output, bank A

3 CLKA2

3

Buffered clock output, bank A

4 V

DD

3.3V supply

5 GND

Ground

6 CLKB1

3

Buffered clock output, bank B

7 CLKB2

3

Buffered clock output, bank B

8 S2

4

Select input, bit 2

9 S1

4

Select input, bit 1

10 CLKB3

3

Buffered clock output, bank B

11 CLKB4

3

Buffered clock output, bank B

12 GND

Ground

13 V

DD

3.3V supply

14 CLKA3

3

Buffered clock output, bank A

15 CLKA4

3

Buffered clock output, bank A

16 CLKOUT

3

Buffered output, internal feedback on this pin

S2

2

1

3

4

5

6

7

8

CLKA2

V

DD

GND

CLKB1

CLKB2

CLKA1

REF

11

9

10

12

13

14

15

16

CLKA3

CLKA4

CLKB3

CLKB4

V

DD

CLKOUT

GND

ASM5P2309A

S1

ASM5P2309A

September 2005

ASM5P2305A

rev 1.6

3.3V Zero Delay Buffer

4 of 20

Notice: The information in this document is subject to change without notice.

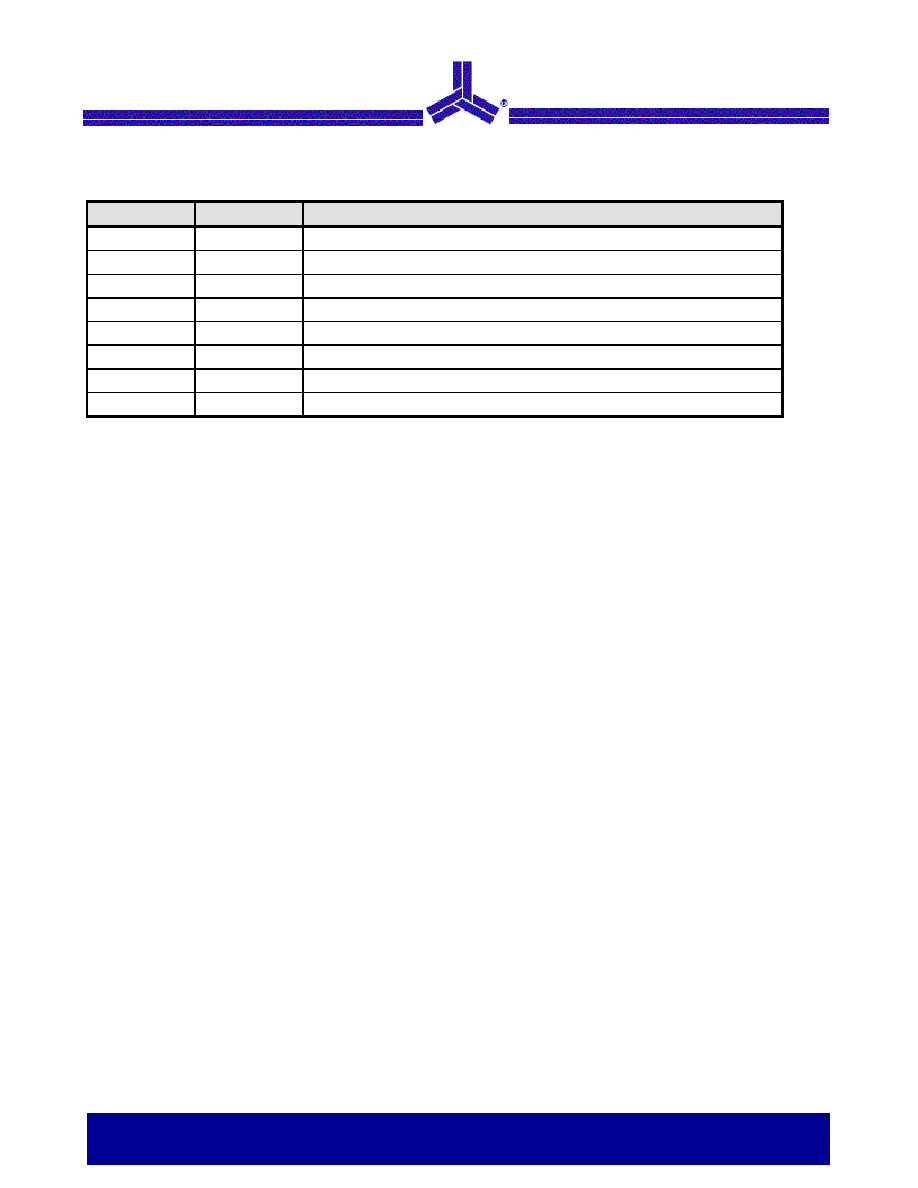

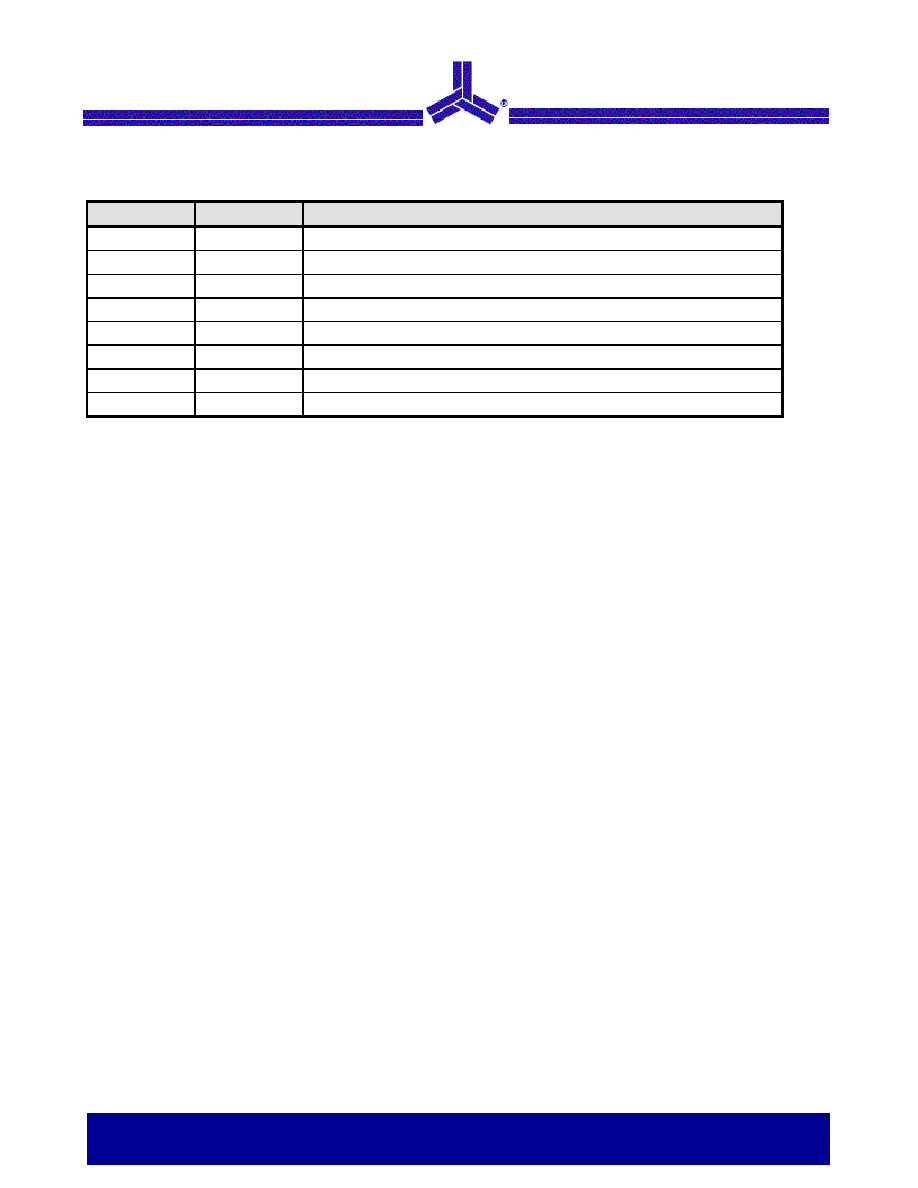

Pin Description for ASM5P2305A

Pin #

Pin Name

Description

1 REF

2

Input reference frequency, 5V-tolerant input

2 CLK2

3

Buffered clock output

3 CLK1

3

Buffered clock output

4 GND

Ground

5 CLK3

3

Buffered clock output

6 V

DD

3.3V supply

7 CLK4

3

Buffered clock output

8 CLKOUT

3

Buffered clock output, internal feedback on this pin

Notes:

2. Weak pull-down.

3. Weak pull-down on all outputs.

4. Weak pull-up on these inputs.

ASM5P2309A

September 2005

ASM5P2305A

rev 1.6

3.3V Zero Delay Buffer

5 of 20

Notice: The information in this document is subject to change without notice.

Absolute Maximum Ratings

Parameter

Min

Max

Unit

Supply Voltage to Ground Potential

-0.5

+7.0

V

DC Input Voltage (Except REF)

-0.5

V

DD

+ 0.5

V

DC Input Voltage (REF)

-0.5

7

V

Storage Temperature

-65

+150

∞C

Max. Soldering Temperature (10 sec)

260

∞C

Junction Temperature

150

∞C

Static Discharge Voltage

(As per JEDEC STD22- A114-B)

2000

V

Note: These are stress ratings only and functional usage is not implied. Exposure to absolute maximum ratings for prolonged periods can

affect device reliability.

Operating Conditions for ASM5P2305A and ASM5P2309A - Commercial Temperature Devices

Parameter

Description

Min

Max

Unit

V

DD

Supply Voltage

3.0

3.6

V

T

A

Operating Temperature (Ambient Temperature)

0

70

∞C

C

L

Load Capacitance, below 100MHz

30

pF

C

L

Load Capacitance, from 100MHz to 133MHz

10

pF

C

IN

Input Capacitance

7

pF