Document Outline

- Mercury Programmable Logic Device Family Data Sheet

Æ

Altera Corporation

1

Mercury

Programmable Logic

Device Family

January 2003, ver. 2.2

Data Sheet

DS-MERCURY-2.2

D

e

ve

l

o

pm

e

n

t

13

To

o

l

s

Features...

High-performance programmable logic device (PLD) family (see

Table 1

)

≠

Integrated high-speed transceivers with support for clock data

recovery (CDR) at up to 1.25 gigabits per second (Gbps)

≠

Look-up table (LUT)-based architecture optimized for high

speed

≠

Advanced interconnect structure for fast routing of critical paths

≠

Enhanced I/O structure for versatile standards and interface

support

≠

Up to 14,400 logic elements (LEs)

System-level features

≠

Up to four general-purpose phase-locked loops (PLLs) with

programmable multiplication and delay shifting

≠

Up to 12 PLL output ports

≠

Dedicated multiplier circuitry for high-speed implementation of

signed or unsigned multiplication up to 16

◊

16

≠

Embedded system blocks (ESBs) used to implement memory

functions including quad-port RAM, true dual-port RAM, first-

in first-out (FIFO) buffers, and content-addressable memory

(CAM)

≠

Each ESB contains 4,096 bits and can be split and used as two

2,048-bit unidirectional dual-port RAM blocks

Note to

Table 1

:

(1)

Each ESB can be used for two dual- or single-port RAM blocks.

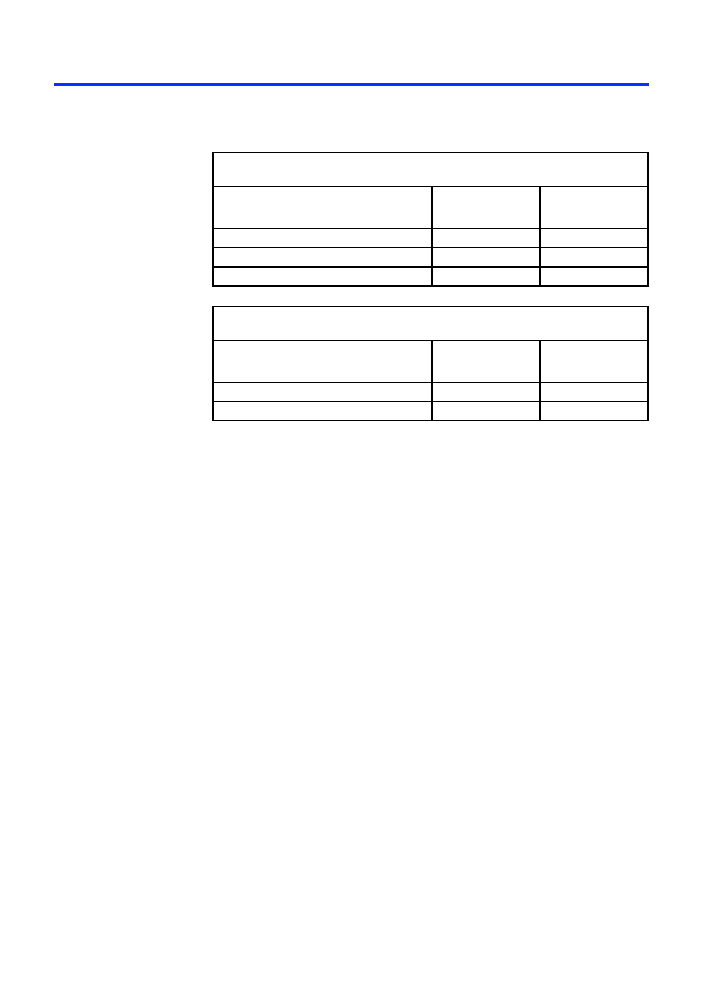

Table 1. Mercury Device Features

Feature

EP1M120

EP1M350

Typical gates

120,000

350,000

HSDI channels

8

18

LEs

4,800

14,400

ESBs

(1)

12

28

Maximum RAM bits

49,152

114,688

Maximum user I/O pins

303

486

2

Altera Corporation

Mercury Programmable Logic Device Family Data Sheet

...and More

Features

Advanced high-speed I/O features

≠

Robust I/O standard support, including LVTTL, PCI up to

66 MHz, 3.3-V AGP in 1

◊

and 2

◊

modes, 3.3-V SSTL-3 and 2.5-V

SSTL-2, GTL+, HSTL, CTT, LVDS, LVPECL, and 3.3-V PCML

≠

High-speed differential interface (HSDI) with dedicated

circuitry for CDR at up to 1.25 Gbps for LVDS, LVPECL, and

3.3-V PCML

≠

Support for source-synchronous True-LVDS

TM

circuitry up to

840 megabits per second (Mbps) for LVDS, LVPECL, and 3.3-V

PCML

≠

Up to 18 input and 18 output dedicated differential channels of

high-speed LVDS, LVPECL, or 3.3-V PCML

≠

Built-in 100-

termination resistor on HSDI data and clock

differential pairs

≠

Flexible-LVDS

TM

circuitry provides 624-Mbps support on up to

100 channels with the EP1M350 device

≠

Versatile three-register I/O element (IOE) supporting double

data rate I/O (DDRIO), double data-rate (DDR) SDRAM, zero

bus turnaround (ZBT) SRAM, and quad data rate (QDR) SRAM

Designed for low-power operation

≠

1.8-V internal supply voltage (V

CCINT

)

≠

MultiVolt

TM

I/O interface voltage levels (V

CCIO

) compatible

with 1.5-V, 1.8-V, 2.5-V, and 3.3-V devices

≠

5.0-V tolerant with external resistor

Advanced interconnect structure

≠

Multi-level FastTrack

Æ

Interconnect structure providing fast,

predictable interconnect delays

≠

Optimized high-speed Priority FastTrack Interconnect for

routing critical paths in a design

≠

Dedicated carry chain that implements arithmetic functions such

as fast adders, counters, and comparators (automatically used by

software tools and megafunctions)

≠

FastLUT

TM

connection allowing high speed direct connection

between LEs in the same logic array block (LAB)

≠

Leap lines allowing a single LAB to directly drive LEs in adjacent

rows

≠

The RapidLAB interconnect providing a high-speed connection

to a 10-LAB-wide region

≠

Dedicated clock and control signal resources, including four

dedicated clocks, six dedicated fast global signals, and additional

row-global signals

Altera Corporation

3

Mercury Programmable Logic Device Family Data Sheet

D

e

ve

l

o

pm

e

n

t

13

To

o

l

s

Tables 2

and

3

show the Mercury

TM

FineLine BGA

TM

device package sizes,

options, and I/O pin counts.

General

Description

Mercury devices integrate high-speed differential transceivers and

support for CDR with a speed-optimized PLD architecture. These

transceivers are implemented through the dedicated serializer,

deserializer, and clock recovery circuitry in the HSDI and incorporate

support for the LVDS, LVPECL, and 3.3-V PCML I/O standards. This

circuitry, together with enhanced I/O elements (IOEs) and support for

numerous I/O standards, allows Mercury devices to meet high-speed

interface requirements.

Mercury devices are the first PLDs optimized for core performance. These

LUT-based, enhanced memory devices use a network of fast routing

resources to achieve optimal performance. These resources are ideal for

data-path, register-intensive, mathematical, digital signal processing

(DSP), or communications designs.

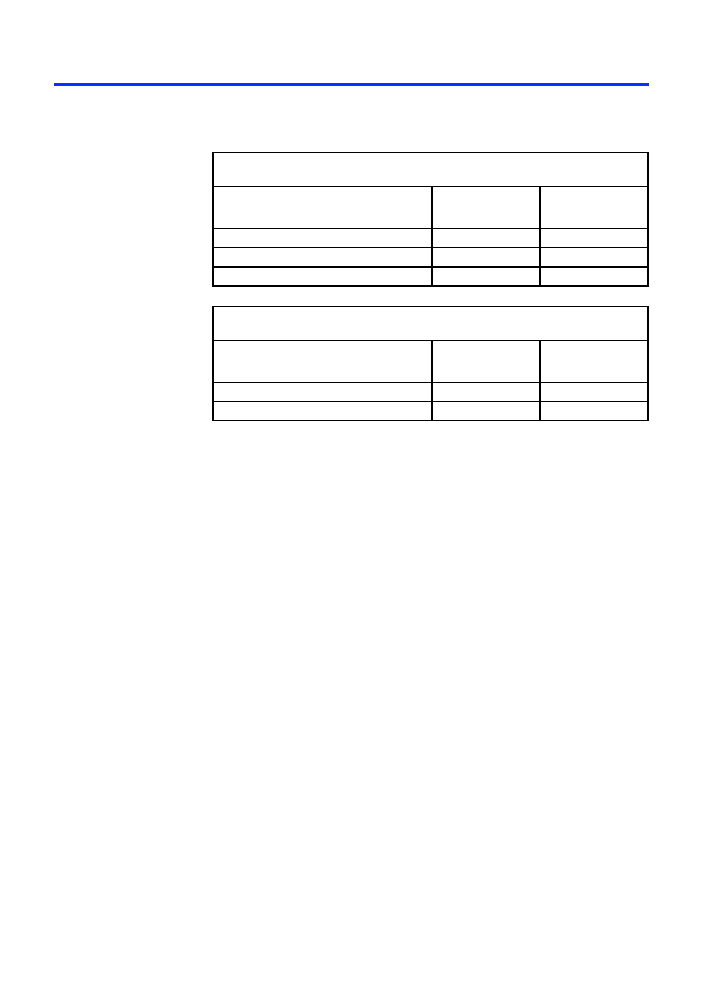

Table 2. Mercury Package Sizes

Feature

484-Pin

FineLine BGA

780-Pin

FineLine BGA

Pitch (mm)

1.00

1.00

Area (mm

2

)

529

841

Length

◊

width (mm

◊

mm)

23

◊

23

29

◊

29

Table 3. Mercury Package Options & I/O Count

Device

484-Pin

FineLine BGA

780-Pin

FineLine BGA

EP1M120

303

EP1M350

486

4

Altera Corporation

Mercury Programmable Logic Device Family Data Sheet

Mercury devices include other features for performance such as quad-

port RAM, CAM, general purpose PLLs, and dedicated circuitry for

implementing multiplier circuits.

Table 4

shows Mercury performance.

Note to

Table 4

:

(1)

The clock tree supports up to 400 MHz. Although the registered performance for these designs exceed 400 MHz,

they are limited by the clock tree limit.

Configuration

The logic, circuitry, and interconnects in the Mercury architecture are

configured with CMOS SRAM elements. Mercury devices are

reconfigurable and are 100% tested prior to shipment. As a result, test

vectors do not have to be generated for fault coverage purposes. Instead,

the designer can focus on simulation and design verification. In addition,

the designer does not need to manage inventories of different ASIC

designs; Mercury devices can be configured on the board for the specific

functionality required.

Mercury devices are configured at system power-up with data stored in

an Altera

Æ

serial configuration device or provided by a system controller.

Altera offers in-system programmability (ISP)-capable configuration

devices, which configure Mercury devices via a serial data stream.

Mercury devices can be configured in under 70 ms. Moreover, Mercury

devices contain an optimized interface that permits microprocessors to

configure Mercury devices serially or in parallel, synchronously or

asynchronously. This interface also enables microprocessors to treat

Mercury devices as memory and to configure the device by writing to a

virtual memory location, simplifying reconfiguration.

Table 4. Mercury Performance

Application

Resources Used

Performance

LEs

ESBs

-5 Speed

Grade

-6 Speed

Grade

-7 Speed

Grade

Units

16-bit loadable counter

(1)

16

0

400

400

400

MHz

32-bit loadable counter

(1)

32

0

400

400

400

MHz

32-bit accumulator

(1)

32

0

400

400

400

MHz

32-to-1 multiplexer

27

0

1.864

2.466

2.723

ns

32

◊

64 asynchronous FIFO

103

2

290

258

242

MHz

8-bit, 37-tap FIR filter

251

1

290

240

205

MSPS

Altera Corporation

5

Mercury Programmable Logic Device Family Data Sheet

D

e

ve

l

o

pm

e

n

t

13

To

o

l

s

After a Mercury device has been configured, it can be reconfigured

in-circuit by resetting the device and loading new data. Real-time changes

can be made during system operation, enabling innovative reconfigurable

computing applications.

Software

Mercury devices are supported by the Altera Quartus

TM

II development

system, a single, integrated package that offers HDL and schematic design

entry, compilation and logic synthesis, full simulation and worst-case

timing analysis, SignalTap

TM

logic analysis, and device configuration. The

Quartus II software also ships with Altera-specific HDL synthesis tools

from Exemplar Logic and Synopsys, and Altera-specific Register Transfer

Level (RTL) and timing simulation tools from Model Technology. The

Quartus II software supports PCs running Windows 98, Windows NT 4.0,

and Windows 2000; UNIX workstations running Solaris 2.6, 7, or 8, or

HP-UX 10.2 or 11.0; and PCs running Red Hat Linux 7.1.

The Quartus II software provides NativeLink

TM

interfaces to other

industry-standard PC- and UNIX-workstation-based EDA tools. For

example, designers can invoke the Quartus II software from within the

Mentor Graphics LeonardoSpectrum software, Synplicity's Synplify

software, and the Synopsys FPGA Express software. The Quartus II

software also contains built-in optimized synthesis libraries; synthesis

tools can use these libraries to optimize designs for Mercury devices. For

example, the Synopsys Design Compiler library, supplied with the

Quartus II development system, includes DesignWare functions

optimized for the Mercury architecture.

For more information on the Quartus II development system, see the

Quartus II Programmable Logic Development System & Software Data Sheet.

Functional

Description

The Mercury architecture contains a row-based logic array to implement

general logic and a row-based embedded system array to implement

memory and specialized logic functions. Signal interconnections within

Mercury devices are provided by a series of row and column

interconnects with varying lengths and speeds. The priority FastTrack

Interconnect structure is faster than other interconnects; the Quartus II

Compiler places design-critical paths on these faster lines to improve

design performance.