| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: FS6131-01 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

I

2

C is a licensed trademark of Philips Electronics, N.V. Windows and Windows NT are registered trademarks of Microsoft Corporation. American Microsystems, Inc. reserves the right to change detail

specifications as may be required to permit improvements in the design of its products.

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

1.0 Features

∑

Complete programmable control via I

2

C

‰

-bus

∑

Selectable CMOS or PECL compatible outputs

∑

External feedback loop capability allows genlocking

∑

Tunable VCXO loop for jitter attenuation

∑

Commercial (FS6131-01) and industrial (FS6131-01i)

temperature versions available

2.0 Description

The FS6131-01 is a monolithic CMOS clock genera-

tor/regenerator IC designed to minimize cost and compo-

nent count in a variety of electronic systems. Via the I

2

C-

bus interface, the FS6131-01 can be adapted to many

clock generation requirements.

The ability to tune the on-board voltage-controlled crystal

oscillator (VCXO), the length of the Reference and Feed-

back Dividers, their granularity, and the flexibility of the

Post Divider make the FS6131-01 the most flexible

stand-alone phase-locked loop (PLL) clock generator

available.

3.0 Applications

∑

Frequency

Synthesis

∑

Line-Locked and Genlock Applications

∑

Clock

Multiplication

∑

Telecom

Jitter

Attenuation

Figure 1: Pin Configuration

1

16

2

3

4

5

6

7

8

15

14

13

12

11

10

9

SCL

SDA

ADDR

VSS

XIN

XOUT

XTUNE

VDD

LOCK/IPRG

EXTLF

VSS

REF

FBK

VDD

CLKP

CLKN

16-pin 0.150" SOIC

F

S

6

131

Figure 2: Block Diagram

FS6131

VCXO

Divider

(optional)

(optional)

CRYSTAL LOOP

MAIN LOOP

VCXO

XOUT

XIN

Control

ROM

XTUNE

Reference

Divider

(N

R

)

Phase-

Frequency

Detector

Charge

Pump

UP

DOWN

REF

FBK

Phase-

Frequency

Detector

Charge

Pump

UP

DOWN

Feedback

Divider

(N

F

)

Internal

Loop

Filter

EXTLF

I

2

C

Interface

SCL

SDA

ADDR

Registers

POST3[1:0]

POST2[1:0]

POST1[1:0]

REFDIV[11:0]

FBKDIV[13:0]

EXTLF

PDREF

PDFBK

VCOSPD,

OSCTYPE

LFTC

MLCP[1:0]

XLCP[1:0]

XLROM[2:0]

XLPDEN,

XLSWAP

REFDSRC

XCT[3:0],

XLVTEN

(f

REF

)

(f

VCO

)

LOCK/

IPRG

Post

Divider

(N

Px

)

Voltage

Controlled

Oscillator

Lock

Detect

CMOS

(optional)

STAT[1:0]

OUTMUX[1:0]

Clock

Gobbler

GBL

(optional)

FBKDSRC[1:0]

CMOS/PECL

Output

CLKN

(f

CLK

)

CLKP

R

LF

C

LF

C

LP

11

00

10

01

01

00

10

11

1

0

1

0

0

1

1

0

1

0

2

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

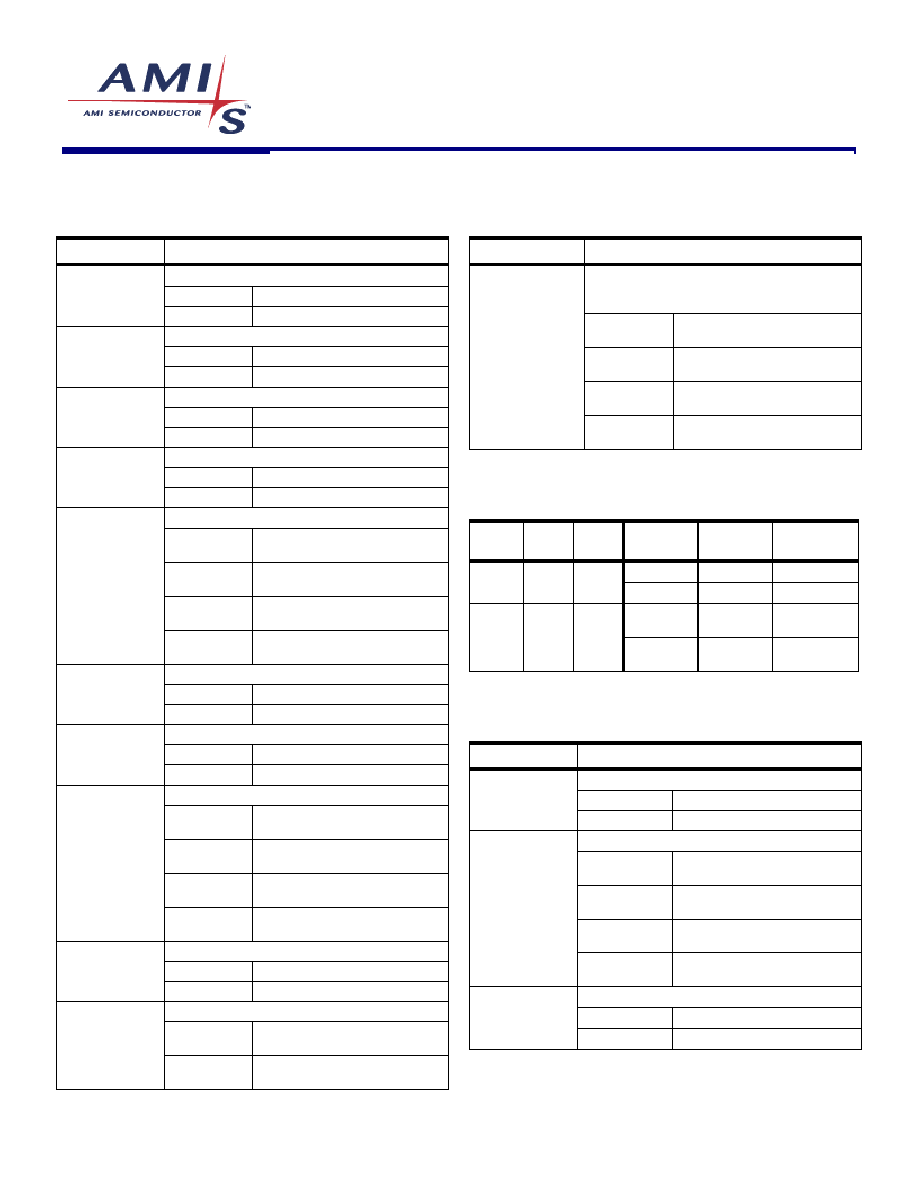

Table 1: Pin Descriptions

Key: AI = Analog Input; AO = Analog Output; DI = Digital Input; DI

U

= Input with Internal Pull-Up; DI

D

= Input with Internal Pull-Down; DIO = Digital Input/Output; DI-3 = Three-Level Digital Input,

DO = Digital Output; P = Power/Ground; # = Active Low pin

PIN

TYPE

NAME

DESCRIPTION

1

DI

SCL

Serial Interface Clock (requires an external pull-up)

2

DIO

SDA

Serial Interface Data Input/Output (requires an external pull-up)

3

DI

ADDR

Address Select Bit (see Section 5.2.1)

4

P

VSS

Ground

5

AI

XIN

VCXO Feedback

6

AO

XOUT

VCXO Drive

7

AI

XTUNE

VCXO Tune

8

P

VDD

Power Supply (+5V)

9

DIO

LOCK/IPRG

Lock Indicator / PECL Current Drive Programming

10

AI

EXTLF

External Loop Filter

11

P

VSS

Ground

12

DI

REF

Reference Frequency Input

13

DI

FBK

Feedback Input

14

P

VDD

Power Supply (+5V)

15

DO

CLKP

Differential Clock Output (+)

16

DO

CLKN

Differential Clock Output (-)

4.0

Functional Block Description

4.1

Main Loop PLL

The Main Loop Phase Locked Loop (ML-PLL) is a stan-

dard phase- and frequency- locked loop architecture. As

shown in Figure 2, the ML-PLL consists of a Reference

Divider, a Phase-Frequency Detector (PFD), a charge

pump, an internal loop filter, a Voltage-Controlled Oscil-

lator (VCO), a Feedback Divider, and a Post Divider.

During operation, the reference frequency (f

REF

), gener-

ated by either the on-board crystal oscillator or an exter-

nal frequency source, is first reduced by the Reference

Divider. The integer value that the frequency is divided by

is called the modulus, and is denoted as N

R

for the Ref-

erence Divider. The divided reference is then fed into the

PFD.

The PFD controls the frequency of the VCO (f

VCO

)

through the charge pump and loop filter. The VCO pro-

vides a high-speed, low noise, continuously variable fre-

quency clock source for the ML-PLL. The output of the

VCO is fed back to the PFD through the Feedback Di-

vider (the modulus is denoted by N

F

) to close the loop.

The PFD will drive the VCO up or down in frequency until

the divided reference frequency and the divided VCO

frequency appearing at the inputs of the PFD are equal.

The input/output relationship between the reference fre-

quency and the VCO frequency is

R

REF

F

VCO

N

f

N

f

=

.

If the VCO frequency is used as the PLL output fre-

quency (f

CLK

) then the basic PLL equation can be rewrit-

ten as

˜

˜

¯

ˆ

Á

Á

Ë

Ê

=

R

F

REF

CLK

N

N

f

f

.

4.1.1 Reference

Divider

The Reference Divider is designed for low phase jitter.

The divider accepts either the output of either the Crystal

Loop (the VCXO output) or an external reference fre-

quency, and provides a divided-down frequency to the

PFD. The Reference Divider is a 12-bit divider, and can

be programmed for any modulus from 1 to 4095. See

both Table 3 and Table 8 for additional programming in-

formation.

3

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

4.1.2 Feedback

Divider

The Feedback Divider is based on a dual-modulus

prescaler technique. The technique allows the same

granularity as a fully programmable feedback divider,

while still allowing the programmable portion to operate at

low speed. A high-speed pre-divider (also called a

prescaler) is placed between the VCO and the program-

mable Feedback Divider because of the high speeds at

which the VCO can operate. The dual-modulus technique

insures reliable operation at any speed that the VCO can

achieve and reduces the overall power consumption of

the divider.

For example, a fixed divide-by-eight could be used in the

Feedback Divider. Unfortunately, a divide-by-eight would

limit the effective modulus of the feedback divider path to

multiples of eight. The limitation would restrict the ability

of the PLL to achieve a desired input-frequency-to-

output-frequency ratio without making both the Reference

and Feedback Divider values comparatively large. Large

divider moduli are generally undesirable due to increased

phase jitter.

Figure 3: Feedback Divider

Dual-

Modulus

Prescaler

A

Counter

M

Counter

f

vco

To understand the operation, refer to Figure 3. The M-

counter (with a modulus of M) is cascaded with the dual-

modulus prescaler. If the prescaler modulus were fixed at

N, the overall modulus of the feedback divider chain

would be M

◊

N. However, the A-counter causes the

prescaler modulus to be altered to N+1 for the first A out-

puts of the prescaler. The A-counter then causes the

dual-modulus prescaler to revert to a modulus of

N

until

the M-counter reaches its terminal state and resets the

entire divider. The overall modulus can be expressed as

)

(

)

1

(

A

M

N

N

A

-

+

+

,

where M

A, which simplifies to

A

N

M

+

◊

.

4.1.3 Feedback

Divider

Programming

The requirement that M

A means that the Feedback Di-

vider can only be programmed for certain values below a

divider modulus of 56. The selection of divider values is

listed in Table 2.

If the desired Feedback Divider is less than 56, find the

divider value in the table. Follow the column up to find the

A-counter program value. Follow the row to the left to find

the M-counter value.

Above a modulus of 56, the Feedback Divider can be

programmed to any value up to 16383. See both Table 3

and Table 8 for additional programming information.

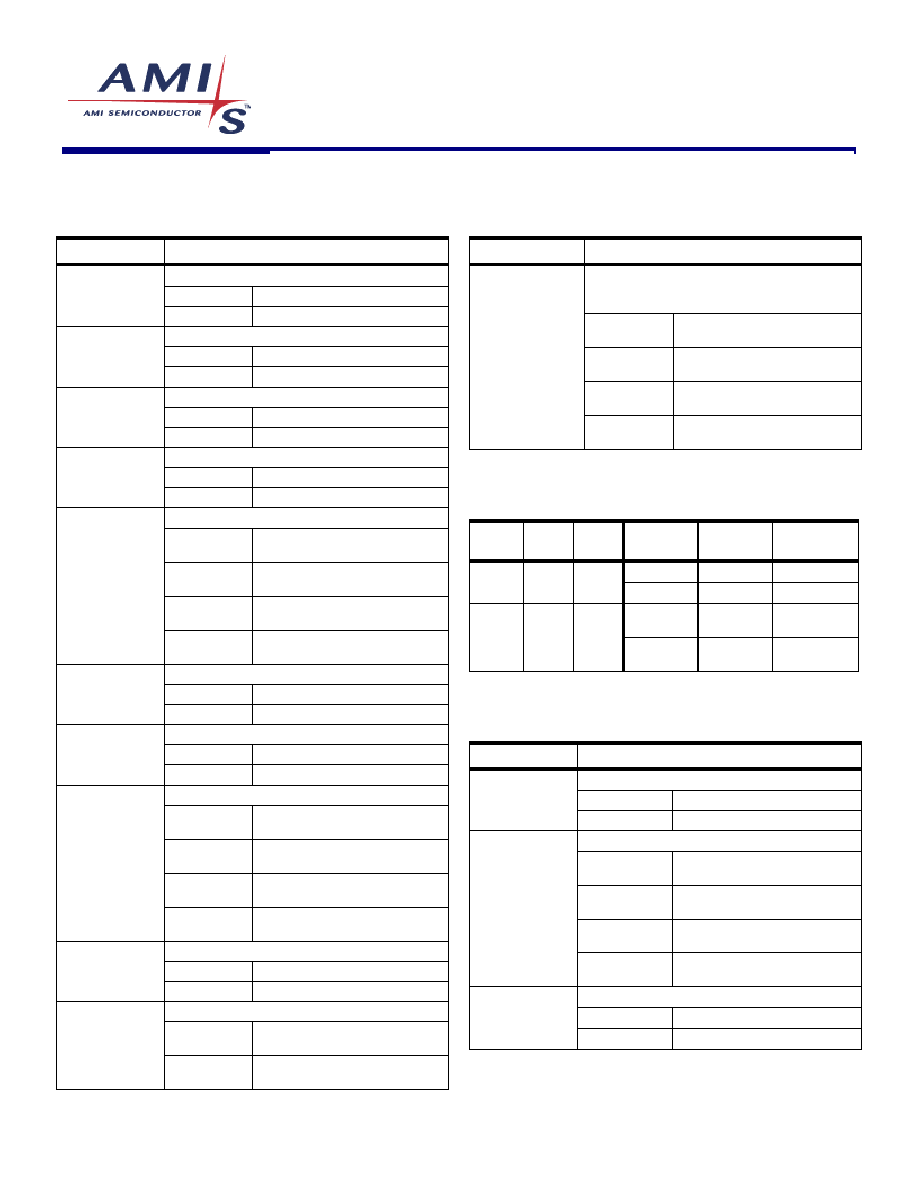

Table 2: Feedback Modulus Below 56

A-COUNTER: FBKDIV[2:0]

M-COUNTER:

FBKDIV[13:3]

000

001

010

011

100

101

110

111

00000000001

8

9

-

-

-

-

-

-

00000000010

16

17

18

-

-

-

-

-

00000000011

24

25

26

27

-

-

-

-

00000000100

32

33

34

35

36

-

-

-

00000000101

40

41

42

43

44

45

-

-

00000000110

48

49

50

51

52

53

54

-

00000000111

56

57

58

59

60

61

62

63

FEEDBACK DIVIDER MODULUS

4.1.4 Post

Divider

The Post Divider consists of three individually program-

mable dividers, as shown in Figure 4.

Figure 4: Post Divider

Post

Divider 1

(N

P1

)

Post

Divider 2

(N

P2

)

Post

Divider 3

(N

P3

)

POST3[1:0]

POST2[1:0]

POST1[1:0]

POST DIVIDER (N

Px

)

f

out

f

GBL

The moduli of the individual dividers are denoted as N

P1

,

N

P2

, and N

P3

, and together they make up the array

modulus N

Px

.

3

2

1

P

P

P

Px

N

N

N

N

◊

◊

=

4

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

The Post Divider performs several useful functions. First,

it allows the VCO to be operated in a narrower range of

speeds compared to the variety of output clock speeds

that the device is required to generate. Second, it

changes the basic PLL equation to

˜

˜

¯

ˆ

Á

Á

Ë

Ê

˜

˜

¯

ˆ

Á

Á

Ë

Ê

=

Px

R

F

REF

CLK

N

N

N

f

f

1

.

The extra integer in the denominator permits more flexi-

bility in the programming of the loop for many applica-

tions where frequencies must be achieved exactly.

Note that a nominal 50/50 duty factor is preserved for

selections which have an odd modulus.

4.2

Phase Adjust and Sampling

In line-locked or genlocked applications, it is necessary to

know the exact phase relation of the output clock relative

to the input clock. Since the VCO is included within the

feedback loop in a simple PLL structure, the VCO output

is exactly phase aligned with the input clock. Every cycle

of the input clock equals N

R

/N

F

cycles of the VCO clock.

Figure 5: Simple PLL

Phase

Frequency

Detect

Feedback

Divider (N

F

)

VCO

f

IN

f

OUT

Reference

Divider (N

R

)

f

IN

f

OUT

The addition of a Post Divider, while adding flexibility,

makes the phase relation between the input and output

clock unknown because the Post Divider is outside the

feedback loop.

Figure 6: PLL with Post Divider

Phase

Frequency

Detect

Feedback

Divider (N

F

)

VCO

f

IN

f

OUT

Reference

Divider (N

R

)

f

IN

f

VCO

Post

Divider (N

F

)

f

VCO

f

OUT

?

4.2.1

Clock Gobbler (Phase Adjust)

The Clock Gobbler circuit takes advantage of the un-

known relationship between input and output clocks to

permit the adjustment of the CLKP/CLKN output clock

phase relative to the REF input. The Clock Gobbler circuit

removes a VCO clock pulse before the pulse clocks the

Post Divider. In this way, the phase of the output clock

can be slipped until the output phase is aligned with the

input clock phase.

To adjust the phase relationship, switch the Feedback

Divider source to the Post Divider input via the

FBKDSRC bit, and toggle the GBL register bit. The Clock

Gobbler output clock is delayed by one VCO clock period

for each transition of the GBL bit from zero to one.

4.2.2 Phase

Alignment

To maintain a fixed phase relation between input and

output clocks, the Post Divider must be placed inside the

feedback loop. The source for the Feedback Divider is

obtained from the output of the Post Divider via the

FBKDSRC switch. In addition, the Feedback Divider must

be dividing at a multiple of the Post Divider.

Figure 7: Aligned I/O Phase

Phase

Frequency

Detect

Feedback

Divider (N

F

)

VCO

f

IN

f

OUT

Reference

Divider (N

R

)

Post

Divider (N

F

)

f

IN

f

OUT

4.2.3

Phase Sampling and Initial Alignment

However, the ability to adjust the phase is useless with-

out knowing the initial relation between output and input

phase. To aid in the initial synchronization of the output

phase to input phase, a Phase Align "flag" makes a tran-

sition (zero to one or one to zero) when the output clock

phase becomes aligned with the feedback source phase.

The feedback source clock is, by definition, locked to the

input clock phase.

First, the FS6131 is used to sample the output clock with

the feedback source clock and set/clear the Phase Align

flag when the two clocks match to within a feedback

source clock period. Then, the Clock Gobbler is used to

delay the output phase relative to the input phase one

VCO clock at a time until a transition on the flag occurs.

When a transition occurs, the output and input clocks are

phase aligned.

5

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

To enter this mode, set STAT[1] to one and clear

STAT[0] to zero. If the CMOS bit is set to one, the

LOCK/IPRG pin can display the flag. The flag is always

available under software control by reading back the

STAT[1] bit, which will be overwritten by the flag in this

mode.

4.2.4 Feedback

Divider

Monitoring

The Feedback Divider clock can be brought out the

LOCK/IPRG pin independent of the output clock to allow

monitoring of the Feedback Divider clock. To enter this

mode, set both the STAT[1] and STAT[0] bits to one. The

CMOS bit must also be set to one to enable the

LOCK/IPRG pin as an output.

4.3

Loop Gain Analysis

For applications where an external loop filter is required,

the following analysis example can be used to determine

loop gain and stability.

The loop gain of a PLL is the product of all of the gains

within the loop.

Establish the basic operating parameters:

Set the charge pump current:

A

I

chgpump

µ

10

=

Set the loop filter values:

pF

C

F

C

k

R

LF

220

015

.

0

15

2

1

=

=

=

µ

Set the VCO gain (VCOSPD):

V

MHz

A

VCO

/

230

=

Set the Feedback Divider:

3500

=

F

N

Set the Reference frequency (at the input to the Phase

Detector:

kHz

f

REF

20

=

The transfer function of the Phase Detector and Charge

Pump combination is (in A/rad):

2

chgpump

PD

I

K

=

The transfer function of the loop filter is (in V/A):

˜

˜

˜

˜

¯

ˆ

Á

Á

Á

Á

Ë

Ê

˜

¯

ˆ

Á

Ë

Ê

+

+

=

1

2

1

1

1

)

(

sC

R

sC

s

K

LF

LF

The VCO transfer function (in rad/s, and accounting for

the phase integration that occurs in the VCO) is:

s

A

s

K

VCO

VCO

1

2

)

(

=

The transfer function of the Feedback Divider is:

F

F

N

K

1

=

Finally, the sampling effect that occurs in the Phase De-

tector is accounted for by:

REF

f

s

SAMP

f

s

e

s

K

REF

˜

˜

˜

¯

ˆ

Á

Á

Á

Ë

Ê

-

=

˜

¯

ˆ

Á

Ë

Ê

-

1

)

(

The loop gain of the PLL is:

)

(

)

(

)

(

)

(

s

K

K

s

K

s

K

K

s

K

SAMP

F

VCO

LF

PD

LOOP

=

Figure 8: Loop Gain vs. Frequency

0.01

Frequency (f

i

)

0.1

0.1kHz

1kHz

10kHz

100kHz

1

10

100

Amp

litu

d

e

6

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

The loop phase angle is:

[

]

)

2

(

arg

i

LOOP

i

f

j

K

=

.

Figure 9: Loop Phase vs. Frequency

-150∞

Frequency (f

i

)

-100∞

P

has

e

0.1kHz

1kHz

10kHz

100kHz

A Nyquist plot of gain vs. amplitude is shown below.

Figure 10: Loop Nyquist Plot

45∞

0∞

315∞

270∞

225∞

180∞

135∞

90∞

0.2

0.4

0.6

0.8

1.0

Phase

Amplitude

1.2

Gain Margin

Phase

Margin

4.4

Voltage-Controlled Crystal Oscillator

The VCXO provides a tunable, low-jitter frequency refer-

ence for the rest of the FS6131 system components.

Loading capacitance for the crystal is internal to the de-

vice. No external components (other than the resonator

itself) are required for operation of the VCXO.

The resonator loading capacitance is adjustable under

register control. This feature permits factory coarse tun-

ing of inexpensive resonators to the necessary precision

for digital video applications. Continuous fine-tuning of

the VCXO frequency is accomplished by varying the volt-

age on the XTUNE pin. The total change (from one ex-

treme to the other) in effective loading capacitance is

1.5pF nominal, and the effect is shown in Figure 11. The

oscillator operates the crystal resonator in the parallel-

resonant mode. Crystal warping, or the "pulling" of the

crystal oscillation frequency, is accomplished by altering

the effective load capacitance presented to the crystal by

the oscillator circuit. The actual amount that changing the

load capacitance alters the oscillator frequency will be

dependent on the characteristics of the crystal as well as

the oscillator circuit itself.

The motional capacitance of the crystal (usually referred

to by crystal manufacturers as C

1

), the static capacitance

of the crystal (C

0

), and the load capacitance (C

L

) of the

oscillator determine the warping capability of the crystal

in the oscillator circuit. A simple formula to determine the

total warping capability of a crystal is

(

)

(

) (

)

C

C

C

C

C

C

C

ppm

f

L

L

L

L

1

0

2

0

6

1

2

1

2

10

)

(

+

◊

+

◊

◊

-

◊

=

,

where C

L1

and C

L2

are the two extremes of the applied

load capacitance obtained from Table 11.

Example: A crystal with the following parameters is used

with the FS6131. The total coarse tuning range is:

C

1

=0.02pF, C

0

=5.0pF, C

L1

=10.0pF, C

L2

=22.66pF

(

)

(

) (

)

ppm

.

.

.

f

305

10

5

66

22

5

2

10

10

66

22

02

0

6

=

+

◊

+

◊

◊

-

◊

=

7

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

4.4.1 VCXO

Tuning

The VCXO may be coarse tuned by a programmable ad-

justment of the crystal load capacitance via the XCT[3:0]

control bits. See Table 11 for the control code and the

associated loading capacitance.

The actual amount of frequency warping caused by the

tuning capacitance will depend on the crystal used. The

VCXO tuning capacitance includes an external 6pF load

capacitance (12pF from the XIN pin to ground and 12pF

from the XOUT pin to ground). The fine tuning capability

of the VCXO can be enabled by setting the XLVTEN bit

to a one, or disabled by setting it to a zero.

Figure 11 shows the typical effect of the coarse and fine

tuning mechanisms. The total coarse tune range is about

350ppm. The difference in VCXO frequency in parts per

million (ppm) is shown as the fine tuning voltage on the

XTUNE pin varies from 0V to 5V. Note that as the crystal

load capacitance is increased the VCXO frequency is

pulled somewhat less with each coarse step, and the fine

tuning range decreases. The fine tuning range always

overlaps a few coarse tuning ranges, eliminating the pos-

sibility of holes in the VCXO response. The different

crystal warping characteristics may change the scaling on

the Y-axis, but not the overall characteristic of the curves.

Figure 11: VCXO Coarse and Fine Tuning

VCXO Range (ppm) vs. XTUNE Voltage (V)

-200

-150

-100

-50

0

50

100

150

200

0

1

2

3

4

5

6

7

8

9 10 11 12 13 14 15

Coarse Tune Setting XCT[3:0]

V

C

X

O

Range (

ppm

)

XTUNE Voltage = 0.0V

XTUNE Voltage = 5.0V

4.5 Crystal

Loop

The Crystal Loop is designed to attenuate the jitter on a

highly jittered, low-Q, low frequency reference. The

Crystal Loop can also maintain a constant frequency out-

put into the Main Loop if the low frequency reference is

intermittent.

The Crystal Loop consists of a Voltage-Controllable

Crystal Oscillator (VCXO), a divider, a PFD, and a charge

pump that tunes the VCXO to a frequency reference. The

frequency reference is phase-locked to the divided fre-

quency of an external, high-Q, jitter-free crystal, thereby

locking the VCXO to the reference frequency. The VCXO

can continue to run off the crystal even if the frequency

reference becomes intermittent.

4.5.1

Locking to an External Frequency Source

When the Crystal Loop is synchronized to an external

frequency source, the FS6131 can monitor the Crystal

Loop and detect if the loop unlocks from the external

source. The Crystal Loop tries to drive to zero frequency

if the external source is dropped, and sets a Lock Status

error flag.

The Crystal Loop can also detect if the VCXO has

dropped out of the Fine Tune range, requiring a change

to the Coarse Tune. The Lock Status also latches the

direction the loop went out of range (high or low) when

the loop became unlocked.

4.5.1.1 Crystal Loop Lock Status Flag

To enable this mode, clear the STAT[1] and STAT[0] bits

to zero. If the CMOS bit is set to one, the LOCK/IPRG pin

will be low if the Crystal Loop becomes unlocked. The

flag is always available under software control by reading

back the STAT[1] bit, which is overwritten with a the

status flag (low = unlocked) in this mode (see Table 6).

8

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

4.5.1.2 Out-Of-Range

High/Low

The direction the loop has gone out-of-range can be de-

termined by clearing STAT[1] to zero and setting STAT[0]

bit to one. If the CMOS bit is set to one, the LOCK/IPRG

pin will go high if the Crystal Loop went out of range high.

If the pin goes to a logic-low, the loop went out of range

low.

The out-of-range information is also available under soft-

ware control by reading back the STAT[1] bit, which is

overwritten by the flag (high = out-of-range high, low =

out-of-range low) in this mode. The bit is set or cleared

only if the Crystal Loop loses lock (see Table 6).

4.5.1.3 Crystal

Loop

Disable

The Crystal Loop is disabled by setting the XLPDEN bit

to a logic-high (1). The bit disables the charge pump cir-

cuit in the loop.

Setting the XLPDEN bit low (0) permits the crystal loop to

operate as a control loop.

4.6

Connecting the FS6131 to an

External Reference Frequency

If a crystal oscillator is not used, tie XIN to ground and

shut down the crystal oscillator by setting XLROM[2:0]=1.

The REF and FBK pins do not have pull-up or pull-down

current, but do have a small amount of hysteresis to re-

duce the possibility of extra edges. Signals may be AC-

coupled into these inputs with an external DC-bias circuit

to generate a DC-bias of 2.5V. Any Reference or Feed-

back signal should be square for best results, and the

signals should be rail-to-rail. Unused inputs should be

grounded to avoid unwanted signal injection.

4.7

Differential Output Stage

The differential output stage supports both CMOS and

pseudo-ECL (PECL) signals. The desired output interface

is chosen via the program registers (see Table 4).

If a PECL interface is used, the transmission line is usu-

ally terminated using a ThÈvenin termination. The output

stage can only sink current in the PECL mode, and the

amount of sink current is set by a programming resistor

on the LOCK/IPRG pin. The ratio of IPRG current to out-

put drive current is shown in Figure 12. Source current is

provided by the pull-up resistor that is part of the

ThÈvenin termination.

Figure 12: IPRG to CLKP/CLKN Current

0.0

5.0

10.0

15.0

20.0

25.0

0

20

40

60

80

CLKP/CLKN PECL Output Current (mA)

IP

R

G

Input

C

u

rrent

(

m

A

)

9

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

5.0 I

2

C-bus Control Interface

This device is a read/write slave device

meeting all Philips I

2

C-bus specifications

except a "general call." The bus has to be

controlled by a master device that generates

the serial clock SCL, controls bus access, and generates

the START and STOP conditions while the device works

as a slave. Both master and slave can operate as a

transmitter or receiver, but the master device determines

which mode is activated. A device that sends data onto

the bus is defined as the transmitter, and a device re-

ceiving data as the receiver.

I

2

C-bus logic levels noted herein are based on a percent-

age of the power supply (V

DD

). A logic-one corresponds

to a nominal voltage of V

DD

, while a logic-zero corre-

sponds to ground (V

SS

).

5.1 Bus

Conditions

Data transfer on the bus can only be initiated when the

bus is not busy. During the data transfer, the data line

(SDA) must remain stable whenever the clock line (SCL)

is high. Changes in the data line while the clock line is

high will be interpreted by the device as a START or

STOP condition. The following bus conditions are defined

by the I

2

C-bus protocol.

5.1.1 Not

Busy

Both the data (SDA) and clock (SCL) lines remain high to

indicate the bus is not busy.

5.1.2

START Data Transfer

A high to low transition of the SDA line while the SCL in-

put is high indicates a START condition. All commands to

the device must be preceded by a START condition.

5.1.3

STOP Data Transfer

A low to high transition of the SDA line while SCL is held

high indicates a STOP condition. All commands to the

device must be followed by a STOP condition.

5.1.4 Data

Valid

The state of the SDA line represents valid data if the SDA

line is stable for the duration of the high period of the SCL

line after a START condition occurs. The data on the

SDA line must be changed only during the low period of

the SCL signal. There is one clock pulse per data bit.

Each data transfer is initiated by a START condition and

terminated with a STOP condition. The number of data

bytes transferred between START and STOP conditions

is determined by the master device, and can continue

indefinitely. However, data that is overwritten to the de-

vice after the first eight bytes will overflow into the first

register, then the second, and so on, in a first-in, first-

overwritten fashion.

5.1.5 Acknowledge

When addressed, the receiving device is required to gen-

erate an Acknowledge after each byte is received. The

master device must generate an extra clock pulse to co-

incide with the Acknowledge bit. The acknowledging de-

vice must pull the SDA line low during the high period of

the master acknowledge clock pulse. Setup and hold

times must be taken into account.

The master must signal an end of data to the slave by not

generating and acknowledge bit on the last byte that has

been read (clocked) out of the slave. In this case, the

slave must leave the SDA line high to enable the master

to generate a STOP condition.

5.2 I

2

C-bus Operation

All programmable registers can be accessed randomly or

sequentially via this bi-directional two wire digital inter-

face. The crystal oscillator does not have to run for com-

munication to occur.

The device accepts the following I

2

C-bus commands:

5.2.1 Slave

Address

After generating a START condition, the bus master

broadcasts a seven-bit slave address followed by a R/W

bit. The address of the device is:

A6

A5

A4

A3

A2

A1

A0

1

0

1

1

X

0

0

where X is controlled by the logic level at the ADDR pin.

The variable ADDR bit allows two different FS6131 de-

vices to exist on the same bus. Note that every device on

an I

2

C-bus must have a unique address to avoid bus

conflicts. The default address sets A2 to 0 via the pull-

down on the ADDR pin.

10

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

5.2.2

Random Register Write Procedure

Random write operations allow the master to directly

write to any register. To initiate a write procedure, the

R/W bit that is transmitted after the seven-bit device ad-

dress is a logic-low. This indicates to the addressed slave

device that a register address will follow after the slave

device acknowledges its device address. The register

address is written into the slave's address pointer. Fol-

lowing an acknowledge by the slave, the master is al-

lowed to write eight bits of data into the addressed regis-

ter. A final acknowledge is returned by the device, and

the master generates a STOP condition.

If either a STOP or a repeated START condition occurs

during a Register Write, the data that has been trans-

ferred is ignored.

5.2.3

Random Register Read Procedure

Random read operations allow the master to directly read

from any register. To perform a read procedure, the R/W

bit that is transmitted after the seven-bit address is a

logic-low, as in the Register Write procedure. This indi-

cates to the addressed slave device that a register ad-

dress will follow after the slave device acknowledges its

device address. The register address is then written into

the slave's address pointer.

Following an acknowledge by the slave, the master gen-

erates a repeated START condition. The repeated

START terminates the write procedure, but not until after

the slave's address pointer is set. The slave address is

then resent, with the R/W bit set this time to a logic-high,

indicating to the slave that data will be read. The slave

will acknowledge the device address, and then transmits

the eight-bit word. The master does not acknowledge the

transfer but does generate a STOP condition.

5.2.4

Sequential Register Write Procedure

Sequential write operations allow the master to write to

each register in order. The register pointer is automati-

cally incremented after each write. This procedure is

more efficient than the Random Register Write if several

registers must be written.

To initiate a write procedure, the R/W bit that is transmit-

ted after the seven-bit device address is a logic-low. This

indicates to the addressed slave device that a register

address will follow after the slave device acknowledges

its device address. The register address is written into the

slave's address pointer. Following an acknowledge by the

slave, the master is allowed to write up to eight bytes of

data into the addressed register before the register ad-

dress pointer overflows back to the beginning address.

An acknowledge by the device between each byte of data

must occur before the next data byte is sent.

Registers are updated every time the device sends an

acknowledge to the host. The register update does not

wait for the STOP condition to occur. Registers are

therefore updated at different times during a Sequential

Register Write.

5.2.5

Sequential Register Read Procedure

Sequential read operations allow the master to read from

each register in order. The register pointer is automati-

cally incremented by one after each read. This procedure

is more efficient than the Random Register Read if sev-

eral registers must be read.

To perform a read procedure, the R/W bit that is trans-

mitted after the seven-bit address is a logic-low, as in the

Register Write procedure. This indicates to the addressed

slave device that a register address will follow after the

slave device acknowledges its device address. The reg-

ister address is then written into the slave's address

pointer.

Following an acknowledge by the slave, the master gen-

erates a repeated START condition. The repeated

START terminates the write procedure, but not until after

the slave's address pointer is set. The slave address is

then resent, with the R/W bit set this time to a logic-high,

indicating to the slave that data will be read. The slave

will acknowledge the device address, and then transmits

all eight bytes of data starting with the initial addressed

register. The register address pointer will overflow if the

initial register address is larger than zero. After the last

byte of data, the master does not acknowledge the

transfer but does generate a STOP condition.

11

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Figure 13: Random Register Write Procedure

A

A

DATA

W A

From bus host

to device

S

REGISTER ADDRESS

P

From device

to bus host

DEVICE ADDRESS

Register Address

Acknowledge

STOP Condition

Data

Acknowledge

Acknowledge

START

Command

WRITE Command

7-bit Receive

Device Address

Figure 14: Random Register Read Procedure

A

R

A

A

A

W

S

REGISTER ADDRESS

P

S

DEVICE ADDRESS

START

Command

WRITE Command

Acknowledge

Register Address

Acknowledge

READ Command

Acknowledge

Data

NO Acknowledge

STOP Condition

From bus host

to device

From device

to bus host

7-bit Receive

Device Address

7-bit Receive

Device Address

DEVICE ADDRESS

DATA

Repeat START

Figure 15: Sequential Register Write Procedure

A

A

A

W

S

P

START

Command

WRITE Command

Acknowledge

Register Address

Acknowledge

Data

Data

Acknowledge

Data

STOP Command

Acknowledge

Acknowledge

From bus host

to device

From device

to bus host

7-bit Receive

Device Address

DEVICE ADDRESS

A

A

REGISTER ADDRESS

DATA

DATA

DATA

Figure 16: Sequential Register Read Procedure

A

W

S

START

Command

WRITE Command

Acknowledge

Register Address

Acknowledge

Data

Acknowledge

Data

STOP Command

Acknowledge

READ Command

NO Acknowledge

From bus host

to device

From device

to bus host

7-bit Receive

Device Address

7-bit Receive

Device Address

DEVICE ADDRESS

A

A

REGISTER ADDRESS

A

R

A P

S

DEVICE ADDRESS

DATA

DATA

Repeat START

12

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

6.0 Programming

Information

All register bits are cleared to zero on power-up. All register bits may be read back as written except STAT[1] (Bit 63).

Table 3: Register Map

ADDRESS

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

STAT[1]

(Bit 63)

STAT[0]

(Bit 62)

XLVTEN

(Bit 61)

CMOS

(Bit 60)

XCT[3]

(Bit 59)

XCT[2]

(Bit 58)

XCT[1]

(Bit 57)

XCT[0]

(Bit 56)

00 = Crystal Loop ≠ Lock Status

01 = Crystal Loop ≠ Out of Range

0 = Fine Tune

Inactive

0 = PECL

10 = Main Loop ≠ Phase Status

BYTE 7

11 = Feedback Divider Output

1 = Fine Tune

Active

1 = CMOS, Lock

Status

VCXO Coarse Tune

See Table 11

XLPDEN

(Bit 55)

XLSWAP

(Bit 54)

XLCP[1]

(Bit 53)

XLCP[0]

(Bit 52)

XLROM[2]

(Bit 51)

XLROM[1]

(Bit 50)

XLROM[0]

(Bit 49)

GBL

(Bit 48)

00 = 1.5

µ

A

0 = Crystal Loop

Operates

0 = Use with

External VCXO

01 = 5

µ

A

0 = No Clock

Phase Adjust

10 = 8

µ

A

BYTE 6

1 = Crystal Loop

Powered Down

1 = Use with

Internal VCXO

11 = 24

µ

A

Crystal Loop Control

See Table 10

1 = Clock Phase

Delay

OUTMUX[1]

(Bit 47)

OUTMUX[0]

(Bit 46)

OSCTYPE

(Bit 45)

VCOSPD

(Bit 44)

LFTC

(Bit 43)

EXTLF

(Bit 42)

MLCP[1]

(Bit 41)

MLCP[0]

(Bit 40)

00 = VCO Output

00 = 1.5

µ

A

01 = Reference Divider Output

0 = Low Phase

Jitter Oscillator

0 = High Speed

Range

0 = Short Time

Constant

0 = Internal Loop

Filter

01 = 5

µ

A

10 = Phase Detector Input

10 = 8

µ

A

BYTE 5

11 = VCXO Output

1 = FS6031

Oscillator

1 = Low Speed

Range

1 = Long Time

Constant

1 = External Loop

Filter

11 = 24

µ

A

FBKDSRC[1]

(Bit 39)

FBKDSRC[0]

(Bit 38)

FBKDIV[13]

(Bit 37)

FBKDIV[12]

(Bit 36)

FBKDIV[11]

(Bit 35)

FBKDIV[10]

(Bit 34)

FBKDIV[9]

(Bit 33)

FBKDIV[8]

(Bit 32)

00 = Post Divider Output

01 = FBK Pin

8192

4096

2048

1024

512

256

10 = Post Divider Input

BYTE 4

11 = FBK Pin

M Counter

FBKDIV[7]

(Bit 31)

FBKDIV[6]

(Bit 30)

FBKDIV[5]

(Bit 29)

FBKDIV[4]

(Bit 28)

FBKDIV[3]

(Bit 27)

FBKDIV[2]

(Bit 26)

FBKDIV[1]

(Bit 25)

FBKDIV[0]

(Bit 24)

128

64

32

16

8

4

2

1

BYTE 3

M Counter

A Counter ≠ See Table 2

POST3[1]

(Bit 21)

POST3[1]

(Bit 20)

POST2[1]

(Bit 19)

POST2[0]

(Bit 18)

POST1[1]

(Bit 17)

POST1[0]

(Bit 16)

00 = Divide by 1

00 = Divide by 1

00 = Divide by 1

01 = Divide by 3

01 = Divide by 3

01 = Divide by 2

10 = Divide by 5

10 = Divide by 5

10 = Divide by 4

BYTE 2

Reserved (0)

Reserved (0)

11 = Divide by 4

11 = Divide by 4

11 = Divide by 8

PDFBK

(Bit 15)

PDREF

(Bit 14)

SHUT

(Bit 13)

REFDSRC

(Bit 12)

REFDIV[11]

(Bit 11)

REFDIV[10]

(Bit 10)

REFDIV[9]

(Bit 9)

REFDIV[8]

(Bit 8)

0 = Feedback

Divider

0 = Reference

Divider

0 = Main Loop

Operates

0 = VCXO

BYTE 1

1 = FBK Pin

1 = REF Pin

1 = Main Loop

Powered Down

1 = Ref Pin

2048

1024

512

256

REFDIV[7]

(Bit 7)

REFDIV[6]

(Bit 6)

REFDIV[5]

(Bit 5)

REFDIV[4]

(Bit 4)

REFDIV[3]

(Bit 3)

REFDIV[2]

(Bit 2)

REFDIV[1]

(Bit 1)

REFDIV[0]

(Bit 0)

BYTE 0

128

64

32

16

8

4

2

1

13

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Table 4: Device Configuration Bits

NAME

DESCRIPTION

REFerence Divider SouRCe

Bit = 0

Crystal Oscillator (VCXO)

REFDSRC

(Bit 12)

Bit = 1

REF pin

main loop SHUT down select

Bit = 0

Disabled (main loop operates)

SHUT

(Bit 13)

Bit = 1

Enabled (main loop shuts down)

Phase Detector REFerence source

Bit = 0

Reference Divider

PDREF

(Bit 14)

Bit = 1

REF pin

Phase Detector FeedBacK source

Bit = 0

Feedback Divider

PDFBK

(Bit 15)

Bit = 1

FBK pin

FeedBacK Divider SouRCe

Bit 39 = 0

Bit 38 = 0

Post Divider Output

Bit 39 = 0

Bit 38 = 1

FBK pin

Bit 39 = 1

Bit 38 = 0

VCO Output (Post Divider Input)

FBKDSRC[1:0]

(Bits 39-38)

Bit 39 = 1

Bit 38 = 1

FBK pin

EXTernal Loop Filter select

Bit = 0

Internal Loop Filter

EXTLF

(Bit 42)

Bit = 1

EXTLF pin

OSCillator TYPe

Bit = 0

Low Phase Jitter Oscillator

OSCTYPE

(Bit 45)

Bit = 1

FS6031 Compatible Oscillator

OUTput MUltipleXer select

Bit 47 = 0

Bit 46 = 0

Main Loop PLL (VCO Output)

Bit 47 = 0

Bit 46 = 1

Reference Divider Output

Bit 47 = 1

Bit 46 = 0

Phase Detector Input

OUTMUX[1:0]

(Bits 47-46)

Bit 47 = 1

Bit 46 = 1

VCXO Output

clock GobBLer control

Bit = 0

No Clock Phase Adjust

GBL

(Bit 48)

Bit = 1

Clock Phase Delay

CLKP/CLKN output mode

Bit = 0

PECL Output

(positive-ECL output drive)

CMOS

(Bit 60)

Bit = 1

CMOS Output /

Lock Status Indicator

Table 5: LOCK/IPRG Pin Configuration Bits

NAME

DESCRIPTION

crystal loop lock STATus mode /

main loop phase align STATus mode

(see also Table 6)

Bit 63 = 0

Bit 62 = 0

Crystal Loop Lock status:

Locked or Unlocked

Bit 63 = 0

Bit 62 = 1

Crystal Loop Lock status:

Out of Range High or Low

Bit 63 = 1

Bit 62 = 0

Main Loop Phase Align status

STAT[1:0]

(Bits 63-62)

Bit 63 = 1

Bit 62 = 1

Feedback Divider output

Table 6: Lock Status

CMOS

STAT

[1]

STAT

[0]

LOCK /

IPRG PIN

STAT[1]

READ

STATUS

1

1

Locked

1

0

0

0

0

Unlocked

0

0

Out-of-

Range: Low

1

0

1

1

1

Out-of-

Range: High

Table 7: Main Loop Tuning Bits

NAME

DESCRIPTION

VCO SPeeD range select (see Table 16)

Bit = 0

High Speed Range

VCOSPD

(Bit 44)

Bit = 1

Low Speed Range

Main Loop Charge Pump current

Bit 41 = 0

Bit 40 = 0

Current = 1.5

µ

A

Bit 41 = 0

Bit 40 = 1

Current = 5

µ

A

Bit 41 = 1

Bit 40 = 0

Current = 8

µ

A

MLCP[1:0]

(Bits 41-40)

Bit 41 = 1

Bit 40 = 1

Current = 24

µ

A

Loop Filter Time Constant (internal)

Bit = 0

Short Time Constant: 13.5

µ

s

LFTC

(Bit 43)

Bit = 1

Long Time Constant: 135

µ

s

14

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Table 8: Divider Control Bits

NAME

DESCRIPTION

REFDIV[11:0]

(Bits 11-0)

REFerence DIVider (N

R

)

FeedBacK DIVider (N

F

)

FBKDIV[2:0]

A-Counter Value

FBKDIV[13:0]

(Bits 37-24)

FBKDIV[13:3]

M-Counter Value

POST Divider #1 (N

P1

)

Bit 17 = 0

Bit 16 = 0

Divide by 1

Bit 17 = 0

Bit 16 = 1

Divide by 2

Bit 17 = 1

Bit 16 = 0

Divide by 4

POST1[1:0]

(Bits 17-16)

Bit 17 = 1

Bit 16 = 1

Divide by 8

POST Divider #2 (N

P2

)

Bit 19 = 0

Bit 18 = 0

Divide by 1

Bit 19 = 0

Bit 18 = 1

Divide by 3

Bit 19 = 1

Bit 18 = 0

Divide by 5

POST2[1:0]

(Bits 19-18)

Bit 19 = 1

Bit 18 = 1

Divide by 4

POST Divider #3 (N

P3

)

Bit 21 = 0

Bit 20 = 0

Divide by 1

Bit 21 = 0

Bit 20 = 1

Divide by 3

Bit 21 = 1

Bit 20 = 0

Divide by 5

POST3[1:0]

(Bits 21-20)

Bit 21 = 1

Bit 20 = 1

Divide by 4

Reserved (0)

(Bits 23-22)

Set these reserved bits to 0

Table 9: Crystal Loop Tuning Bits

NAME

DESCRIPTION

Crystal Loop Charge Pump current

Bit 53 = 0

Bit 52 = 0

Current = 1.5

µ

A

Bit 53 = 0

Bit 52 = 1

Current = 5

µ

A

Bit 53 = 1

Bit 52 = 0

Current = 8

µ

A

XLCP[1:0]

(Bits 53-52)

Bit 53 = 1

Bit 52 = 1

Current = 24

µ

A

XLROM[2:0]

(Bits 51-49)

Crystal Loop Divider ROM select and Crystal

Oscillator Power-Down (see Table 10)

Crystal Loop Voltage fine Tune ENable

Bit = 0

Disabled (fine tune is inactive)

XLVTEN

(Bit 61)

Bit = 1

Enabled (fine tune is active)

Crystal Loop SWAP polarity

Bit = 0

Use with an external VCXO that

increases in frequency in re-

sponse to an increasing voltage

at the XTUNE pin.

XLSWAP

(Bit 54)

Bit = 1

Use with a VCXO that increases

in frequency in response to a

decreasing voltage at the XTUNE

pin.

Use this setting for Internal

VCXO

Crystal Loop Power Down Enable

Bit = 0

Disabled (crystal loop operates)

XLPDEN

(Bit 55)

Bit = 1

Enabled

(crystal loop is powered down)

XCT[3:0]

(Bits 59-56)

Crystal Coarse Tune (see Table 11)

Table 10: Crystal Loop Control ROM

XLROM

[2]

XLROM

[1]

XLROM

[0]

VCXO

DIVIDER

CRYSTAL

FREQUENCY (MHz)

0

0

0

1

-

0

0

1

3072

24.576

0

1

0

3156

25.248

0

1

1

2430

19.44

1

0

0

2500

20.00

1

0

1

4000

32.00

1

1

0

3375

27.00

1

1

1

Crystal Oscillator Power-Down

15

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

6.1

VCXO Coarse Tune

The VCXO may be coarse tuned by a programmable ad-

justment of the crystal load capacitance via XCT[3:0].

The actual amount of frequency warping caused by the

tuning capacitance will depend on the crystal used. The

VCXO tuning capacitance includes an external 6pF load

capacitance (12pF from the XIN pin to ground and 12pF

from the XOUT pin to ground). The fine tuning capability

of the VCXO can be enabled by setting the XLVTEN bit

to a logic-one, or disabled by setting the bit to a logic-

zero.

Table 11: VCXO Coarse Tuning Capacitance

XCT[3]

XCT[2]

XCT[1]

XCT[0]

VCXO TUNING

CAPACITANCE (pF)

0

0

0

0

10.00

0

0

0

1

10.84

0

0

1

0

11.69

0

0

1

1

12.53

0

1

0

0

13.38

0

1

0

1

14.22

0

1

1

0

15.06

0

1

1

1

15.91

1

0

0

0

16.75

1

0

0

1

17.59

1

0

1

0

18.43

1

0

1

1

19.28

1

1

0

0

20.13

1

1

0

1

20.97

1

1

1

0

21.81

1

1

1

1

22.66

16

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

7.0 Electrical

Specifications

Table 12: Absolute Maximum Ratings

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These conditions represent a stress rating only, and functional operation of the device at

these or any other conditions above the operational limits noted in this specification is not implied. Exposure to maximum rating conditions for extended conditions may affect device performance,

functionality, and reliability.

PARAMETER

SYMBOL

MIN.

MAX.

UNITS

Supply Voltage, dc (V

SS

= ground)

V

DD

V

SS

-0.5

7

V

Input Voltage, dc

V

I

V

SS

-0.5

V

DD

+0.5

V

Output Voltage, dc

V

O

V

SS

-0.5

V

DD

+0.5

V

Input Clamp Current, dc (V

I

< 0 or V

I

> V

DD

)

I

IK

-50

50

mA

Output Clamp Current, dc (V

I

< 0 or V

I

> V

DD

)

I

OK

-50

50

mA

Storage Temperature Range (non-condensing)

T

S

-65

150

∞C

Ambient Temperature Range, Under Bias

T

A

-55

125

∞C

Junction Temperature

T

J

150

∞C

Lead Temperature (soldering, 10s)

260

∞C

Input Static Discharge Voltage Protection (MIL-STD 883E, Method 3015.7)

2

kV

CAUTION: ELECTROSTATIC SENSITIVE DEVICE

Permanent damage resulting in a loss of functionality or performance may occur if this device is subjected to a high-energy elec-

trostatic discharge.

Table 13: Operating Conditions

PARAMETER

SYMBOL

CONDITIONS/DESCRIPTION

MIN.

TYP.

MAX.

UNITS

Supply Voltage

V

DD

5V ± 10%

4.5

5

5.5

V

Ambient Operating Temperature Range

T

A

0

70

∞C

Crystal Resonator Frequency

f

XIN

19.44

27

28

MHz

Crystal Resonator Load Capacitance

C

XL

Parallel resonant, AT cut

18

pF

Crystal Resonator Motional Capacitance

C

XM

Parallel resonant, AT cut

25

fF

Serial Data Transfer Rate

Standard mode

10

100

400

kb/s

PECL Mode Programming Current

(LOCK/IPRG Pin High-Level Input Current)

I

IH

PECL Mode

15

mA

Output Driver Load Capacitance

C

L

15

pF

17

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Table 14: DC Electrical Specifications

Unless otherwise stated, V

DD

= 5.0V ± 10%, no load on any output, and ambient temperature range T

A

= 0∞C to 70∞C. Parameters denoted with an asterisk ( * ) represent nominal characterization

data and are not production tested to any specific limits. MIN and MAX characterization data are

±

3

from typical. Negative currents indicate current flows out of the device.

PARAMETER

SYMBOL

CONDITIONS/DESCRIPTION

MIN.

TYP.

MAX.

UNITS

Overall

Supply Current, Dynamic,

(with Loaded Outputs)

I

DD

f

CLK

= 66MHz; CMOS Mode, V

DD

= 5.5V

100

mA

Supply Current, Static

I

DDL

SHUT = 1, XLROM[2:0] = 7, XLPDEN = 1

V

DD

= 5.5V

12

mA

Serial Communication I/O (SDA, SCL)

High-Level Input Voltage

V

IH

Outputs off

3.5

V

DD

+0.3

V

Low-Level Input Voltage

V

IL

Outputs off

V

SS

-0.3

1.5

V

Hysteresis Voltage *

V

hys

Outputs off

2

V

Input Leakage Current

I

I

-1

1

µ

A

Low-Level Output Sink Current (SDA)

I

OL

V

OL

= 0.4V

20

32

mA

Tristate Output Current

I

Z

-10

10

µ

A

Address Select Input (ADDR)

High-Level Input Voltage

V

IH

2.4

V

DD

+0.3

V

Low-Level Input Voltage

V

IL

V

SS

-0.3

0.8

V

High-Level Input Current (pull-down)

I

IH

V

IH

= V

DD

= 5.5V

5

16

30

µ

A

Low-Level Input Current

I

IL

-2

2

µ

A

Reference Frequency Input (REF, FBK)

High-Level Input Voltage

V

IH

3.5

V

DD

+0.3

V

Low-Level Input Voltage

V

IL

V

SS

-0.3

1.5

V

Hysteresis Voltage

V

hys

500

mV

Input Leakage Current

I

I

-1

1

µ

A

Loop Filter Input (EXTLF)

Input Leakage Current

I

I

EXTLF = 0

-1

1

µ

A

V

O

= 0.8V; EXTLF =1, MLCP[1:0] = 0

-1.5

V

O

= 0.8V; EXTLF =1, MLCP[1:0] = 1

-5

V

O

= 0.8V; EXTLF =1, MLCP[1:0] = 2

-8

High-Level Output Source Current

I

OH

V

O

= 0.8V; EXTLF =1, MLCP[1:0] = 3

-24

µ

A

V

O

= 4.2V; EXTLF =1, MLCP[1:0] = 0

1.5

V

O

= 4.2V; EXTLF =1, MLCP[1:0] = 1

5

V

O

= 4.2V; EXTLF =1, MLCP[1:0] = 2

8

Low-Level Output Sink Current

I

OL

V

O

= 4.2V; EXTLF =1, MLCP[1:0] = 3

25

µ

A

Crystal Oscillator Input (XIN)

Threshold Bias Voltage

V

TH

1.5

2.2

3.5

V

High-Level Input Current

I

IH

Outputs off; V

IH

= 5V

10

24

30

mA

Low-Level Input Current

I

IL

Outputs off; V

IL

= 0V

-10

-19

-30

mA

Crystal Loading Capacitance *

C

L(xtal)

As seen by an external crystal connected

to XIN and XOUT; VCXO tuning disabled

10

pF

Input Loading Capacitance *

C

L(XIN)

As seen by an external clock driver on

XOUT; XIN unconnected; VCXO disabled

20

pF

18

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Table

15: DC Electrical Specifications, continued

Unless otherwise stated, V

DD

= 5.0V ± 10%, no load on any output, and ambient temperature range T

A

= 0∞C to 70∞C. Parameters denoted with an asterisk ( * ) represent nominal characterization

data and are not production tested to any specific limits. MIN and MAX characterization data are

±

3

from typical. Negative currents indicate current flows out of the device.

PARAMETER

SYMBOL

CONDITIONS/DESCRIPTION

MIN.

TYP.

MAX.

UNITS

Crystal Oscillator Output (XOUT)

High-Level Output Source Current

I

OH

V

O

= 0V, float XIN

-20

-30

-50

mA

Low-Level Output Sink Current

I

OL

V

O

= 5V, float XIN

-20

-40

-50

mA

VCXO Tuning I/O (XTUNE)

High-Level Input Voltage

V

IH

Lock Status: Out of Range HIGH

3.2

V

DD

+0.3

V

Low-Level Input Voltage

V

IL

Lock Status: Out of Range LOW

V

SS

-0.3

0.3

V

Hysteresis Voltage

V

hys

1.0

V

Input Leakage Current

I

I

XLPDEN = 0

-1

1

µ

A

V

O

= 0.8V; XLCP[1:0] = 0

-1.5

V

O

= 0.8V; XLCP[1:0] = 1

-5

V

O

= 0.8V; XLCP[1:0] = 2

-8

High-Level Output Source Current

I

OH

V

O

= 0.8V; XLCP[1:0] = 3

-24

µ

A

V

O

= 4.2V; XLCP[1:0] = 0

1.5

V

O

= 4.2V; XLCP[1:0] = 1

5

V

O

= 4.2V; XLCP[1:0] = 2

8

Low-Level Output Sink Current

I

OL

V

O

= 4.2V; XLCP[1:0] = 3

25

µ

A

Lock Indicator / PECL Current Program I/O (LOCK/IPRG)

Low-Level Input Current

I

IL

PECL Mode

-1

1

µ

A

High-Level Output Source Current

I

OH

CMOS Mode; V

O

= 2.4V

-25

-38

mA

Low-Level Output Sink Current

I

OL

CMOS Mode; V

O

= 0.4V

5

9

mA

z

OH

V

O

= 0.5V

DD

; output driving high

66

Output Impedance *

z

OL

V

O

= 0.5V

DD

; output driving low

76

Short Circuit Source Current *

I

SCH

V

O

= 0V; shorted for 30s, max.

-47

mA

Short Circuit Sink Current *

I

SCL

V

O

= 5V; shorted for 30s, max.

47

mA

Clock Outputs, CMOS Mode (CLKN, CLKP)

High-Level Output Source Current

I

OH

V

O

= 2.4V

-45

-68

mA

Low-Level Output Sink Current

I

OL

V

O

= 0.4V

15

20

mA

z

OH

V

O

= 0.5V

DD

; output driving high

28

Output Impedance *

z

OL

V

O

= 0.5V

DD

; output driving low

33

Short Circuit Source Current *

I

SCH

V

O

= 0V; shorted for 30s, max.

-100

mA

Short Circuit Sink Current *

I

SCL

V

O

= 5V; shorted for 30s, max.

100

mA

Clock Outputs, PECL Mode (CLKN, CLKP)

IPRG Current to Output Current Ratio

1:4

Low-Level Output Sink Current

I

OL

IPRG input current = 15mA

60

mA

Tristate Output Current

I

Z

-10

10

µ

A

19

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Table 16: AC Timing Specifications

Unless otherwise stated, V

DD

= 5.0V ± 10%, no load on any output, and ambient temperature range T

A

= 0∞C to 70∞C. Parameters denoted with an asterisk ( * ) represent nominal characterization

data and are not production tested to any specific limits. MIN and MAX characterization data are

±

3

from typical.

PARAMETER

SYMBOL

CONDITIONS/DESCRIPTION

CLOCK

(MHz)

MIN.

TYP.

MAX.

UNITS

Overall

CMOS Outputs

130

Output Frequency *

f

O(max)

PECL Outputs

230

MHz

Low Phase Jitter Oscillator (OSCTYPE = 0)

VCOSPD = 0

40

160

VCOSPD = 1

40

100

FS6031 Compatible Oscillator (OSCTYPE = 1)

VCOSPD = 0

40

230

VCO Frequency *

f

VCO

VCOSPD = 1

40

140

MHz

Low Phase Jitter Oscillator (OSCTYPE = 0)

VCOSPD = 0

125

VCOSPD = 1

75

FS6031 Compatible Oscillator (OSCTYPE = 1)

VCOSPD = 0

130

VCO Gain *

A

VCO

VCOSPD = 1

78

MHz/V

LFTC = 0

13.5

Loop Filter Time Constant *

LFTC = 1

135

µ

s

Rise Time *

t

r

CMOS Outputs, V

O

= 0.5V to 4.5V; C

L

= 15pF

1.1

ns

Fall Time *

t

f

CMOS Outputs, V

O

= 4.5V to 0.5V; C

L

= 15pF

0.8

ns

Frequency Synthesis

200

µ

s

Lock Time (Main Loop) *

Line Locked Modes (8kHz reference)

10

ms

Disable Time *

From falling edge of SCL for the last data bit

(SHUT = 1 to 0) to output locked

10

µ

s

Divider Modulus

Feedback Divider

N

F

FBKDIV[13:0] (See also Table 2)

8

16383

Reference Divider

N

R

REFDIV[11:0]

1

4095

N

P1

POST1[1:0] (See also Table 8)

1

8

N

P2

POST2[1:0] (See also Table 8)

1

5

Post Divider

N

P3

POST3[1:0] (See also Table 8)

1

5

20

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Table 17: AC Timing Specifications, continued

Unless otherwise stated, V

DD

= 5.0V ± 10%, no load on any output, and ambient temperature range T

A

= 0∞C to 70∞C. Parameters denoted with an asterisk ( * ) represent nominal characterization

data at T

A

= 27∞C and are not production tested to any specific limits. MIN and MAX characterization data are

±

3

from typical.

PARAMETER

SYMBOL

CONDITIONS/DESCRIPTION

CLOCK

(MHz)

MIN.

TYP.

MAX.

UNITS

Clock Output (CLKP, CLKN)

Duty Cycle *

Ratio of pulse width (as measured from rising edge to next falling

edge at 2.5V) to one clock period

100

47

54

%

Rising edges 50ms apart at 2.5V, relative to an ideal clock,

C

L

=15pF, f

REF

=8kHz, N

R

=1, N

F

=193, N

Px

=64, C

LF

=0.054

µ

F,

R

LF

=15.7k

, C

LP

=1800pF, OSCTYPE=0, MLCP=3, XLROM=7

1.544

270

Rising edges 50ms apart at 2.5V, relative to an ideal clock,

C

L

=15pF, f

REF

=15kHz, N

R

=1, N

F

=800, N

Px

=10, C

LF

=0.0246

µ

F,

R

LF

=15.7k

, C

LP

=820pF, OSCTYPE=0, MLCP=3, XLROM=7

12.00

160

On rising edges 5ms apart at 2.5V relative to an ideal clock,

C

L

=15pF, f

REF

=31.5kHz, N

R

=1, N

F

=799, N

Px

=4, C

LF

=0.015

µ

F,

R

LF

=15.7k

, C

LP

=470pF, OSCTYPE=0, MLCP=3, XLROM=7

25.175

100

On rising edges 500

µ

s apart at 2.5V relative to an ideal clock,

C

L

=15pF, CMOS mode, f

XIN

=27MHz, N

F

=200, N

R

=27, N

Px

=2

100

30

Jitter, Long Term (

y

(

)) *

t

j(LT)

On rising edges 500

µ

s apart at 2.5V relative to an ideal clock,

C

L

=15pF, PECL mode, f

XIN

=27MHz, N

F

=200, N

R

=27, N

Px

=1

200

30

ps

From rising edge to next rising edge at 2.5V, C

L

=15pF,

f

REF

=8kHz, N

R

=1, N

F

=193, N

Px

=64, C

LF

=0.054

µ

F, R

LF

=15.7k

,

C

LP

=1800pF, OSCTYPE=0, MLCP=3, XLROM=7

1.544

140

From rising edge to next rising edge at 2.5V, C

L

=15pF,

f

REF

=15kHz, N

R

=1, N

F

=800, N

Px

=10, C

LF

=0.0246

µ

F, R

LF

=15.7k

,

C

LP

=820pF, OSCTYPE=0, MLCP=3, XLROM=7

12.00

130

From rising edge to next rising edge at 2.5V, C

L

=15pF,

f

REF

=31.5kHz, N

R

=1, N

F

=799, N

Px

=4, C

LF

=0.015

µ

F, R

LF

=15.7k

,

C

LP

=470pF, OSCTYPE=0, MLCP=3, XLROM=7

25.175

105

From rising edge to next rising edge at 2.5V, C

L

=15pF,

CMOS mode, f

XIN

=27MHz, N

F

=200, N

R

=27, N

Px

=2

100

340

Jitter, Period (peak-peak) *

t

j(

P)

From rising edge to next rising edge at 2.5V, C

L

=15pF,

PECL mode, f

XIN

=27MHz, N

F

=200, N

R

=27, N

Px

=1

200

270

ps

21

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Table 18: Serial Interface Timing Specifications

Unless otherwise stated, V

DD

= 5.0V ± 10%, no load on any output, and ambient temperature range T

A

= 0∞C to 70∞C. Parameters denoted with an asterisk ( * ) represent nominal characterization

data and are not production tested to any specific limits. MIN and MAX characterization data are

±

3

from typical.

STANDARD MODE

PARAMETER

SYMBOL

CONDITIONS/DESCRIPTION

MIN.

MAX.

UNITS

Clock frequency

f

SCL

SCL

0

400

kHz

Bus free time between STOP and START

t

BUF

4.7

µ

s

Set up time, START (repeated)

t

su:STA

4.7

µ

s

Hold time, START

t

hd:STA

4.0

µ

s

Set up time, data input

t

su:DAT

SDA

250

ns

Hold time, data input

t

hd:DAT

SDA

0

µ

s

Output data valid from clock

t

AA

Minimum delay to bridge undefined region of the falling

edge of SCL to avoid unintended START or STOP

3.5

µ

s

Rise time, data and clock

t

R

SDA, SCL

1000

ns

Fall time, data and clock

t

F

SDA, SCL

300

ns

High time, clock

t

HI

SCL

4.0

µ

s

Low time, clock

t

LO

SCL

4.7

µ

s

Set up time, STOP

t

su:STO

4.0

µ

s

Figure 17: Bus Timing Data

SCL

SDA

~ ~

~ ~

~ ~

STOP

t

su:STO

t

hd:STA

START

t

su:STA

ADDRESS OR

DATA VALID

DATA CAN

CHANGE

Figure 18: Data Transfer Sequence

SCL

SDA

IN

t

hd:DAT

~ ~

t

hd:STA

t

su:STA

t

su:STO

t

LO

t

HI

SDA

OUT

t

su:DAT

~ ~

~ ~

t

BUF

t

R

t

F

t

AA

t

AA

22

FS6131-01

FS6131-01

FS6131-01

FS6131-01

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Programmable Line Lock Clock Generator IC

Table 19: CLKP, CLKN Clock Outputs (CMOS Mode)

Low Drive Current (mA)

High Drive Current (mA)

Voltage

(V)

MIN.

TYP.

MAX.

Voltage

(V)

MIN.

TYP.

MAX.