05/2005

ARA05050

Reverse Amplifier with Step Attenuator

Data Sheet - Rev 2.2

FEATURES

∑

Low Cost Integrated Monolothic GaAs Amplifier

With Step Attenuator

∑

Attenuation Range: 0-30 dB, Adjustable In

2dB Increments Via a 4 Wire Parallel Control

∑

Meets DOCSIS Distortion Requirements at

+58dBmV Output Signal Level

∑

Low Distortion and Low Noise

∑

Low Signal toNoise Ratio at All Gain Levels

∑

Frequency Range: 5-100 MHz

∑

5 Volt Operation

∑

RoHS-Compliant Package Option

APPLICATIONS

∑

MCNS/DOCSIS Compliant Cable Modems

∑

CATV Interactive Set-Top Box

∑

OpenCable Set-Top Box

∑

Fiber Nodes

∑

Cable Modem Termination Systems (CMTS)

PRODUCT DESCRIPTION

The ARA05050 is a GaAs IC designed to provide the

reverse path amplification and output level control

functions in a CATV Set-Top Box or Cable Modem. It

incorporates a digitally controlled precision step

attenuator that is preceded by an ultra low noise

amplifier stage, and followed by an ultra-linear output

driver amplifier. This device is capable of meeting

the MCNS/DOCSIS requirements for harmonic

Figure 1. Cable Modem or Set Top Box Application Diagram

S12 Package

28 Pin SSOP with Heat Slug

Diplexer

ARA05050

SAW

Filter

Double-

Conversion

Tuner

MAC

Upstream

QPSK/16QAM

Modulator

QAM Receiver

with FEC

Balun

Transmit Enable/Disable

Attenuation Control

Microcontroller

with Ethernet

MAC

RAM

ROM

10Base-T

Transceiver

RJ45

Connector

Clock

Clock

Data

Data

54-860 MHz

44 MHz

5-42 MHz

4

LPF

Switch

performance at a +58dBmV output level while

requiring only a single polarity +5V supply. Both the

input and the output are single-ended and matched

to 75 Ohms. The precision attenuator provides up to

30 dB of attenuation in 2 dB increments. The

ARA05050 is offered in a 28-pin SSOP package that

features a heat slug on the bottom of the package,

and is available in a RoHS-compliant option.

2

Data Sheet - Rev 2.2

05/2005

ARA05050

Figure 2: Functional Block Diagram

Figure 3: Pinout

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

GND

I

SET1

ATT

OUT

ATT

ACG1

RF

IN2

V

REF1

RF

OUT1

ATT

IN

16 dB

V

ATT

8 dB

RF

IN

I

SET2

RF

OUT

Bypass

2 dB

N/C

4 dB

ATT

ACG1

ATT

ACG1

ATT

ACG1

V

REF2

ATT

ACG2

ATT

ACG2

ATT

ACG2

ATT

ACG2

N/C

N/C

RF

IN

RF

OUT

I

SET2

I

SET1

16 dB

2 dB

4 dB

8 dB

RF

IN2

RF

OUT1

ATT

OUT

ATT

IN

A1

A2

30 dB, 2dB step digital attenuator section

4

Data Sheet - Rev 2.2

05/2005

ARA05050

ELECTRICAL CHARACTERISTICS

R

E

T

E

M

A

R

A

P

N

I

M

X

A

M

T

I

N

U

V

:

y

l

p

p

u

S

g

o

l

a

n

A

SUP

)

8

1

,

2

1

,

4

s

n

i

p

(

0

9

C

D

V

)

9

1

,

5

s

n

i

p

(

s

e

g

a

tl

o

V

e

c

n

e

r

e

f

e

R

r

e

if

il

p

m

A

5

.

2

-

V

SUP

2

C

D

V

F

R

s

t

u

p

n

I

r

e

if

il

p

m

A

t

a

r

e

w

o

P

s

n

i

p

(

4

2

,

0

1

)

-

0

6

+

V

m

B

d

)

6

1

,

5

1

,

4

1

,

3

1

s

n

i

p

(

s

l

o

r

t

n

o

C

r

o

t

a

u

n

e

tt

A

0

6

V

e

r

u

t

a

r

e

p

m

e

T

e

g

a

r

o

t

S

5

5

-

0

0

2

+

o

C

e

r

u

t

a

r

e

p

m

e

T

g

n

ir

e

d

l

o

S

-

0

6

2

o

C

e

m

i

T

g

n

ir

e

d

l

o

S

-

5

c

e

S

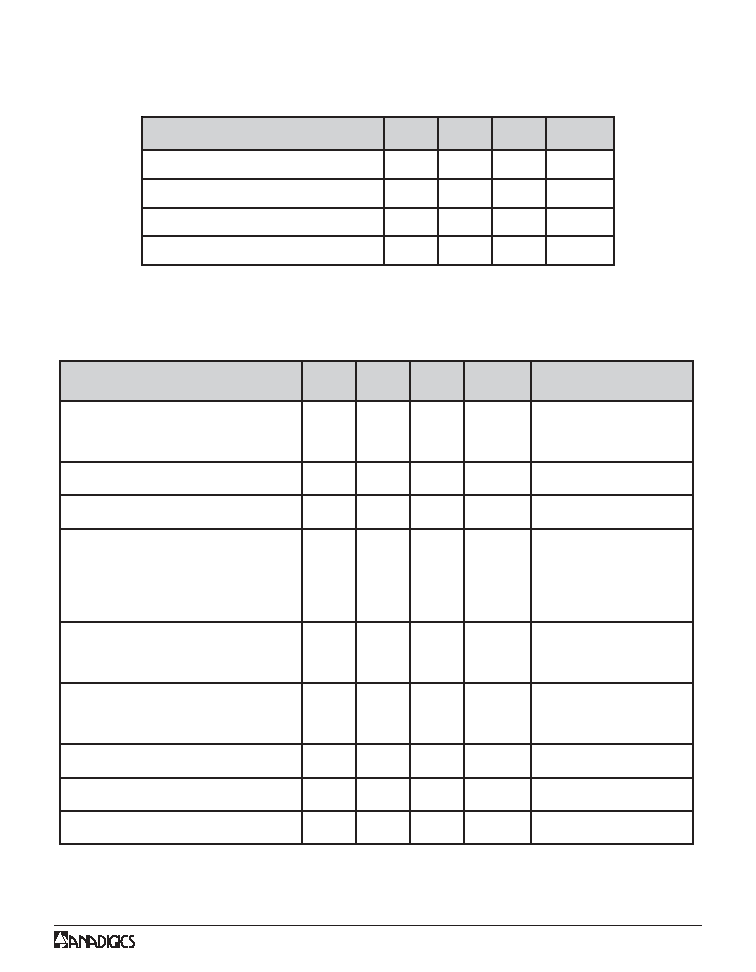

Table 2: Absolute Minimum and Maximum Ratings

Table 3: Operating Ranges

R

E

T

E

M

A

R

A

P

N

I

M

P

Y

T

X

A

M

T

I

N

U

V

:

y

l

p

p

u

S

r

e

if

il

p

m

A

DD

)

8

1

,

4

s

n

i

p

(

5

.

4

5

7

C

D

V

V

:

y

l

p

p

u

S

r

o

t

a

u

n

e

tt

A

ATTN

)

2

1

n

i

p

(

V

DD

5

.

0

-

5

7

C

D

V

)

6

1

,

5

1

,

4

1

,

3

1

s

n

i

p

(

s

l

o

r

t

n

o

C

r

o

t

a

u

n

e

tt

A

0

-

5

.

5

V

)

9

1

,

5

s

n

i

p

(

s

e

g

a

tl

o

V

e

c

n

e

r

e

f

e

R

r

e

if

il

p

m

A

-

5

7

.

1

-

C

D

V

e

r

u

t

a

r

e

p

m

e

T

e

s

a

C

0

4

-

5

2

5

8

o

C

Stresses in excess of the absolute ratings may cause permanent damage.

Functional operation is not implied under these conditions. Exposure to

absolute ratings for extended periods of time may adversely affect reliability.

The device may be operated safely over these conditions; however, parametric

performance is guaranteed only over the conditions defined in the electrical specifications.

Notes:

1. Pins 3 and 26 should be AC-coupled. No external DC bias should be applied.

2. Pins 10, 11, 24 and 25 should be grounded or pulled to ground through a resistor.

No external DC bias should be applied.

3. Pins 6, 7, 8, 9, 20, 21, 22 and 23 should be AC-grounded. No external DC bias

should be applied.

Data Sheet - Rev 2.2

05/2005

5

ARA05050

R

E

T

E

M

A

R

A

P

N

I

M

P

Y

T

X

A

M

T

I

N

U

)

4

n

i

p

(

t

n

e

r

r

u

C

1

A

r

e

if

il

p

m

A

-

5

7

5

9

A

m

)

8

1

n

i

p

(

t

n

e

r

r

u

C

2

A

r

e

if

il

p

m

A

-

0

0

1

0

3

1

A

m

)

2

1

n

i

p

(

t

n

e

r

r

u

C

r

o

t

a

u

n

e

tt

A

-

8

-

A

m

n

o

it

p

m

u

s

n

o

C

r

e

w

o

P

l

a

t

o

T

-

2

9

.

0

2

.

1

W

Notes:

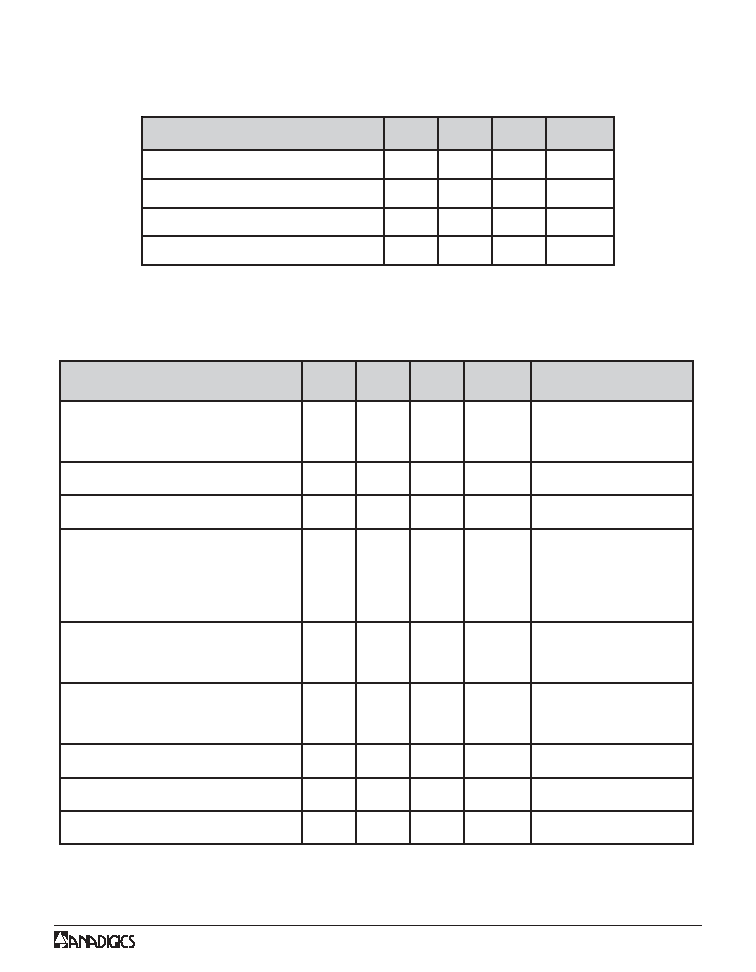

(1) See Figures 5 and 6 for performance at higher frequencies.

All specifications as measured in ANADIGICS test fixture.

Table 4: DC Electrical Specifications

T

A

=25

∞

C; V

DD

, V

ATTN

= +5.0 VDC

Table 5: AC Electrical Specifications

T

A

=25

∞

C; V

DD

, V

ATTN

= +5.0 VDC

R

E

T

E

M

A

R

A

P

N

I

M

P

Y

T

X

A

M

T

I

N

U

S

T

N

E

M

M

O

C

)

z

H

M

0

1

(

n

i

a

G

0

5

0

5

0

A

R

A

R

0

5

0

5

0

A

R

A

0

3

1

3

2

3

2

3

3

3

3

3

B

d

g

n

it

t

e

s

n

o

it

a

u

n

e

tt

a

B

d

0

s

s

e

n

t

a

l

F

n

i

a

G

-

5

7

.

0

5

.

1

B

d

z

H

M

0

0

1

o

t

5

e

r

u

t

a

r

e

p

m

e

T

r

e

v

o

n

o

it

a

ir

a

V

n

i

a

G

-

6

0

0

.

0

-

-

C

∞

/

B

d

s

p

e

t

S

n

o

it

a

u

n

e

tt

A

B

d

2

B

d

4

B

d

8

B

d

6

1

6

.

1

8

.

3

0

.

8

0

.

6

1

5

8

.

1

0

.

4

3

.

8

6

.

6

1

2

.

2

2

.

4

5

.

8

0

.

7

1

B

d

z

H

M

2

4

o

t

5

)

1

(

,

c

i

n

o

t

o

n

o

M

2

d

n

l

e

v

e

L

n

o

it

r

o

t

s

i

D

c

i

n

o

m

r

a

H

z

H

M

5

z

H

M

5

2

-

-

0

6

-

3

6

-

5

5

-

5

5

-

c

B

d

s

m

h

O

5

7

o

t

n

i

V

m

B

d

8

5

+

3

d

r

l

e

v

e

L

n

o

it

r

o

t

s

i

D

c

i

n

o

m

r

a

H

z

H

M

5

z

H

M

5

2

-

-

3

6

-

3

6

-

0

6

-

0

6

-

c

B

d

s

m

h

O

5

7

o

t

n

i

V

m

B

d

8

5

+

3

d

r

t

p

e

c

r

e

t

n

I

t

u

p

t

u

O

r

e

d

r

O

8

7

-

-

V

m

B

d

t

n

i

o

P

n

o

i

s

s

e

r

p

m

o

C

n

i

a

G

B

d

1

-

0

7

-

V

m

B

d

e

r

u

g

i

F

e

s

i

o

N

-

7

.

1

5

.

2

B

d