08/2001

1

S2

12 Pin 4 Sided SQFP

Package

FEATURES

∑

Single +5 Volt Supply

∑

Automatic Gain Control

∑

-43 dBm Sensitivity

∑

0 dBm Optical Overload

∑

70 MHz Bandwidth

APPLICATIONS

∑

OC-1 Receiver

∑

FITL

∑

Low Noise RF Amplifier

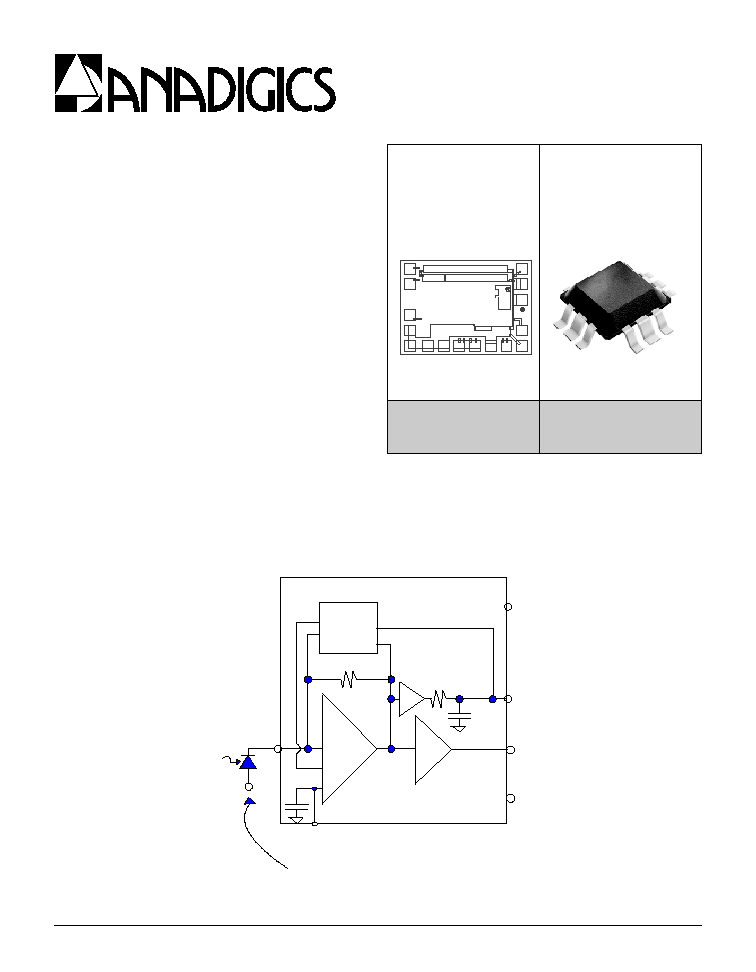

Figure 1: ATA00501 Equivalent Circuit

ATA00501

AGC Transimpedance Amplifier

SONET OC-1

PRELIMINARY DATA SHEET-Rev 1.5

VDD1

I

IN

GND

GND

GND GND

GND

GND

GND

GND

C

BY

C

BY

C

AGC

V

OUT

1992

19F

V

DD2

D1C

The ANADIGICS ATA00501 is a 5V low noise

transimpedance amplifier with AGC designed to be

used in OC-1 fiber optic links. The device is used in

conjunction with a photodetector (PIN diode or

avalanche photodiode) to convert an optical signal

into an output voltage. The ATA00501 has a bandwidth

of 70MHz and a dynamic range in excess of 40dB. It

is manufactured in a GaAs MESFET process and

available in bare die form or a 12 pin SQFP package.

PRODUCT DESCRIPTION

V

DD

V

OUT

C

AGC

GND

I

IN

C

BY

Photodetector cathode must be connected

To I

IN

for proper AGC operation

PATENT PENDING

GND

or

neg.supply

VGA

- 35

70K

+

4pF

+ 0.8

AGC

60K

20pF

PRELIMINARY DATA SHEET - Rev 1.5

08/2001

21.

ATA00501

Table 1: ATA00501D1C Pad Description (Die Only)

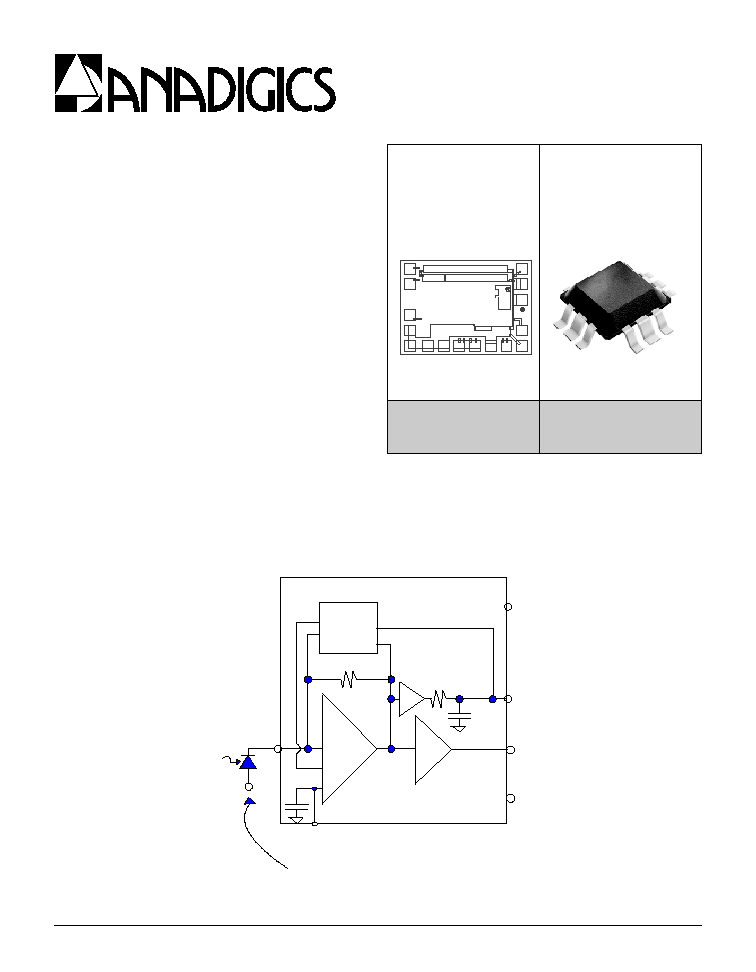

Figure 2: Bonding Pad Layout (Die Only)

ELECTRICAL CHARACTERISTICS

Table 3: Absolute Maximum Ratings

D

A

P

N

O

I

T

P

I

R

C

S

E

D

T

N

E

M

M

O

C

1

D

D

V

1

D

D

V

e

g

a

t

s

n

i

a

g

t

u

p

n

i

r

o

f

y

l

p

p

u

s

e

v

it

i

s

o

P

2

D

D

V

2

D

D

V

e

g

a

t

s

n

i

a

g

d

n

o

c

e

s

r

o

f

y

l

p

p

u

s

e

v

it

i

s

o

P

N

II

t

n

e

r

r

u

C

t

u

p

n

I

A

I

T

n

o

it

a

r

e

p

o

r

e

p

o

r

p

r

o

f

e

d

o

h

t

a

c

r

o

t

c

e

t

e

d

t

c

e

n

n

o

C

T

U

O

V

e

g

a

tl

o

V

t

u

p

t

u

O

A

I

T

k

c

o

l

b

C

D

l

a

n

r

e

t

x

e

s

e

ri

u

q

e

R

C

G

A

C

r

o

ti

c

a

p

a

C

C

G

A

l

a

n

r

e

t

x

E

t

n

a

t

s

n

o

c

e

m

it

C

G

A

=

C

G

A

C

*

K

0

7

Y

B

C

r

o

ti

c

a

p

a

c

s

s

a

p

y

b

e

g

a

t

s

n

i

a

g

t

u

p

n

I

F

p

6

5

>

925 um

VDD1

I

IN

GND

GND

GND GND

GND

GND

GND

GND

C

BY

C

BY

C

AGC

V

OUT

1992

19F

1250 um

V

DD2

V

1

D

D

V

0

.

7

V

2

D

D

V

0

.

7

I

N

I

A

m

5

T

A

0

4

-

.

p

m

e

T

g

n

it

a

r

e

p

O

o

5

2

1

o

t

C

o

C

T

S

5

6

-

.

p

m

e

T

e

g

a

r

o

t

S

o

0

5

1

o

t

C

o

C

Figure 3: Pin Layout

1

2

3

4

5

6

7

8

9

10

11

12

Table 2:ATA00501S2C Pin Description

Stresses in excess of the absolute ratings

may cause permanent damage. Functional

operation is not implied under these

conditions. Exposure to absolute ratings for

extended periods of time may adversely

affect reliability.

N

I

P

N

O

I

T

P

I

R

C

S

E

D

N

I

P

N

O

I

T

P

I

R

C

S

E

D

1

C

N

7

V

T

U

O

2

D

N

G

8

D

N

G

3

I

N

I

9

C

N

4

C

Y

B

0

1

V

D

D

5

D

N

G

1

1

D

N

G

6

C

C

G

A

2

1

C

N

PRELIMINARY DATA SHEET - Rev 1.5

08/2001

3

ATA00501

Table 4: Electrical Specifications

Notes:

(1) f=50MHz

(2) Measured with IIN below AGC Threshold. During AGC, input impedance will decrease propor-

tionally to I

IN

(3) Defined as the IIN where Transresistance has decreased by 50%.

(4) See note on Indirect Measurement of Optical Overload.

(5) See note on Measurement of Input Referred Noise Current.

(6) C

AGC

= 56 pF

(7) Parameter is guaranteed (not tested) by design and characterization data @ 51Mb/s, assuming

detector responsivity of 0.9

R

E

T

E

M

A

R

A

P

N

I

M

P

Y

T

X

A

M

T

I

N

U

)

A

n

0

0

5

<

c

d

I,

=

L

R

(

e

c

n

a

t

s

i

s

e

r

s

n

a

r

T

5

5

K

R

(

e

c

n

a

t

s

i

s

e

r

s

n

a

r

T

L

)

0

5

=

)

1

(

5

1

8

2

K

B

d

3

-

h

ti

w

d

n

a

B

0

5

0

7

z

H

M

e

c

n

a

t

s

i

s

e

R

t

u

p

n

I

)

2

(

0

0

5

1

e

c

n

a

t

s

i

s

e

R

t

u

p

t

u

O

0

3

0

5

0

6

e

g

a

tl

o

V

t

e

s

ff

O

t

u

p

n

I

5

.

1

6

.

1

9

.

1

s

tl

o

V

e

g

a

tl

o

V

t

e

s

ff

O

t

u

p

t

u

O

8

.

1

s

tl

o

V

tf

ir

D

e

g

a

tl

o

V

t

e

s

ff

O

1

/

V

m

o

C

I

(

d

l

o

h

s

e

r

h

T

C

G

A

N

I

)

)

3

(

5

0

1

A

d

a

o

lr

e

v

O

l

a

c

it

p

O

)

4

(

3

-

0

m

B

d

t

n

a

t

s

n

o

C

e

m

i

T

C

G

A

)

6

(

6

1

c

e

s

E

I

D

-

y

ti

v

it

i

s

n

e

S

l

a

c

it

p

O

)

7

(

3

4

-

m

B

d

P

F

Q

S

-

y

ti

v

it

i

s

n

e

S

l

a

c

it

p

O

)

7

(

1

4

-

m

B

d

t

n

e

r

r

u

C

y

l

p

p

u

S

0

3

5

4

A

m

e

g

n

a

R

e

g

a

tl

o

V

g

n

it

a

r

e

p

O

5

.

4

+

0

.

5

+

0

.

6

+

s

tl

o

V

e

g

n

a

R

e

r

u

t

a

r

e

p

m

e

T

g

n

it

a

r

e

p

O

0

4

-

5

8

o

C

m

m

W

W

W

W

•

PRELIMINARY DATA SHEET - Rev 1.5

08/2001

41.

ATA00501

Figure 4: ATA 00501D1C Typical Bonding

APPLICATION INFORMATION

Power Supplies and General Layout

Considerations

The ATA00501S2C may be operated from a positive

supply as low as + 4.5 V and as high as + 6.0 V.

Below + 4.5 V, bandwidth, overload and sensitivity

will degrade, while at + 6.0 V, bandwidth, overload

and sensitivity improve (see Bandwidth vs.

Temperature curves). Use of surface mount, low

inductance power supply bypass capacitors

(>=56pF) are essential for good high frequency and

low noise performance. The power supply bypass

capacitors should be mounted on or connected to a

good low inductance ground plane.

General Layout Considerations

Since the gain stages of the transimpedance

amplifier have an open loop bandwidth in excess

of 1.0 GHz, it is essential to maintain good high

frequency layout practices. To prevent oscillations,

a low inductance RF ground plane should be made

available for power supply bypassing. Traces that

can be made short should be made short, and the

utmost care should be taken to maintain very low

capacitance at the photodiode-TIA interface (I

IN

),

excess capacitance at this node will cause a

degradation in bandwidth and sensitivity (see

Bandwidth vs. CT curves).

PIN

56pF

56pF

V

DD

OUT

56pF

56pF

GND

VDD2

GND

GND

1992

V

OUT

GND

GND

C

BY

C

AGC

C

BY

GND

GND

GND

GND

I

IN

60C

V

DD

Figure 6: Bandwidth vs. Temperature

0.04

0.05

0.06

0.07

0.08

0.09

-40

10

60

85

V

DD

=

4.5 V

V

DD

=

5.0 V

V

DD

=

5.5 V

C

T

= 0.5 pF

Temperature (C)

Bandwidth

(GHz)

Figure 5: ATA 00501S2C External Circuit

1

2

3

4

5

6

7

8

9

10

11

12

I

IN

NC

GND

or

Neg.Supply

0.1µF

Vout

NC

0.1µF

V

DD

NC

56 pF

56 pF

PRELIMINARY DATA SHEET - Rev 1.5

08/2001

5

ATA00501

Note: All performance curves are typical @ TA =25 oC

unless otherwise noted.

IIN Connection

(Refer to the equivalent circuit diagram.) Bonding

the detector cathode to IIN (and thus drawing current

from the ATA00501) improves the dynamic range.

Although the detector may be used in the reverse

direction for input currents not exceeding 25

m

A, the

specifications for optical overload will not be met.

VOUT Connection

The output pad should be connected via a coupling

capacitor to the next stage of the receiver channel

(filter or decision circuits), as the output buffers are

not designed to drive a DC coupled 50 ohm load

(this would require an output bias current of

approximately 36 mA to maintain a quiescent 1.8

Volts across the output load). If VOUT is connected

to a high input impedance decision circuit (>500

ohms), then a coupling capacitor may not be

required, although caution should be exercised

since DC offsets of the photo detector/TIA

combination may cause clipping of subsequent gain

or decision circuits.

Figure 7: Bandwidth vs. CT

V

DD

= 4.5 V

V

DD

= 5.0 V

V

DD

= 5.5 V

90

80

70

60

50

40

30

0 0.2 0.4 0.6 0.8 1 1.2

B(3dB) A/ 2

Rf (C

in

+C

t

)

C

T

(pF)

Bandwidth

(MHz)

Figure 8: Transimpedance vs. I

IN

V

DD

= 5.5 V

V

DD

= 4.5 V

I

IN

(mA DC)

-2.1 -1.6 -1.1 -0.6 -0.1

25

22

19

16

13

10

7

4

1

I

IN

50

Transimpedance

(K

Ohm)

Figure 9: Bandwidth vs. I

IN

Figure 10: V

OUT

vs. I

IN

V

DD

= 4.5 V

V

DD

= 5.5 V

50

I

IN

- 2.1 - 1.6 - 1.1 - 0.6 - 0.1

1.44

1.24

1.04

.84

.64

.44

.24

.04

R

f

Bandwidth

(GHz)

I

IN

(mA DC)

V

DD

= 4.5 V

V

DD

= 5.5 V

Output Collapse

I

IN

v

OUT

Heavy AGC

Linear Region

(

o

3.4

3.2

3.0

2.9

2.7

2.5

2.4

2.2

2.0

1.9

1.7

1.5

1.4

1.2

1.0

0.8

0.7

0.5

0.3

0.2

0.0

R

f

-4 - 3 - 2 - 1

I

IN

(mA DC)

V

O

U

T

(

V

olt

s

)