DS020700-U001e

- 1 -

AN220E04 Datasheet

Dynamically Reconfigurable FPAA

www.anadigm.com

DS020700-U001e

- 2 -

Disclaimer

Anadigm reserves the right to make any changes without further notice to any products herein. Anadigm makes no

warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does

Anadigm assume any liability arising out of the application or use of any product or circuit, and specifically disclaims

any and all liability, including with out limitation consequential or incidental damages. "Typical" parameters can and

do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer

application by customer's technical experts. Anadigm does not in this document convey any license under its patent

rights nor the rights of others. Anadigm software and associated products cannot be used except strictly in

accordance with an Anadigm software license. The terms of the appropriate Anadigm software license shall prevail

over the above terms to the extent of any inconsistency.

© Anadigm

Æ

Ltd. 2003

© Anadigm

Æ

, Inc. 2003

All Rights Reserved.

AN220E04 Datasheet ≠ Dynamically Reconfigurable FPAA

DS020700-U001e

- 3 -

PRODUCT AND ARCHITECTURE OVERVIEW

The AN220E04 is the first member of Anadigm

Æ

's second

generation FPAA family ≠ the Anadigmvortex family. Based on a

fully differential switched-capacitor architecture, this new product

family features higher bandwidth, improved total harmonic

distortion (THD) and the ability to implement a host of advanced

functions.

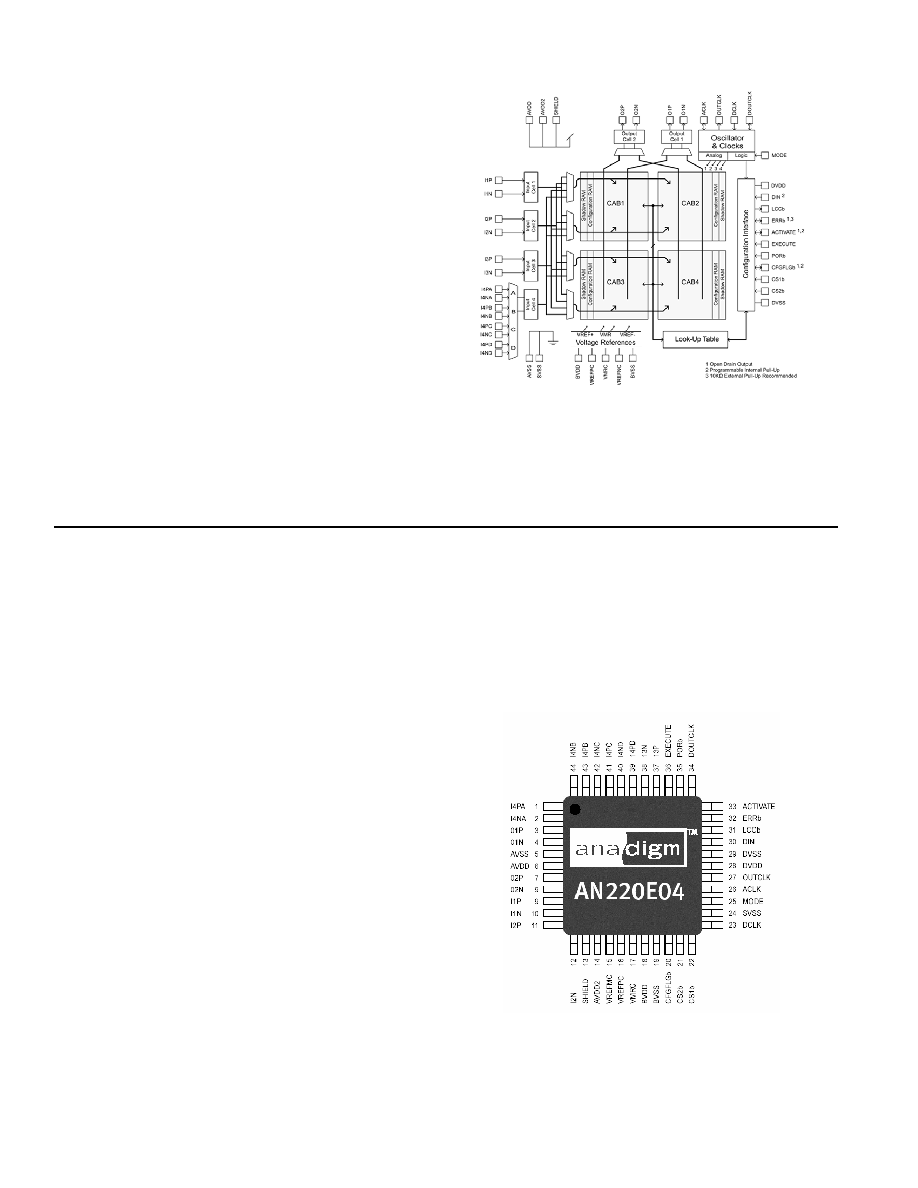

The AN220E04 consists of a 2 x 2 matrix of fully configurable

switched capacitor configurable analog blocks (CABs), enmeshed

in a fabric of programmable interconnect resources. These

programmable features are directed by an on-chip SRAM

configuration memory. The four CABs have access to a single

Look-Up Table (LUT) which can be used to implement non linear

functions such as user-defined input-to-output transfer functions,

and arbitrary signal waveform generation.

Analog input signals come in from the outside world via the four

input cells. The fourth input cell of the AN220E04 has a special

`multiplexing' feature which allows the connection of up to four

unique signal sources. An input cell can accept either a single-

ended signal or a differential signal pair. The input cells each

have built-in programmable anti-aliasing filters, as well as a high

gain amplifier which has an optional chopper stabilized operating

mode designed for use with signals requiring significant gain and

hence ultra low input offset voltages

.

The AN220E04 is also designed to support dynamic

reconfiguration. There are two memories on the AN220E04:

Figure 1: Architectural overview of the AN220E04 device

Shadow SRAM and Configuration SRAM. The new

reconfiguration data is stored in the Shadow SRAM, which can

then be transferred to the Configuration SRAM at just a single

clock edge providing for synchronized on-the-fly update of the

analog circuit function.

PRODUCT FEATURES

∑

Dynamic reconfiguration

∑ Fully

differential

architecture

∑

Fully differential I/O buffering with options for single ended

to differential conversion

∑

Low input offset through chopper stabilized amplifiers

∑

Built-in Successive Approximation Register (SAR)

∑

256 Byte Look-Up Table (LUT) for linearization and

arbitrary signal generation

∑

4:1 Input multiplexer

∑

Typical Signal Bandwidth: DC-2MHz (Bandwidth is CAM

dependent)

∑

Signal to Noise Ratio:

o Broadband

80dB

o Narrowband

(audio)

100dB

∑

Total Harmonic Distortion (THD): 80dB

∑

DC offset <100µV

∑

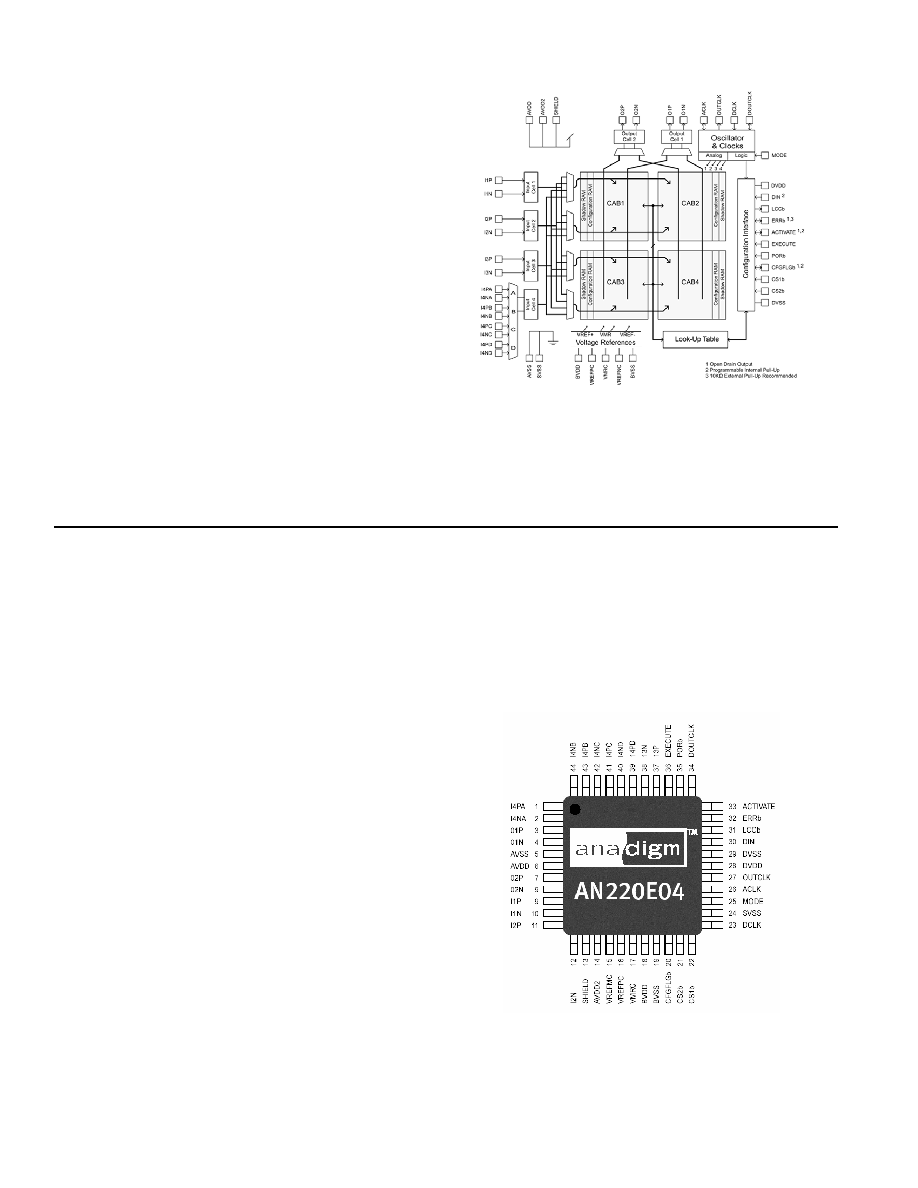

Package: 44-pin QFP (10x10x2mm)

o

Lead pitch 0.8mm

∑

Supply voltage: 5V

ORDERING CODES

AN220E04-QFPSP

Dynamically reconfigurable FPAA

Sample Pack

AN220E04-QFPTY

Dynamically reconfigurable FPAA

Tray (96 pcs)

AN220E04-QFPTR

Dynamically reconfigurable FPAA

Tape & Reel (1000 pcs)

AN220D04-EVAL

AN220E04 Evaluation Kit

AN220D04-DEVLP

AN220E04 Development Kit

APPLICATIONS

∑

Real-time software control of analog system peripherals

∑ Intelligent

sensors

∑

Adaptive filtering and control

∑

Adaptive DSP front-end

∑

Adaptive industrial control and automation

∑ Self-calibrating

systems

∑

Compensation for aging of system components

∑

Dynamic recalibration of remote systems

∑

Ultra-low frequency signal conditioning

∑

Custom analog signal processing

[For more detailed information on the features of the AN220E04 device,

please refer to the AN120E04/AN220E04 User Manual]

AN220E04 Datasheet ≠ Dynamically Reconfigurable FPAA

DS020700-U001e

- 4 -

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings

Parameter Symbol

Min

Typ

Max

Unit

Comment

DC Power Supplies

AVDD(2)

BVDD

DVDD

-0.5 - 5.5

V

V

AVSS, BVSS, DVSS and SVSS all

held to 0.0 V

a

xVDD to xVDD Offset

-0.5

0.5

V

Ideally all supplies should be at the

same voltage

Package Power Dissipation

Pmax 25∞C

Pmax 85∞C

- -

1.8

0.73

W

Still air, No heatsink, 4 layer board,

44 pins.

ja = 55∞C/W

Analog and Digital Input Voltage

Vinmax Vss-0.5 - Vdd+0.5 V

Ambient Operating Temperature

Top

-40

-

85

∞C

Storage Temperature

Tstg

-65

150

∞C

a

Absolute Maximum DC Power Supply Rating - The failure mode is non-catastrophic for Vdd of up to 7 volts, but will cause reduced

operating life time. The additional stress caused by higher local electric fields within the CMOS circuitry may induce metal migration,

oxide leakage and other time/quality related issues.

Recommended Operating Conditions

Parameter Symbol

Min

Typ

Max

Unit

Comment

DC Power Supplies

AVDD(2)

BVDD

DVDD

4.75 5.00 5.25 V

AVSS, BVSS, DVSS and SVSS all

held to 0 V

Analog Input Voltage.

Vina

VMR-1.9 -

VMR+1.9

V

VMR

is 2.0 volts above AVSS

Digital Input Voltage

Vind

0

-

DVDD

V

Junction Temp

Tj

-40

-

125

∞C

Assume a package

ja = 55∞C/W

b

b

In order to calculate the junction temperature you must first empirically determine the current draw (total Idd) for the design. Once the

current consumption established then the following formula can be used; Tj = Ta + Idd x Vdd x 55 ∞C/W, where Ta is the ambient

temperature. The worst case

ja of 55 ∞C/W assumes no air flow and no additional heatsink of any type.

General Digital I/O Characteristics (Vdd = 5v +/- 10%, -40 to 85 deg.C)

Parameter Symbol

Min

Typ

Max

Unit

Comment

Input Voltage Low

Vih

0

-

30

-

% of DVDD

Input Voltage High

Vil

70

-

100

-

% of DVDD

Output Voltage Low

Vol

0

-

20

-

% of DVDD

Output Voltage High

Voh

80

-

100

-

% of DVDD

Input Leakage Current

Iil

-

-

±1.0

µA

All pins except DCLK

Input Leakage Current

Iil -

±12.0

-

µA

DCLK if a crystal is connected and

the on-chip oscillator is used

Max. Capacitive Load

Cmax - - 10

pF

The maximum load for a digital

output is 10 pF // 10 Kohm

Min. Resistive Load

Rmin 10 - -

Kohm

The maximum load for a digital

output is 10 pF // 10 Kohm

DCLK Frequency

Fmax - - 40

MHz

For MODE = 1, Max DCLK is

16 MHz

ACLK Frequency

Fmax - - 40

MHz

Divide down to <8 MHz prior to use

as a CAB clock

Clock Duty Cycle

-

45

-

55

%

All clocks

AN220E04 Datasheet ≠ Dynamically Reconfigurable FPAA

DS020700-U001e

- 5 -

Detailed Digital I/O Interface Characteristics: Vdd = 5.0volts

LCCb

Parameter Symbol

Min

Typ

Max

Unit

Comment

Output Voltage Low

Vol

Vss

-

150

mV

Load 20pF//50Kohm to Vss

Output Voltage High

Voh

4.5

-

Vdd

V

Load 20pF//50Kohm to Vss

Max. Capacitive Load

Cmax

-

-

20

pF

Maximum load 20 pF // 50 Kohm

Min. Resistive Load

Rmin

50

-

-

Kohm

Maximum load 20 pF // 50 Kohm

Current Sink

Isnkmax

-

-

15

mA

LCCb pin shorted to Vdd

Current Source

Isrcmax

-

-

4

mA

LCCb pin shorted to Vss

CFGFLG, ACTIVATE

Parameter Symbol

Min

Typ

Max

Unit

Comment

Input Voltage Low

Vil

0

30

%

% of DVDD

Input Voltage High

Vih

70

100

%

% of DVDD

Output Voltage Low

Vol Vss - 85

mV

Pin load =

Internal pullup + 20pF//50K to Vss

Output Voltage High

Voh 4.5 - Vdd

V

Pin load =

Internal pullup + 20pF//50K to Vss

Output Voltage Low

Vol Vss - 200

mV

Pin Load =

External 5K ohm pullup +

20pF//50K to Vss

Output Voltage High

Voh 4.5 - Vdd

V

Pin Load =

External 5Kohm pullup +

20pF//50K to Vss

Max. Capacitive Load

Cmax

-

-

50

pF

Maximum load 50 pF // 50 Kohm

Min. Resistive Load

Rmin

50

-

-

Kohm

Maximum load 50 pF // 50 Kohm

Current Sink

Isnkmax

-

-

2.5

mA

Pin shorted to Vdd

Current Source

Isrcmax

-

-

200

µA

Pin shorted to Vss

External Resistive Pullup

Rpullupext 5

7.5 10 Kohm

Use only if internal pullup is

deselected

ERRb

Parameter Symbol

Min

Typ

Max

Unit

Comment

Input Voltage Low

Vil

0

30

%

% of DVDD

Input Voltage High

Vih

70

100

%

% of DVDD

Output Voltage Low

Vol

Vss

-

50

mV

Output

Voltage

High

Voh 4.9 - Vdd

V

Max. Capacitive Load

Cmax

-

-

50

pF

Maximum load 50 pF // 50 Kohm

Min. Resistive Load

Rmin

50

-

-

Kohm

Maximum load 50 pF // 50 Kohm

Current Sink

Isnkmax

-

-

10

mA

Current Source

Isrcmax

-

-

0

µA

External Resistive Pullup

Rpullupext

10

10

10

Kohm

DCLK,Mode,DIN,EXECUTE,PORb,CS1b,CS2b

Parameter Symbol

Min

Typ

Max

Unit

Comment

Input Voltage Low

Vil

0

-

30

%

% of DVDD

Input Voltage High

Vih

70

-

100

%

% of DVDD