AAT3242

300mA/150mA Dual CMOS LDO Linear Regulator

3242.2005.01.1.4

1

PowerLinear

TM

General Description

The AAT3242 is a dual low dropout linear regulator

with Power OK (POK) outputs. Two integrated reg-

ulators provide a high power 300mA output and a

lower power 150mA output, making this device

ideal for use with microprocessors and DSP cores

in portable products. Two POK pins provide open

drain output signals when their respective regulator

output is within regulation. The AAT3242 has inde-

pendent input voltage and enable pins for increased

design flexibility. This device features a very low

quiescent current (140µA typical) and low dropout

voltages (typically 200mV and 400mV at the full

output current level), making it ideal for portable

applications where extended battery life is critical.

The AAT3242 has complete over-current/short-cir-

cuit and over-temperature protection circuits to

guard against extreme operating conditions.

The AAT3242 is available in a space-saving 12-pin

TSOPJW package. This device is capable of oper-

ation over the -40∞C to +85∞C temperature range.

Features

∑

High/Low Current Outputs, 300mA/150mA

∑

Low Dropout:

∑

LDO A: 400mV at 300mA

∑

LDO B: 200mV at 150mA

∑

High Output Voltage Accuracy: ±1.5%

∑

High PSRR: 65dB at 1KHz

∑

70µA Quiescent Current for Each LDO

∑

Over-Current/Short-Circuit Protection

∑

Over-Temperature Protection

∑

Two POK Outputs

∑

Independent Power and Enable Inputs

∑

Uses Low Equivalent Series Resistance

(ESR) Ceramic Capacitors

∑

12-Pin TSOPJW Package

∑

-40∞C to +85∞C Temperature Range

Applications

∑

Cellular Phones

∑

Digital Cameras

∑

Handheld Instruments

∑

Microprocessor / DSP Core / I/O Power

∑

Notebook Computers

∑

PDAs and Handheld Computers

∑

Portable Communication Devices

Typical Application

AAT3242

2.2µF

100k

2.2µF

Enable B

Enable A

VIN

OUTPUT A

OUTPUT B

POKA

100k

POKB

POKA

OUTA

OUTB

POKB

GND

ENB

INB

INA

ENA

AAT3242

300mA/150mA Dual CMOS LDO Linear Regulator

2

3242.2005.01.1.4

Pin Descriptions

Pin Configuration

TSOPJW-12

(Top View)

1

2

3

4

5

6

12

11

10

9

8

7

ENA

GND

GND

POKA

OUTB

INB

INA

OUTA

POKB

GND

GND

ENB

Pin #

Symbol

Function

1

ENA

Enable Regulator A pin; this pin should not be left floating. When pulled

low, the PMOS pass transistor turns off and the device enters shutdown

mode, consuming less than 1µA.

2, 3, 8, 9

GND

Ground connection pins.

4

POKA

Power OK pin with open drain output. It is pulled low when the OUTA pin is

below the 10% regulation window.

5

OUTB

Low current (150mA) regulator output pin; should be decoupled with a

2.2µF or greater output low-ESR ceramic capacitor.

6

INB

Input voltage pin for Regulator B; should be decoupled with 1µF or greater

capacitor.

7

ENB

Enable Regulator B; this pin should not be left floating. When pulled low, the

PMOS pass transistor turns off and the device enters shutdown mode, con-

suming less than 1µA.

10

POKB

Power OK pin with open drain output. It is pulled low when the OUTB pin is

below the 10% regulation window.

11

OUTA

High-current (300mA) regulator output pin; should be decoupled with a

2.2µF or greater output low-ESR ceramic capacitor.

12

INA

Input voltage pin for Regulator A; should be decoupled with 1µF or greater

capacitor.

AAT3242

300mA/150mA Dual CMOS LDO Linear Regulator

3242.2005.01.1.4

3

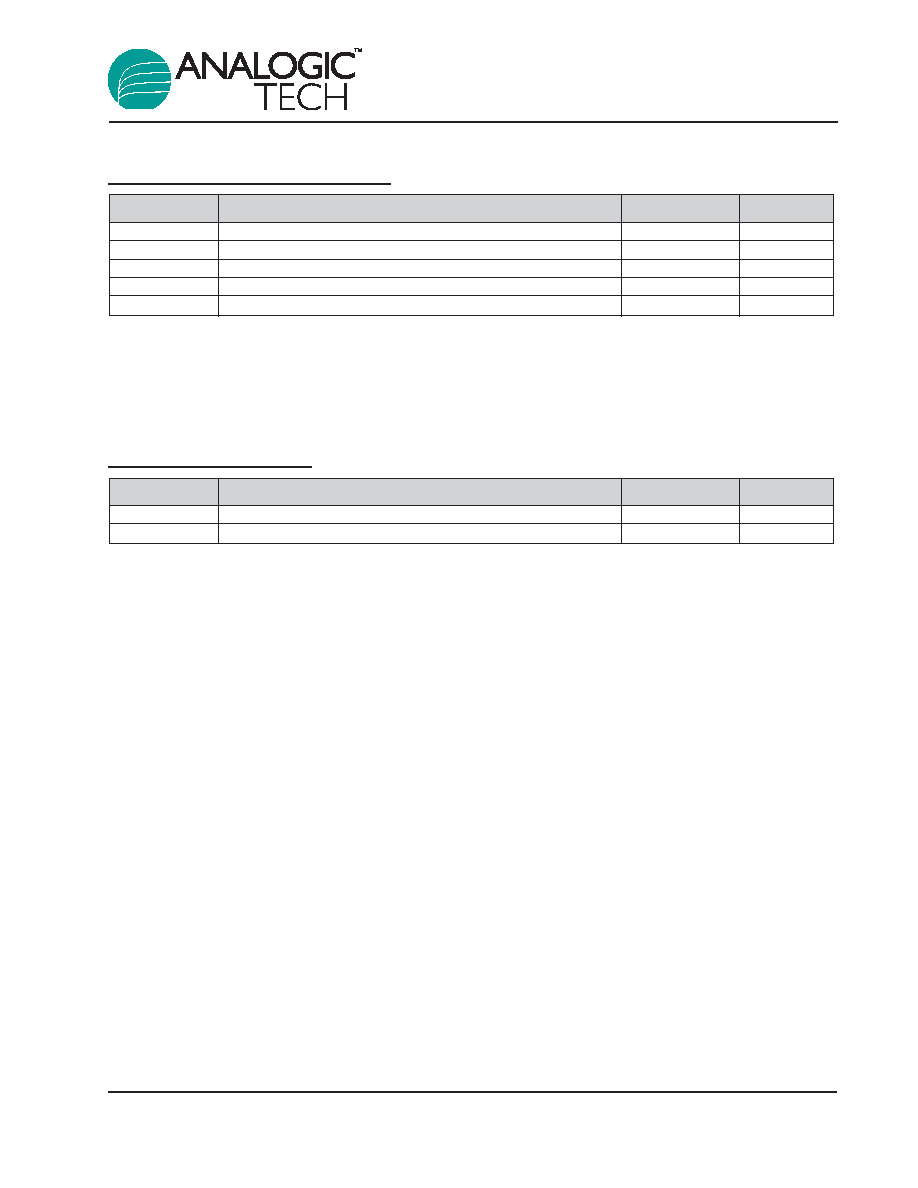

Absolute Maximum Ratings

1

Notes:

1: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at condi-

tions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

2: Based on long-term current density limitation.

Thermal Information

Note 1: Mounted on an FR4 board.

Note 2: Derate 9.1mW/∞C above 25∞C.

Symbol

Description

Value

Units

JA

Thermal Resistance

1

110

∞C/W

P

D

Maximum Power Dissipation (T

A

= 25∞C)

2

909

mW

Symbol

Description

Value

Units

V

IN

Input Voltage

6.0

V

V

ENIN(MAX)

Maximum EN to Input Voltage

0.3

V

I

OUT

2

DC Output Current

P

D

/(V

IN

-V

O

)

mA

T

J

Operating Junction Temperature Range

-40 to 150

∞C

T

LEAD

Maximum Soldering Temperature (at leads, 10 sec)

300

∞C

AAT3242

300mA/150mA Dual CMOS LDO Linear Regulator

4

3242.2005.01.1.4

Electrical Characteristics

1

V

IN

= V

OUT(NOM)

+ 1.0 V for V

OUT

options greater than 1.5V. V

IN

= 2.5V for V

OUT

1.5 V. I

OUT

= 1.0mA, C

OUT

= 2.2 µF, C

IN

= 1.0 µF, T

A

= -40∞C to +85∞C, unless otherwise noted. Typical values are T

A

= 25∞C.

Notes:

1: The AAT3242 is guaranteed to meet performance specifications over the -40∞C to +85∞C operating temperature range and is assured

by design, characterization, and correlation with statistical process controls.

2: V

DO

is defined as V

IN

- V

OUT

when V

OUT

is 98% of nominal.

3: For V

OUT

<2.1V, V

DO

= 2.5 - V

OUT

.

4: C

IN

= 10µF.

5: To calculate minimum input voltage, use the following equation: V

IN(MIN)

= V

OUT(MAX)

+ V

DO(MAX)

as long as V

IN

2.5V.

Symbol

Description

Conditions

Min

Typ Max

Units

LDO A; I

OUT

= 300mA

V

OUT

Output Voltage Tolerance

I

OUT

= 1mA T

A

= 25∞C

-1.5

1.5

%

to 300mA

T

A

= -40 to 85∞C

-2.5

2.5

V

IN

Input Voltage

V

OUT

+ V

DO

5

5.5

V

V

DO

Dropout Voltage

2,3

I

OUT

= 300mA

400 600

mV

V

OUT

/

Line Regulation

4

V

IN

= V

OUT

+ 1 to 5.0 V

0.09

%/V

V

OUT

*V

IN

V

OUT(Line)

Dynamic Line Regulation

I

OUT

= 300mA, V

IN

= V

OUT

+ 1

5.0

mV

to V

OUT

+ 2, T

R

/T

F

= 2µS

V

OUT(Load)

Dynamic Load Regulation

I

OUT

= 1mA to 300mA,

60

mV

T

R

<5µS

V

EN(L)

Enable Threshold Low

0.6

V

V

EN(H)

Enable Threshold High

1.5

V

V

POK

Power OK Trip Threshold

V

OUT

Rising, T

A

= 25∞C

90

94

98

% of V

OUT

V

POKHYS

Power OK Hysteresis

1.0

% of V

OUT

V

POK(LO)

Power OK Output Voltage Low

I

SINK

= 1mA

0.4

V

I

POK

POK Output Leakage Current

V

POK

<5.5V, V

OUT

in Regulation

1.0

µA

I

OUT

Output Current

V

OUT

> 1.2V

300

mA

I

SC

Short-Circuit Current

V

OUT

< 0.4V

600

mA

I

Q

Ground Current

V

IN

=5V, No Load; EN A = V

IN

70

125

µA

I

SD

Shutdown Current

V

IN

= 5V, EN A = 0V

1.0

µA

1kHz

65

PSRR

Power Supply Rejection Ratio

I

OUT

=10mA 10kHz

45

dB

1MHz

42

T

SD

Over-Temperature Shutdown

145

∞C

Threshold

T

HYS

Over-Temperature Shutdown

12

∞C

Hysteresis

e

N

Output Noise

e

NBW

= 300Hz to 50kHz

250

µVRMS

TC

Output Voltage Temperature

22

ppm/∞C

Coefficient

AAT3242

300mA/150mA Dual CMOS LDO Linear Regulator

3242.2005.01.1.4

5

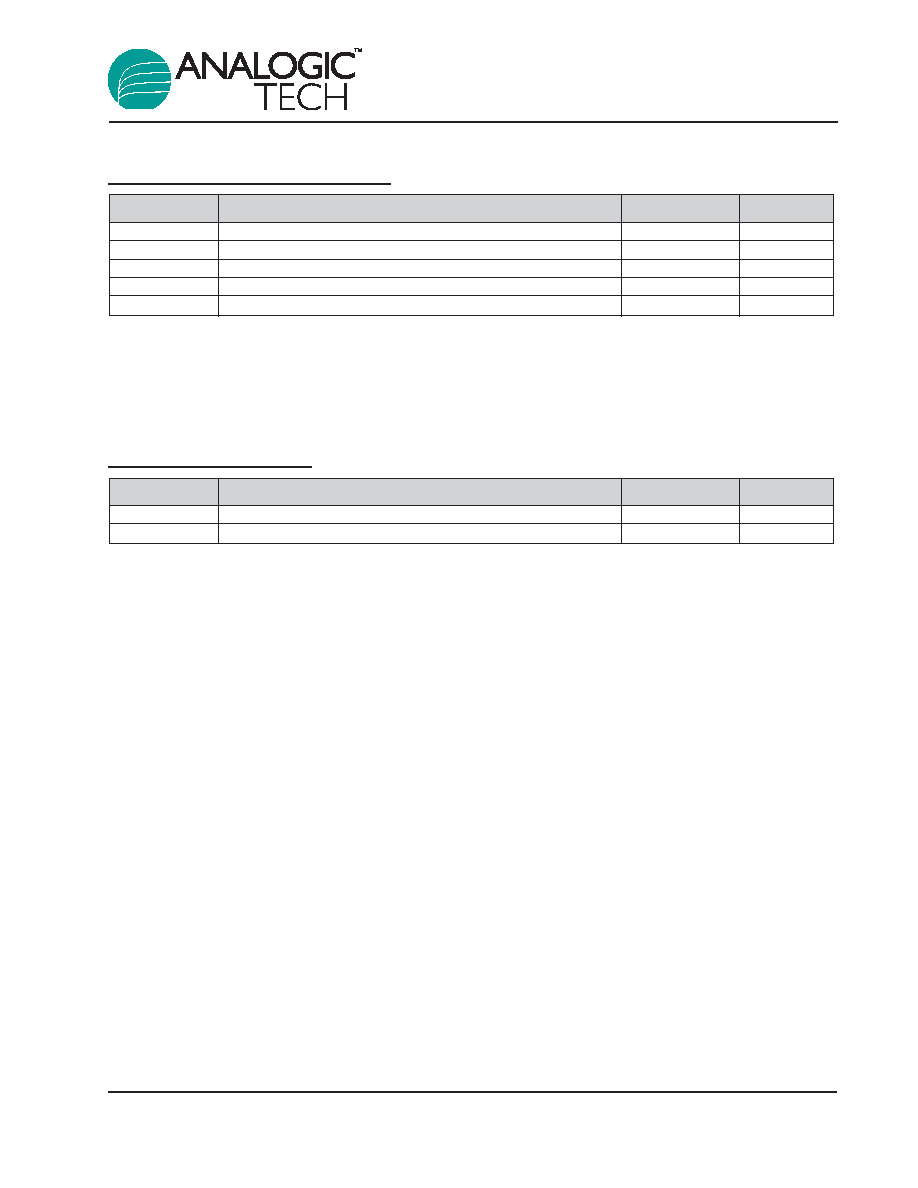

Electrical Characteristics

1

(continued)

V

IN

= V

OUT(NOM)

+ 1.0 V for V

OUT

options greater than 1.5V. V

IN

= 2.5V for V

OUT

1.5 V. I

OUT

= 1.0mA, C

OUT

= 2.2 µF, C

IN

= 1.0 µF, T

A

= -40∞C to +85∞C, unless otherwise noted. Typical values are T

A

= 25∞C.

Notes:

1: The AAT3242 is guaranteed to meet performance specifications over the -40∞C to +85∞C operating temperature range and is assured

by design, characterization, and correlation with statistical process controls.

2: V

DO

is defined as V

IN

- V

OUT

when V

OUT

is 98% of nominal.

3: For V

OUT

<2.3V, V

DO

= 2.5 - V

OUT

.

4: C

IN

= 10µF.

5: To calculate minimum input voltage, use the following equation: V

IN(MIN)

= V

OUT(MAX)

+ V

DO(MAX)

as long as V

IN

2.5V.

Symbol

Description

Conditions

Min

Typ Max

Units

LDO B; I

OUT

= 150mA

V

OUT

Output Voltage Tolerance

I

OUT

= 1mA T

A

= 25∞C

-1.5

1.5

%

to 150mA

T

A

= -40 to 85∞C

-2.5

2.5

V

IN

Input Voltage

V

OUT

+ V

DO

5

5.5

V

V

DO

Dropout Voltage

2,3

I

OUT

= 150mA

200 300

mV

V

OUT

/

Line Regulation

4

V

IN

= V

OUT

+ 1 to 5.0 V

0.09

%/V

V

OUT

*V

IN

V

OUT(Line)

Dynamic Line Regulation

I

OUT

= 150mA, V

IN

= V

OUT

+ 1

5.0

mV

to V

OUT

+ 2, T

R

/T

F

= 2 µS

V

OUT(Load)

Dynamic Load Regulation

I

OUT

= 1mA to 150mA, T

R

<5µS

60

mV

V

EN(L)

Enable Threshold Low

0.6

V

V

EN(H)

Enable Threshold High

1.5

V

V

POK

Power OK Trip Threshold

V

OUT

Rising, T

A

= 25∞C

90

94

98

% of V

OUT

V

POKHYS

Power OK Hysteresis

1.0

% of V

OUT

V

POK(LO)

Power OK Output Voltage Low

I

SINK

= 1mA

0.4

V

I

POK

POK Output Leakage Current

V

POK

<5.5V, V

OUT

in Regulation

1.0

µA

I

OUT

Output Current

V

OUT

> 1.2V

150

mA

I

SC

Short-Circuit Current

V

OUT

< 0.4V

600

mA

I

Q

Ground Current

V

IN

= 5V, No Load; EN B = V

IN

70

125

µA

1kHz

65

PSRR

Power Supply Rejection Ratio

I

OUT

= 10mA 10kHz

45

dB

1MHz

42

T

SD

Over-Temperature Shutdown

145

∞C

Threshold

T

HYS

Over-Temperature Shutdown

12

∞C

Hysteresis

e

N

Output Noise

e

NBW

= 300Hz to 50kHz

250

µVRMS

T

C

Output Voltage Temperature

22

ppm/∞C

Coefficient