Symbol

V

DS

V

GS

I

DM

I

AR

E

AR

T

J

, T

STG

Symbol

Typ

Max

14.2

20

39

50

R

JL

0.8

1.5

2.5

W

T

A

=70∞C

1.6

W

Junction and Storage Temperature Range

A

P

D

∞C

100

50

-55 to 175

T

C

=100∞C

I

D

Continuous Drain

Current

B,G

Maximum

Units

Parameter

T

C

=25∞C

G

T

C

=100∞C

B

30

Maximum Junction-to-Ambient

A

Steady-State

85

65

200

Avalanche Current

C

30

Power Dissipation

A

T

A

=25∞C

P

DSM

∞C/W

Absolute Maximum Ratings T

A

=25∞C unless otherwise noted

V

V

±20

Pulsed Drain Current

Power Dissipation

B

T

C

=25∞C

Gate-Source Voltage

Drain-Source Voltage

Maximum Junction-to-Lead

C

Steady-State

∞C/W

Thermal Characteristics

Parameter

Units

Maximum Junction-to-Ambient

A

t 10s

R

JA

∞C/W

A

Repetitive avalanche energy L=0.1mH

C

120

mJ

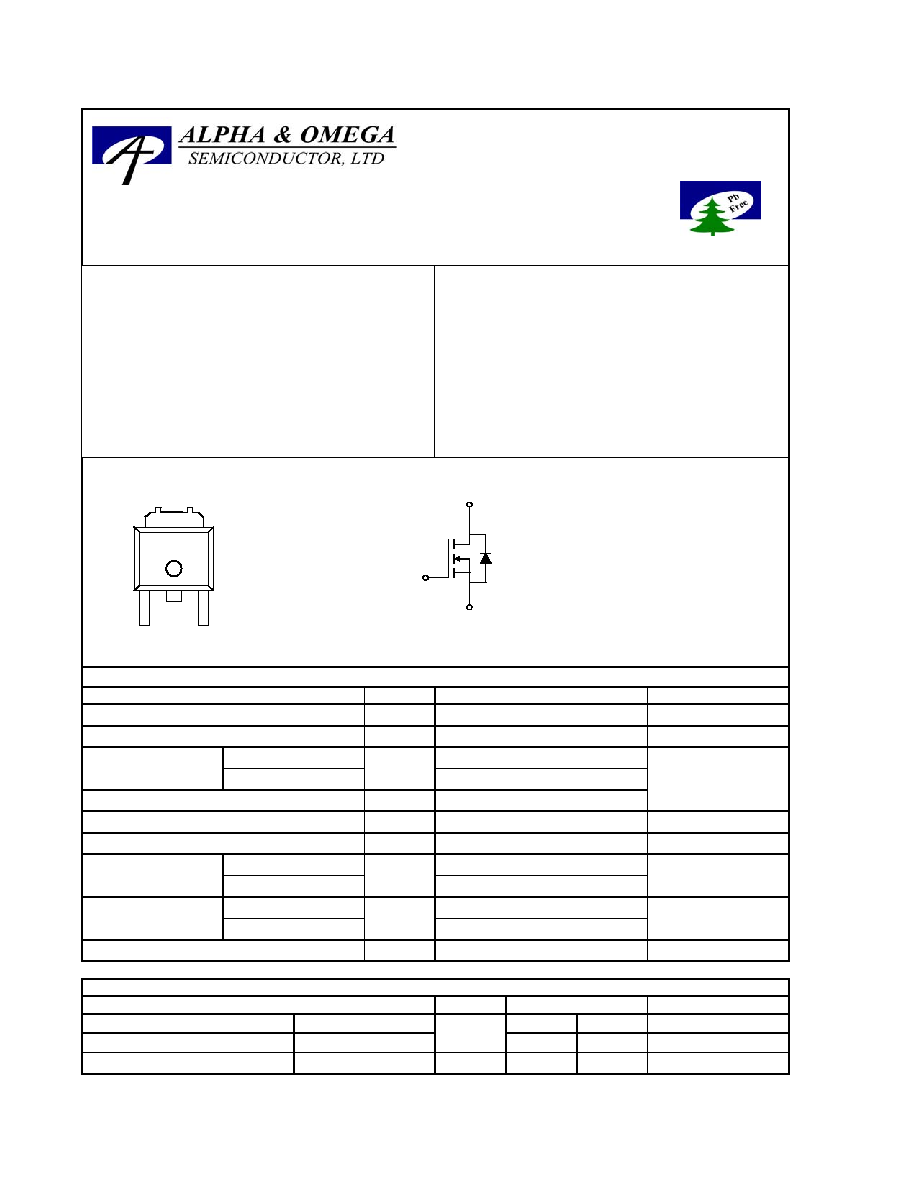

AOD412

N-Channel Enhancement Mode Field Effect Transistor

Features

V

DS

(V) = 30V

I

D

= 85A (V

GS

= 10V)

R

DS(ON)

< 7.0m

(V

GS

= 10V)

R

DS(ON)

< 10.5m

(V

GS

= 4.5V)

General Description

The AOD412 uses advanced trench technology to

provide excellent R

DS(ON)

, low gate chargeand low

gate resistance. This device is ideally suited for use

as a high side switch in CPU core power conversion.

Standard Product AOD412 is Pb-free (meets ROHS

& Sony 259 specifications). AOD412L is a Green

Product ordering option. AOD412 and AOD412L are

electrically identical.

G

D

S

G D S

TO-252

D-PAK

Top View

Drain Connected

to Tab

Alpha & Omega Semiconductor, Ltd.

AOD412

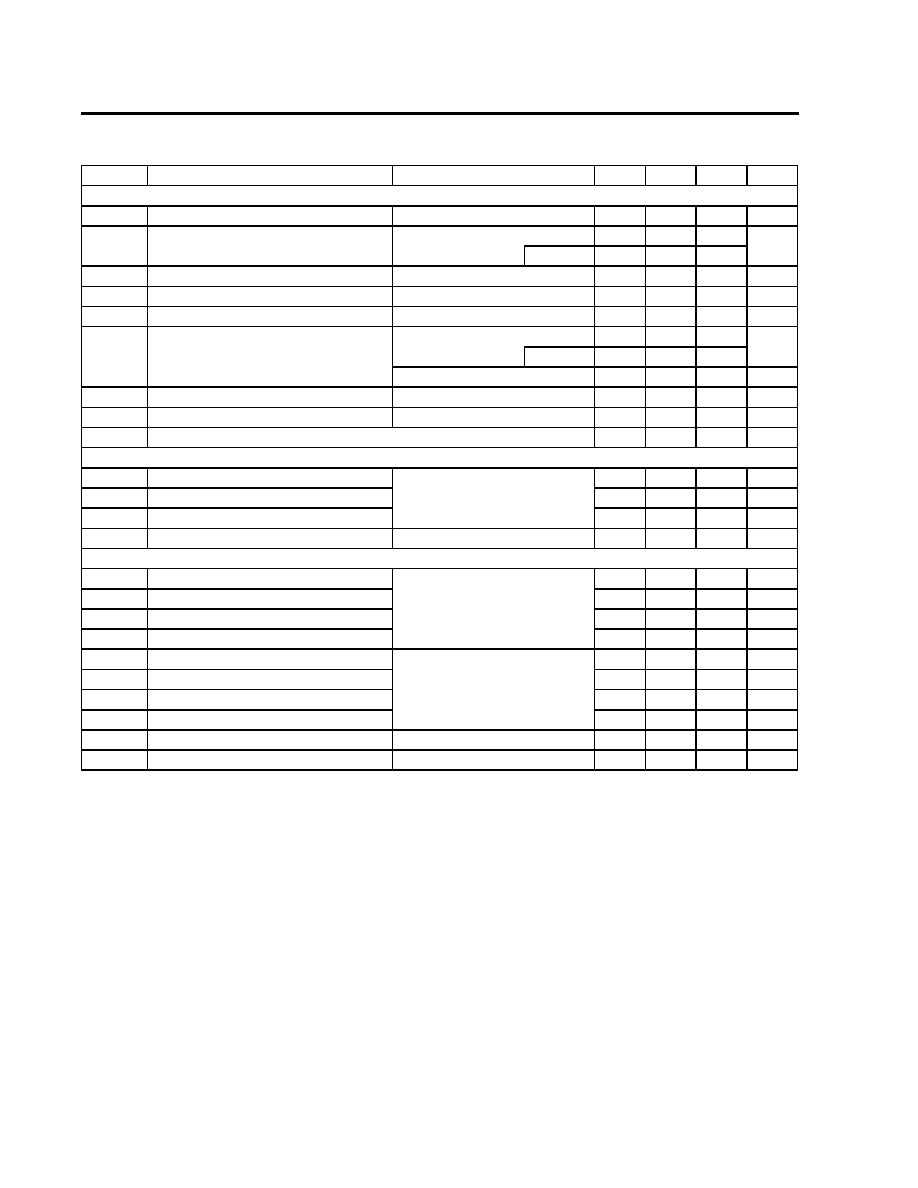

Symbol

Min

Typ

Max

Units

BV

DSS

30

V

0.005

1

T

J

=55∞C

5

I

GSS

100

nA

V

GS(th)

1.5

2.15

2.5

V

I

D(ON)

85

A

5.5

7

T

J

=125∞C

8.8

11

8.25

10.5

m

g

FS

60

S

V

SD

0.72

1

V

I

S

85

A

C

iss

1320

1600

pF

C

oss

533

pF

C

rss

154

pF

R

g

0.95

1.2

Q

g

(10V)

26

32

nC

Q

g

(4.5V)

13.3

16.2

nC

Q

gs

3.2

nC

Q

gd

6.6

nC

t

D(on)

7.2

10

ns

t

r

12.5

18

ns

t

D(off)

22

33

ns

t

f

6

9

ns

t

rr

29.7

36

ns

Q

rr

29

36

nC

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL

COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING

OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,

FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

Gate Drain Charge

V

GS

=0V, V

DS

=15V, f=1MHz

SWITCHING PARAMETERS

Total Gate Charge

Gate Source Charge

Gate resistance

V

GS

=0V, V

DS

=0V, f=1MHz

V

GS

=4.5V, V

DS

=15V, I

D

=20A

Total Gate Charge

Turn-On Rise Time

Turn-Off DelayTime

V

GS

=10V, V

DS

=15V, R

L

=0.75

,

R

GEN

=3

Turn-Off Fall Time

Turn-On DelayTime

m

V

GS

=4.5V, I

D

=20A

I

S

=1A,V

GS

=0V

V

DS

=5V, I

D

=20A

Maximum Body-Diode Continuous Current

Input Capacitance

Output Capacitance

DYNAMIC PARAMETERS

R

DS(ON)

Static Drain-Source On-Resistance

Forward Transconductance

Diode Forward Voltage

I

DSS

µ

A

Gate Threshold Voltage

V

DS

=V

GS

I

D

=250

µ

A

V

DS

=24V, V

GS

=0V

V

DS

=0V, V

GS

= ±20V

Zero Gate Voltage Drain Current

Gate-Body leakage current

Electrical Characteristics (T

J

=25∞C unless otherwise noted)

STATIC PARAMETERS

Parameter

Conditions

Body Diode Reverse Recovery Time

Body Diode Reverse Recovery Charge

I

F

=20A, dI/dt=100A/

µ

s

Drain-Source Breakdown Voltage

On state drain current

I

D

=250

µ

A, V

GS

=0V

V

GS

=10V, V

DS

=5V

V

GS

=10V, I

D

=20A

Reverse Transfer Capacitance

I

F

=20A, dI/dt=100A/

µ

s

A: The value of R

JA

is measured with the device mounted on 1in

2

FR-4 board with 2oz. Copper, in a still air environment with T

A

=25∞C. The Power

dissipation P

DSM

is based on steady-state R

JA

and the maximum allowed junction temperature of 150∞C. The value in any given application depends on

the user's specific board design, and the maximum temperature fo 175∞C may be used if the PCB or heatsink allows it.

B. The power dissipation P

D

is based on T

J(MAX)

=175∞C, using junction-to-case thermal resistance, and is more useful in setting the upper dissipation

limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package limit.

C: Repetitive rating, pulse width limited by junction temperature T

J(MAX)

=175∞C.

D. The R

JA

is the sum of the thermal impedence from junction to case R

JC

and case to ambient.

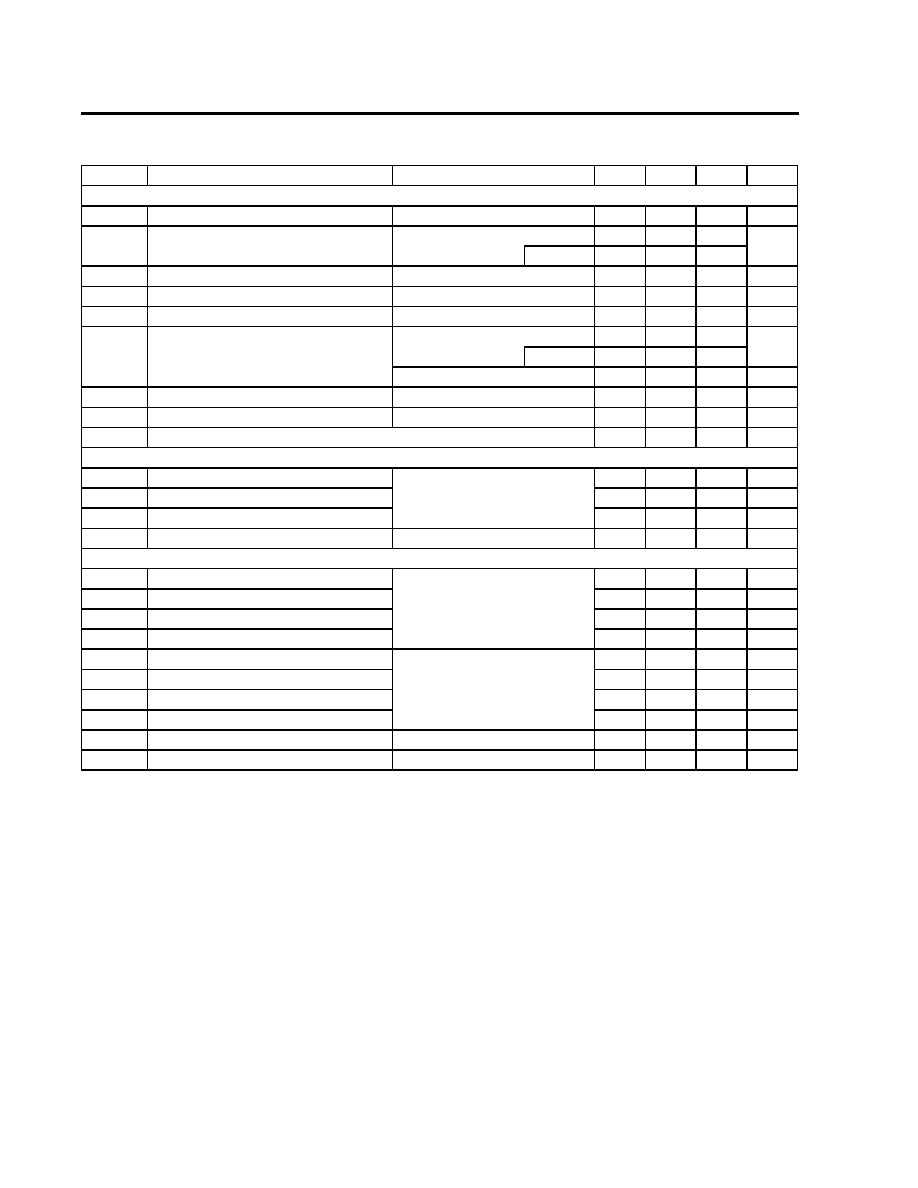

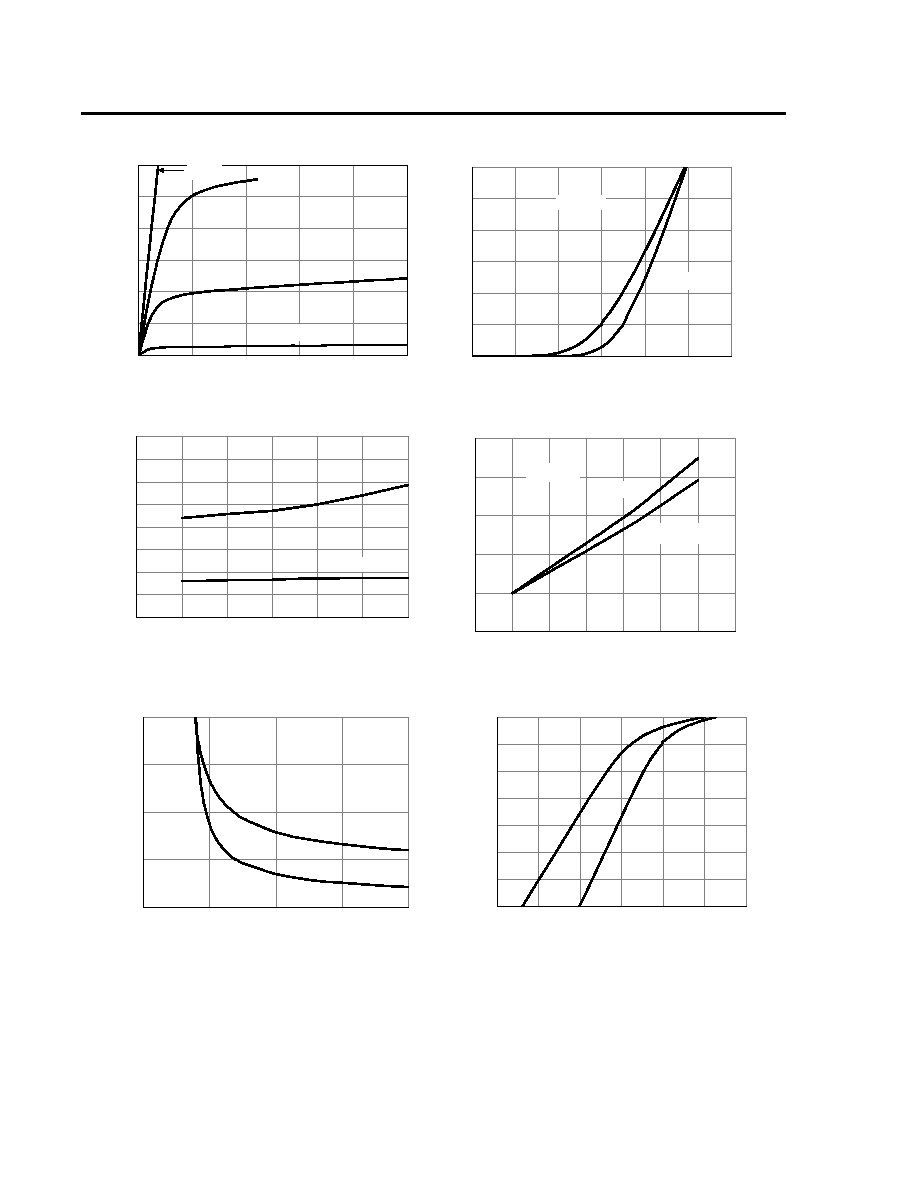

E. The static characteristics in Figures 1 to 6 are obtained using <300

µ

s pulses, duty cycle 0.5% max.

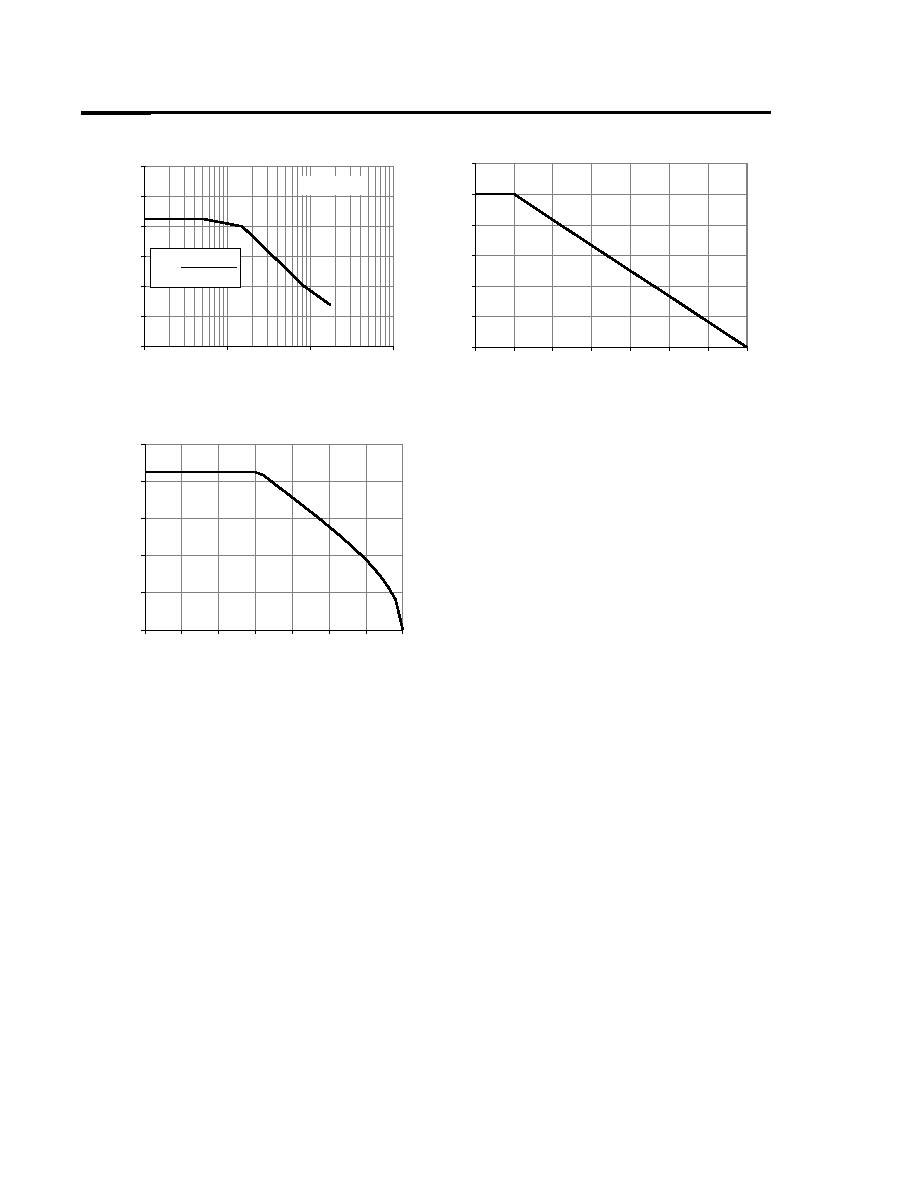

F. These tests are performed with the device mounted on 1 in

2

FR-4 board with 2oz. Copper, in a still air environment with T

A

=25∞C. The SOA curve

provides a single pulse rating.

G. The maximum current rating is limited by the package current capability.

Rev 3 : July 2005

Alpha & Omega Semiconductor, Ltd.

AOD412

TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

0

10

20

30

40

50

60

0

1

2

3

4

5

V

DS

(Volts)

Fig 1: On-Region Characteristics

I

D

(A

)

V

GS

=3V

3.5V

10V

4.0V

0

10

20

30

40

50

60

1.5

2

2.5

3

3.5

4

4.5

V

GS

(Volts)

Figure 2: Transfer Characteristics

I

D

(A

)

4

5

6

7

8

9

10

11

12

0

10

20

30

40

50

60

I

D

(A)

Figure 3: On-Resistance vs. Drain Current and Gate

Voltage

R

DS(

O

N)

(m

)

1.0E-05

1.0E-04

1.0E-03

1.0E-02

1.0E-01

1.0E+00

1.0E+01

1.0E+02

0.0

0.2

0.4

0.6

0.8

1.0

1.2

V

SD

(Volts)

Figure 6: Body-Diode Characteristics

I

S

(A

)

25∞C

125∞C

0.8

1

1.2

1.4

1.6

1.8

0

25

50

75

100

125

150

175

Temperature (∞C)

Figure 4: On-Resistance vs. Junction Temperature

N

o

r

m

aliz

ed

O

n

-

R

esist

an

ce

V

GS

=10V

V

GS

=4.5V

4

8

12

16

20

2

4

6

8

10

V

GS

(Volts)

Figure 5: On-Resistance vs. Gate-Source Voltage

R

DS(

O

N)

(m

)

25∞C

125∞C

V

DS

=5V

V

GS

=4.5V

V

GS

=10V

I

D

=20A

25∞C

125∞C

I

D

=20A

Alpha & Omega Semiconductor, Ltd.

AOD412

TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

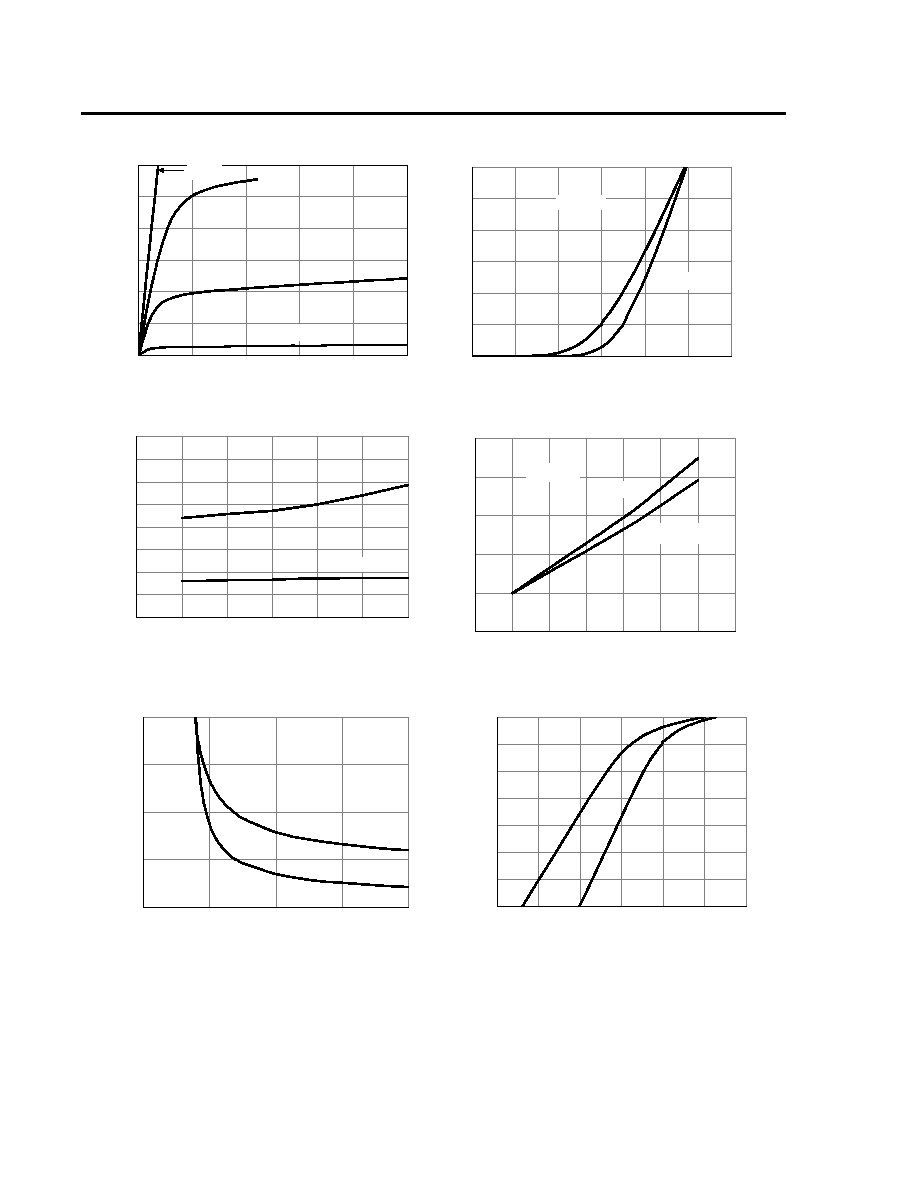

0

2

4

6

8

10

0

5

10

15

20

25

30

Q

g

(nC)

Figure 7: Gate-Charge Characteristics

V

GS

(V

ol

ts

)

0

400

800

1200

1600

2000

2400

0

5

10

15

20

25

30

V

DS

(Volts)

Figure 8: Capacitance Characteristics

C

a

p

acit

a

n

ce (

p

F

)

C

iss

0

20

40

60

80

100

0.01

0.1

1

10

100

1000

Pulse Width (s)

Figure 10: Single Pulse Power Rating Junction-to-

Ambient (Note F)

Po

w

e

r (

W

)

0.001

0.01

0.1

1

10

0.00001

0.0001

0.001

0.01

0.1

1

10

100

1000

Pulse Width (s)

Figure 11: Normalized Maximum Transient Thermal Impedance (Note F)

Z

JA

N

o

r

m

aliz

ed

T

r

an

sien

t

T

h

er

m

a

l R

esist

an

ce

C

oss

C

rss

0.1

1

10

100

1000

0.1

1

10

100

V

DS

(Volts)

I

D

(A

mps

)

Figure 9: Maximum Forward Biased Safe

Operating Area (Note F)

100

µ

s

10ms

1ms

0.1s

1s

10s

DC

R

DS(ON)

limited

T

J(Max)

=150∞C

T

A

=25∞C

V

DS

=15V

I

D

=20A

Single Pulse

D=T

on

/T

T

J,PK

=T

A

+P

DM

.Z

JA

.R

JA

R

JA

=50∞C/W

T

on

T

P

D

In descending order

D=0.5, 0.3, 0.1, 0.05, 0.02, 0.01, single pulse

T

J(Max)

=150∞C

T

A

=25∞C

10

µ

s

Alpha & Omega Semiconductor, Ltd.