SRAM

AS5C512K8

Austin Semiconductor, Inc.

AS5C512K8

Rev. 4.5 7/01

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

1

FEATURES

∑ Ultra High Speed Asynchronous Operation

∑ Fully Static, No Clocks

∑ Multiple center power and ground pins for improved

noise immunity

∑ Easy memory expansion with CE\ and OE\

options

∑ All inputs and outputs are TTL-compatible

∑ Single +5V Power Supply +/- 10%

∑ Data Retention Functionality Testing (Contact Factory)

∑ Cost Efficient Plastic Packaging

∑ Extended Testing Over -55∫C to +125∫C for plastics

∑ Plastic 36 pin PSOJ is fully compatible with the

Ceramic 36 pin SOJ

∑ 3.3V Future Offering

OPTIONS

MARKING

∑ Timing

15ns access

-15

17ns access

-17

20ns access

-20

25ns access

-25

35ns access

-35

45ns access

-45

∑ Operating Temperature Ranges

Military (-55

o

C to +125

o

C)

XT

Industrial (-40

o

C to +85

o

C)

IT

∑ Package(s)

Ceramic LCC

EC

No. 210

Ceramic Flatpack

F

No. 307

Plastic SOJ

DJ

No. 903

Ceramic SOJ

ECJ

No.503

∑ 2V data retention/low power

L (Consult Factory)

∑ Radiation Tolerant (EPI)

E

PIN ASSIGNMENT

(Top View)

36-Pin SOJ (DJ & ECJ)

36-Pin CLCC (EC)

GENERAL DESCRIPTION

The AS5C512K8 is a high speed SRAM. It offers flexibility in

high-speed memory applications, with chip enable (CE\) and output

enable (OE\) capabilities. These features can place the outputs in

High-Z for additional flexibility in system design.

Writing to these devices is accomplished when write enable (WE\)

and CE\ inputs are both LOW. Reading is accomplished when WE\

remains HIGH and CE\ and OE\ go LOW.

As a option, the device can be supplied offering a reduced power

standby mode, allowing system designers to meet low standby power

requirements. This device operates from a single +5V power supply

and all inputs and outputs are fully TTL-compatible.

The AS5C512K8DJ offers the convenience and reliability of the

AS5C512K8 SRAM and has the cost advantage of a durable plastic.

The AS5C512K8DJ is footprint compatible with 36 pin CSOJ

package of the SMD 5692-95600.

36-Pin Flat Pack (F)

AVAILABLE AS MILITARY

SPECIFICATIONS

∑SMD 5962-95600

∑SMD 5962-95613

∑MIL-STD-883

512K x 8 SRAM

HIGH SPEED SRAM with

REVOLUTIONARY PINOUT

For more products and information

please visit our web site at

www.austinsemiconductor.com

SRAM

AS5C512K8

Austin Semiconductor, Inc.

AS5C512K8

Rev. 4.5 7/01

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

2

FUNCTIONAL BLOCK DIAGRAM

TRUTH TABLE

MODE

OE\

CE\

WE\

I/O

POWER

STANDBY

X

H

X

HIGH-Z

STANDBY

READ

L

L

H

Q

ACTIVE

NOT SELECTED

H

L

H

HIGH-Z

ACTIVE

WRITE

X

L

L

D

ACTIVE

S

N

O

I

T

C

N

U

F

N

I

P

8

1

A

-

0

A

s

t

u

p

n

I

s

s

e

r

d

d

A

\

E

W

e

l

b

a

n

E

e

t

i

r

W

\

E

C

e

l

b

a

n

E

p

i

h

C

\

E

O

e

l

b

a

n

E

t

u

p

t

u

O

O

/

I

0

O

/

I

-

7

s

t

u

p

t

u

O

/

s

t

u

p

n

I

a

t

a

D

V

C

C

r

e

w

o

P

V

S

S

d

n

u

o

r

G

C

N

n

o

i

t

c

e

n

n

o

C

o

N

X = Don't Care

VCC

GND

INPUT BUFFER

4,194,304-BIT

MEMORY ARRAY

1024 ROWS X

4096 COLUMNS

I/O

CONTROLS

COLUMN DECODER

ROW DECODER

*POWER

DOWN

CE\

OE\

WE\

DQ8

DQ1

A0-A18

*On the low voltage Data Retention option.

SRAM

AS5C512K8

Austin Semiconductor, Inc.

AS5C512K8

Rev. 4.5 7/01

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

3

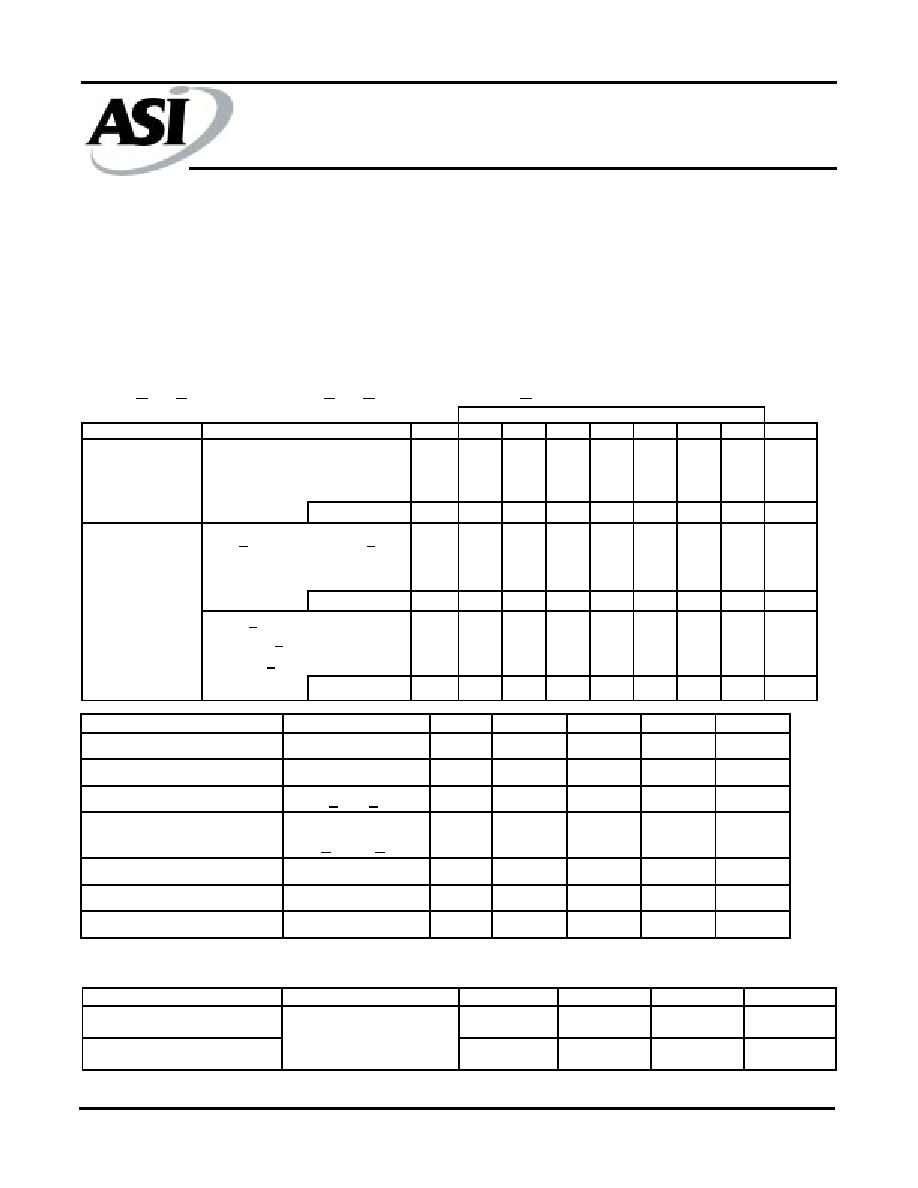

ABSOLUTE MAXIMUM RATINGS*

Voltage on Vcc Supply Relative to Vss

Vcc ..............................................................................-.5V to +7.0V

Storage Temperature (Plastic)......................-65

∞

C to +150

∞

C

Storage Temperature (Ceramic)...................-55∞C to +125∞C

Short Circuit Output Current (per I/O)...........................20mA

Voltage on any Pin Relative to Vss.................-.5V to Vcc+1V

Maximum Junction Temperature**..............................+150

∞

C

Power Dissipation ................................................................1W

*Stresses greater than those listed under "Absolute Maximum

Ratings" may cause permanent damage to the device. This is

a stress rating only and functional operation of the device at

these or any other conditions above those indicated in the

operation section of this specification is not implied. Exposure

to absolute maximum rating conditions for extended periods

may affect reliability.

** Junction temperature depends upon package type, cycle

time, loading, ambient temperature and airflow, and humidity.

ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

(-55

o

C < T

A

< +125

o

C & -40

o

C < T

A

< +85

o

C ; Vcc = 5V +10%)

DESCRIPTION

SYM

-15

-17

-20

-25

-35

-45

UNITS NOTES

I

CCSP

225

225

225

225

225

225

mA

3

"L" Version Only

I

CCLP

180

180

180

180

180

180

mA

I

SBTSP

60

60

60

60

60

60

mA

"L" Version Only I

SBTLP

30

30

30

30

30

30

mA

I

SBCSP

25

25

25

25

25

25

mA

"L" Version Only I

SBCLP

10

10

10

10

10

10

mA

MAX

Power Supply

Current: Standby

CONDITIONS

WE\=CE\<V

IL

; Vcc = MAX

f = MAX = 1/t

RC

Outputs Open

CE\ > V

IH

, All other inputs < V

IL

,

Vcc = MAX, f = 0,

Outputs Open

CE\ > Vcc -0.2V; Vcc = MAX

V

IN

<Vss +0.2V or

V

IN

>Vcc -0.2V; f = 0

Power Supply

Current: Operating

�

�

�

�

�

�

�

!

!

µ

"

# �

#$ %$&'

!

!

µ

"

#

( ) *"

)

# �

( *"

)

+,

)

CAPACITANCE

PARAMETER

CONDITIONS

SYMBOL

MAX

UNITS

NOTES

Input Capacitance

C

I

12

pF

4

Output Capactiance

Co

14

pF

4

T

A

= 25

o

C, f = 1MHz

V

IN

= 0

SRAM

AS5C512K8

Austin Semiconductor, Inc.

AS5C512K8

Rev. 4.5 7/01

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

4

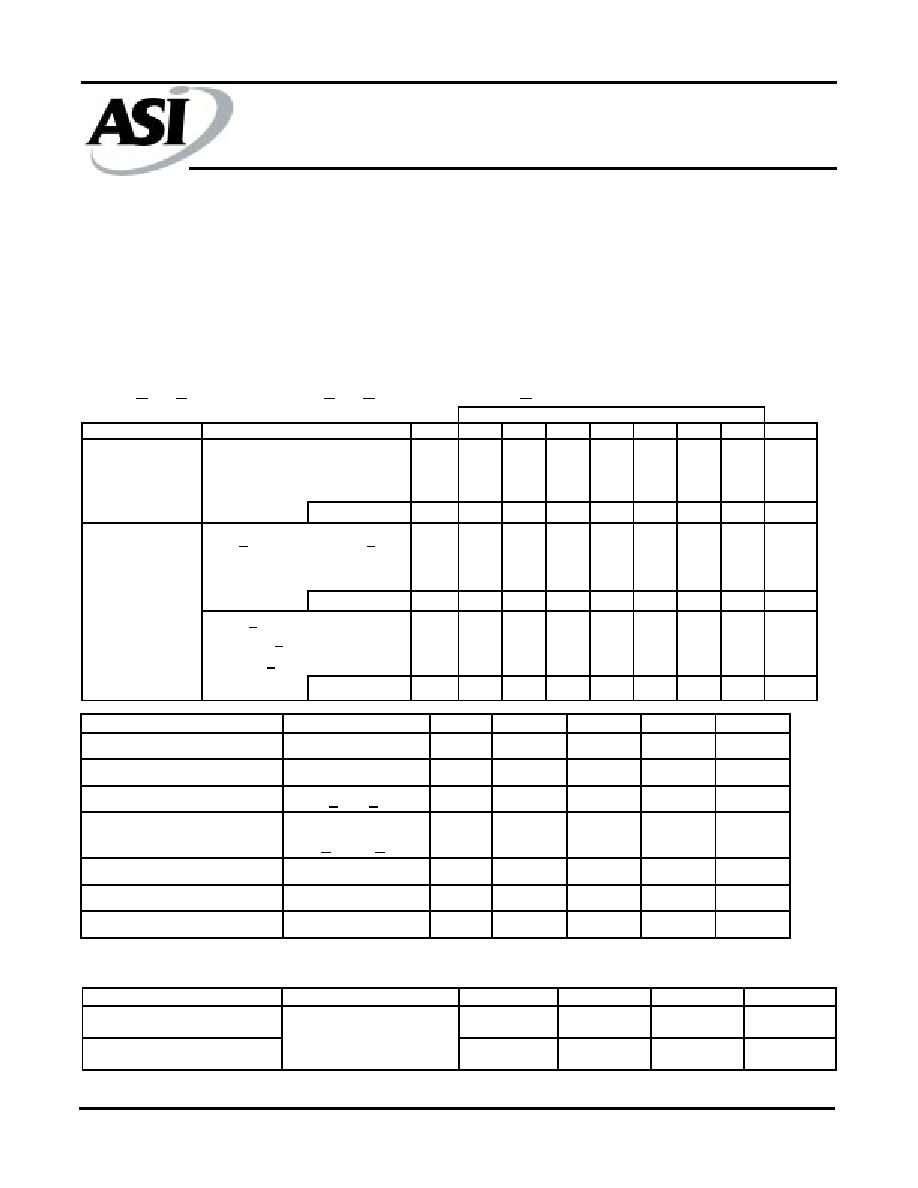

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

(-55

o

C < T

A

< +125

o

C or -40

o

C to +85

o

C; Vcc = 5V +10%)

�

�

�

�

! � "

# $%&

)

"%&

*

*

' ('

�

*

*

# $%&

�

�

�

�

�

�

)

"%&

*

*

' ('

�

+,

�

- +

(

.

- +

(

/

�

! � - +

+,

0 +

(

)

/

�

�

1

)

�

�

+

)

# $%&

�

�

�

�

�

�

+

"%&

*

*

' ('

SRAM

AS5C512K8

Austin Semiconductor, Inc.

AS5C512K8

Rev. 4.5 7/01

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

5

167 ohms

167 ohms

1.73V

1.73V

C=5pF

C=30pF

Q

Q

Input pulse levels ...................................................... Vss to 3.0V

Input rise and fall times ......................................................... 3ns

Input timing reference levels ............................................... 1.5V

Output reference levels ........................................................ 1.5V

Output load ................................................. See Figures 1 and 2

NOTES

1.

All voltages referenced to V

SS

(GND).

2.

-2V for pulse width < 20ns

3.

I

CC

is dependent on output loading and cycle rates.

4.

This parameter is guaranteed but not tested.

5.

Test conditions as specified with the output loading

as shown in Fig. 1 unless otherwise noted.

6.

t

LZCE,

t

LZWE,

t

LZOE,

t

HZCE,

t

HZOE and

t

HZWE

are specified with CL = 5pF as in Fig. 2. Transition is

measured ±200mV from steady state voltage.

7.

At any given temperature and voltage condition,

t

HZCE is less than

t

LZCE, and

t

HZWE is less than

t

LZWE.

8.

WE\ is HIGH for READ cycle.

9.

Device is continuously selected. Chip enables and

output enables are held in their active state.

10. Address valid prior to, or coincident with, latest

occurring chip enable.

11.

t

RC = Read Cycle Time.

12. Chip enable and write enable can initiate and

terminate a WRITE cycle.

13. Output enable (OE\) is inactive (HIGH).

14. Output enable (OE\) is active (LOW).

15. ASI does not warrant functionality nor reliability of

any product in which the junction temperature

exceeds 150∞C. Care should be taken to limit power to

acceptable levels.

Fig. 1 Output Load

Equivalent

Fig. 2 Output Load

Equivalent

DATA RETENTION ELECTRICAL CHARACTERISTICS (L Version Only)

AC TEST CONDITIONS

DESCRIPTION

SYM

MIN

MAX

UNITS

NOTES

Vcc for Retention Data

V

DR

2

V

Data Retention Current

Vcc = 2.0V

I

CCDR

4.5

mA

Chip Deselect to Data

t

CDR

0

ns

4

Operation Recovery Time

t

R

10

ms

4, 11

CONDITIONS

CE\ > V

CC

-0.2V

V

IN

> V

CC

-0.2 or 0.2V