B C M 8 7 0 1 F E A T U R E S

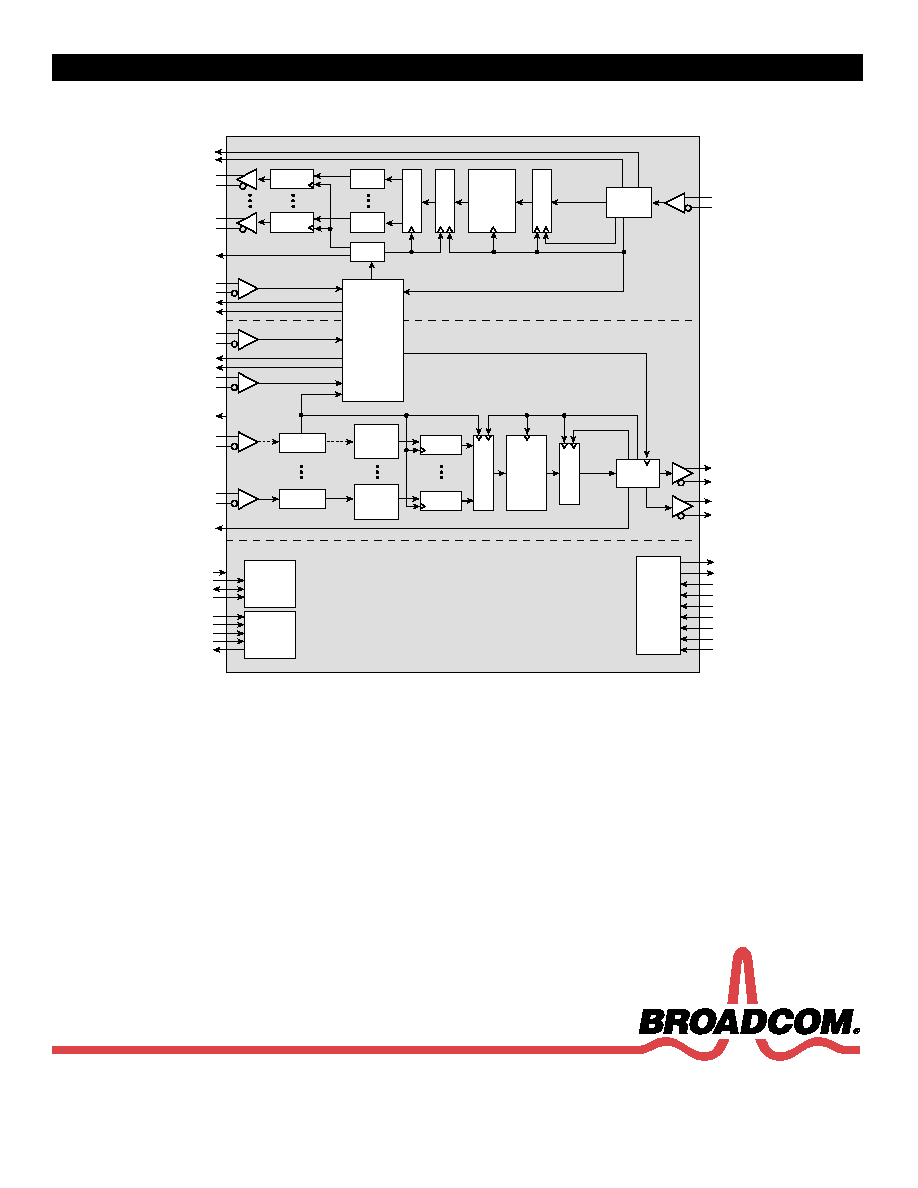

Media

Access

Controller

Interface

MAC

RS

XGXS

XGXS

Management

Interface

XAUI

3.125 Gbps

BCM8701

PCS/PMA

MDC MDIO

OTX

ORX

Optical

PMD

10.3125 Gbps

Application Block Diagram

∑

Low power consumption eliminates external heat

sinks, fans for system airflow, and expensive high-

current power supplies.

∑

Reduces design cycle and time to market.

∑

Uses the most effective silicon economy of scale for

CMOS-based devices.

∑

Target applications:

∑ LAN/WAN switches

∑ Switch/router backbone

∑ Hubs and repeaters

∑ Network interface cards (NICs)

∑ Test equipment

S U M M A R Y O F B E N E F I T S

SERIAL 10 GIGABIT ETHERNET TRANSCEIVER WITH XAUI INTERFACE

PRODUCT

Brief

B C M 8 7 0 1

∑

IEEE 802.3ae compliant, 10.3125, Gbps, serial

Ethernet transceiver (LAN PHY)

∑

Fully integrated CMU, CDR, and SERDES

∑

PMD interface with serial 10.3125 Gbps CML

∑

PSC 64B/66B scrambler/descrambler

∑

XGXS 8B/10B error detection ENDEC

∑

XAUI link synchronization/deskew

∑

Four-lane, 3.125-Gbps XAUI interface

∑

Loss-of-signal detection

∑

Loopback modes

∑

802.3 Clause 33 Management Interface with Extended

Indirect Address Register access

∑

Built-in self-test (BIST)

∑

Power supplies: Core, LVPECL, CML, and XAUI at

1.8V, and CMOS at 1.8 or 3.3V

The BCM8701 Ethernet LAN PHY is a fully integrated

serialization/deserialization (10.3125 Gbps) interface device

performing the extension functions for a 10.3125 Gbps serial

Ethernet Reconciliation Sublayer (RS) interface. The XGXS,

PCS, and PMA functions include 8B/10B coding, 64B/66B

coding, SERDES, Clock Multiplication Unit (CMU), and Clock

and Data Recovery (CDR).

On-chip clock synthesis is performed by the high-frequency,

low-jitter, phase-locked loops for the PMD and XAUI output re-

timers. Individual PMD and XAUI clock recovery are performed

on the device by synchronizing the on-chip VCOs directly to

their respective incoming data streams. Elastic buffers allow

the XAUI and PMD interfaces to operate in either a

synchronous or an asynchronous configuration. An external

156.25-MHz VCXO is required for synchronous mode

operation or for asynchronous mode with clock cleanup.

The BCM8701 is packaged in a 19 x 19 x 1.86 mm BGA with a

1 mm ball pitch.

B C M 8 7 0 1 O V E R V I E W

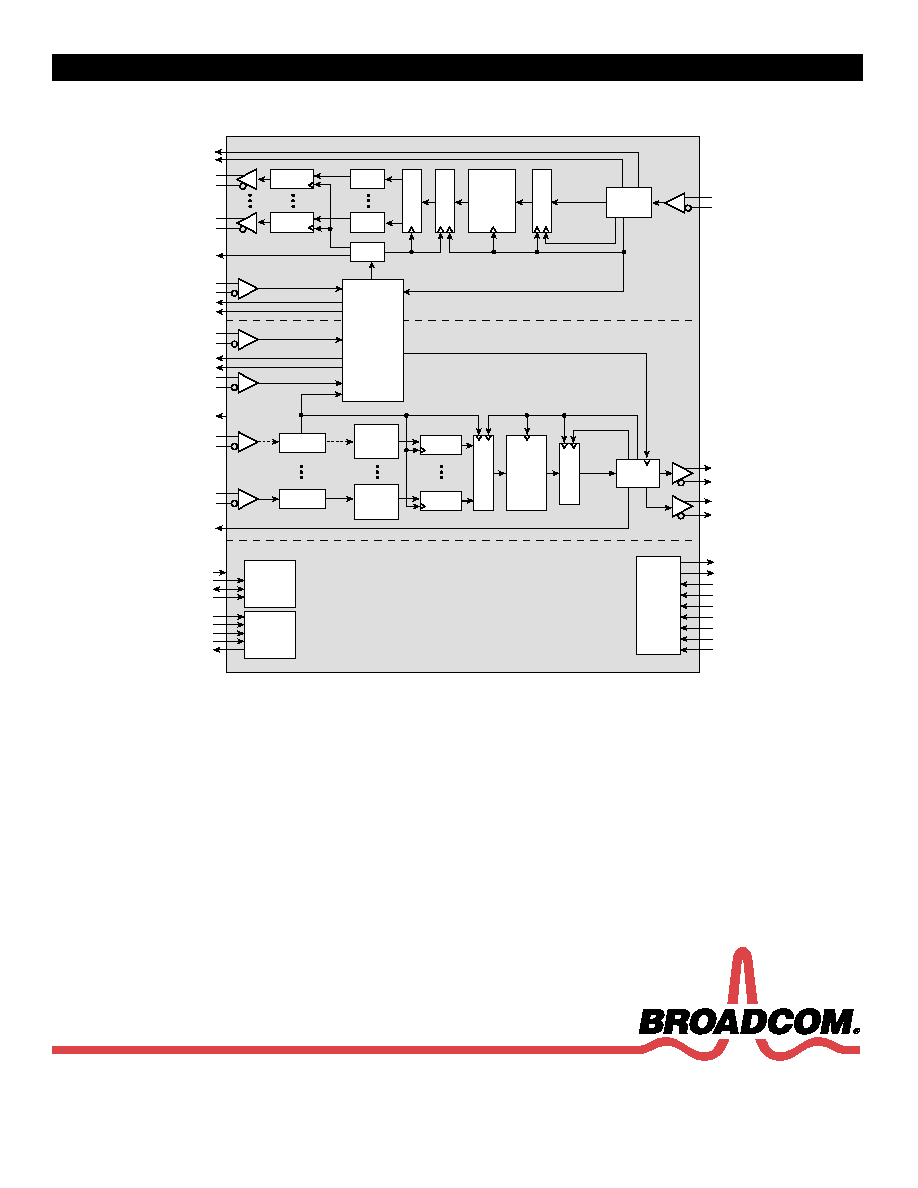

OPTXENB

OPTXRST

OPTXFLT

OPTXLOSBI

OPTXPM

OPTXBM

OPTYPE[1:0]

OPOUTLVL

OPINLVL

PCDRLK

PLOSB

XAOP

XAON

XDOP

XDON

XCMULK

XEXTCLKP

XEXTCLKN

XPDOUT

XPLLLK

PEXTCLKP

PEXTCLKN

PPDOUT

PPLLLK

PVCOXP

PVCOXN

XAIP

XAIN

XLOSB

XDIP

XDIN

PCMULK

RSTB

MDC

MDIO

PHYAD[4:0]

TRST

JTCK

TMS

TDI

TDO

3.125-Gbps

Differential

XAUI

AC-coupled

156.25-MHz

Differential

LVPECL

AC-coupled

3.125-Gbps

Differential

XAUI

PDIP

PDIN

PDOP

PDON

PCOP

PCON

AC-coupled

10.3125-Gbps

Differential

CML

10.3125-Gbps

Differential

CML

10.3125-GHz

Differential

CML

Serializer

Serializer

8B/10B

Encoder

8B/10B

Encoder

CMU

Randomizer

Elastic FIFO

Elastic FIFO

64B/66B

Synchronizer

Descrambler

Decoder

Gearbox

Gearbox

CDR &

Deserializer

Clock

Management

CDR and

Deserializer

CDR and

Deserializer

Sync Detect

Lane Sync

8B/10B

Decoder

Sync Detect

Lane Sync

8B/10B

Decoder

Lane

Alignment

FIFO

Lane

Alignment

FIFO

64B/66B

Encoder

Scrambler

CMU &

Serializer

Receive Path

Transmit Path

Optics

Control

and

Status

Management

Registers

JTAG

For more information please contact us at:

Phone: 949-450-8700, FAX: 949-450-8710

Email: info@broadcom.com

Visit our web site at: www.broadcom.com

© 2001 by BROADCOM CORPORATION. All rights reserved.

8701-PB01-R-8.24.01

Broadcom

Æ

and the pulse logo

Æ

are registered trademarks of Broadcom Corporation

and/or its subsidiaries in the United States and certain other countries.

BROADCOM CORPORATION

16215 Alton Parkway, P.O. Box 57013

Irvine, California 92619-7013

Block Diagram