| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CH7006C-V | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

201-0000-026 Rev. 2.3, 5/2/2001

1

CH7006C

CHRONTEL

Digital PC to TV Encoder Features

Features

∑ Function compatible with CH7004

∑ Universal digital interface accepts YCrCb (CCIR601

or 656) or RGB (15, 16 or 24-bit) video data in both

non-interlaced and interlaced formats

∑ TrueScale

TM

rendering engine supports underscan

operations for various graphic resolutions

•

∑ Enhanced text sharpness and adaptive flicker removal

with up to 5-lines of filtering

∑ Enhanced dot crawl control and area reduction

∑ Fully programmable through serial port

∑ Supports NTSC, NTSC-EIA (Japan), and PAL (B, D,

G, H, I, M and N) TV formats

∑ Provides Composite, S-Video and SCART outputs

∑ Auto-detection of TV presence

∑ Supports VBI pass-through

∑ Programmable power management

∑ 9-bit video DAC outputs

∑ Complete Windows and DOS driver software

∑ Offered in 44-pin PLCC, 44-pin TQFP (1.4 mm)

General Description

Chrontel's CH7006 digital PC to TV encoder is a stand-

alone integrated circuit which provides a PC 99 compliant

solution for TV output. It provides a universal digital

input port to accept a pixel data stream from a compatible

VGA controller (or equivalent) and converts this directly

into NTSC or PAL TV format.

This circuit integrates a digital NTSC/PAL encoder with

9-bit DAC interface, and new adaptive flicker filter, and

high accuracy low-jitter phase locked loop to create

outstanding quality video. Through its TrueScale

TM

scaling and deflickering engine, the CH7006 supports full

vertical and horizontal underscan capability and operates

in 5 different resolutions including 640x480 and 800x600.

A new universal digital interface along with full

programmability make the CH7006 ideal for system-level

PC solutions. All features are software programmable

through a standard serial port, to enable a complete PC

solution using a TV as the primary display.

Patent number 5,781,241

•

Patent number 5,914,753

Figure 1: Functional Block Diagram

TRIPLE

DAC

PLL

RGB-YUV

CONVERTER

SYSTEM CLOCK

Y/R

CVBS/B

C/G

YUV-RGB CONVERTER

DIGITAL

INPUT

INTERFACE

SERIAL PORT

CONTROLLER

LINE

MEMORY

TRUE SCALE

SCALING &

DEFLICKERING

ENGINE

TIMING & SYNC

GENERATOR

NTSC/PAL

ENCODER

& FILTERS

D[15:0]

PIXEL DATA

XCLK

H

V

XI

XO/FIN

P-OUT

SC

SD

RESET*

DS/BCO

RSET

CSYNC

CHRONTEL

CH7006C

2

201-0000-026 Rev. 2.3, 5/2/2001

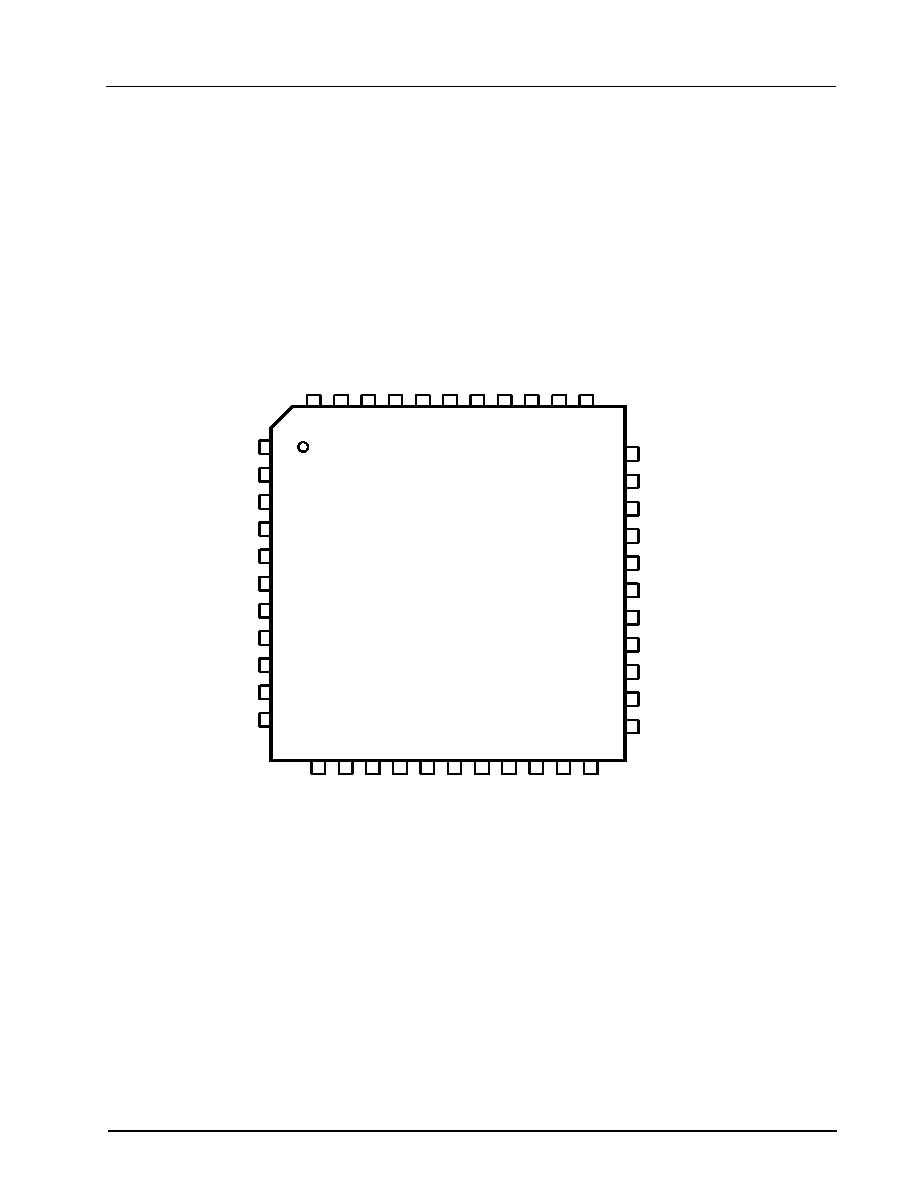

Figure 2: 44-Pin PLCC

XO/FIN

XI

DVDD

RESET*

D[3]

D[4]

D[5]

D[8]

D[6]

DVDD

D[7]

DGND

SC

SD

DGND]

D[9]

D[10]

D[11]

AVDD

VDD

RSET

GND

D[2

]

D[1

]

V

H

XCLK

DVDD

P-OUT

D[0

]

DGND

DS/BCO

AGND

D

[

12]

D

[

13]

D

[

14]

DGN

D

D

[

15]

DV

DD

CS

Y

N

C

GN

D

CVBS

C

Y

7

8

9

10

13

12

11

39

38

37

36

35

14

15

16

17

34

33

32

31

30

29

6

5

4

3

2

1

44

43

42

41

40

18

19

20

21

24

23

22

25

26

27

28

CHRONTEL

CH7006

201-0000-026 Rev. 2.3, 5/2/2001

3

CHRONTEL

CH7006C

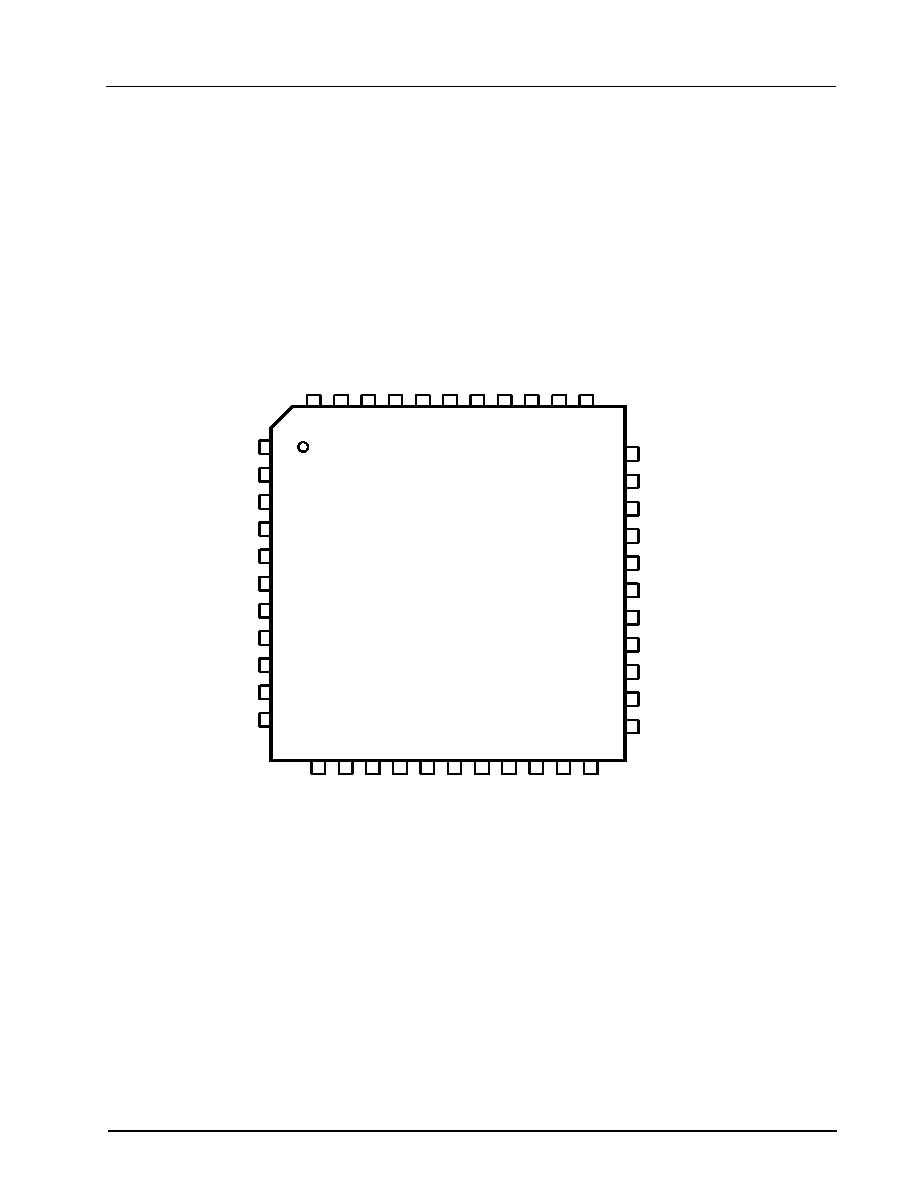

Figure 3: 44-Pin TQFP

XO/FIN

XI

DVDD

ADDR

D[3]

D[4]

D[5]

D[8]

D[6]

DVDD

D[7]

DGND

SC

SD

DGND]

D[9]

D[10]

D[11]

AVDD

VDD

RSET

GND

D[2

]

D[1

]

V

XCLK

DV

DD

P-O

U

T

D[0

]

DG

N

D

D

S

/BCO

AG

N

D

D[1

2

]

D[1

3

]

D[1

4

]

DGND

D[1

5

]

DVDD

CSYNC

GND

CVBS

C

Y

1

2

3

4

7

6

5

33

32

31

30

29

8

9

10

11

28

27

26

25

24

23

44

43

42

41

40

39

38

37

36

35

34

12

13

14

15

18

17

16

19

20

21

22

CHRONTEL

CH7006

D[3]

D[4]

D[5]

D[8]

D[6]

DVDD

D[7]

DGND]

D[9]

D[10]

D[11]

XO/FIN

XI

DVDD

RESET*

DGND

SC

SD

AVDD

VDD

RSET

GND

H

CHRONTEL

CH7006C

4

201-0000-026 Rev. 2.3, 5/2/2001

Table 1. Pin Descriptions

44-Pin

PLCC

44Pin

TQFP

Type

Symbol

Description

4-10,

12-13,

15-21

1,2,

3,4,

6,7,9,

10,11,

12,13,

14,15,

42,43,

44

In

D15-D0

Digital Pixel Inputs

These pins accept digital pixel data streams with either 8, 12, or 16-bit

multiplexed or 16-bit non-multiplexed formats, determined by the input

mode setting (see Registers and Programming section). Inputs D0 - D7

are used when operating in 8-bit multiplexed mode. Inputs D0 - D11

are used when operating in 12-bit mode. Inputs D0 - D15 are used

when operating in 16-bit mode. The data structure and timing

sequence for each mode is described in the section on Digital Input

Port.

43

37

Out

P-OUT

Pixel Clock Output

The CH7006, operating in master mode, provides a pixel data clocking

signal to the VGA controller. This clock will only be provided in master

clock modes and will be tri-stated otherwise. This pin provides the pixel

clock output signal (adjustable as 1X,2X or 3x) to the VGA controller

(see the section on Digital Video Interface, Registers and Programming

for more details). The capacitive loading on this pin should be kept to a

minimum.

1

39

In

XCLK

Pixel Clock Input

To operate in a pure master mode, the P-OUT signal should be

connected to the XCLK input pin. To operate in a pseudo-master mode,

the P-OUT clock is used as a reference frequency, and a signal locked

to this output (at 1X, 1/2X, or 1/3X the P-OUT frequency) is input to the

XCLK pin. To operate in slave mode, the CH7006 accepts an external

pixel clock input at this pin. The capacitive loading on this pin should be

kept to a minimum.

3

41

In/Out

V

Vertical Sync Input/Output

This pin accepts the vertical sync signal from the VGA controller, or

outputs a vertical sync to the VGA controller. The capacitive loading on

this pin should kept to a minimum.

2

40

In/Out

H

Horizontal Sync Input/Output

This pin accepts the horizontal sync from the VGA controller, or outputs

a horizontal sync to the VGA controller. The capacitive loading on this

pin should be kept to a minimum.

41

35

In/Out

DS/BCO

Data/Start (input) / Buffered Clock (output)

When configured as an input, the rising edge of this signal identifies the

first active pixel of data for each active line.

When configured as an output this pin provides a buffered clock output.

The output clock can be selected using the BCO register (17h) (see

Registers and Programming).

38

32

In

XI

Crystal Input

A parallel resonance 14.31818 MHz (± 50 ppm) crystal should be

attached between XI and XO/FIN. However, if an external CMOS clock

is attached to XO/FIN, XI should be connected to ground.

39

33

In

XO/FIN

Crystal Output or External Fref

A 14.31818 MHz (± 50 ppm) crystal may be attached between XO/FIN

and XI. An external CMOS compatible clock can be connected to

XO/FIN as an alternative.

44-Pin

PLCC

44Pin

TQFP

Type

Symbol

Description

30

24

In

RSET

Reference Resistor

A 360

resistor with short and wide traces should be attached

between RSET and ground. No other connections should be made to

this pin.

201-0000-026 Rev. 2.3, 5/2/2001

5

CHRONTEL

CH7006C

28

22

Out

Y/R

Luminance Output

A 75

termination resistor with short traces should be attached

between Y and ground for optimum performance. In normal operating

modes other than SCART and RGB bypass, this pin outputs the

composite video signal. In SCART and RGB Bypass modes, this pin

outputs the red signal.

27

21

Out

C/G

Chrominance Output

A 75

termination resistor with short traces should be attached

between C and ground for optimum performance. In normal operating

modes other than SCART and RGB bypass, this pin outputs the

composite video signal. In SCART and RGB Bypass modes, this pin

outputs the green signal.

26

20

Out

CVBS/B

Composite Video Output

A 75

termination resistor with short traces should be attached

between CVBS and ground for optimum performance. In normal

operating modes other than SCART and RGB bypass, this pin outputs

the composite video signal. In SCART and RGB Bypass modes, this pin

outputs the blue signal.

23

17

Out

CSYNC

Composite Sync Output

A 75

termination resistor with short traces should be attached

between CSYNC and ground for optimum performance. In SCART

mode, this pin outputs the composite sync signal.

32

26

In/Out

SD

Serial Data (External pull-up required)

This pin functions as the serial data pin of the serial port, and uses the

DVDD supply and is not 5V tolerant.

33

27

In

SC

Serial Clock (Internal pull-up)

This pin functions as the serial clock pin of the serial port, and uses the

DVDD supply and is not 5V tolerant.

35

29

In Reset*

Reset Input

When this pin is low, the CH7006 is held in the power-on reset

condition. When this pin is high, the device operates normally and

reset is controlled through the serial port register.

40 34

Power

AGND

Analog ground

This pin provides the ground reference for the analog section of the

CH7006, and MUST be connected to the system ground, to prevent

latchup. Refer to the Application Information section for information on

proper supply decoupling.

37

31

Power

AVDD

Analog Supply Voltage

This pins supplies the 5V power to the analog section of the CH7006.

31

25

Power

VDD

DAC Power Supply

This pins supplies the 5V power to CH7006's internal DAC's.

44-Pin

PLCC

44Pin

TQFP

Type

Symbol

Description

25, 29

19,23

Power

GND

DAC Ground

These pins provide the ground reference for CH7006's internal DACs.

For information on proper supply decoupling, please refer to the

Application Information section.

11, 22,

36, 44

5,16,

30,38

Power

DVDD

Digital Supply Voltage

These pins supply the 3.3V power to the digital section of CH7006.

14, 24,

34, 42

8,18,

28,36

Power

DGND

Digital Ground

These pins provide the ground reference for the digital section of

CH7006, and MUST be connected to the system ground to prevent

latchup.

N/A

N/A

Out

R

R (Red) Component Output

This pin provides the analog Red component of the digital RGB input in

the RGB Pass-Through mode.

Table 1. Pin Descriptions