| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CD6420 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

1

Copyright

©

Cirrus Logic, Inc. 1997

(All Rights Reserved)

Cirrus Logic, Inc.

Crystal Semiconductor Products Division

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.crystal.com

CS6420

Full-Duplex Speakerphone Chip

Features

l

Single-chip full-duplex hands-free operation

l

Automatic gain control

l

Optional 34 dB microphone preamplifier

l

Integrated mute and volume control

l

Integrated 80 dB IDR dual codec

l

Speech-trained Network and Acoustic Echo

Cancellers

l

Powerdown mode

l

Microcontroller Interface

General Description

Most modern speakerphones use half-duplex operation,

which switches transmission between the far-end talker

and the speakerphone user. This is done because the

acoustic coupling between the speaker and microphone

is much higher in speakerphones than in handsets

where the coupling is mechanically suppressed.

The CS6420 enables full-duplex conversation with a sin-

gle-chip solution. The CS6420 can easily replace

existing half-duplex speakerphone ICs with a huge in-

crease in conversation quality.

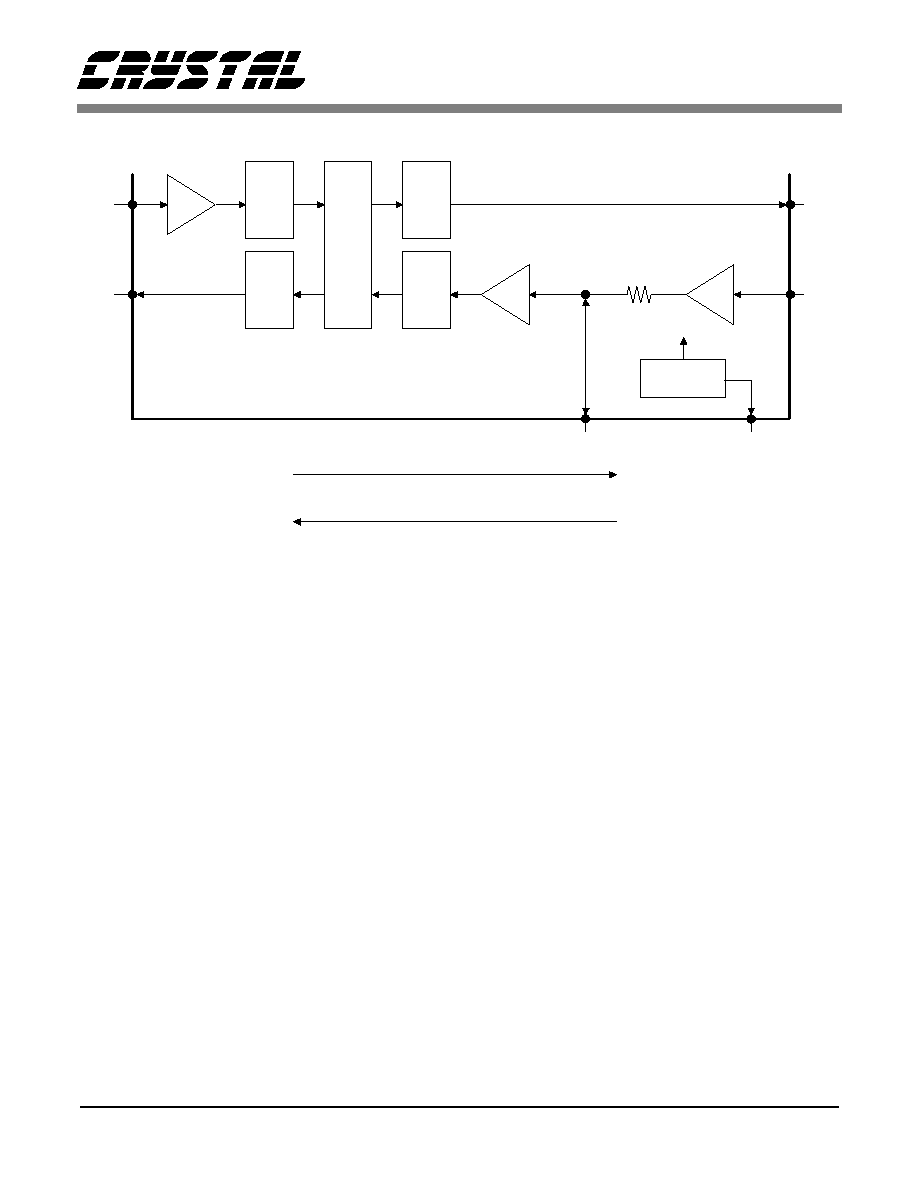

The CS6420 consists of telephone & audio interfaces,

two codecs and an echo-cancelling DSP.

ORDERING INFORMATION

CS6420-CS

20-pin SOIC

CDB6420

Evaluation Board

BANDGAP

AO

DGND

NI

DATA

STROBE

DRDY

CLKI

CLKO

API

RST

Microcontroller Interface

NO

AVDD

DVDD

AVDD

NC4

NC3

NC2

NC1

AGND

AD

C

0,6,9.5,12 dB

H

i

gh P

a

s

s

Filt

e

r

Rx

AG

C

Rx

S

u

ppr

es

s

i

on

Hal

f

Dupl

e

x

Mu

te

/V

o

l

u

m

e

Co

ntr

o

l

DA

C

+

-

Pre-Emphasis

Network

Echo Canceller

Filter

AD

C

0,6,9.5,12 dB

Filt

e

r

Hg

i

h

P

a

s

s

Tx

A

G

C

S

u

ppre

s

s

i

on

Tx

Hal

f

D

upl

ex

Con

t

r

o

l

Mu

te

/V

o

l

u

m

e

DA

C

+

-

Filter

Echo Canceller

Acoustic

Pre-Emphasis

APO

MB

34 dB

1 k

2.12 V

3.5 V

Clock

Generation

JUN `97

DS205PP2

CS6420

2

DS205PP2

TABLE OF CONTENTS

Absolute Maximum Ratings ..............................................................................................4

Recommended Operating Conditions..............................................................................4

Power Consumption ..........................................................................................................4

Analog Characteristics ........................................................................................................4

Analog Transmission Characteristics..............................................................................5

Microphone Amplifier ........................................................................................................5

Digital Characteristics .......................................................................................................5

Overview ............................................................................................................................8

Functional Description .....................................................................................................8

Analog Interface .......................................................................................................8

Acoustic Interface ..............................................................................................9

Network Interface ............................................................................................10

Microcontroller Interface .........................................................................................10

Description ......................................................................................................10

Register Definitions .........................................................................................11

Register 0..................................................................................................12

Mic - Microphone Preamplifier Enable ...............................................12

TSD - Transmit Suppression Disable.................................................12

GB - Graded Beta ..............................................................................12

ACC - Acoustic Coefficient Control ....................................................13

RVol - Receive Volume Control .........................................................13

TGain - Transmit Analog Gain ...........................................................13

Register 1..................................................................................................14

HD - Half-Duplex Disable...................................................................14

RSD - Receive Suppression Disable .................................................14

Taps - AEC/NEC Tap Allocation ........................................................15

NCC - Network Coefficient Control ....................................................15

TVol - Transmit Volume Control.........................................................15

RGain - Receive Analog Gain............................................................15

Register 2..................................................................................................16

NErle - Network ERLE Threshold ......................................................16

NFNse - Network Full-Duplex Noise Threshold .................................16

RHDet - Receive Half-Duplex Detection Threshold ...........................17

HDly - Half-Duplex Holdover Delay....................................................17

NseRmp - Background Noise Power Estimator Ramp Rate..............17

RSThd - Receive Suppression Threshold..........................................17

PCSen- Path Change Sensitivity .......................................................17

Register 3..................................................................................................18

AErle - Acoustic ERLE Threshold ......................................................18

AFNse - Acoustic Full-Duplex Noise Threshold.................................18

THDet - Transmit Half-Duplex Detection Threshold ..........................18

TSAtt - Transmit Suppression Attenuation.........................................19

TSBias - Transmit Suppression Bias .................................................19

TSThd - Transmit Suppression Threshold .........................................19

HHold - Hold in Half-Duplex on Howl.................................................19

Reset ...............................................................................................................19

Clocking ..................................................................................................................19

Power Supply .........................................................................................................20

Power Down Mode ..........................................................................................20

Noise and Grounding ......................................................................................21

Design Considerations ...................................................................................................22

Algorithmic Considerations .....................................................................................22

Full-Duplex Mode ............................................................................................22

Theory of Operation ..................................................................................22

Adaptive Filter ...........................................................................................23

Pre-Emphasis ....................................................................................23

Graded Beta.......................................................................................23

Update Control ..........................................................................................24

CS6420

DS205PP2

3

Speech Detection ..................................................................................... 24

Half-Duplex Mode ........................................................................................... 24

AGC ................................................................................................................ 25

Suppression .................................................................................................... 25

Transmit Suppression............................................................................... 26

Receive Suppression ................................................................................ 27

Circuit Design ......................................................................................................... 27

Interface Considerations ................................................................................. 27

Analog Interface........................................................................................ 27

Microcontroller Interface ........................................................................... 27

Grounding Considerations .............................................................................. 28

Layout Considerations .................................................................................... 28

System Design ....................................................................................................... 28

Gain Structure ................................................................................................. 28

Testing Issues ................................................................................................. 29

ERLE ........................................................................................................ 29

Convergence Time ................................................................................... 30

Half-Duplex Switching............................................................................... 30

Pin Descriptions .............................................................................................................. 31

Analog Interface .............................................................................................. 31

Microcontroller Interface ................................................................................. 32

Clock ............................................................................................................... 32

Power Supply .................................................................................................. 32

Miscellaneous ................................................................................................. 33

Glossary ........................................................................................................................... 34

Package Dimensions ...................................................................................................... 37

CS6420

4

DS205PP2

WARNING: Operation beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Notes: 1. AO and NO outputs are not loaded.

Notes: 2. These parameters are guaranteed by design or by characterization.

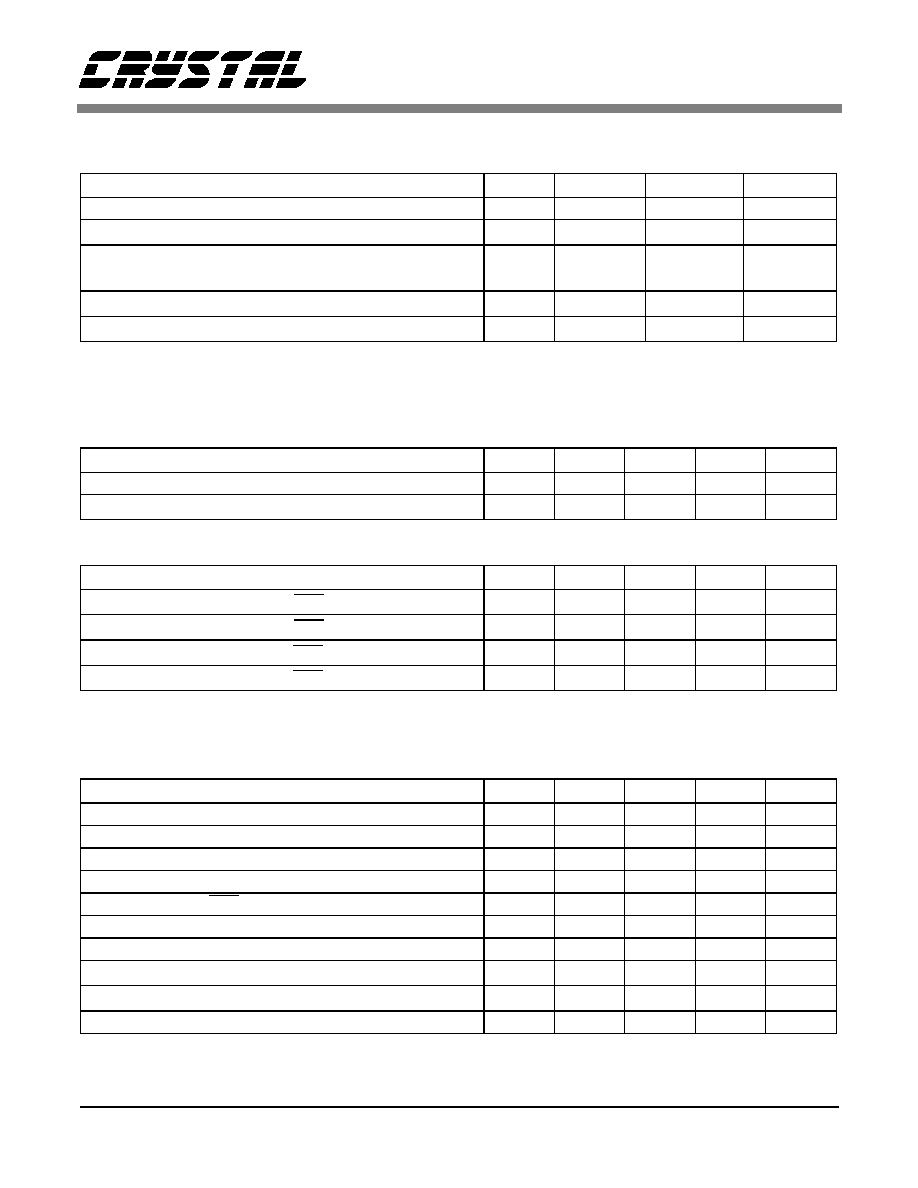

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Min

Max

Units

DC Supply (AVDD, DVDD)

-0.3

6.0

V

Input Current (Except supply pins)

I

in

-10

+10

mA

Input Voltage

Analog

Digital

V

ina

V

ind

-0.3

-0.3

AVDD+0.3

DVDD+0.3

V

Ambient Operating Temperature

T

A

-40

85

∞C

Storage Temperature

T

stg

-65

150

∞C

RECOMMENDED OPERATING CONDITIONS

Parameter

Symbol

Min

Typ

Max

Units

DC Supply (AVDD, DVDD)

4.5

5.0

5.5

V

Ambient Operating Temperature

T

AOp

0

25

70

∞C

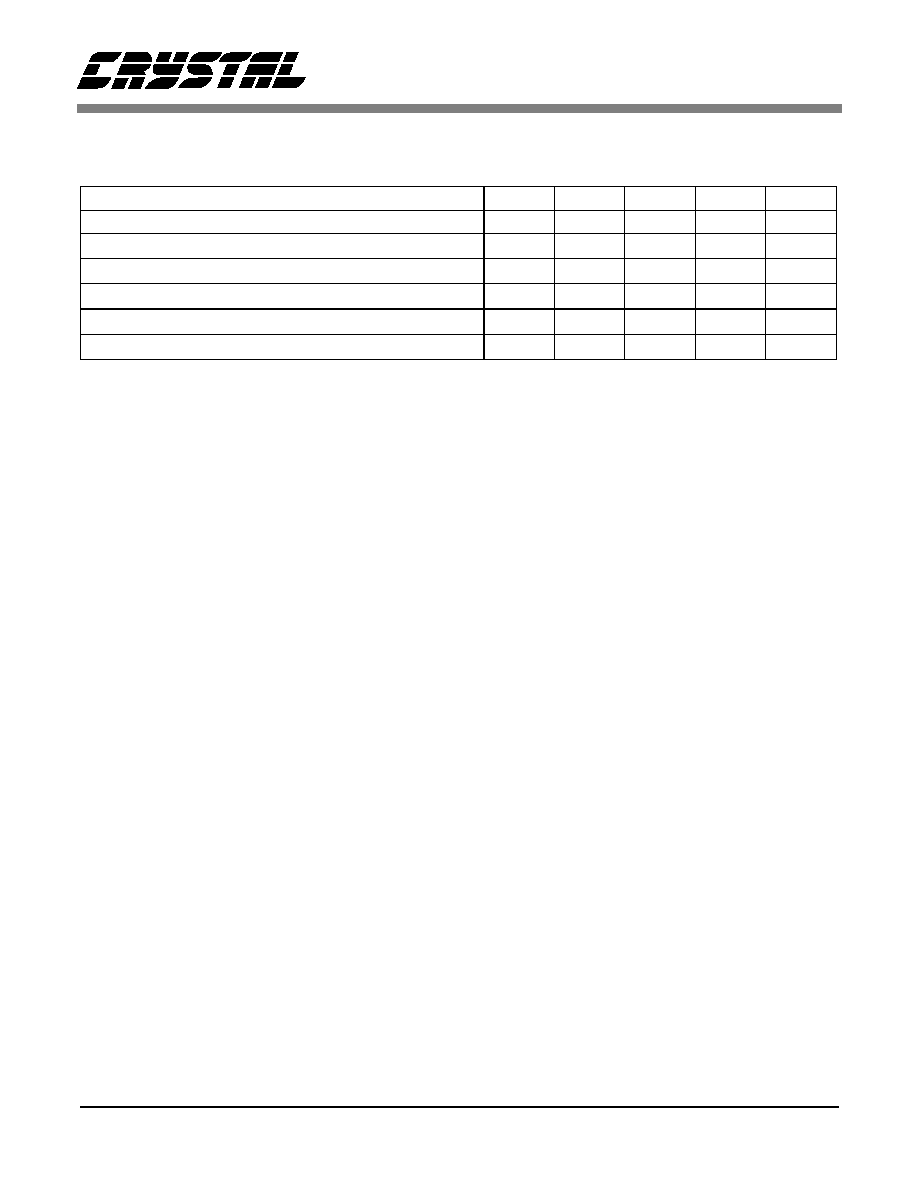

POWER CONSUMPTION

(T

A

= 25∞C, DVDD = AVDD = 5V, f

XTAL

= 20.480 MHz) (Note 1)

Parameter

Symbol

Min

Typ

Max

Units

Power Supply Current, Analog (RST=0)

P

DA0

1

mA

Power Supply Current, Analog (RST=1)

P

DA

10

20

mA

Power Supply Current, Digital (RST=0)

P

DD0

1

mA

Power Supply Current, Digital (RST=1)

P

DD

50

60

mA

ANALOG CHARACTERISTICS

(T

A

= 25∞C, DVDD = AVDD = 5V, f

XTAL

= 20.480 MHz)

Parameter

Symbol

Min

Typ

Max

Units

Input Offset Voltage (APO, NI)

2.12

V

Output Offset Voltage (AO, NO)

2.12

V

Transmit Group Delay

(Note 2)

6

ms

Receive Group Delay

(Note 2)

6

ms

Settling Time from RST rising

104

ms

MB Output Voltage

3.5

V

MB Drive Capability

10

µ

A

Input Impedance (APO, NI)

(Note 2)

Z

in

300

k

Load Impedance (AO, NO)

(Note 2)

Z

load

10

k

Power Supply Rejection (1 kHz)

40

dB

CS6420

DS205PP2

5

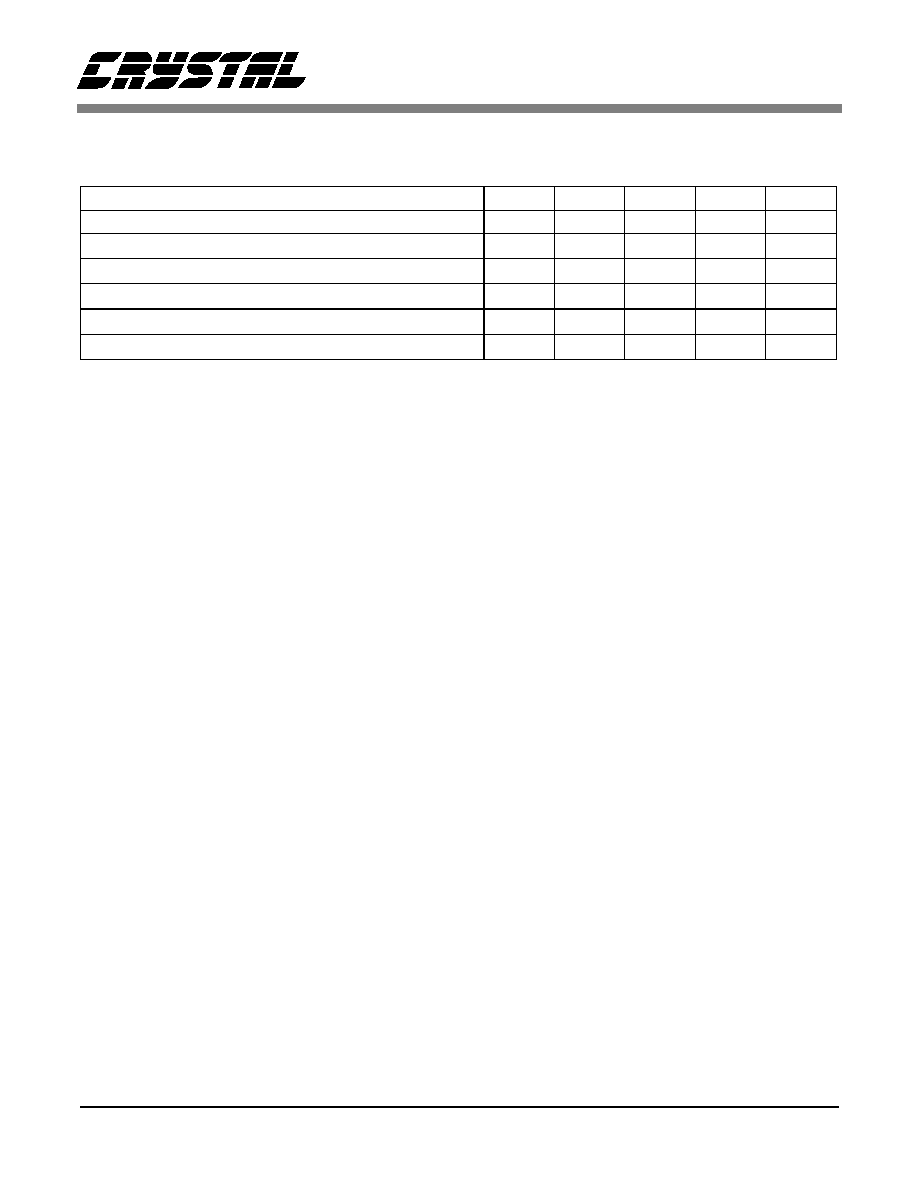

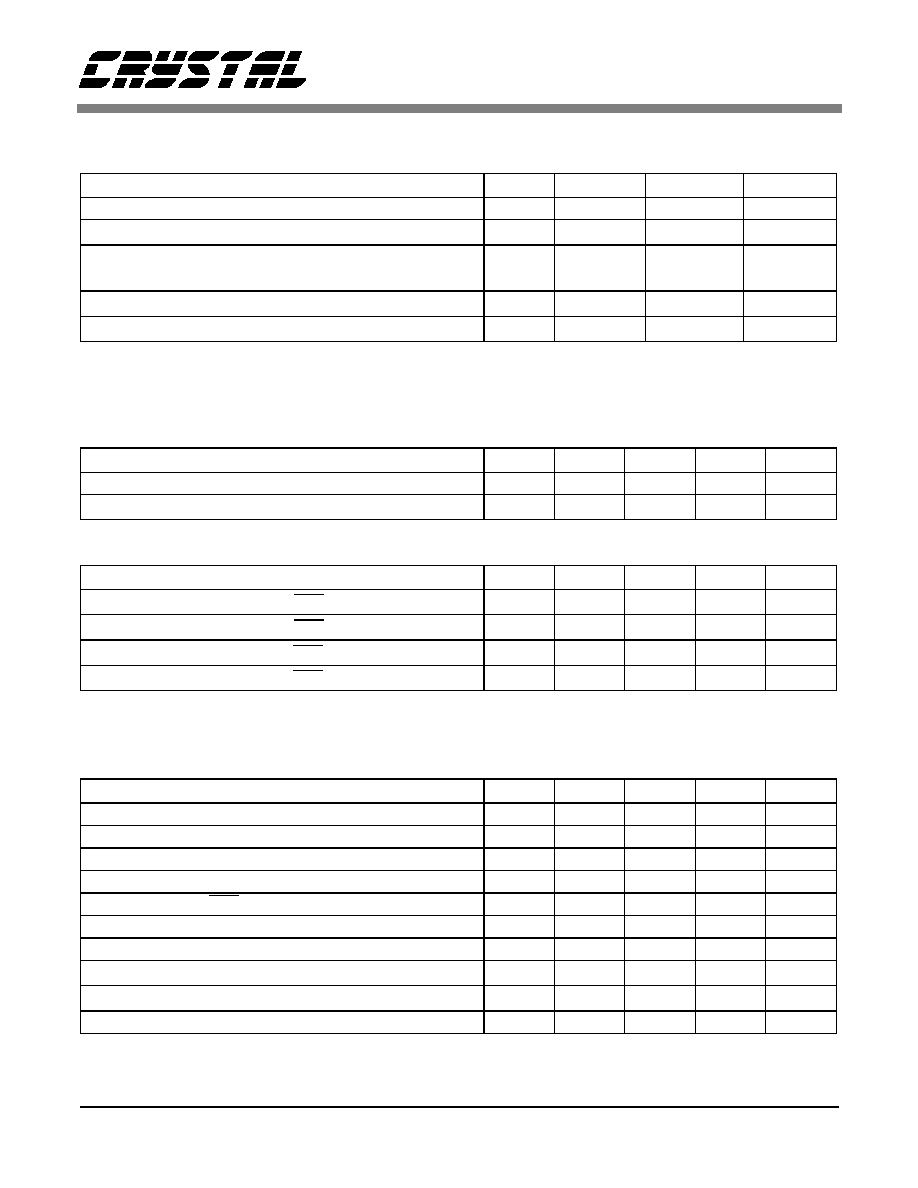

ANALOG TRANSMISSION CHARACTERISTICS

(T

A

= 25∞C, DVDD = AVDD = 5V, f

XTAL

=

20.480 MHz, RVol=TVol=RGain=TGain= 0 dB, HD=TSD=RSD=1, analog inputs and ouputs loaded with resistors

and capacitors as shown in the typical connection diagram, Figure 2)

Parameter

Symbol

Min

Typ

Max

Units

Idle Channel Noise

A-weighted (0-20 kHz)

(Inputs grounded

C-Message weighted (0-4 kHz)

through a capacitor)

Psophometrically weighted (0-4 kHz)

17

-67

-69

dBV

dBrnC0

dBm0p

Signal-to-Noise Ratio

A-weighted (0-20 kHz)

(Full Scale, 1 kHz

C-Message weighted (0-4 kHz)

sine wave input)

Psophometrically weighted (0-4 kHz)

SNR

69

17

-67

dB

dBrnC0

dBm0p

Total Harmonic Distortion

C-Message Weighted (0-4 kHz)

THD

0.1

%

Programmable Gain

RGain/TGain = 00

RGain/TGain = 01

RGain/TGain = 10

RGain/TGain = 11

0

6

9.5

12

dB

Volume Control Stepsize (TVol/RVol)

3

dB

ADC Full-scale Voltage Input

0.9

1.0

Vrms

DAC Full-scale Voltage Output

1.0

1.1

Vrms

ADC Noise Floor

C-Message Weighted (0-4 kHz)

-80

dBV

DAC Noise Floor, DAC muted C-Message Weighted (0-4 kHz)

-85

dBV

MICROPHONE AMPLIFIER

(T

A

= 25∞C, DVDD = AVDD = 5V,f

XTAL

= 20.480 MHz)

Parameter

Symbol

Min

Typ

Max

Units

Gain (Zsource = 50

)

A

mic

34

dB

Signal-to-Noise Ratio

A-weighted (0-20 kHz)

SNR

m

63

dB

Input Impedance

Z

inm

5

k

Input Offset Voltage

V

offm

2.12

V

DIGITAL CHARACTERISTICS

(T

A

= 25∞C, DVDD = AVDD = 5V,f

XTAL

= 20.480 MHz)

Parameter

Symbol

Min

Typ

Max

Units

High-Level Input Voltage

V

IH

DVDD-1.0

V

Low-Level Input Voltage

V

IL

1.0

V

Input Leakage Current

I

leak

10

µ

A

Input Capacitance

C

IN

5

pF

CS6420

6

DS205PP2

SWITCHING CHARACTERISTICS

Parameter

Symbol

Min

Typ

Max

Units

Input rise time

t

rise

1.0

µs

RST low time

t

RSTL

1.0

µs

CLKI frequency

f

XTAL

18.432

20.480

22.528

MHz

CLKI duty cycle

t

LCLKI

40

50

60

%

DRDY frequency

f

DRDY

DC

f

XTAL

/ 2560

kHz

STROBE frequency

f

STROBE

DC

9.0

MHz

DRDY to STROBE setup time

t

sDRDY

30

ns

DATA to STROBE setup time

t

sDATA

30

ns

STROBE to DATA hold time

t

hDATA

30

ns

STROBE to DRDY hold time

t

hDRDY

30

ns

Bit15

DATA

DRDY

STROBE

Bit14

Bit0

t sDRDY

t sDATA

t hDATA

t hDRDY

Figure 1. Microcontroller Interface Switching Characteristics

CS6420

DS205PP2

7

AVDD

AGND

API

APO

MB

AO

CLKO

CLKI

STROBE

DATA

DRDY

NI

NO

DGND

DVDD

0.1

µ

F

1

µ

F

+

0.1

µ

F

1

µ

F

+

0.47

µ

F

10

µ

F

22pF

Telephone

Line Out

Telephone

Line In

From

Microprocessor

22pF

+5V Analog

0.022

µ

F

0.1

µ

F

+

RST

NC1

NC2

NC3

NC4

1

2

20

18

19

3

3300pF

12.1 k

13

14

9

10

11

12

20.480 MHz

8

6

5

7

3300 pF

6.04 k

0.47

µ

F

3300 pF

12.1 k

17

4

15

16

ferrite bead

1.5 k

+5V Analog

10 k

Figure 2. Typical Connection Diagram (Microphone Preamplifier Enabled)

AVDD

AGND

API

APO

MB

AO

CLKO

CLKI

STROBE

DATA

DRDY

NI

NO

DGND

DVDD

0.1

µ

F

1

µ

F

+

0.1

µ

F

1

µ

F

+

0.47

µ

F

10

µ

F

22pF

Telephone

Line Out

Telephone

Line In

From

Microprocessor

22pF

+5V Analog

0.1

µ

F

+

RST

NC1

NC2

NC3

NC4

1

2

20

18

19

3

3300pF

12.1 k

13

14

9

10

11

12

20.480 MHz

8

6

5

7

3300 pF

6.04 k

0.47

µ

F

3300 pF

12.1 k

17

4

15

16

ferrite bead

3300 pF

0.47

µ

F

near-end

input

6.04 k

Figure 3. Typical Connection Diagram (Microphone Preamplifier Disabled)

CS6420

8

DS205PP2

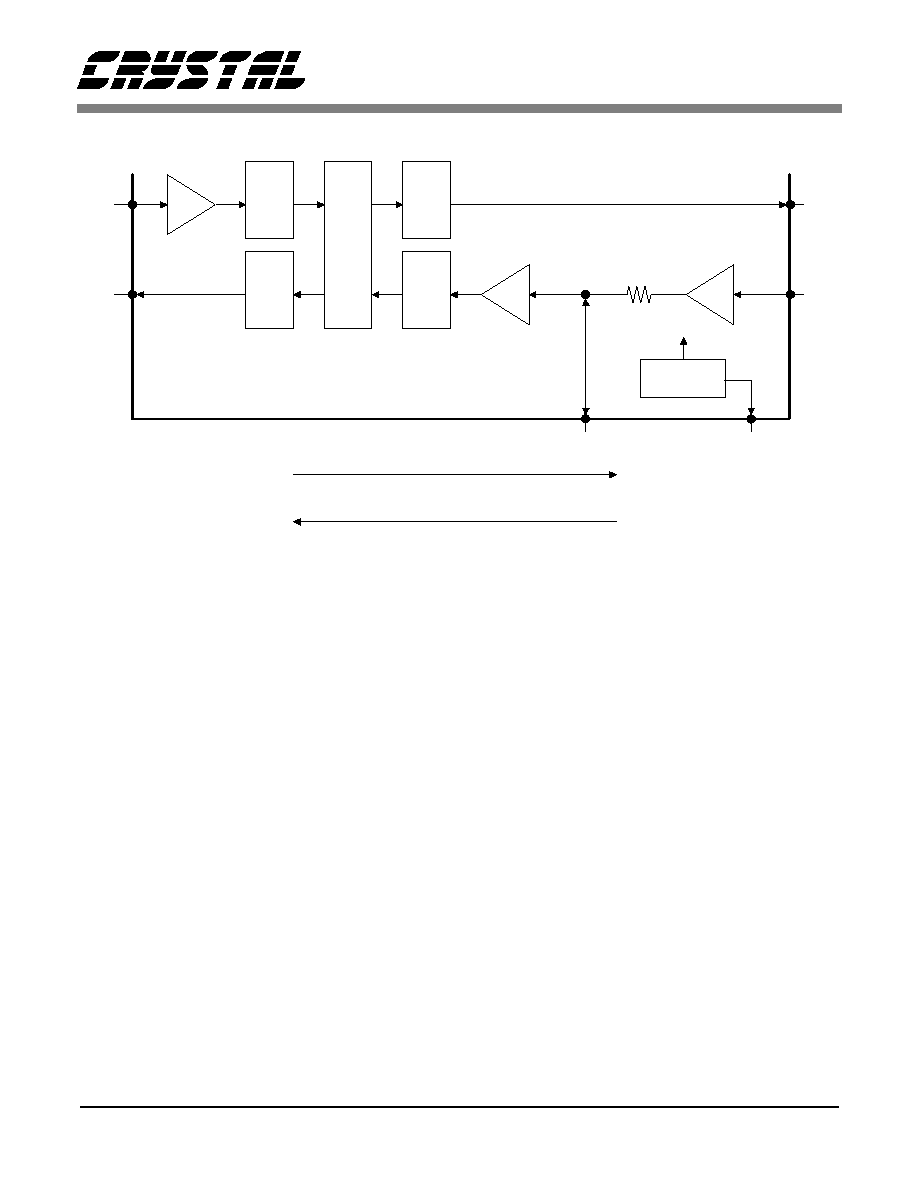

OVERVIEW

The CS6420 is a full-duplex speakerphone chip for

use in hands-free communications with telephony

quality audio. Common applications include

speakerphones, inexpensive video-conferencing,

and cellular phone car kits. The CS6420 requires

very few external components and allows system

control through a microcontroller interface.

Hands-free communication through a microphone

and speaker typically results in acoustic feedback

or howling because the loop gain of the system ex-

ceeds unity by the time audio amplitudes are ad-

justed to a reasonable level. The solution to the

howling problem has typically been half-duplex,

where either the transmit or the receive channel is

active, never both at the same time. This prevents

the howling, but diminishes the overall communi-

cation quality by clipping words and forcing the

talker at each end to wait for the talker at the other

end to stop speaking.

Full-duplex conversation, where both transmit and

receive channels are active simultaneously, is the

conversation quality we enjoy when using hand-

sets. Full-duplex for hands-free communications is

achieved in the CS6420 using a digital signal pro-

cessing technique called "Echo Cancellation." The

end result is a more natural conversation than half-

duplex, with no awkward breaks and pauses, as if

both parties were speaking to each other directly.

Echo Cancellation reduces overall loop gain and

the acoustic coupling between speaker and micro-

phone. This coupling reduction prevents the annoy-

ing effect of hearing one's own delayed speech, the

effect being worse when there is delay in the sys-

tem, such as vocoder delay in digital cellular

phones.

The CS6420 is a complete system implementation

of a Digital Signal Processor with RAM and pro-

gram ROM, running Echo Cancellation algorithms

developed at Crystal Semiconductor using custom-

er input, integrated with two delta-sigma codecs.

The CS6420 is intended to provide a full-duplex

speakerphone solution with a minimum of design

effort while displacing existing half-duplex speak-

erphone chips.

FUNCTIONAL DESCRIPTION

The CS6420 is roughly divided into four external

interface blocks. The analog interfaces connect the

chip to the transmit and receive paths. Certain con-

trol functions are accessible through the microcon-

troller interface. Two pins accommodate either a

crystal or an externally applied digital clock signal.

Analog and digital power and ground are provided

through four pins.

Analog Interface

In a speakerphone application, one input of the

CS6420 connects to the signal from the micro-

phone, sometimes called the near-end input or

transmit input, and one output connects to the

speaker. The output that leads to the speaker is

sometimes called the near-end output or receive

output. Together, the input and output that connect

to the microphone and speaker are referred to as the

Acoustic Interface.

The signal received at the near-end input is then

passed to the far-end output or transmit output after

acoustic echo cancellation. This signal is sent to the

telephone line. The signal from the telephone line

is received at the far-end input, also called the re-

ceive input, and this signal is passed to the receive

output after network echo cancellation. Together,

the far-end input and output form the Network In-

terface.

The analog interfaces are physically implemented

using delta sigma converters running at an output

word rate of 8 kHz, resulting in a passband from

DC to 4 kHz. Because the inputs are analog to dig-

ital converters (ADCs), certain design consider-

ations must be kept in mind: specifically, anti-

aliasing and full-scale input voltage. The ADCs ex-

pect a single-pole RC filter with a corner at 8 kHz,

CS6420

DS205PP2

9

and they are post-compensated internally to pre-

vent any resultant passband droop. The ADCs also

expect a maximum of 1 V

rms

(2.8 V

pp

) at their in-

puts (which are biased around 2.12 VDC). A signal

of higher amplitude will clip the ADC input and

may result in poor echo canceller performance. See

the Design Considerations section for more details.

The outputs are delta-sigma digital to analog con-

verters (DACs) and have similar requirements to

the ADCs. The DACs are pre-compensated to ex-

pect a single-pole RC filter with a corner frequency

at 4 kHz. The full scale voltage output from a DAC

is 1 V

rms

(2.8 V

pp

) swinging around a DC bias of

2.12 V.

Acoustic Interface

The pins API (pin 20), APO (pin 18), MB (pin 19),

and AO (pin 3) make up the Acoustic Interface. A

block diagram of the Acoustic Interface is shown in

Figure 4.

API and APO are, respectively, the input and out-

put of the built-in analog pre-amplifier. The pre-

amplifier is an inverting amplifier with a fixed gain

of 34 dB biased around an input offset voltage

(V

off

) of 2.12 V. APO is the output of the pre-am-

plifier after a 1 k

resistor. The circuitry connected

to the amplifier input must present low source im-

pedance (<100

) to the API pin or the gain will be

reduced. When using the pre-amplifier, connecting

a 0.022

µ

F capacitor to ground off APO will pro-

vide the anti-aliasing filter required by the ADC, as

shown in Figure 2. The pre-amplifier may be by-

passed by clearing Mic (Register 0, bit 15) using the

Microcontroller Interface (see Microcontroller In-

terface section), grounding API through a capacitor,

and driving APO directly. In this case, the signal into

APO must be low-pass filtered by a single-pole RC

filter with a corner frequency at 8 kHz (see Figure 3).

Following the pre-amplifier is a programmable an-

alog gain stage (PGA) which is controllable

through the Microcontroller Interface. This gain

19 MB

18 APO

20

AO

0,6,9.5,12 dB

ADC

DAC

DAC

ADC

D

S

P

NI

17

NO

4

FAR-END

Transmit Path

Receive Path

API

3.5V

2.12V

1k

BANDGAP

34 dB

0,6,9.5,12 dB

NEAR-END

3

PGA

PGA

Figure 4. Analog Interface

CS6420

10

DS205PP2

stage allows gains of 0 dB, 6 dB, 9.5 dB, and 12 dB

to be added prior to the ADC input. The default

gain stage setting is 0 dB.

The signal at APO should not exceed 2.8 V

pp

at the

default gain stage setting. If other gain stages are

used then the full-scale signal at APO must also

change. Table 1 shows full-scale voltages as mea-

sured at APO for given programmable gains:

Table 1. Full scale voltages for each gain stage.

MB provides a stable 3.5 VDC output from the on-

board voltage reference of the CS6420. MB may

not be connected to any load. MB serves to provide

decoupling for the internal 2.12 VDC bandgap ref-

erence, and must have a 0.1

µ

F and a 10

µ

F capac-

itor to ground for bypass. Noise on MB will

strongly influence the overall analog perfor-

mance of the CS6420.

The acoustic output, AO, should connect to a sin-

gle-pole low-pass RC network with a corner fre-

quency of 4 kHz, which will filter out-of-band

components. The maximum voltage swing at AO is

2.8 V

pp

. AO is capable of driving down to a 10 k

load.

Network Interface

The pins NI (pin 17) and NO (pin 4) make up the

Network Interface. The details of the Network In-

terface are shown in Figure 4.

NI is the input from the telephone network side into

the CS6420. The signal into NI must be low pass

filtered by a single-pole RC filter with a corner fre-

quency of 8 kHz.

A programmable analog gain stage (PGA) accessi-

ble through the Microcontroller Interface amplifies

signals received at NI. This gain stage allows gains

of 0 dB, 6 dB, 9.5 dB, and 12 dB to be added prior

to the ADC input. The default gain stage setting for

the network side is 0 dB.

The signal at NI should not exceed 2.8 V

pp

at the

default gain stage setting. If other gain stages are

used then the full-scale signal at NI must also

change. Table 1 shows full-scale voltages as mea-

sured at NI for given programmable gains.

The output to the telephone network side, NO,

should connect to a single pole RC network with a

corner frequency at 4 kHz, which will filter out-of-

band components. The maximum swing NO is ca-

pable of producing is 2.8 V

pp

. NO is capable of

driving down to a 10 k

load.

Microcontroller Interface

Several control functions of the CS6420 are acces-

sible through its Microcontroller Interface, which

consists of three pins: DATA (pin 8), STROBE

(pin 7), and DRDY (pin 6). These inputs are intend-

ed to connect to the outputs of a microcontroller to

allow write-only access to the 16-bit Microcontrol-

ler Control Register (MCR).

The RST (pin 5) pin, which affects the entire inte-

grated circuit, is especially significant to the Micro-

controller Interface. RST is used to place the

CS6420 into a known state of operation. Two sub-

types of reset are possible: cold reset and warm re-

set.

Description

The Microcontroller Interface is implemented by a

serial shift register gated by DRDY. The microcon-

troller begins the transaction by setting DRDY low

and STROBE low. The most significant bit (MSB),

Bit 15, of the 16-bit data word should be presented

to the DATA pin and then STROBE should be

brought high to shift the data bit into the CS6420.

STROBE should be brought low again so it is ready

Gain Setting

Full-scale Voltage

0 dB

2.8 V

pp

6 dB

1.4 V

pp

9.5 dB

0.94 V

pp

12 dB

0.71 V

pp

CS6420

DS205PP2

11

to shift the next bit into the shift register. The next

data bit should then be presented to the DATA pin

ready to be latched by the rising edge of STROBE.

This procedure repeats for all sixteen bits as shown

in Figure 5. After the last bit has been shifted in,

DRDY should be brought high to indicate the con-

clusion of the transfer, and four extra STROBE

pulses must be applied to latch the data into the

CS6420.

Since the MCR is a shift register, the STROBE can

be run arbitrarily slow with a duty cycle limited

only by the hold time specified in the Switching

Characterstics table. The Microcontroller Interface

is read once every 125

µ

s, so it must not be updated

faster than this.

Register Definitions

The four control registers accessible through the

MCR are described in detail in the following tables.

These registers are addressed by bits b2 and b1 of

the MCR. Bit b0 must always be 0. Table 2 shows

the relative bit positions of all the registers. Tables

3 to 6 show the four control registers in more detail.

The Register Map at the top of each register de-

scription shows the names of all the bits, with their

reset values below the bitfield name. The reset val-

ue can also be found in the Word column of the bit-

field summary as indicated by an `*'.

Table 2. MCR Control Register Mapping

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

Mic

TSD

GB

ACC

RVol

TGain

0

0

0

HD

RSD

Taps

NCC

TVol

RGain

0

1

0

NErle

NFNse

RHDet

HDly

NseRmp

RSThd

PCSen

1

0

0

AErle

AFNse

THDet

TSAtt

TSBias

TSThd

HHold

1

1

0

Bit15

Bit14

Bit13

Bit12

Bit11

Bit10

Bit9

Bit8

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

DATA

DRDY

STROBE

1

2

3

4

four extra strobe pulses

Figure 5. Microcontroller Interface

CS6420

12

DS205PP2

Register 0

* Denotes reset value

Table 3. Register 0 Bit Definitions

Mic - Microphone Preamplifier Enable

The microphone preamplifier described in the

Acoustic Interface section is enabled by default, but

may be disabled by setting Mic to 0. Refer to the

Acoustic Interface section for more details on us-

ing/disabling the Microphone Preamplifier.

TSD - Transmit Suppression Disable

The Transmit Supplementary Echo Suppression

function is a non-linear echo control mechanism.

The Transmit Suppression will introduce TSAtt

(see Register 3) dB of attenuation into the transmit

path only when there is speech detected in the re-

ceive path and no near-end speech. When only

near-end speech is present, or if there is no speech

in either direction, the suppression attenuation is

removed. By default, the transmit suppression

function is enabled.

GB - Graded Beta

The room-size adjustment scheme called "graded

beta," provided for the acoustic echo canceller in the

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

Mic

TSD

GB

ACC

RVol

TGain

0

0

0

1

0

10

00

00100

00

0

0

0

Bits

Name

Function

Word

Operation

15

Mic

Microphone Preamplifier Enable

0

1*

disable preamp

enable preamp

14

TSD

Tx Suppression Disable

0*

1

enable Tx suppression

disable Tx suppression

13-12

GB

Graded Beta

00

01

10*

11

0.00 dB/ms

0.75 dB/ms

0.38 dB/ms

0.19 dB/ms

11-10

ACC

AEC Coefficient Control

00*

01

10

11

Normal

Clear

Freeze

reserved

9-5

RVol

Rx Volume Control

00000

00001

---

00100*

---

01010

01011

---

11101

11110

11111

+30 dB

+27 dB

+18 dB

+0 dB

-3 dB

-57 dB

-60 dB

mute

4-3

TGain

Tx Analog Gain

00*

01

10

11

0 dB

6 dB

9.5 dB

12 dB

CS6420

DS205PP2

13

CS6420, is controlled by GB. The network echo

canceller does not support graded beta.

Graded beta is an architectural enhancement to the

CS6420 which takes advantage of the fact that

acoustic echoes tend to decay exponentially with

time. The CS6420 can increase the beta, or update

gain, for the coefficients of the adaptive filter

which occur earlier in time and decrease it for those

that occur later in time, which increases conver-

gence speed while maintaining stability. In order to

make this improvement, there is an implicit assump-

tion that the decay rate of the echo is known. The

graded beta control allows the system designer to ad-

just this. For very acoustically live rooms, use either

no decay (00) or slight decay (11). Cars and acousti-

cally dead rooms can benefit from the most rapid de-

cay (01).

ACC - Acoustic Coefficient Control

The coefficients of the AEC adaptive filters in the

CS6420 are controlled by ACC. The default posi-

tion (00) yields normal operation, which means the

coefficients are free to adjust themselves to the

echo path in order to cancel echo. When set to the

clear position (01), the adaptive filter coefficients

are all held at zero, so the echo canceller is effec-

tively disabled. Note that unless the half-duplex

mode is disabled, this will force the CS6420 into

half-duplex mode. The freeze position (10) causes

the coefficients to hold their current values.

RVol - Receive Volume Control

Volume in the receive path is set by RVol. The vol-

ume control in the receive direction is implemented

by a peak-limiting automatic gain control (AGC)

and digital attenuation at the near-end output DAC.

The AGC is discussed in detail in the Design Con-

siderations section. See the sub-section on AGC

for a full explanation of how it functions.

When the reference level is set to +0 dB, the AGC

is effectively disabled. Volume control is imple-

mented by digital attenuation in 3 dB steps from

this point on down. The maximum gain is +30 dB

and the minimum is -60 dB in 3 dB steps. The low-

est gain setting (11111) mutes the receive path.

The default setting for the receive reference level is

+18 dB.

TGain - Transmit Analog Gain

TGain selects the amount of additional on-chip an-

alog gain to be supplied to the acoustic input of the

CS6420. A programmable gain amplifier (PGA)

exists before each ADC which allows 0 dB, 6 dB,

9.5 dB, or 12 dB of gain to be added to the signal

path. The acoustic side defaults to 0 dB of gain.

Note: Changing the analog gain will change the full-

scale voltage as applied to the input pin. Make

sure that the ADC input does not clip with the gain

stage on.

CS6420

14

DS205PP2

Register 1

* Denotes reset value

Table 4. Register 1 Bit Definitions

HD - Half-Duplex Disable

In normal operation, the CS6420 will be in a half-

duplex mode if the echo canceller is not providing

enough loop gain reduction to prevent howling.

This half-duplex mode would be active at power-

up, for example, before the adaptive filter has had a

chance to adapt. This half-duplex mode prevents

howling and also masks the convergence process.

In some cases, such as when measuring conver-

gence speed (see Testing Issues), the half-duplex

mode is undesirable. By default, the half-duplex

mode is enabled.

RSD - Receive Suppression Disable

The Receive Supplementary Echo Suppression

function is a non-linear echo control mechanism.

Supplementary Echo Suppression attenuates sig-

nals in the receive direction by 24 dB when far-end

speech is absent in the receive path. The attenua-

tion is released only when the receive channel is ac-

tive. It is also designed to not be triggered by

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

HD

RSD

Taps

NCC

TVol

RGain

0

1

0

0

0

10

00

01010

00

0

1

0

Bits

Name

Function

Word

Operation

15

HD

Half-Duplex Disable

0*

1

enable half-duplex

disable half-duplex

14

RSD

Rx Suppression Disable

0*

1

enable Rx suppression

disable Rx suppression

13-12

Taps

AEC/NEC Tap Allocation

00

01

10*

11

444/0 (55.5ms/disabled)

380/128 (47.5ms/16ms)

316/192 (39.5ms/24ms)

252/256 (31.5ms/32ms)

11-10

NCC

NEC Coefficient Control

00*

01

10

11

Normal

Clear

Freeze

reserved

9-5

TVol

Tx Volume Control

00000

00001

---

00100

---

01010*

01011

---

11101

11110

11111

+30 dB

+27 dB

+18 dB

+0 dB

-3 dB

-57 dB

-60 dB

mute

4-3

RGain

Rx Analog Gain

00*

01

10

11

0 dB

6 dB

9.5 dB

12 dB

CS6420

DS205PP2

15

network echo. By default, the receive suppression

function is enabled.

Taps - AEC/NEC Tap Allocation

The CS6420 has a total of 63.5 ms of echo canceller

taps that it can partition for use by the network and

acoustic echo cancellers. By default, the CS6420

allocates 39.5 ms for the AEC and 24 ms for the

NEC. Some applications will never have a network

echo path, and so should allocate all taps for the

AEC. See NErle and NFNse in Register 2, and

AErle and AFNse in Register 3 for more options

when an echo path is nonexistent.

NCC - Network Coefficient Control

The NEC adaptive filter's coefficients are con-

trolled by NCC. See ACC in Register 0 for more

details. The default setting for NCC is Normal

mode.

TVol - Transmit Volume Control

Volume in the transmit path is controlled by TVol.

Like receive volume, the transmit volume is con-

trolled by an AGC. See RVol in Register 0 for more

details. The default setting for the transmit refer-

ence level is +0 dB.

RGain - Receive Analog Gain

RGain selects the amount of additional on-chip an-

alog gain to be supplied to the network input of the

CS6420. A programmable gain amplifier (PGA)

exists before each ADC which allows 0 dB, 6 dB,

9.5 dB, or 12 dB of gain to be added to the signal

path. The network side defaults to 0 dB of gain.

Note: Changing the analog gain will change the full-

scale voltage as applied to the input pin. Make

sure that the ADC input does not clip with the gain

stage on.

CS6420

16

DS205PP2

Register 2

* Denotes reset value

Table 5. Register 2 Bit Definitions

NErle - Network ERLE Threshold

The CS6420 will allow full-duplex operation only

when the Network ERLE exceeds the threshold set

by NErle. See also NFNse. See Glossary for a def-

inition of ERLE.

NFNse - Network Full-Duplex Noise Threshold

NFNse works in conjunction with NErle to deter-

mine when the CS6420 should transition into full-

duplex operation. If the current noise level at the

far-end input is greater than NFNse, then NErle is

used to determine if full-duplex is allowed. If the

noise level is below the level of NFNse, the

CS6420 uses an internal estimate of asymptotic

performance to determine whether or not to transi-

tion to full-duplex. If NFNse is zero, NErle is al-

ways used as the full-duplex criterion. The other

values exist for cases where there is not a network

path to converge to, or the existence of a network

path can not be determined prior to placing a call.

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

NErle

NFNse

RHDet

HDly

NseRmp

RSThd

PCSen

1

0

0

00

00

00

00

00

00

0

1

0

0

Bits

Name

Function

Word

Operation

15-14

NErle

NEC ERLE Threshold

00*

01

10

11

24 dB

18 dB

30 dB

reserved

13-12

NFNse

NEC Full-Duplex Noise Threshold

00*

01

10

11

zero

-42 dB

-54 dB

reserved

11-10

RHDet

Rx Half-Duplex Detection Threshold

00*

01

10

11

5 dB

3 dB

6 dB

reserved

9-8

HDly

Half-Duplex Holdover Delay

00*

01

10

11

200 ms

100 ms

150 ms

reserved

7-6

NseRmp

Background Power Estimator Ramp Rate

00*

01

10

11

1 s

0.5 s

2 s

reserved

5-4

RSThd

Rx Suppression Threshold

00*

01

10

11

5 dB

3 dB

6 dB

reserved

3

PCSen

Path Change Sensitivity

0*

1

high sensitivity

low sensitivity

CS6420

DS205PP2

17

RHDet - Receive Half-Duplex Detection

Threshold

The sensitivity of the speech detector controls

channel switching and ownership in half-duplex

mode. The receive speech detector registers speech

if the receive channel signal power is RHDet above

the noise floor for the receive channel.

HDly - Half-Duplex Holdover Delay

After a channel goes idle in the half-duplex mode

of operation, a change of channel ownership is in-

hibited for HDly in order to prevent false switching

due to echoes. The half-duplex will be more im-

mune to false switching if this delay is longer, but

it will also prevent a fast response to legitimate

channel changes.

NseRmp - Background Noise Power Estimator

Ramp Rate

The background noise power estimators increase at

a rate of 3 dB/NseRmp until the background noise

power estimate equals the current input power esti-

mate. The background noise power estimators

quickly track drops in the current input power esti-

mate. Choose small values of NseRmp if the envi-

ronment is expected to have rapidly varying noise

levels. Choose large values of NseRmp if the envi-

ronment is expected to have relatively constant

noise power.

RSThd - Receive Suppression Threshold

This parameter sets the threshold for far-end

speech detection for disengaging receive suppres-

sion. The speech detector that disengages the re-

ceive suppression has its sensitivity controlled by

RSThd. The suppression is inserted into the receive

path unless signal from the far-end exceeds the re-

ceive channel noise power by RSThd, in which

case speech is assumed to be detected and the sup-

pression is defeated until speech is no longer de-

tected. Decreasing RSThd to make the speech

detector more sensitive could result in false detec-

tions due to spurious noise events which may cause

an unpleasant noise modulation at the near-end. In-

creasing RSThd to make it robust to spurious noise,

but may cause weak far-end talkers to not be heard.

RSThd does not affect the ability of the receive

suppressor to attenuate residual network echo.

PCSen- Path Change Sensitivity

The Acoustic Interface is likely to have many path

changes, for example, as people move about in the

room where the full-duplex speakerphone is being

used. The sensitivity of the path change detector

can be changed with the PCSen Bit. Set PCSen to 0

for high sensitivity and 1 for low sensitivity.

If PCSen is set to high, extended doubletalk may

cause the CS6420 to briefly drop into half-duplex.

When PCSen is set to low, brief echo may be heard

during path changes.

CS6420

18

DS205PP2

Register 3

* Denotes reset value

Table 6. Register 3 Bit Definitions

AErle - Acoustic ERLE Threshold

The CS6420 will allow full-duplex operation only

when the Acoustic ERLE it provides exceeds AEr-

le. See also AFNse. See Glossary for a definition

of ERLE.

AFNse - Acoustic Full-Duplex Noise Threshold

AFNse works in conjunction with AErle to deter-

mine when the CS6420 should transition into full-

duplex operation. If the current noise level at the

near-end input is greater than AFNse, then AErle is

used to determine if full-duplex is allowed. If the

noise level is below the level of AFNse, the

CS6420 uses an internal estimate of asymptotic

performance to determine whether or not to transi-

tion to full-duplex. If AFNse is zero, AErle is al-

ways used as the full-duplex criterion. The other

values exist for cases where there may not be an

acoustic path to converge to.

THDet - Transmit Half-Duplex Detection

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

AErle

AFNse

THDet

TSAtt

TSBias

TSThd

HHold

1

1

0

00

00

00

00

00

00

0

1

1

0

Bits

Name

Function

Word

Operation

15-14

AErle

AEC ERLE Threshold

00*

01

10

11

24 dB

18 dB

30 dB

reserved

13-12

AFNse

AEC Full-Duplex Noise Threshold

00*

01

10

11

zero

-42 dB

-54 dB

reserved

11-10

THDet

Tx Half-Duplex Detection Threshold

00*

01

10

11

5 dB

3 dB

6 dB

reserved

9-8

TSAtt

Tx Suppression Attenuation

00*

01

10

11

18 dB

12 dB

24 dB

reserved

7-6

TSBias

Tx Suppression Bias

00*

01

10

11

18 dB

15 dB

21 dB

reserved

5-4

TSThd

Tx Suppression Threshold

00*

01

10

11

15 dB

12 dB

9 dB

reserved

3

HHold

Hold in Half-Duplex on Howl

0*

1

disable

enable

CS6420

DS205PP2

19

Threshold

The sensitivity of the speech detector controls

channel switching and ownership in half-duplex

mode. The transmit speech detector registers

speech if the transmit channel signal power is TH-

Det above the noise floor of the transmit channel.

TSAtt - Transmit Suppression Attenuation

This parameter sets the amount of suppression at-

tenuation inserted into the transmit path when

transmit suppression is engaged.

TSBias - Transmit Suppression Bias

The bias level affects the ease with which near-end

speech may break-in or be crushed by far-end

speech. See the Design Considerations section on

Transmit Suppression for full details.

TSThd - Transmit Suppression Threshold

This parameter sets the ERLE requirement for dis-

crimination between echo and near-end speech by

the supplementary echo suppressor. See the De-

sign Considerations section on Transmit Suppres-

sion for full details.

HHold - Hold in Half-Duplex on Howl

This is a control flag which, if enabled, holds the

system in the half-duplex operation if it were to

howl for any reason and the howl detectors trip and

clear coefficients. The system may transition to

full-duplex if the flag is subsequently cleared.

Reset

A hardware reset, achieved by bringing RST low

for at least 1 µs and then high again, must be ap-

plied after initial power-on.

When RST is held low, the various internal blocks

of the CS6420 are powered down. When RST is

brought high, the oscillator is enabled and approx-

imately 4 ms later, all digital clocks begin operat-

ing. The ADCs and DACs are calibrated and all

internal digital initializations occur. The MCR is

sampled after the reset timer expires (104 ms after

the rise of RST or sooner if using the early exit de-

scribed below) to determine whether the reset was

warm or cold. After the MCR is initially sampled,

the default (reset) values of the MCR are restored

to it.

Cold reset is a total reset of all the components of

the CS6420. The ADCs and DACs are reset, the

echo canceller memories and registers are all

cleared, and the default settings of the MCR are re-

stored. Cold reset is the default reset mode upon

power up or in the absence of a microcontroller.

Warm reset is like cold reset except that the echo

canceller coefficients and certain key variables are

not cleared, but instead keep their pre-reset value.

This gives the CS6420 a headstart in adapting to its

environment if the echo environment is relatively

stable, assuming a cold reset happened at least once

since power up.

The CS6420 is warm reset by raising the RST pin

high, waiting 4 ms for the digital clocks to start, and

then writing 0111111111111110 (0x7FFE) to the

MCR within 104 ms after RST goes high. If no

control word is sent, the CS6420 will cold reset. If

the control word is sent after the timer has expired,

it is interpreted as a normal control word.

Another special reset option is to exit the 100 ms

reset timer before the 100 ms has elapsed. This is

accomplished by writing a control word to the

MCR with Bit 15 set high. To exit the timer early

in cold reset, write 1000000000000 (0x8000). The

timer may be bypassed and warm reset asserted by

sending 1111111111111110 (0xFFFE). The

100 ms timer prevents operation until the bias volt-

ages generated on-chip settle, but the startup delay

might be objectionable in some applications.

Clocking

The clock for the converters and DSP is provided

via the clocking pins, CLKI (pin 14) and CLKO

(pin 13). A 20.480 MHz parallel resonant crystal

CS6420

20

DS205PP2

placed between these two pins and loaded with

22 pF capacitors will allow the on-chip oscillator to

provide this system clock. Alternatively, the CLKI

pin may be driven by a CMOS level clock signal.

The clock may vary from 20.480 MHz by up to

10%, however, this will change the sampling rate

of the converters and echo canceller, which will af-

fect the bandwidth of the analog signals and the du-

ration of echo that the echo canceller can

accommodate. CLKO is not connected when CLKI

is driven by the CMOS signal.

Power Supply

The pins AVDD (pin 1) and AGND (pin 2) power

the analog sections of the CS6420, and DVDD (pin

16) and DGND (pin 15) power the digital sections.

This distinction is important because internal to the

part, the digital power supply is likely to contain

high-frequency energy. The analog power supply is

kept clean internally by drawing current from a dif-

ferent pin, thereby achieving high performance in

the converters.

The digital supply of the CS6420 should not be

connected to the system digital supply, if there is

one, as the CS6420 has internal timing mechanisms

designed to minimize the detrimental effects of its

own digital noise, but cannot use these to compen-

sate for externally introduced digital noise. The

CS6420 digital power supply should be derived

from its analog power supply through a ferrite bead

with low (< 1

) DC impedance.

Power Down Mode

Typical power consumption of the CS6420 is 60

mA, assuming normal operating conditions. This

current consumption can be further reduced by in-

voking the powerdown mode, which is entered by

holding RST low. Holding RST low will power

down all the internal blocks of the CS6420 and stop

the oscillator. In powerdown mode, current con-

sumption drops to less than 1 mA.

AGND

DVDD

MB

AVDD

+5V

Analog

Supply

DGND

From

Ferrite

Bead

Figure 6. Suggested Layout

CS6420

DS205PP2

21

Noise and Grounding

Since the CS6420 is a mixed-signal integrated cir-

cuit, the system designer must pay special attention

to layout and decoupling to minimize noise con-

cerns. The three best methods to reduce noise when

using the CS6420 are to have good decoupling of

power supplies, separation of analog and digital

power and ground, and careful board layout.

Figure 6 shows the suggested placement of decou-

pling capacitors for the power supplies. Note that

the trace length from the power pin to the capaci-

tors is minimized. Also note that the smaller valued

capacitor is placed closer to the pin than the larger

valued capacitor. The smaller capacitor decouples

high frequency noise and the larger capacitor atten-

uates lower frequencies.

The separation of analog and digital power and

ground is done in two ways. The power is separated

by deriving the digital power for the CS6420 from

the analog through a ferrite bead to isolate analog

from digital, as shown in Figure 7. The ferrite bead

serves as a low-pass filter to remove CS6420 digi-

tal switching noise from the analog power supply.

The ground is separated by isolating all the digital

components of the system board on one ground

plane and all the analog and linear components on

a different ground plane. The CS6420 should be

placed over the analog ground plane. This prevents

digital switching noise from the digital components

of the board from coupling into the converters and

aliasing into the passband.

+5V

(Analog)

AVDD

AGND

DVDD

DGND

Analog Ground Plane

Digital Ground Plane

Microcontroller

1

µ

F

0.1

µ

F

0.1

µ

F

1

µ

F

Ferrite Bead

Figure 7. Ground Planes

CS6420

22

DS205PP2

DESIGN CONSIDERATIONS

When designing the CS6420 into a system, it is im-

portant to keep several considerations in mind.

These concerns can be loosely grouped into three

categories: algorithmic considerations, circuit de-

sign considerations, and system design consider-

ations.

Algorithmic Considerations

The CS6420 facilitates full-duplex hands-free

communication via many algorithms running on

the Digital Signal Processor that is the core of the

CS6420. Among these are the algorithms that per-

form the adaptive filtering, the half-duplex switch-

ing, digital volume control, and supplementary

echo suppression.

Full-Duplex Mode

Full-duplex hands-free communication is achieved

through a technique called adaptive filtering. The

basic principle behind adaptive filtering is that the

acoustic path between speaker and microphone can

be modeled by a transfer function which can be dy-

namically determined by an adaptive digital filter.

This principle assumes good update control and

speech/tone detection algorithms to prevent the fil-

ter from mistraining.

Theory of Operation

Figure 8 illustrates how the adaptive filter can can-

cel echo and reduce loop gain. The echo path of the

system is between points B and C: the speaker to

microphone coupling. A signal injected at A

(sometimes called a "training signal") is sent both

to B, the input of the echo path, and to F, the input

of the adaptive filter. The signal at B is modified by

the transducers and the environment, and received

at point C (an "Echo"). Meanwhile, let us assume

for argument's sake that the adaptive filter has ex-

actly the right transfer function to match the echo

path BC, and so the signal at point D is approxi-

mately equal to the signal at point C. After these are

subtracted by the summing element, all that is left

is the error signal at point E, which should be very

small.

If a person were to speak into the microphone at

point C, that signal would pass through the sum-

ming element unchanged because the adaptive fil-

ter had no comparable input to subtract out. In this

manner, the person at A and the person at C may si-

multaneously speak and A will not hear his own

echo.

In the real world, the echo path is not static. It will

change, for example, when people move in the

room, when someone moves the speaker or the mi-

crophone, or when someone drops a piece of paper

on top of the speaker. So, the filter needs to adapt

to modify its transfer function to match that of the

environment. It does so by measuring the error sig-

nal at point E and trying to minimize it. This signal

is fed back to the adaptive filter to measure perfor-

mance and how best to adapt, or train.

The trouble arises when the person at the near-end

(C) speaks: the error signal will be non-zero, but

the adaptive filter should not change. If it tries to

train to the near-end signal, the adaptive filter has

no way to reduce the error signal, because there is

no input to the filter, and therefore no output from

it. The adaptive filter would mistrain.

To prevent this mistraining, the echo canceller uses

double-talk detection algorithms to determine

when to update. These update control algorithms

Adaptive Filter

A

E

D

B

C

+

-

F

Figure 8. Simplified Acoustic Echo Canceller

Block Diagram

CS6420

DS205PP2

23

are the heart of most echo canceller implementa-

tions.

The worst case situation for the CS6420 is when

parties at both ends are speaking and the person at

the near-end is moving. In this case, the echo can-

celler will cease to adapt because of the double-

talk, but the echo will not be optimally reduced be-

cause of the change in path.

Adaptive Filter

The adaptive filter in the CS6420 uses an algorithm

called the "Normalized Least-Mean-Square

(NLMS)" update algorithm to learn the echo path

transfer function. This Finite Impulse Response

(FIR) filter has 508 taps, which can model up to

63.5ms of total path response at a sampling rate of

8kHz. The coverage time is calculated by the fol-

lowing formula:

x

508 = 63.5 ms.

The CS6420's adaptive filter, like all FIR filters,

only models Linear and Time Invariant (LTI) sys-

tems. So, any non-linearity in the echo path can not

be modeled by the adaptive filter and the resulting

signals will not be cancelled. Signal clipping and

poor-quality speakers are very common sources of

non-linearity and distortion.

A common integration problem for echo cancellers

is signal clipping in the echo path. For example, if

a speaker driver is driven to its rails, the distortion

of the speech may be hard to perceive, but it is very

bad for the echo canceller. This technique has been

used in half-duplex phones to provide good low-

level signal gain at the expense of distortion with

high amplitude signals. Since this does not work

for the CS6420, an AGC mechanism has been in-

troduced to provide equivalent behavior without

clipping. See the section on AGC for more details.

Another common problem is speaker quality. A

poor quality speaker which is perfectly acceptable

for a half-duplex speakerphone, may limit the echo

canceller's performance in a full-duplex speaker-

phone. The distortion elements will not be modeled

by the adaptive filter and so limit its effectiveness.

Speakers should have better than 2% THD perfor-

mance to not impede the adaptive filter.

Volume control should be implemented only using

the CS6420 Microcontroller Interface. A real-time

external change in the gain of the speaker driver,

for example, would result in a change in the trans-

fer function of the echo path, and so would force

the adaptive filter to readapt. If the volume control

is done before the input to the adaptive filter, the

echo path does not change, and no retraining is nec-

essary. Another side benefit of the CS6420 volume

control is that it transparently provides dynamic

range compression.

Pre-Emphasis

The typical training signal for the adaptive filter

will be speech, but most adaptive filters work opti-

mally with white noise. Speech has very different

spectral characteristics than white noise because of

its quasi-periodic nature.

Research at Crystal has shown that quasi-periodic

signals cause the formation of spurious non-zero

coefficients within the adaptive filter at tap inter-

vals determined by the periodicity of the signal.

This results in small changes in period being very

destructive to the adaptive filter's performance.

One mechanism the CS6420 uses to prevent this

filter corruption with speech is to pre-emphasize

the signal sent to the adaptive filter so that much of

the low frequency content is removed.

The CS6420 works very well with a speech training

signal because of the pre-emphasis filter. White

noise training signals, however, will result in sub-

optimal performance, so when testing, white noise

is not recommended as a training signal.

Graded Beta

The update gain of an adaptive filter, sometimes

called the "beta", is the rate at which the filter co-

1

8kHz

-------------

CS6420

24

DS205PP2

efficients can change. If beta is too low, the adap-

tive filter will be slow to adapt. Conversely, if it is

too high, the filter will be unstable and will create

unwanted noise in the system.

In most echo canceller implementations, the beta is

a fixed value for all the filter coefficients. In some

situations, though, through knowledge of the char-

acteristics of echo path response, the beta can be

varied for groups of coefficients. This preserves

stability by allowing the beta to be higher for some

coefficients and compensating by reducing beta be-

low nominal for others.

For example, acoustic echo tends to decay expo-

nentially, so the first taps need to be large and the

later taps will be small. Having a large beta for the

first taps will allow those taps to be adapted faster,

while having a small beta for the later taps will

keep the filter stable. This has an added benefit of

suppressing the spurious taps mentioned in the Pre-

Emphasis Filter section above.

The Microcontroller Interface allows four settings

for graded beta: none, 0.19 dB/ms, 0.38 dB/ms, and

0.75 dB/ms. Use 0.75 dB/ms for acoustically dead

rooms or cars, and 0.19 dB/ms or no grading of beta

for large, or acoustically live rooms.

Update Control

As mentioned in the Theory of Operation section,

the update control algorithms are the heart of any

useful echo canceller implementation. Aside from

telling the adaptive filter when to adapt, they are re-

sponsible for correcting performance when the path

changes too quickly for the filter. For example, if

the adaptive filter is actually adding signal power

instead of cancelling, the update control algorithms

will reset the adaptive filter to cleared coefficients,

forcing it to restart.

Speech Detection

The CS6420 detects speech by using power estima-

tors to track deviations from a background noise

power level. The power estimators filter and aver-

age the raw incoming samples from the ADC.

A background noise level is established by a regis-

ter that increases 3 dB at intervals determined by

NseRmp (Register 2, bits 7 and 6). When the power

estimator level rises, the background noise level

will slowly increase to try to match it. When the

power estimator level is below the background

noise level, the background noise level is quickly

reset to match the power estimator level. This

method allows significant flexibility in tracking the

background noise level.

Speech is detected when the power estimator level

rises above the background noise level by a given

threshold. The half-duplex receive speech detector

threshold is set by RHDet (Register 2, bits 11 and

10), the half-duplex transmit speech detector

threshold is set by THDet (Register 3, bits 11 and

10), and the receive suppression speech detector

threshold is set by RSThd (Register 2, bits 5 and 4).

The transmit speech detectors for both half-duplex

and suppression default to 5 dB.

Note that constant power signals which persist for

long durations, such as tones from a signal genera-

tor, will be detected as speech only as long as the

background noise level has not risen to within the

speech detection threshold of the signal power.

When a tone has persisted for long enough, the

background noise level will be equal to the power

estimator level, and so the tone will no longer be

considered speech. This duration is dependent

upon the power difference between the signal and

the ambient noise power, as well as NseRmp. It

should be noted that the CS6420 has a tone detector

to prevent updates when tones are present and allow

tones to persist regardless of the speech detectors.

Half-Duplex Mode

In cases where the system relies on the echo cancel-

ler for stability, a fail-safe mechanism must be in

place for instances when the echo canceller is not

CS6420

DS205PP2

25

performing adequately. The CS6420 implements a

half-duplex mode to guarantee communication

even when the echo canceller is disabled.

When the CS6420 is first powered on, or emerges

from a reset, the echo canceller coefficients are

cleared, and the echo cancellers provide no benefit

at this point. The half-duplex mode is on to prevent

howling and echo from interfering with communi-

cation. Once the CS6420's adaptive filters have

adapted sufficiently, the half-duplex mode is auto-

matically disabled, and full-duplex communication

can occur.

The half-duplex mode allows three states: transmit,

receive, and idle. In the transmit state, the transmit

channel is open and the receive channel is muted.

The receive state mutes the transmit channel. The

idle state is an internal state which is used to en-

hance switching decision making. The CS6420

must be idle before it will allow a state change be-

tween transmit and receive.

The half-duplex controller can be susceptible to

echo, so a holdover timer is provided to help pre-

vent false switching. Holdover will force the chan-

nel to remain in its current state for a fixed duration

after speech has stopped. HDly (Register 2, bits 9

and 8) sets the duration of the holdover. Longer

holdover will tend to make interrupting much hard-

er, but will be much more robust to spurious

switching caused by echo.

AGC

The CS6420 implements a peak-limiting AGC in

both the transmit and receive directions in order to

boost low-level signals without compromising per-

formance when high amplitude signals are present.

The technique effectively results in dynamic range

compression.

The AGC works by setting a reference level based

on the value represented by TVol (Register 1, bits

9-5) for the transmit direction and RVol (Register

0, bits 9-5) for the receive direction. If the signal

from the input is above this reference, it is attenu-

ated to the reference level with an attack time of

125

µ

s. This attenuation level decays with a time

constant of 30 ms unless another signal greater than

the reference level is detected. After the attenua-

tion, a post-scaler scales the reference level to full-

scale (the maximum digital code), which amplifies

all signals by the difference between the reference

level and full-scale.

For example, Figure 9 shows how the AGC works

with a reference level of +30 dB (Word = 00000).

Any signal greater than 30 dB below full-scale (a),

is scaled down to 30 dB (b). This signal is then

scaled up +30 dB (the reference level) to provide

the final output (c). Note that the combination of at-

tenuation and gain results in less than +30 dB total

gain being applied. If the input signal is below 30

dB below full-scale (d), no attenuation is done and

the full +30 dB of gain is applied to the signal (e).

When the reference level is set to +0 dB, the AGC

is effectively disabled. Volume control is imple-

mented by digital attenuation in 3 dB steps from

this point on down. The maximum gain is +30 dB

and the minimum is -60 dB in 3 dB steps. The low-

est gain setting (11111) mutes the path. The signal

scaling takes place in between the two cancellers,

and so does not disturb the echo canceller as chang-

ing gain in the echo path would (see the Adaptive

Filter section for more details).

Suppression

Echo cancellation is somewhat of a misnomer in

that echo is merely attenuated, not entirely can-

celled. Some residual echo still exists after the

summing node. This residual echo, though very

low, may be audible when the near-end talker is not

speaking. Suppression further attenuates the ech-

oed signal.

The CS6420 employs supplementary echo suppres-

sion which adds attenuation on top of the cancella-

tion to remove the residual echo. For example, the

CS6420

26

DS205PP2

transmit channel will engage extra attenuation

whenever only the far-end talker is speaking. How-

ever, if the near-end talker starts speaking, the at-

tenuation is removed and the system relies on the

near-end talker's speech to mask residual echo.

Suppression causes some modulation of the per-

ceived background noise which may be distracting

to some users. As a result, it may be desirable to

limit the suppression attenuation to the minimum

necessary. The CS6420 provides TSAtt (Register

3, bits 9 and 8) to control the amount of attenuation

introduced by suppression in the transmit channel.

Receive suppression attenuates by 24 dB.

The suppression in the transmit suppression and

that in the receive direction work very differently.

The transmit suppression works in a "default off"

mode while the receive suppression is "default on."

Transmit Suppression

The transmit suppressor attenuates the transmit

path when only far-end speech is present, hence the

name "default off." This ensures that the suppres-

sion engages only when necessary.

Recall that the purpose of Transmit Suppression is

to mask residual echo by inserting additional

loss/attenuation in the transmit path in the scenario

when only far-end speech is present; the residual

echo, if any, in double-talk being masked by near-

end speech assuming reasonable levels of ERLE.

There are two controls/tweekable parameters for

governing the behavior of Transmit Suppression.

The two controls are adjustable through the Micro-

controller Interface, and they are TSThd (Register

3, bits 5 and 4) and TSBias (Register 3, bits 7 and

6). TSThd is the primary control and should be ad-

justed before changing the value of TSBias from its

default setting. TSThd sets the ERLE expectation

to be used in discriminating between near-end

speech and far-end echo. This control setting will

by far predominate in affecting the manner in

which Transmit Suppression behaves.

TSBias is a secondary control. This is to be adjust-

ed after the system designer is more or less satisfied

with the behavior of Transmit Suppression with the

TSThd set. It affects the ease with which a near-end

talker may disengage Transmit Suppression and

-30dB

Fs

(a) Input Signal

t

-30dB

Fs

(c) AGC Gain

t

-30dB