CS22250 Wireless 10BT Controller

1 of 32

DS551PP2

Rev. 3.0

www.cirrus.com

1

Introduction

The Cirrus Logic CS22250 Wireless Network Controller enables high speed, 11 Mbps digital

wireless data connectivity for wireless Ethernet bridge, access points, and other broadband

applications.

The CS22250 is a highly integrated single-chip Ethernet bridge solution for wireless networks

supporting video, audio, voice, and data traffic. The programmable controller executes Cirrus

Logic's WhitecapTM2 networking protocol that provides Wi-FiTM (802.11b) compliance, multimedia

and a foundation for quality of service (QoS) applications, and Ethernet to wireless bridging. The

device includes several high performance components including an ARM7TDMI RISC processor

core, a Forward Error Correction (FEC) codec, and a wireless radio MAC supporting up to 11

Mbps throughput. The CS22250 utilizes state of the art 0.18um CMOS process and is housed in

a 208 FPBGA compact package, offering low-lead inductance suitable for highly integrated radio

applications. The core is powered at 1.8 V with 3.3V I/O to reduce overall power consumption. In

addition, the CS22250 supports various power management modes for host, MAC, baseband,

and radio interfaces.

The CS22250 is designed to provide integrated low cost IEEE 802.3 standard compliant system

solutions. The controller also incorporates a high-speed parallel interface, which can be used to

interface with other ASICs (eg: HNPA 2.0 Network controller) to implement a variety of other

wireless LAN bridging products.

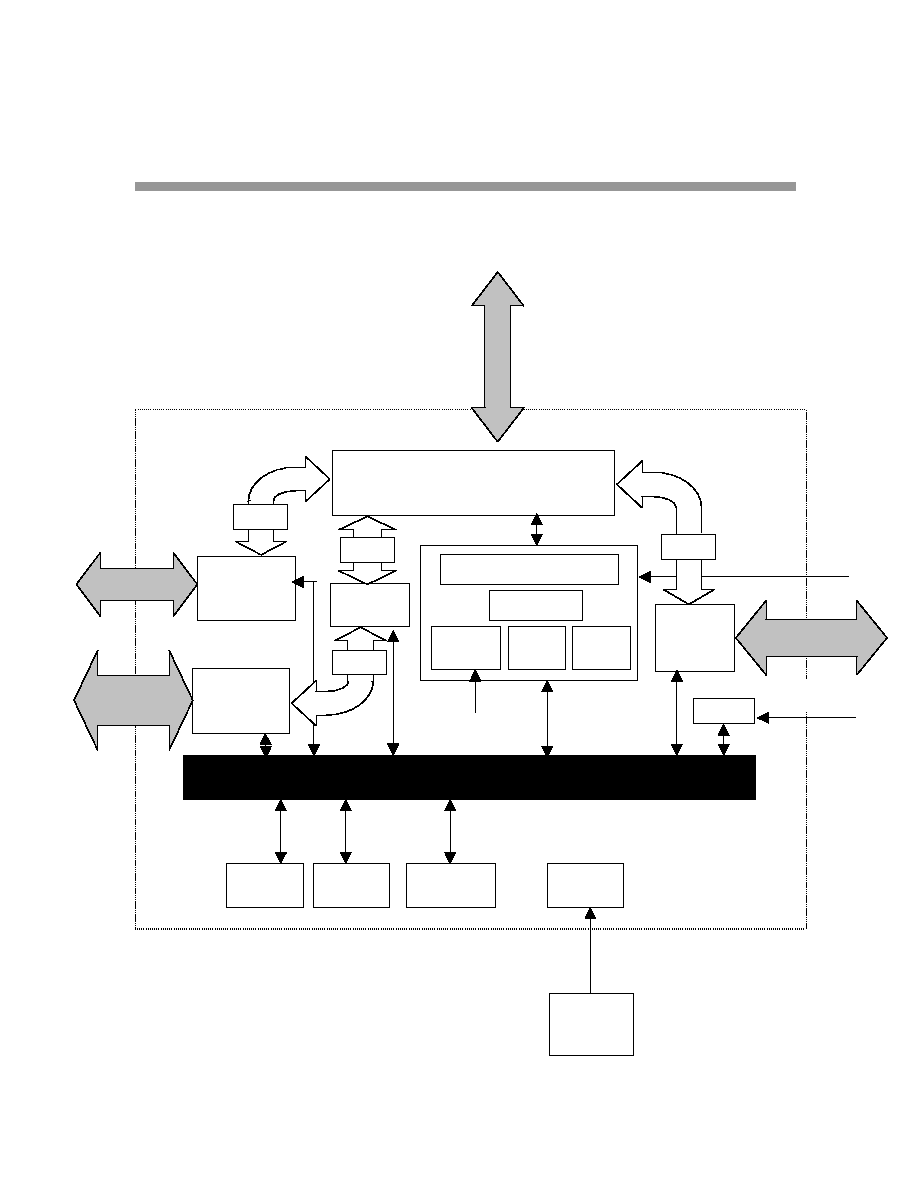

Figure 1. Example System Block Diagram

2.4 GHz Direct Sequence

Spread Spectrum

11 Mbps Wireless

Baseband I/F

CS22250

Wireless 10BT

Controller

802.11b compatible

2.4 GHz

Digital Radio

PHY Transceiver

System Memory

SDRAM (Up to 4MB)

SRAM (Up to 256KB)

Boot ROM/Flash

(Up to 1MB)

High Speed Parallel Interface

AUI Serial Interface

CS22250 Data Sheet

Wireless 10BT Controller

Configuration Interface (USB)

10 BaseT

Ethernet PHY

CS22250 Wireless 10BT Controller

2 of 32

DS551PP2

Rev. 3.0

www.cirrus.com

2

Features

Embedded ARM Core and System Support Logic

� High Performance ARM7TDMI RISC processor core up to 77MHz

� 4KB integrated, one-way set associative, unified, write through cache

� Individual interrupt for each functional block

� Two 23-bit programmable (periodic or one-shot) general purpose timers

� 8 Dword (32-bits) memory write and read buffers for high system performance

� Abort cycle detection and reporting for debugging

� ARM performance monitoring function for system fine-tuning

� Programmable performance improvement logic based on system configuration.

Enhanced Memory Controller Unit

� Programmable memory controller unit supporting SDRAM /async SRAM/boot ROM/Flash

interface

� 16-bit data bus with 12-bit address supporting up to 4MB and up to 103 MHz (100/133MHz

SDRAM)

� 8-bit data bus with addressing support up to 1MB of boot ROM/Flash

� Programmable SDRAM timing and size parameters, such as CAS latencies and number of

banks, columns and rows

� Flexible independent DMA engines for Ethernet MAC, Digital Radio and External Bus

functional units

FEC codec

� High performance Reed-Solomon coding for error correction (255:239 block coding)

� Reduces error probability of a typical 10e-3 error rate environment to 10e-9

� Programmable rate FEC engine to optimize channel efficiency

� Low latency, fully pipelined hardware encoding and decoding. Supports byte-wise single

cycle throughput up to 77MHz, with a sustain rate of 77MBps

� Double buffering (63 Dword read/write buffer) to enhance system performance

Digital Wireless Radio MAC

� Glue-less interface to 802.11b radio baseband transceiver

� 11Mbps data rate

� 32 Dword transmit/receive FIFO

� Supports clear channel assessment (CCA)

Ethernet Interface

� IEEE802.3 Ethernet MAC controller

� Two independent full-duplex DMA channels transfer between Ethernet interface to system

memory

� Standard 7-pin serial interfaces to AUI or Twisted Pair 10-BaseT

� Standard half-duplex CSMA/CD and full-duplex operation

USB Device Configuration Interface

� USB 1.1 compliant

CS22250 Wireless 10BT Controller

3 of 32

DS551PP2

Rev. 3.0

www.cirrus.com

2

Features and Benefits

Power Management

� ACPI compliant

� Programmable sleep timer for ARM core and system power management

� Independent power management control for individual functional blocks

� Supports variable rate radio transmit, receive and standby radio power modes

Clock and PLL Interface

� Single 44MHz crystal oscillator reference clock

� Internal PLL to generate internal and on board clocks

Chip Processing and Packaging

� 208 FPBGA package and 0.18um state of the art CMOS process

� 1.8 V core for low power consumption. 3.3V I/O

High Speed Parallel Interface

� Multi-purpose 32bit bus for connecting with other high speed devices

� Supports operations at � the speed of the ARM clock (up to 38MHz)

� Two independent full-duplex DMA channels transfer between external devices to ARM

system memory

� Supports one external interrupt pin to the ARM core

CS22250 Wireless 10BT Controller

4 of 32

DS551PP2

Rev. 3.0

www.cirrus.com

IMPORTANT NOTICE

"Preliminary" product information describes products that are in production, but for which full characterization data is not

yet available. "Advance" product information describes products that are in development and subject to development

changes. Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is

accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without

warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to

verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the

terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent

infringement, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use

of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third

parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or

implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights.

Cirrus owns the copyrights of the information contained herein and gives consent for copies to be made of the information

only for use within your organization with respect to Cirrus integrated circuits or other parts of Cirrus. This consent does

not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating

any work for resale.

An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products

or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be

exported or taken out of Japan. An export license and/or quota needs to be obtained from the competent authorities of

the Chinese Government if any of the products or technologies described in this material is subject to the PRC Foreign

Trade Law and is to be exported or taken out of the PRC.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH,

PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS").

CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-

SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN

SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product

names in this document may be trademarks or service marks of their respective owners.

Use of this product in any manner that complies with the MPEG-2 video standard as defined in ISO documents IS 13818-

1 (including annexes C, D, F, J, and K), IS 13818-2 (including annexes A, B, C, and D, but excluding scalable extensions),

and IS 13818-4 (only as it is needed to clarify IS 13818-2) is expressly prohibited without a license under applicable

patents in the MPEG-2 patent portfolio, which license is available from MPEG LA, L.L.C. 250 Steele Street, Suite 300,

Denver, Colorado 80296.

CS22250 Wireless 10BT Controller

5 of 32

DS551PP2

Rev. 3.0

www.cirrus.com

3

Functional Description

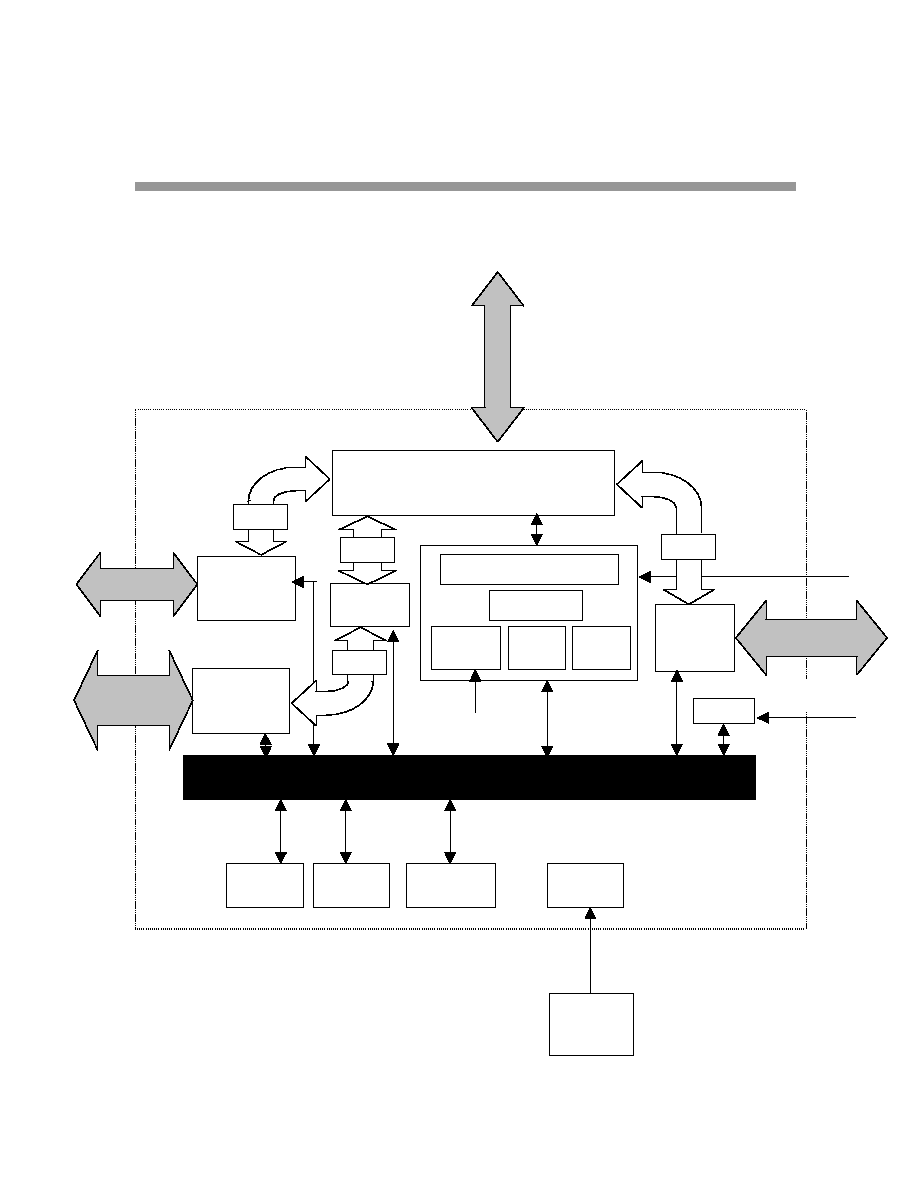

Figure 2. Block Diagram of Major Functional Units

JTAG/Test Interface

Digital Radio

Interface

Memory/Boot ROM

Controller

Arbiter

ARM 7TDMI

Radio MAC

w /DMA Ctrl

FEC codec

S

y

stem

Me

mo

r

y

7 pin Serial

Interface

Config.

Registers

Clock/PLL

Ethernet

MAC

w/ DMA

Controller

Crystal or

Oscillator

4KB

Cache

Timer

(2)

Interrupt

controller

Sleep

Timer

77MHz System Control Bus

Read/Write Buffer

DMA

Controller

Parallel

Interface

Controller

High Speed

Parallel

Interface

DMA

DMA

DMA

USB

USB Device

Configuration Interface

DMA