Copyright 2002 Cirrus Logic (All Rights Reserved)

OCT '02

DS581PP2

1

http://www.cirrus.com

New Highly-Integrated Processor

for Tomorrow's DVD Players

and DVD Receivers

(cont.)

CS98200 Data Sheet

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

FEATURES

s DVD-Video, VCD, VCD 2.0, SVCD, CD, and other

popular standards

s DVD-Audio including CPPM and Verance

TM

watermark protection

s MPEG-1, MPEG-2, and leading edge MPEG-4 audio

and video decoding

s Kodak Picture CD

s Flexible ATAPI or AV bus DVD loader support with

no additional logic

s Dual 32-bit RISC processors, supported by RTOS,

C/C++ compilers, and source level debuggers

s 32-bit DSP capable of running AC-3, MPEG, DTS,

MP3, WMA, and AAC audio decode algorithms

s High quality integrated video encoder with six 10-bit

video D/A converters

s Component (RGB or YUV) or composite & S-Video

output

s Interlaced (PAL/NTSC) or progressive (480p) output,

with Macrovision

TM

copy protection

s CCIR656 video I/O for video capture, PVR and DVR

type applications, picture-in-picture support

s IEC60958/937 (S/PDIF) & simultaneous PCM output

s 5.1 downmix, karaoke echo mix, pitch shift, and many

other effects

s PAL / NTSC transcoding

s Dual 16550 compatible UARTs

s ATAPI/ IDE interface for hard disk, audio server, and

Personal Video Recorder (PVR) applications

s 240-pin MQFP package

ORDERING INFORMATION:

CS98200-CM

See ordering information legend on

page 60

.

OVERVIEW

CS98200 is a highly-integrated processor that provides all

of the audio and video processing functions needed for

the next generation of feature-rich DVD players, DVD

receivers and Internet DVD applications. Tomorrow's

features available today in a single chip solution are

DVD-Audio, MP3, WMA

�

, MPEG-2/4: AAC, Kodak

Picture CD

TM

, Dolby Digital

TM

, Dolby ProLogic II

TM

, and

DTS Digital Surround

TM

decoding. It supports most

popular CD formats, DVD navigation, disk control,

video decoding and up to eight channels of audio output.

An extension of Cirrus' CS98000 DVD product line, the

CS98200 integrates six 10-bit video digital-to-analog

converters (DACs) and TV encoding with progressive

scan functionality. Progressive scan video provides high

resolution and eliminates the "flickering" effect present in

traditional video playback. Other features enabled by

this integrated chip include karaoke functionality and

video special effects. Its extended feature set makes it

ideal for your next innovative DVD application ... today.

Need to get your product to market quickly? Cirrus'

Total Entertainment platform solutions include DVD

front-end controllers, MPEG encoders, audio DSPs, and

digital power amplifiers ... everything you need to

launch your product before the competition. CS98200 is a

Cirrus Total Entertainment Total-E

TM

IC solution

specifically designed for consumer entertainment

electronics.

2

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

OVERVIEW

(cont.)

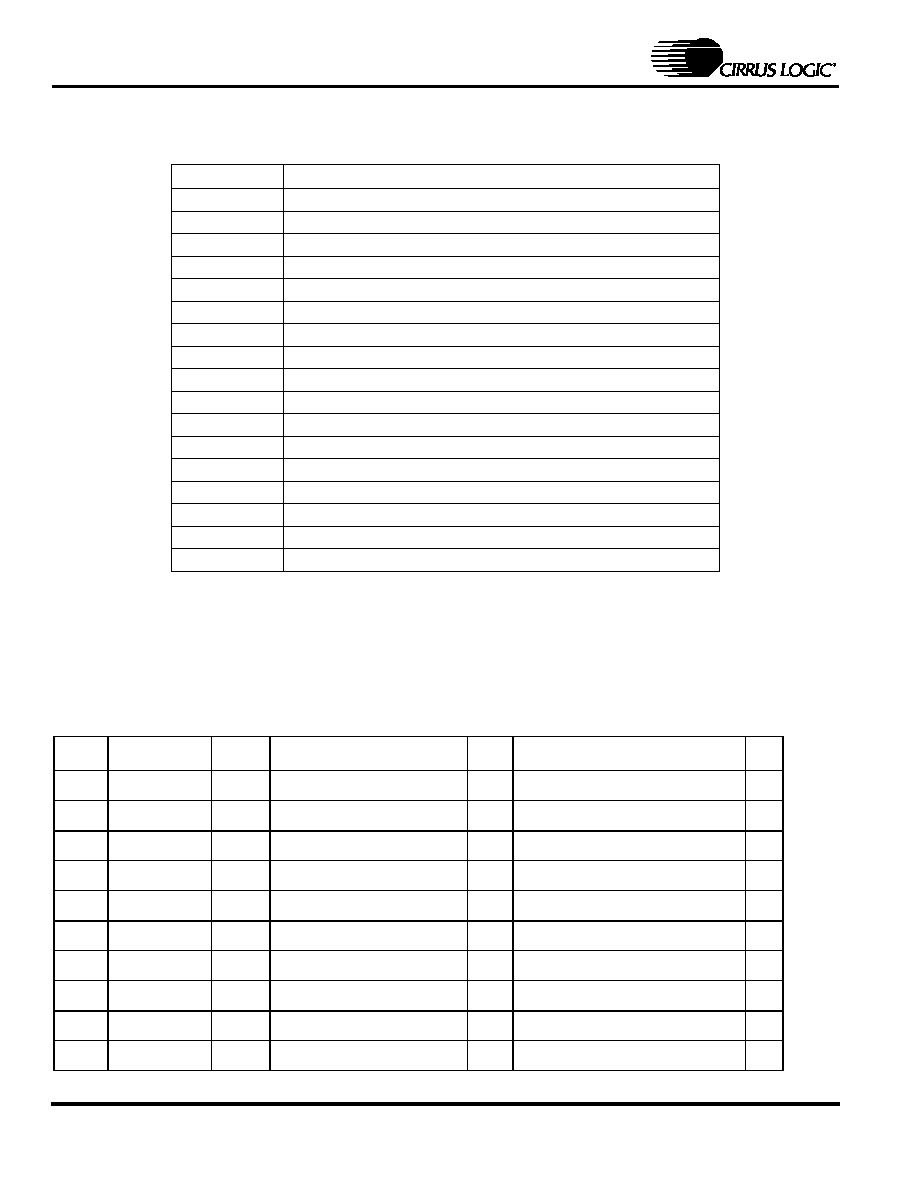

Here is a summary of the CS98200 features.

System Characteristics

� Dual 32-bit (180 MHz) RISC processors

� 32-bit DSP processor ~ 180 MIPS

� 240-pin MQFP package

� All I/O pins are 3 V with 5 V tolerance

� Advanced 0.18 � CMOS technology

� Low power modes and clock shutoff

Memory Controller

� Up to 120 MHz SDRAM from 4 MB to 32 MB

� FLASH databus isolated from SDRAM bus to allow

faster SDRAM access

� 32-bit data bus for DRAM, 8-bit data bus for ROM

data flow engine

� Two DMA controllers -- local memory based and

direct memory-to-memory

� DMA to/from main RAM into local SRAM

MPEG Video Decoder

� DVD, VCD, VCD 2.0 and SVCD

� MPEG-1, MPEG-2, and MPEG-4 simple profile

� Anti-tearing logic controls picture decode and

presentation

� Advanced error concealment hardware

Audio Interface

� 8 channels PCM output at 24-bits/192 kHz output

rate

� 2 channels I2S input at 24-bits/96 kHz

� IEC 60958/61937 capabilities

External Interface

� Serial master/slave ports for controlling DVD device

� ATAPI/IDE interface can also control hard disk

drives for PVR features

� Programmable bidirectional I/O pins

� All pins not used for other functions can be

reassigned as general purpose I/O pins

� Hardware assisted support for infrared remote

devices, such as remote control, infrared keyboard,

mouse, printer, and more

� Programmable parallel host master interface supports

formats including ATAPI, ISA, and more

� I/O channel interface supports all DVD loader

protocols

Video Processor

� OSD module with multiple regions and

transparencies

� Full screen graphics module, with 16 bit true-color

graphics plane

� High quality video scaling using multi-tap

programmable vertical and horizontal filters

Video Encoder

� Six 10-bit video DAC's, drives 37.5

load directly

� Progressive (480p) or interlaced PAL (B, D, G, H, I, N,

M, 60) and NTSC mode output

� Component (RBG or YUV) or composite + S-Video

output

� Macrovision

TM

7.1 support (interlaced) and

Macrovision

TM

1.03 support (progressive)

� Wide-screen signaling support (interlaced and

progressive) and CGMS

� Closed captioning support

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

3

CS98200

Next Generation DVD Processor

R IS C 0

R IS C 1

D S P

Au d io

In terfa ce

In stru ction

C ach e

D ata

C ach e

C PU Pipe

M A C

In stru ction

C ach e

D ata

C ach e

M A C

C PU Pipe

C PU /M A C

In stru ction

C ach e

X,Y D ata

M e m o ry

PC M O u t

PC M In

SP D IF O u t

D V D L o ad er I/O

M P E G D ec o d er

VL C

Pa rser

M o tion

C om p

ID C T

R AM

D VD C ustom L oad er

Pa ralle l/Se ria l Da ta

Se ria l C on tro l

AT AP I/G en eric

Pa ralle l Bu s Interfa ce

H o s t B u s I/O

D ata flo w

E n g in e

S ys tem C o n tro ls

N T S C /P A L E n co d er

V id e o P ro ce ss o r

S u b p ic tu re

S R A M + C P U IF

S ys tem S yn c

S im p le I/O

D R AM

C o n tro lle r

V id e o C ap tu re

G rap h ics

D M A (R d + W r)

FL AS H

M em ory.C o ntrol

ST C

Sch ed ule

D M A (2)t

SR A M Bu ffer

D ecryptio n

M isc.

R eg ister

Ba nks

In te rrup t

PL L

PL L

Tim e rs

D ig ital

En cod in g

3 D AC s

3 D AC s

32 K Byte

In te rna l

SR A M

Arb iter

+

C on tro l

D M A

D eco de

r

Sca le r

Line B uffe r

O n Scre en D ispla y O ve rla y

M a in V id eo

Sca ling a nd D ispla y

Pictu re in P icture O ve rla y

Line B uffe r / F licke r F ilte r

M a in G ra ph ics

D eco de r

FIFO

SD R A M C on tro l

Vide o M ixin g

D ua l U AR T

PW M S em i-D A C

2-W ire Se ria l (I

2

C )

3/4 W ire S erial (SP I)

Pro gra m m ab le I/O

In fra red Inp ut

PL L

M P E G 4 V id eo

D ec o d er Ac ce lera to r

C PU In te rfa ce

AL U + log ic

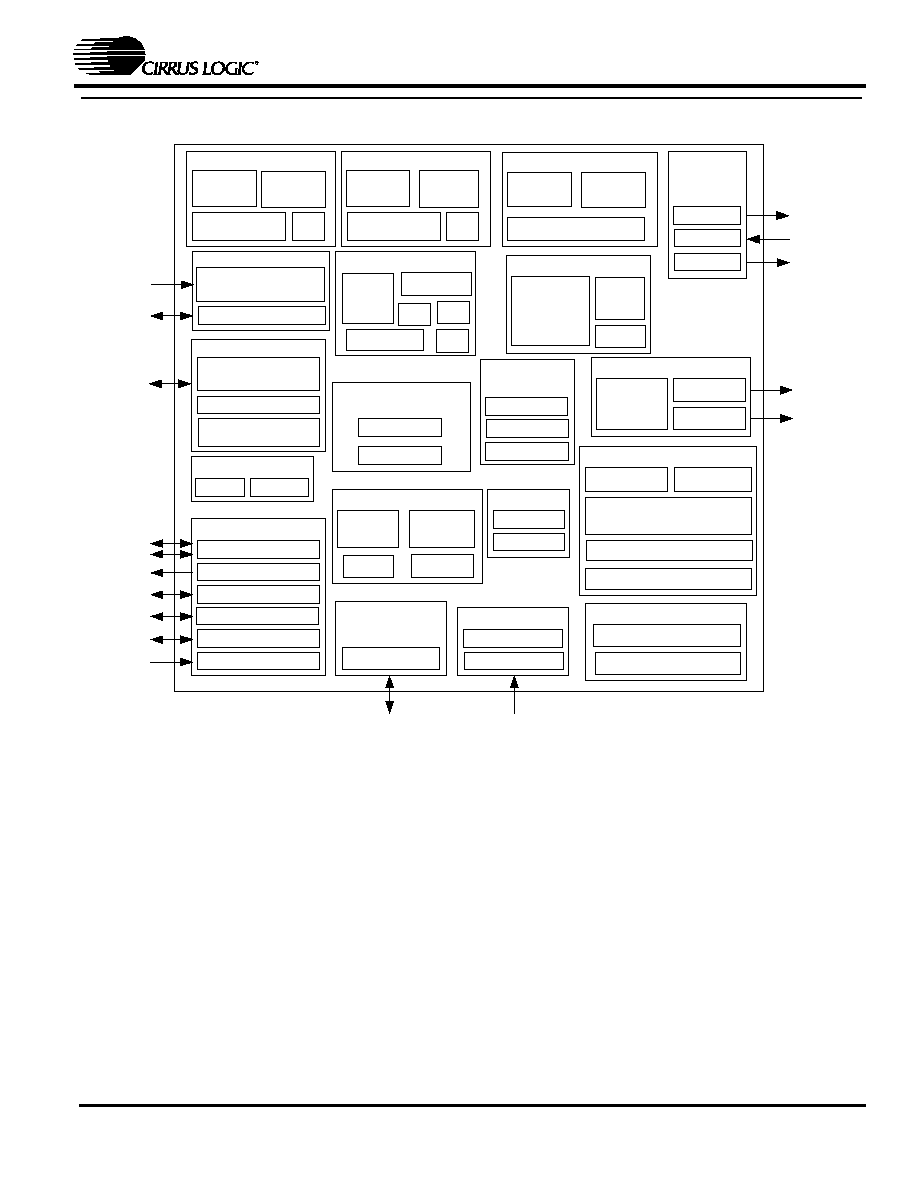

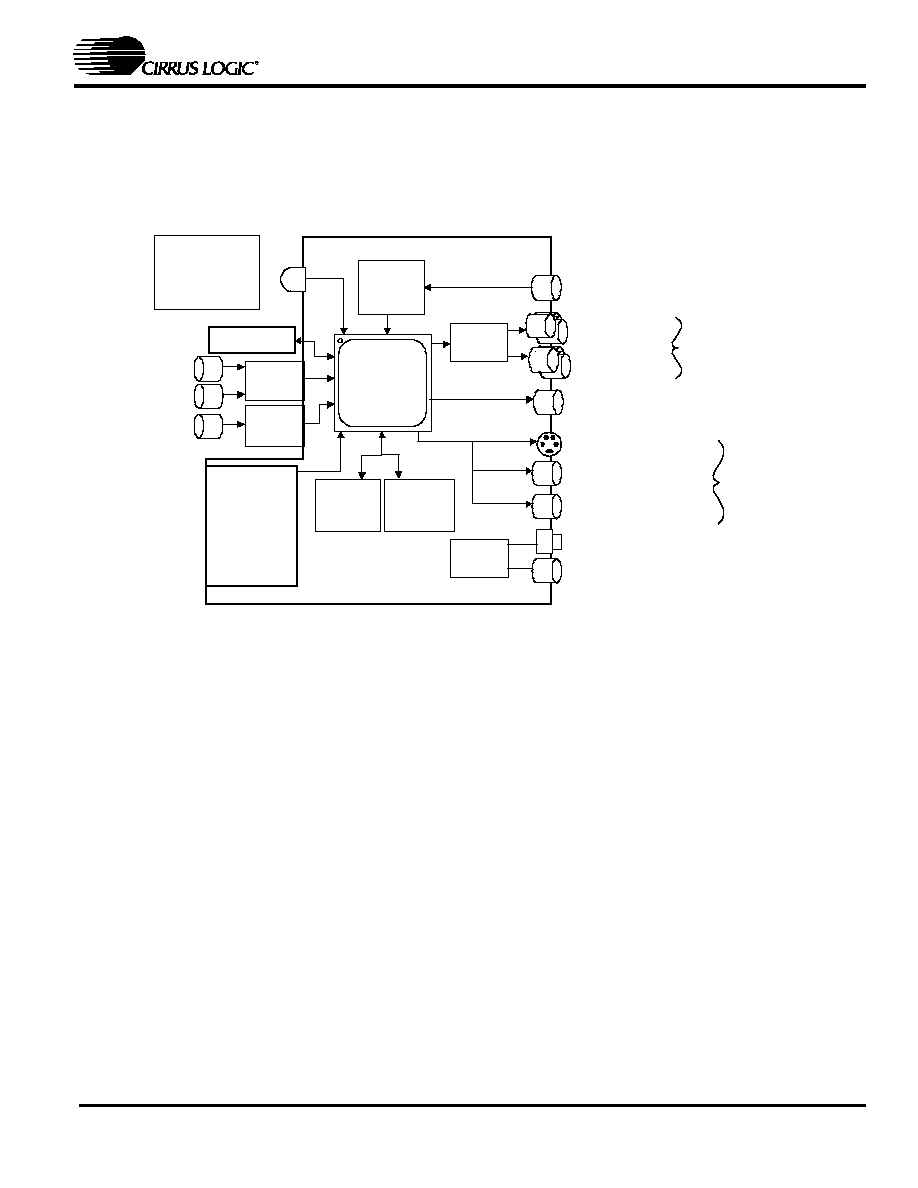

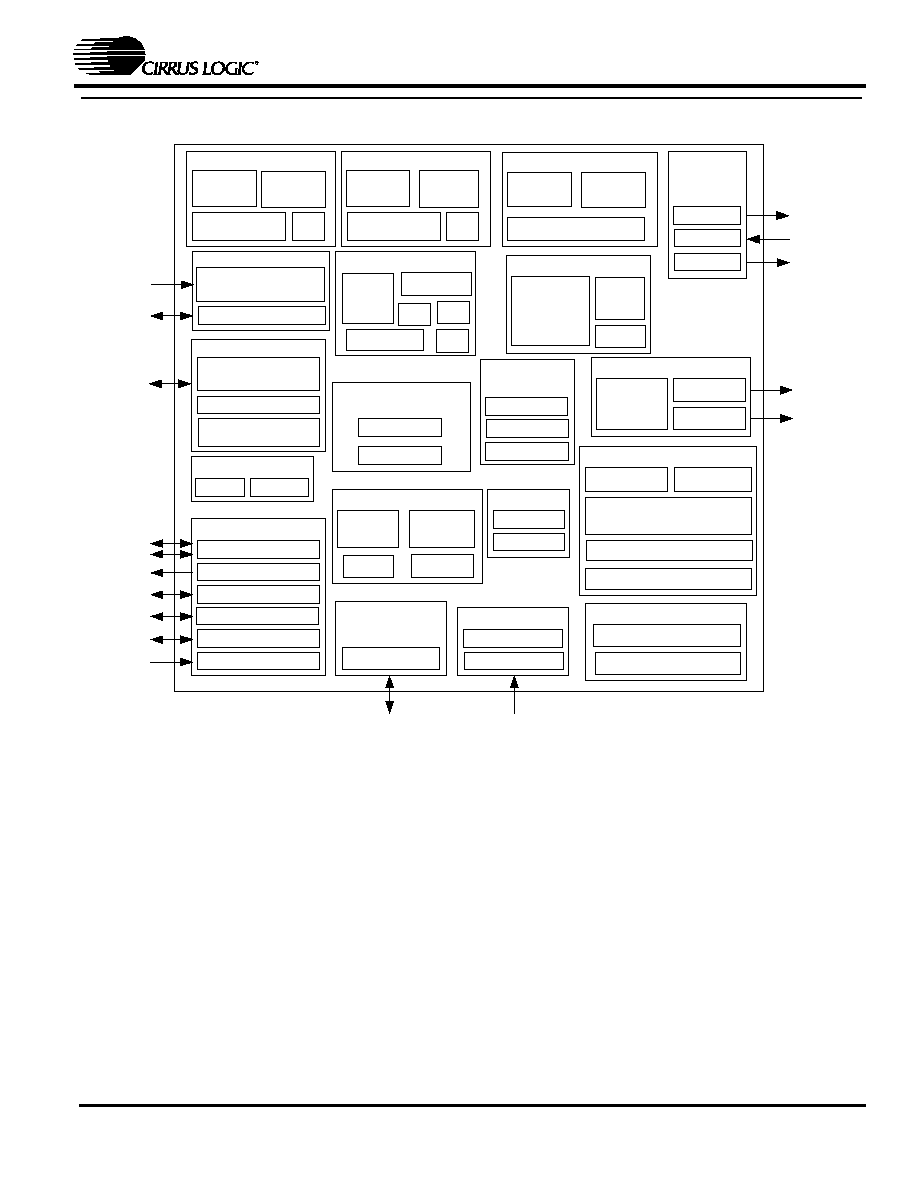

BLOCK DIAGRAM

4

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

Table of Contents

1. CHARACTERISTICS AND SPECIFICATIONS ........................................................................ 8

1.1 AC and DC Parametric Specifications ...............................................................................8

1.1.1 Absolute Maximum Rating .................................................................................... 8

1.1.2 Recommended Operating Conditions ...................................................................8

1.1.3 Electrical Characteristics ......................................................................................8

2. TIMINGS .................................................................................................................................. 10

2.1 Timing Diagram Conventions ........................................................................................... 10

2.2 DC Characteristics ........................................................................................................... 11

2.2.1 ATAPI Interface ................................................................................................... 11

2.2.2 DVD Loader Interface ......................................................................................... 12

2.2.3 DVD Serial Interface Timing ................................................................................ 15

2.2.4 SDRAM Interface ................................................................................................ 16

2.2.5 ROM/NVRAM Interface ....................................................................................... 18

2.2.6 Digital Video Output Interface ............................................................................. 20

2.2.7 Video Input Interface ........................................................................................... 21

2.2.8 Audio Input Interface Timing ............................................................................... 22

2.2.9 Audio Output Interface Timing ............................................................................. 23

2.2.10 Miscellaneous Timings ...................................................................................... 24

3. TYPICAL APPLICATION ........................................................................................................ 25

4. CS98200 DEVICE SUMMARY ................................................................................................ 26

4.1 Block Diagram .................................................................................................................. 26

Contacting Cirrus Logic Support

Fo r a ll pro du ct qu es tio ns a nd in qu iries con tac t a C irrus L og ic S ales R e pre se ntative .

To find on e n ea rest yo u g o to

http://www.cirrus.com /corporate/contacts/sales.cfm

IMPORTANT NOTICE

"Preliminary" product information describes products that are in production, but for which full characterization data is not yet available. "Advance" product information

describes products that are in development and subject to development changes. Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in

this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" wit hout warranty of any kind (express or

implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete.

All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement,

and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this infor mation as the basis for manufacture or sale of

any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license,

express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights of the infor-

mation contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other

parts of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for

resale.

An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or techno logies described in this material and

controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan. An export license and/or quota needs to be obtained from the

competent authorities of the Chinese Government if any of the products or technologies described in this material is subject to the PRC Foreign Trade Law and is to be

exported or taken out of the PRC.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR

ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR

USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDE R-

STOOD TO BE FULLY AT THE CUSTOMER'S RISK.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names i n this document may be trademarks or

service marks of their respective owners.

Purchase of I

2

C components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the Phillips I

2

C Patent Rights to use those com-

ponents in a standard I

2

C system

Microsoft

�

and Windows Media Technology

TM

are registered trademarks or trademarks of Microsoft, Inc. in the United States and/or other countries.

. HDCD

�

,

High Definition Compatible Digital

�

and Pacific Microsonics

TM

Inc. are either registered trademarks or trademarks of Pacific Microsonics Inc. in the United States and/or

other countries. HDCD technology provided under license from Pacific Microsonics Inc. This products design (and/or software) is covered by one or more of the following:

5,479,168; 5,638,074; 5,640,161; 5,808,574; 5,838,274; 5,854,600; 5,864,311; 5,872,531 with other patents pending.

Dolby Digital, AC-3, Dolby Pro Logic, Dolby Pro Logic II, Dolby Surround, Surround EX, Virtual Dolby Digital and the "AAC" logo are trademarks and the "Dolby Digital"

logo, "Dolby Digital with Pro Logic II" logo, "Dolby" and the double-"D" symbol are registered trademarks of Dolby Laboratories Licensing Corporation. DTS, DTS Digital

Surround, DTS-ES Extended Surround, DTS Neo:6, and DTS Virtual 5.1 are trademarks and the "DTS", "DTS-ES", "DTS Virtual 5.1" logos are registered trademarks of the

Digital Theater Systems Corporation. The "MPEG Logo" is a registered trademark of Philips Electronics N. V. Home THX Cinema and THX are registered trademarks of

Lucasfilm Ltd. Surround EX is a jointly developed technology of THX and Dolby Labs, Inc. AAC (Advanced Audio Coding) is an "MPEG-2-standard-based" digital audio

compression algorithm (offering up 5.1 discrete decoded channels for this implementation) collaboratively developed by AT&T, the Fraunhofer Institute, Dolby Laborato-

ries, and the Sony Corporation. In regards to the MP3 capable functionality of the CS98XXX Family DSP (via downloading of mp3_49 3xxx_vv.ld and mp3e_493xxx_vv.ld

application codes) the following statements are applicable: "Supply of this product conveys a license for personal, private and non-commercial use. MPEG Layer III audio

decoding technology licensed from Fraunhofer IIS and THOMSON Multimedia."

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

5

CS98200

Next Generation DVD Processor

4.2 CS98200 Device Details .................................................................................................. 26

4.2.1 RISC-32 Processors ........................................................................................... 26

4.2.2 Powerful 24/32-Bit DSP ...................................................................................... 26

4.2.3 System Controls .................................................................................................. 26

4.2.4 Memory Controller .............................................................................................. 26

4.2.5 Data Flow Engine ................................................................................................ 27

4.2.6 MPEG Video Decoder ......................................................................................... 27

4.2.7 System Synchronization ..................................................................................... 27

4.2.8 Audio Interface .................................................................................................... 27

4.2.9 Video Input .......................................................................................................... 27

4.2.10 External Interface .............................................................................................. 27

4.2.11 Video Processor ................................................................................................ 27

4.2.12 Sub-Picture Processor ...................................................................................... 27

4.2.13 Graphics Engine ............................................................................................... 27

4.2.14 On Screen Display Module ............................................................................... 28

4.2.15 DVD Loader Interface ....................................................................................... 28

4.2.16 CPU Interface and SRAM Controller ................................................................ 28

4.2.17 Host Bus Interface ............................................................................................ 28

4.2.18 Video Encoder .................................................................................................. 28

4.2.19 System Functions ............................................................................................. 28

5. FUNCTIONAL DESCRIPTION ............................................................................................... 29

5.1 RISC Processor ............................................................................................................... 29

5.2 DSP Processor ................................................................................................................ 29

5.3 Memory Control ............................................................................................................... 29

5.4 Dataflow Control (DMA) ................................................................................................... 29

5.5 System Control Functions ............................................................................................... 29

5.6 DVD/ATAPI Interface ....................................................................................................... 30

5.7 Serial DVD Interface ........................................................................................................ 30

5.8 MPEG Video Decoding .................................................................................................... 30

5.9 Audio Processing ............................................................................................................. 30

5.10 Video Encoder with Progressive Video DACs ............................................................... 32

5.11 Video Input/Output Interface .......................................................................................... 33

5.12 Universal Asynchronous Receiver/Transmitters (UARTs) ............................................. 34

6. MEMORY MAP ....................................................................................................................... 35

6.1 Processor Memory Map .................................................................................................. 35

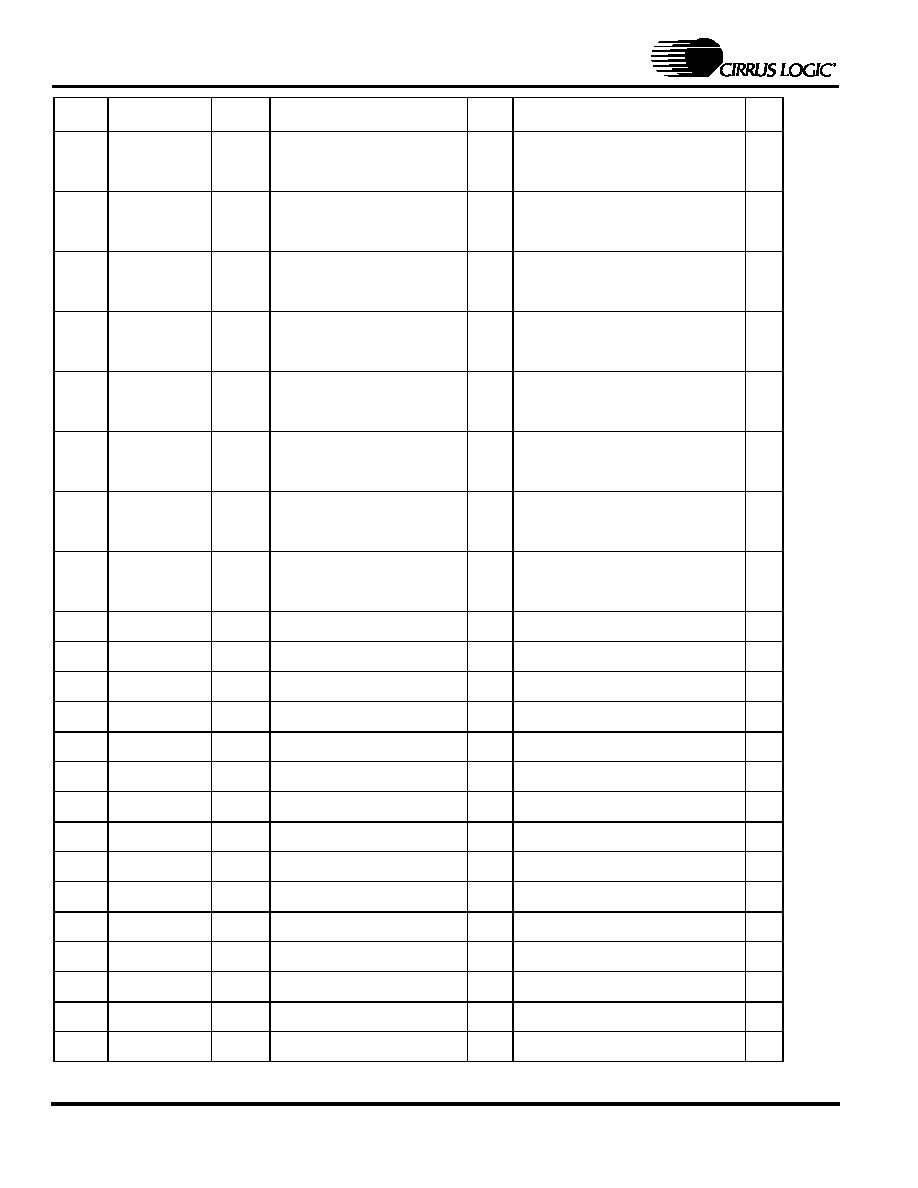

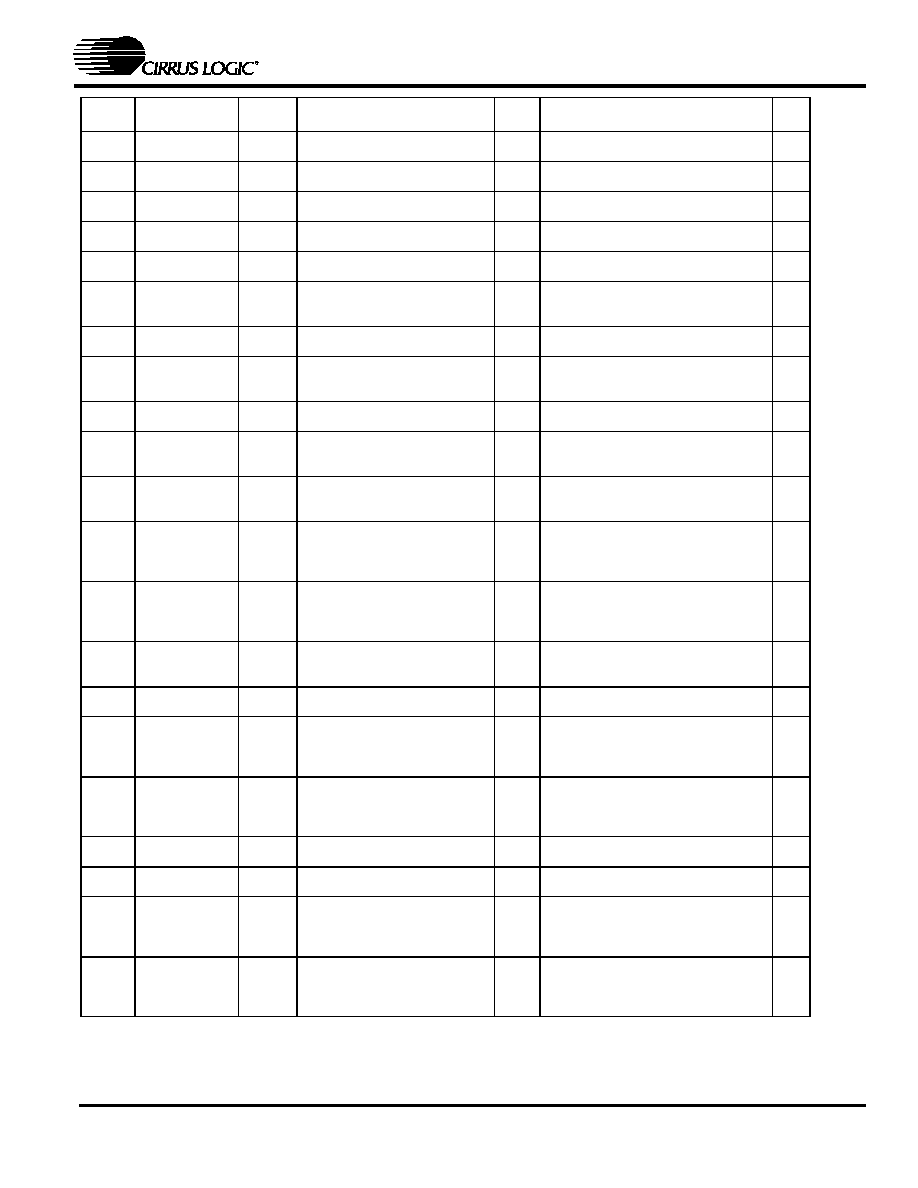

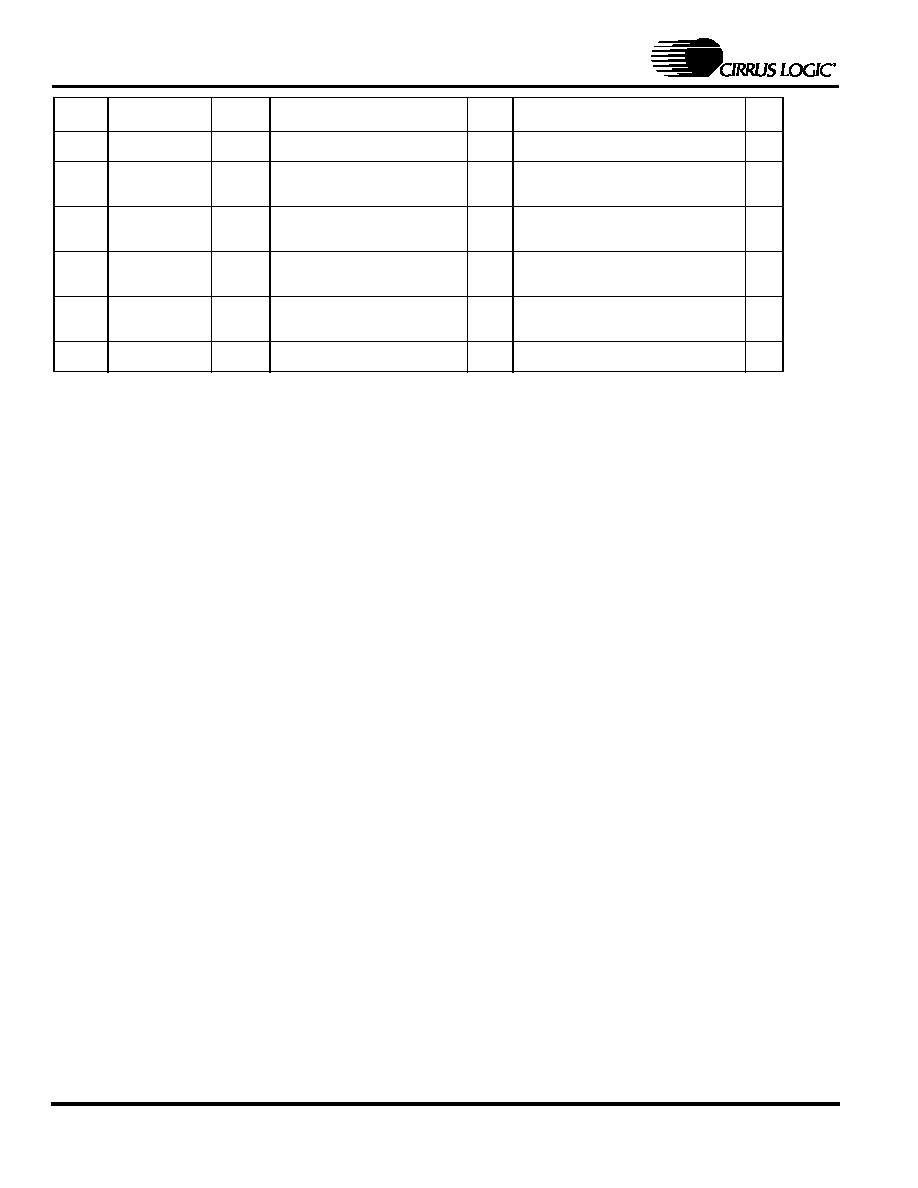

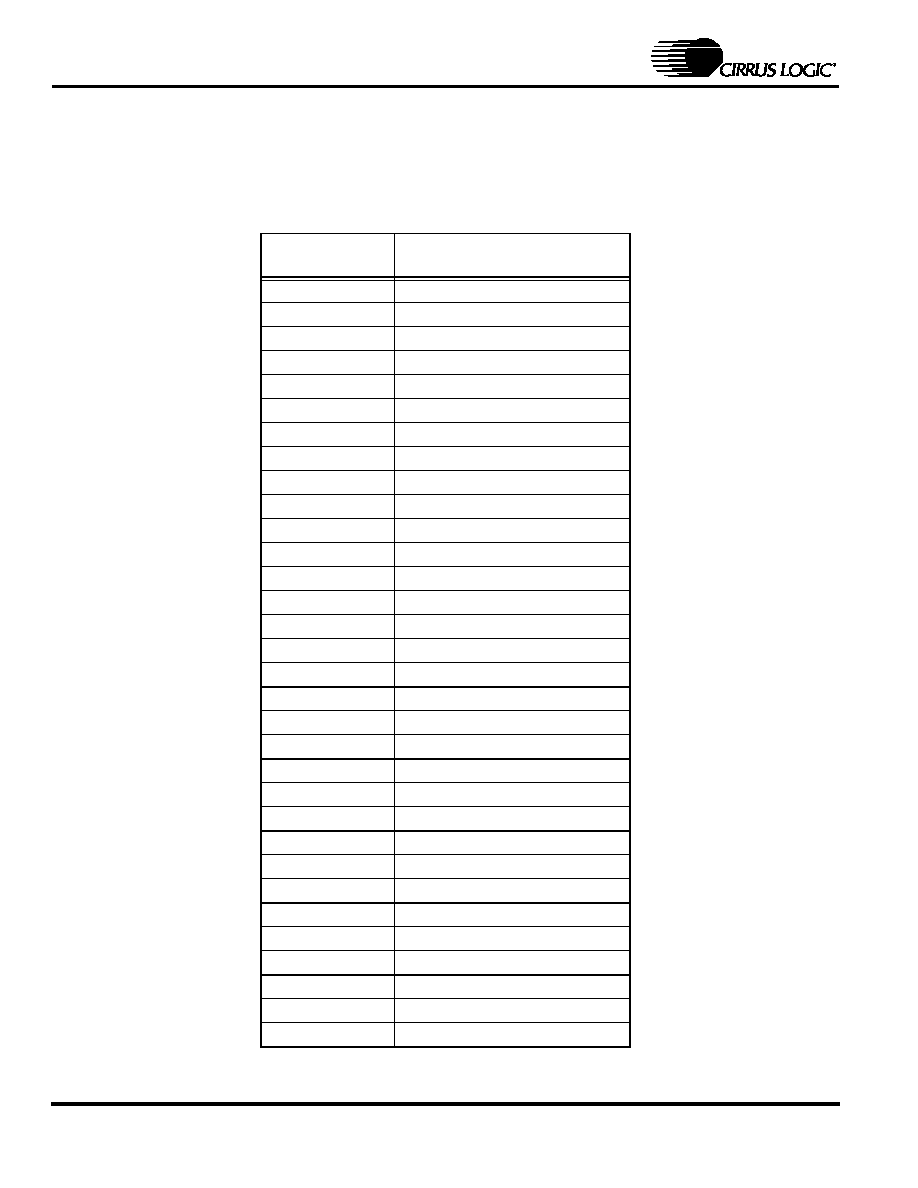

7. 240-PIN MQFP PIN DESCRIPTION ....................................................................................... 36

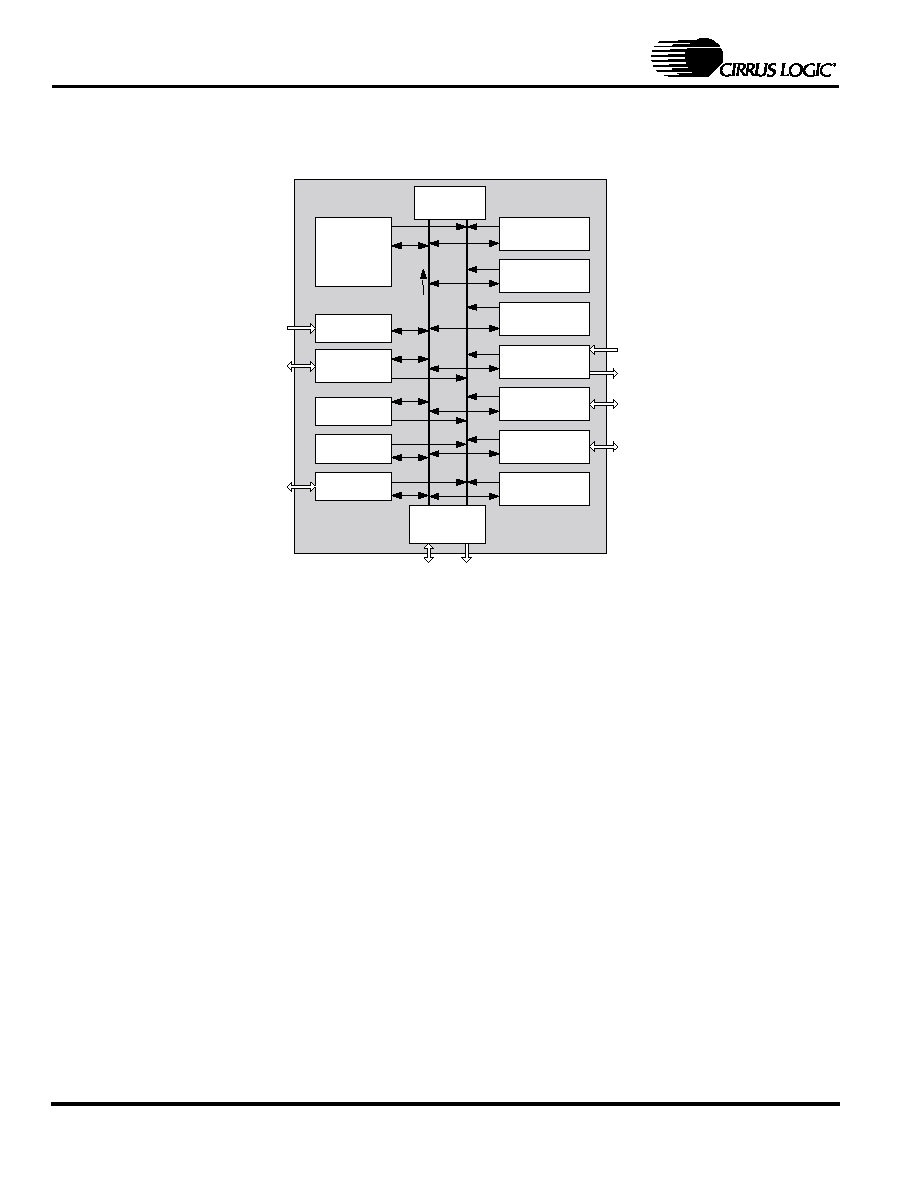

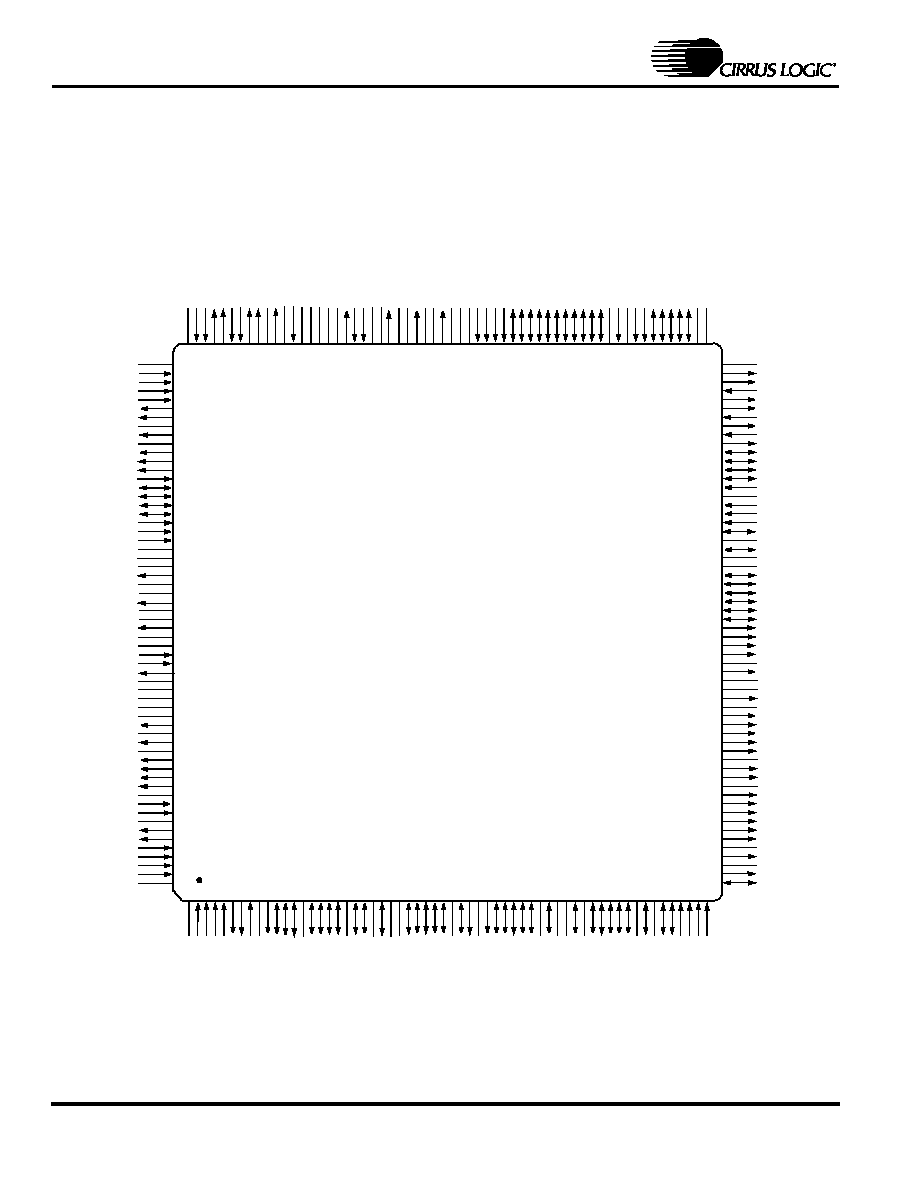

7.1 240-Pin MQFP Pin Layout ............................................................................................... 36

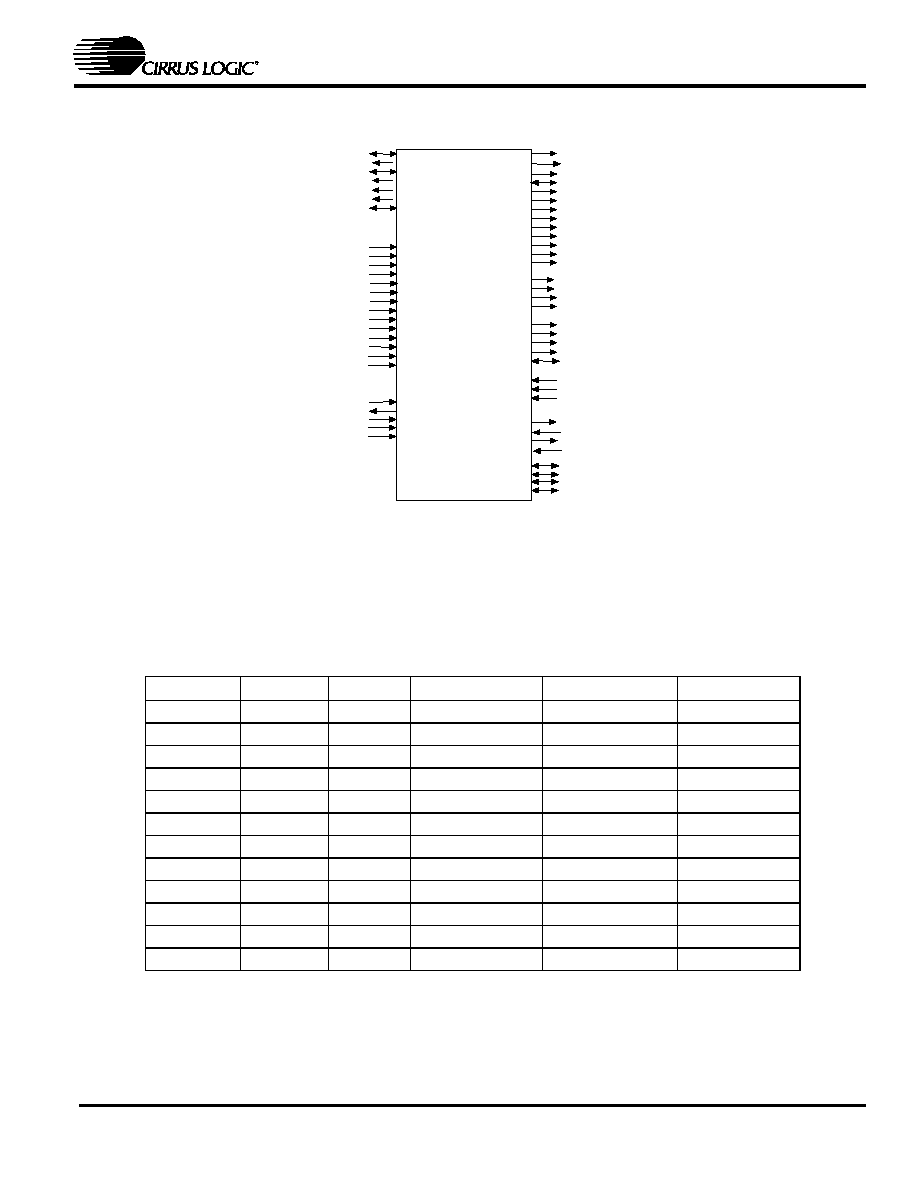

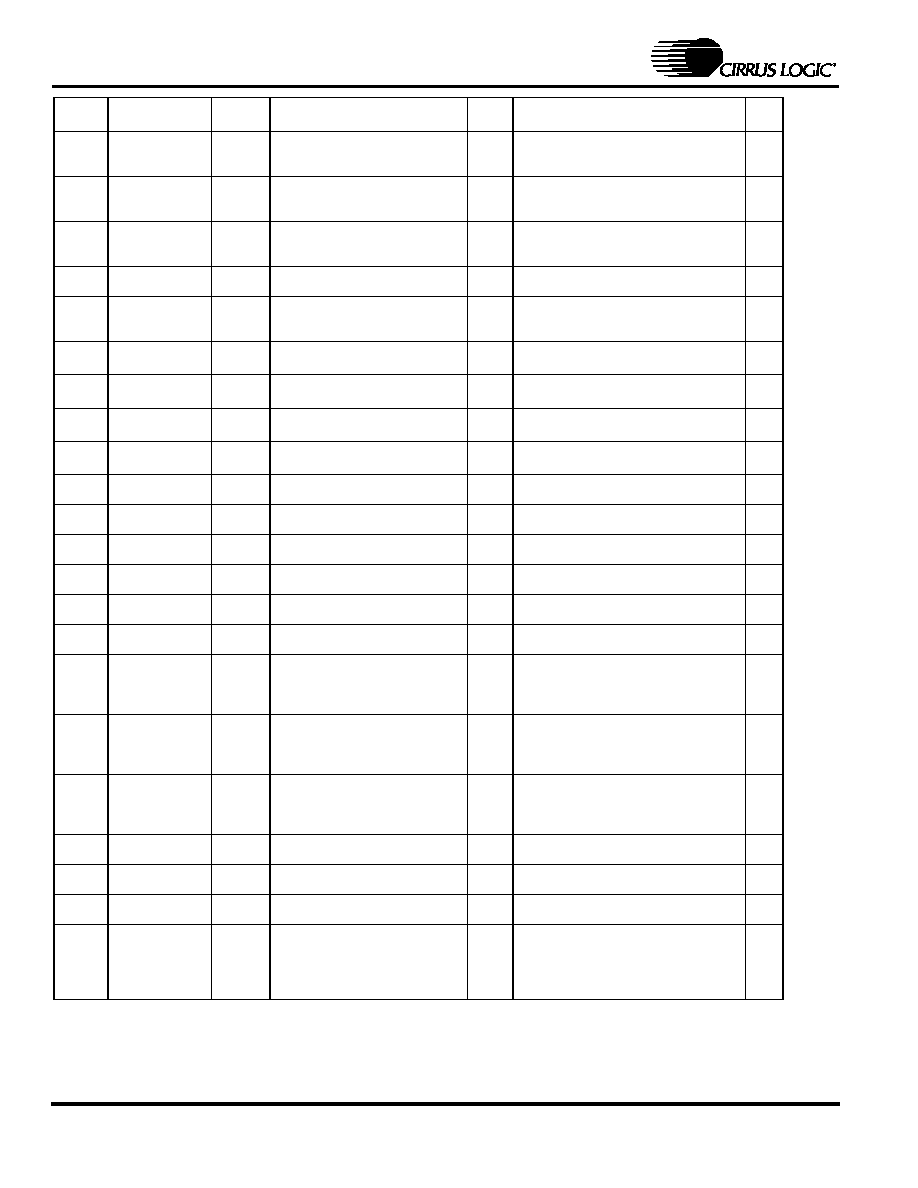

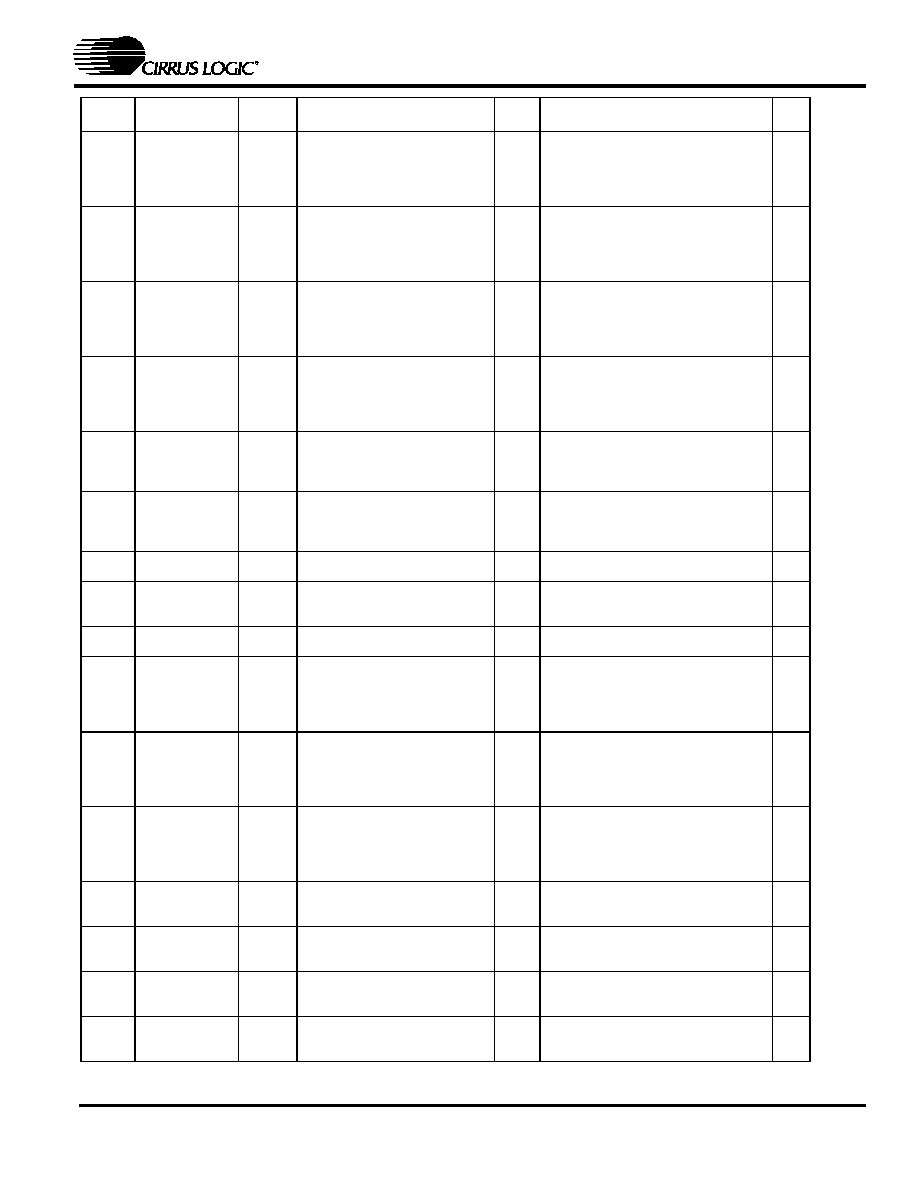

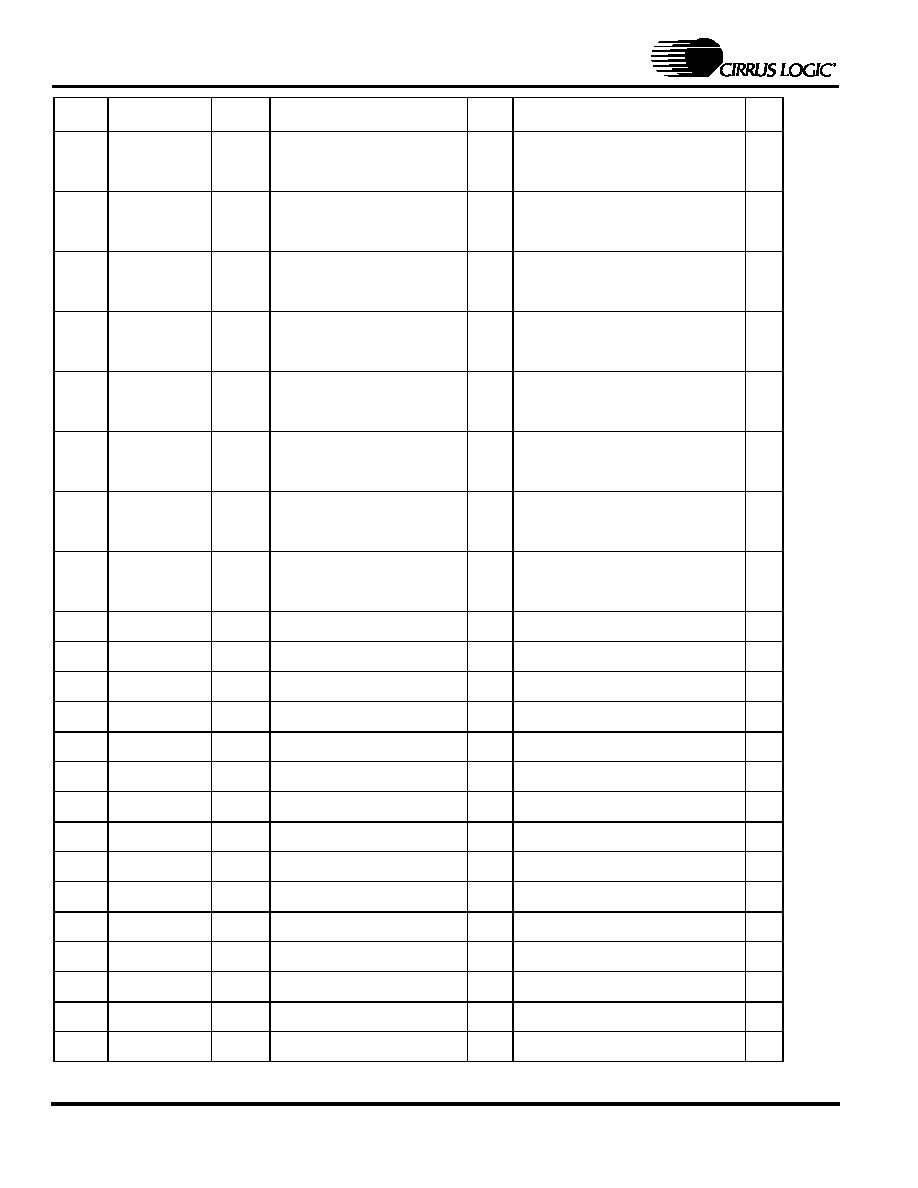

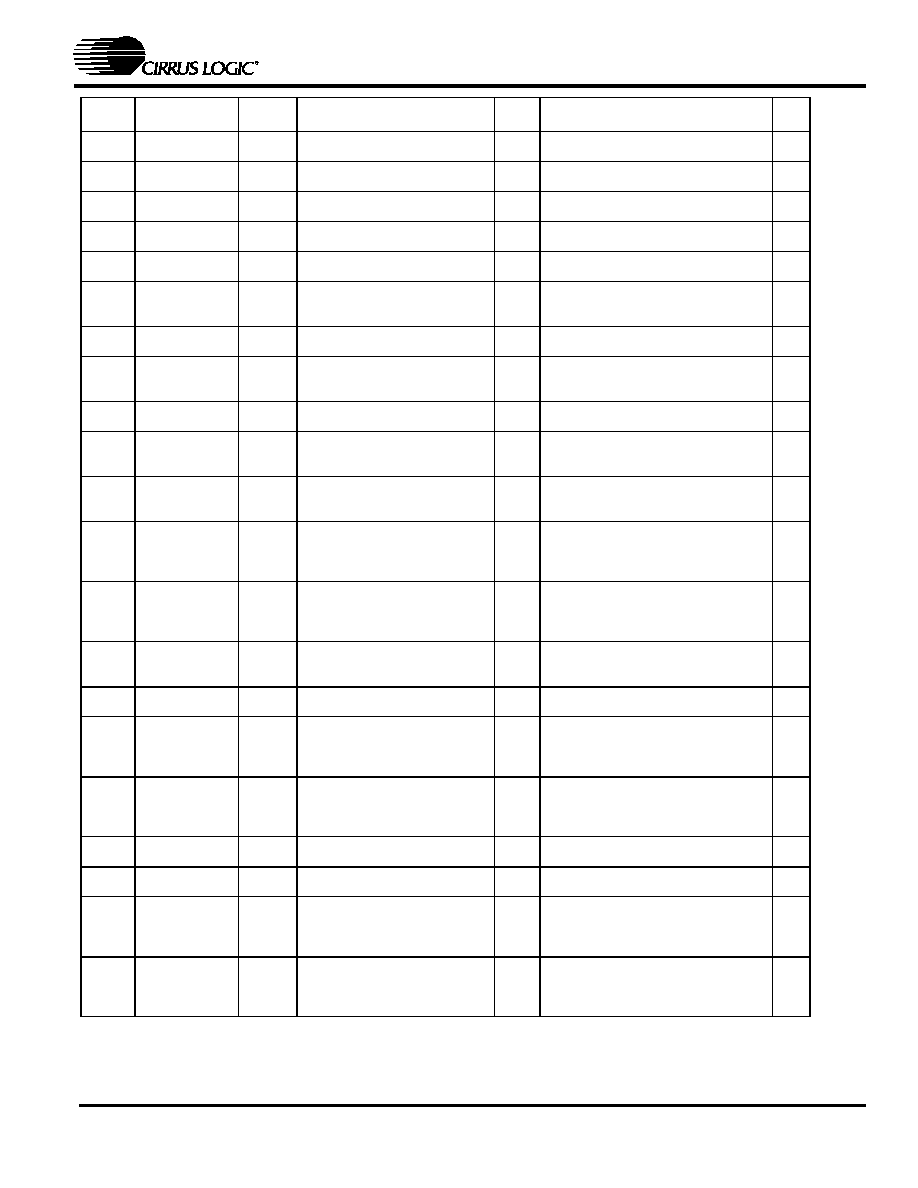

7.2 240-Pin MQFP Pin Summary .......................................................................................... 37

7.3 Pin Configuration Summary ............................................................................................. 37

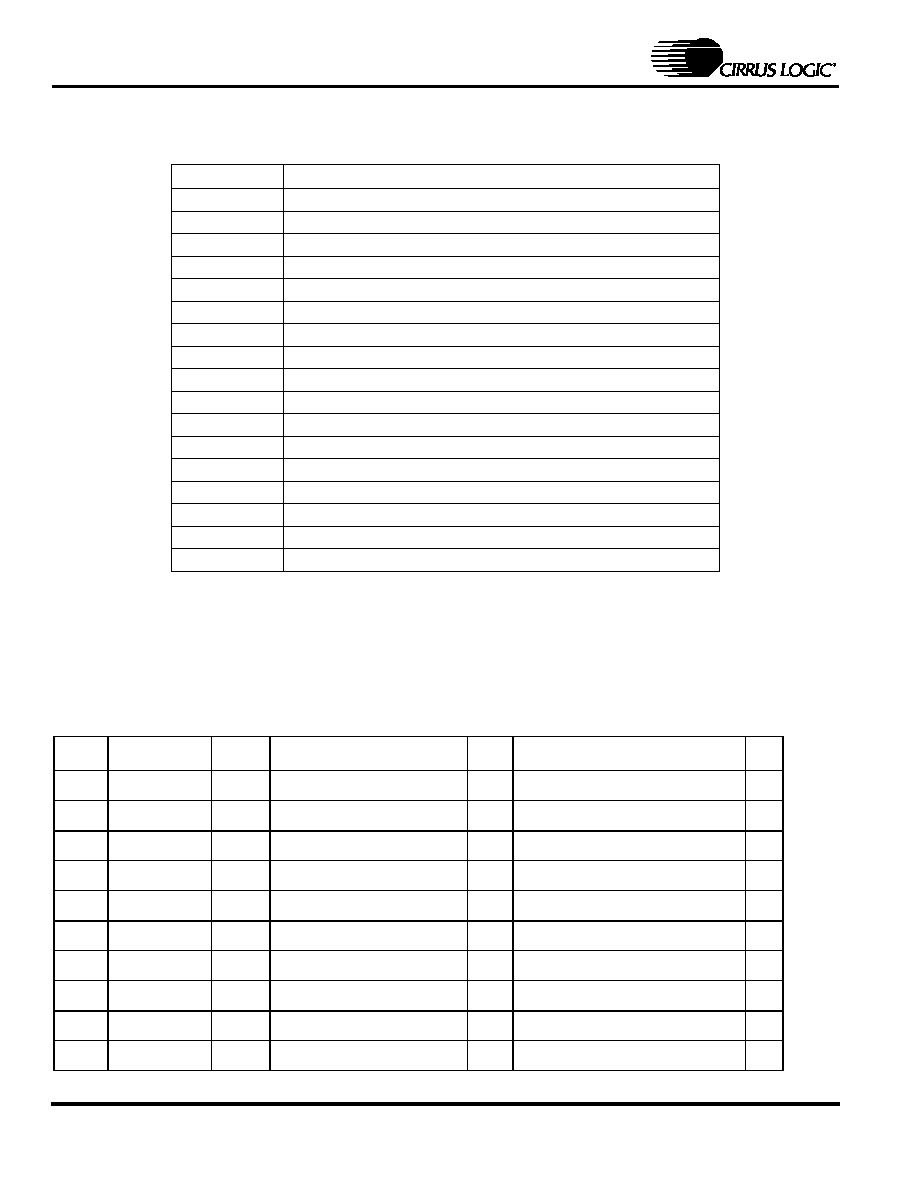

7.4 Explanation of Pin Types ................................................................................................. 38

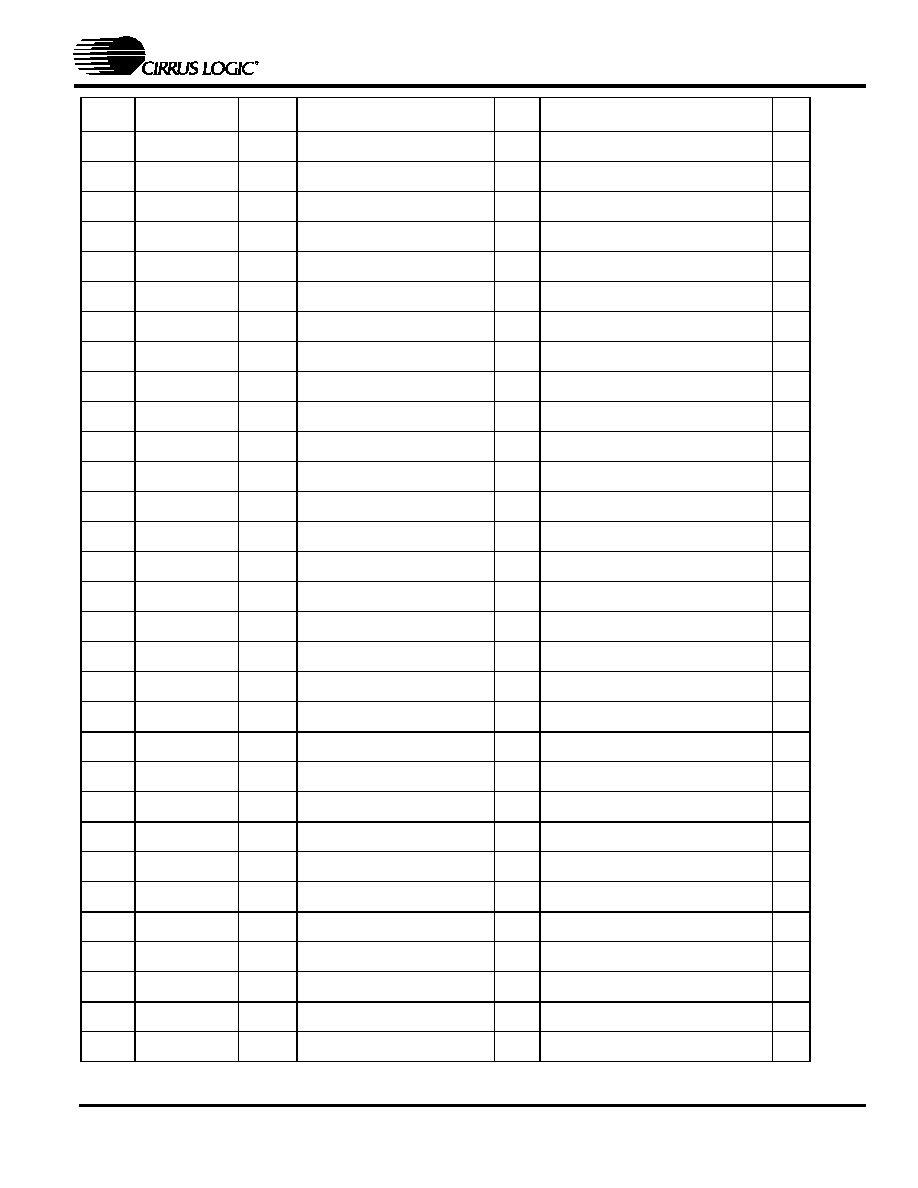

7.5 240-Pin MQFP Pin Assignments ..................................................................................... 38

8. INTERFACE DESCRIPTIONS ................................................................................................ 49

8.1 SDRAM Interface Pins ..................................................................................................... 49

8.2 ROM/NVRAM Interface Pins ........................................................................................... 49

8.3 Video Output Interface Pins ............................................................................................. 50

8.4 Video Input Interface Pins ............................................................................................... 50

8.5 Audio PCM Interface Pins ............................................................................................... 51

8.6 Host Master/ATAPI Interface ........................................................................................... 52

8.7 DVD Loader Interface ...................................................................................................... 53

8.8 DVD Serial Data Interface ............................................................................................... 53

8.9 SPI Interface .................................................................................................................... 54

8.10 General Purpose Input/Output (GPIO) .......................................................................... 54

8.11 UART Interface Pins ...................................................................................................... 55

8.12 I

2

C Interface .................................................................................................................. 55

8.13 Miscellaneous Interface Pins ......................................................................................... 55

6

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

8.14 Power and Ground ......................................................................................................... 56

9. 240-PIN MQFP PACKAGE SPECIFICATIONS ...................................................................... 57

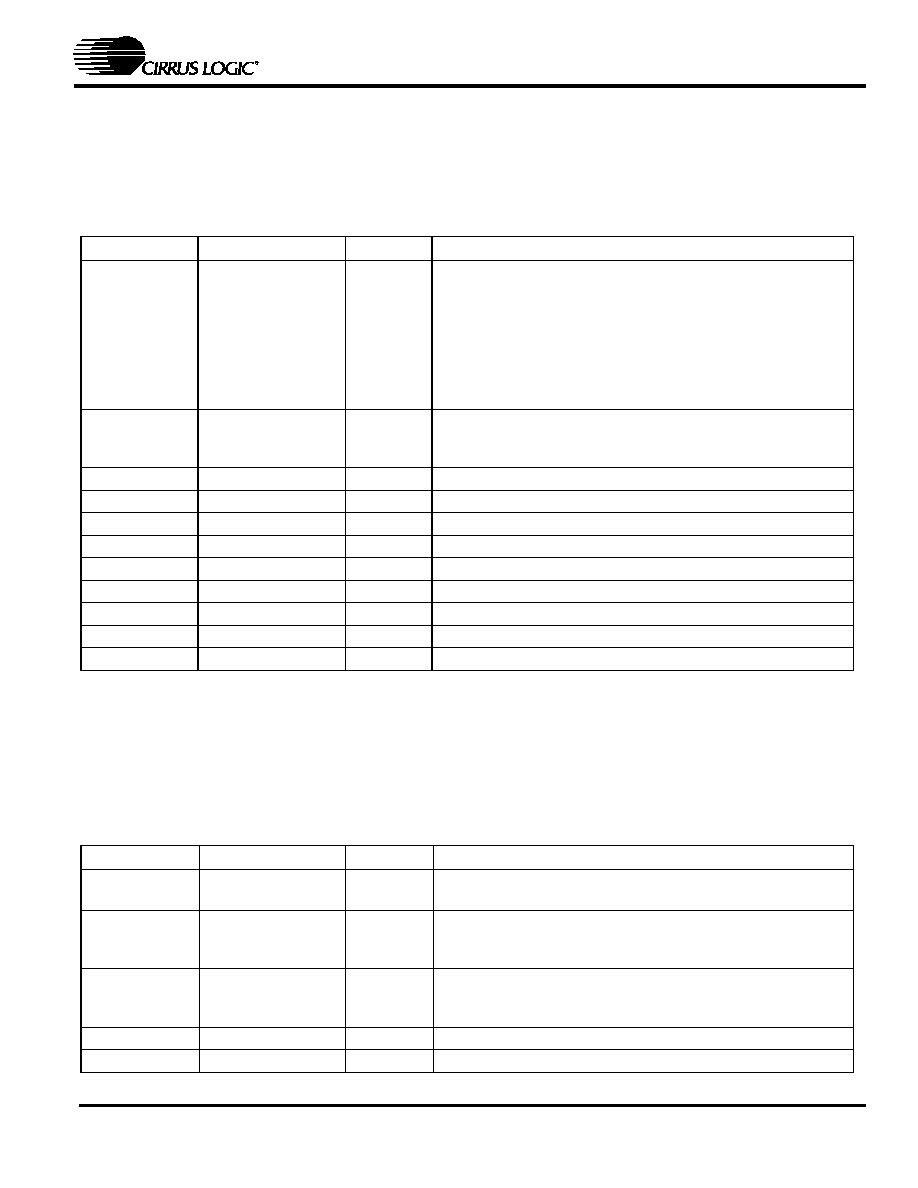

10. CONVENTIONS .................................................................................................................... 58

10.1 Acronyms and Abbreviations ......................................................................................... 58

10.2 Units of Measurement .................................................................................................... 59

10.3 General Conventions ..................................................................................................... 59

10.4 Pin Description Conventions .......................................................................................... 60

11. ORDERING INFORMATION LEGEND ................................................................................. 60

List of Figures

Figure 1. Legend for Timing Diagrams .......................................................................................... 10

Figure 2. ATAPI Interface Timing Diagram.................................................................................... 11

Figure 3. DVD Loader Host Interface ............................................................................................ 12

Figure 4. DVD Loader Data Interface ............................................................................................ 13

Figure 5. DVD Loader CD Interface .............................................................................................. 13

Figure 6. DVD Loader CD Interface Formats ................................................................................ 14

Figure 7. DVD Serial Interface Timing ........................................................................................... 15

Figure 8. SDRAM Refresh Transaction ......................................................................................... 16

Figure 9. SDRAM Burst Write Transaction.................................................................................... 16

Figure 10. SDRAM Burst Read Transaction.................................................................................. 17

Figure 11. SDRAM Timing............................................................................................................. 17

Figure 12. ROM/NVRAM Reading Timing ..................................................................................... 18

Figure 13. ROM/NVRAM Write Timing.......................................................................................... 19

Figure 14. CS98200 Digital Video Interface Timing Diagram ........................................................ 20

Figure 15. Video Input Timing ....................................................................................................... 21

Figure 16. Audio Input Timings...................................................................................................... 22

Figure 17. Digital Audio Out Timing Diagram ................................................................................ 23

Figure 18. Miscellaneous Timings ................................................................................................. 24

Figure 19. CS98200 Typical Application ....................................................................................... 25

Figure 20. CS98200 Block Diagram .............................................................................................. 26

Figure 21. Video DAC Connections............................................................................................... 32

Figure 22. UART Data Transfer..................................................................................................... 34

Figure 23. 240-Pin MQFP Pin Layout............................................................................................ 36

Figure 24. 240-Pin MQFP Pinout Summary .................................................................................. 37

Figure 25. 240-Pin MQFP Package Drawing ................................................................................ 57

List of Tables

Table 1. ATAPI Interface Characteristics ...................................................................................... 11

Table 2. SDRAM Interface Characteristics .................................................................................... 16

Table 3. RAM/NVROM Characteristics ......................................................................................... 18

Table 4. CS98200 Digital Video Interface Characteristics............................................................. 20

Table 5. Video Input Interface Symbols and Characterization Data .............................................. 21

Table 6. Audio Input Interface Symbols and Characterization Data .............................................. 22

Table 7. Digital Audio Out Characteristics ..................................................................................... 23

Table 8. Miscellaneous Timing Characteristics ............................................................................. 24

Table 9. Memory Map-RISC0 Processor....................................................................................... 35

Table 10. Host Debug Port Address Map...................................................................................... 35

Table 11. DSP Address Map ......................................................................................................... 35

Table 12. Pin Configuration Summary........................................................................................... 37

Table 13. Pin Type Legend ........................................................................................................... 38

Table 14. 240-Pin MQFP Pin Assignments ................................................................................... 38

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

7

CS98200

Next Generation DVD Processor

Table 15. SDRAM Interface Pins .................................................................................................. 49

Table 16. ROM/NVRAM Interface................................................................................................. 49

Table 17. Video Output Interface .................................................................................................. 50

Table 18. Video Input Interface ..................................................................................................... 50

Table 19. PCM Audio Interface ..................................................................................................... 51

Table 20. Host Master/ATAPI Interface ........................................................................................ 52

Table 21. DVD I/O Channel Interface ........................................................................................... 53

Table 22. SPI Interface ................................................................................................................. 54

Table 23. General Purpose I/O Interface ...................................................................................... 54

Table 24. UART Interface Pins ..................................................................................................... 55

Table 25. I

2

C Interface Pins .......................................................................................................... 55

Table 26. Miscellaneous Interface Pins ........................................................................................ 55

Table 27. Power and Ground ........................................................................................................ 56

Table 28. Acronyms and Abbreviations ........................................................................................ 58

Table 29. Units of Measurement ................................................................................................... 59

Table 30. Pin Description Conventions ......................................................................................... 60

8

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

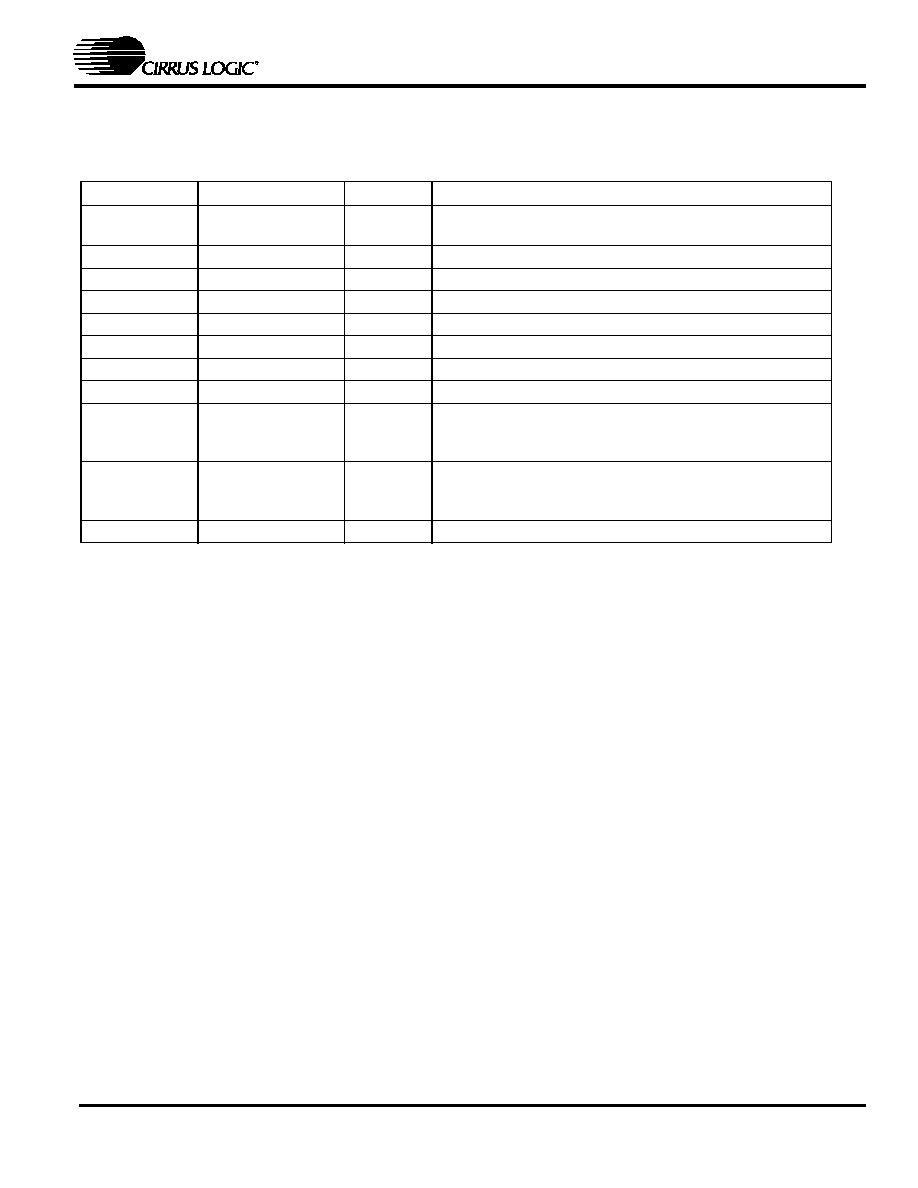

1.

CHARACTERISTICS AND SPECIFICATIONS

1.1

AC AND DC PARAMETRIC SPECIFICATIONS

(AGND, DGND=0 V, all voltages with respect to 0 V)

1.1.1

ABSOLUTE MAXIMUM RATING

CAUTION: Operating beyond these Minimum and Maximum limits can result in permanent dam-

age to the device. Cirrus Logic recommends that CS98200 devices operate at the settings described

in the next table.

1.1.2

RECOMMENDED OPERATING CONDITIONS

1.1.3

ELECTRICAL CHARACTERISTICS

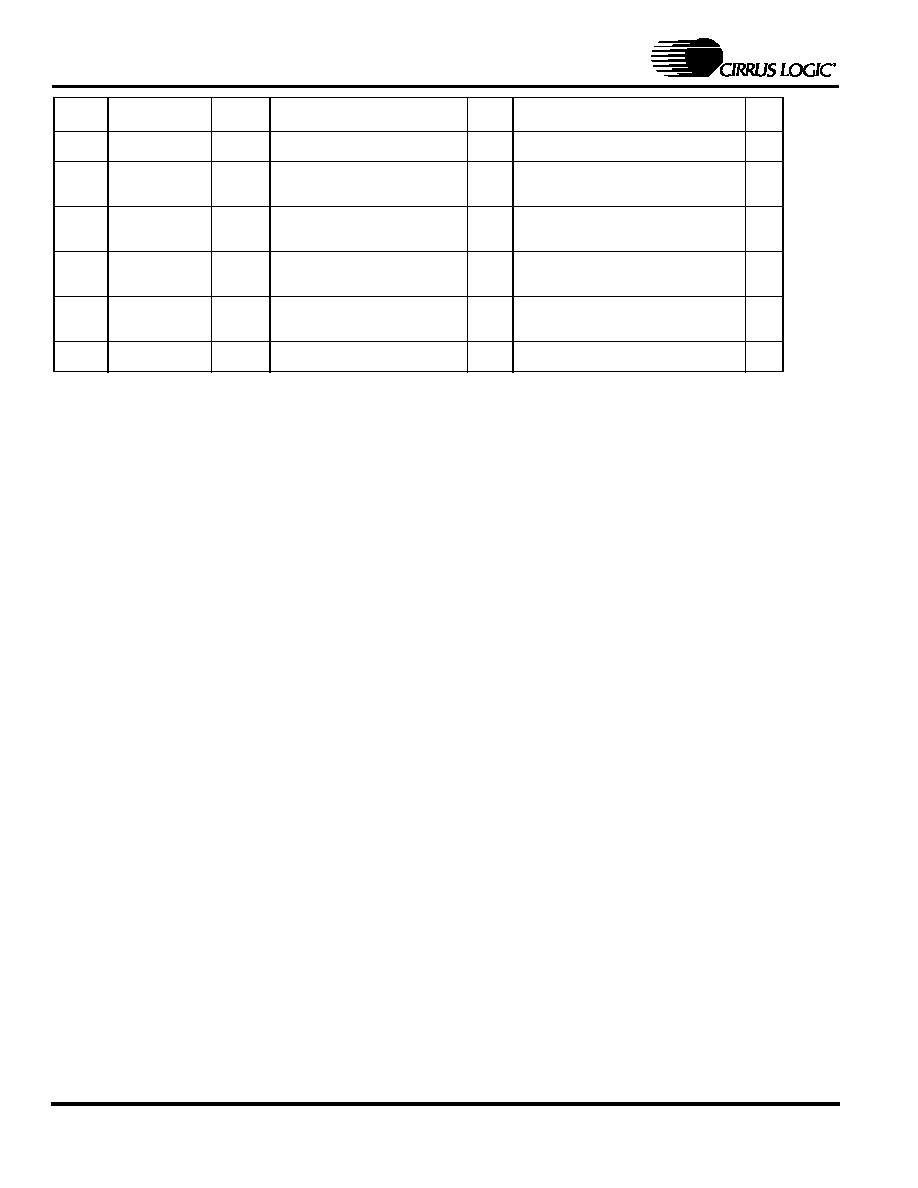

Symbol

Description

Min

Max

Unit

VDD

IO

Power Supply Voltage on analog core and I/O ring

-0,5

4.6

Volts

VDD

CORE

Power Supply Voltage on core logic and PLL

-0.5

2.5

Volts

V

I

Digital Input Applied Voltage (power applied)

-0.5

5.5

Volts

I

I

Digital Input Forced Current

-10

10

mA

I

O

Digital Output Forced Current

-50

50

mA

T

SOL

Lead Soldering Temperature

-

260

o

C

T

VSOL

Vapor Phase Soldering Temperature

-

235

o

C

T

STOR

Storage Temperature (no power applied)

-40

125

o

C

T

AMB

Ambient Temperature (power applied)

0

70

o

C

P

total

Total Power consumption

-

2.2

W

Parameter

Symbol

Min

Typ

Max

Units

Supply Voltage, Analog and IO

V

IO

& V

AA

3.0

3.3

3.6

Volts

Supply Voltage, Core Logic and PLL

V

PLL &

V

DD

1.62

1.8

1.98

Volts

Ambient Temperature (power applied)

T

AMB

0

25

70

o

C

Parameter

Symbol

Conditions

Min

Typ

Max

Units

Supply Current, IO

I

DD

Normal Operating

65

mA

Supply Current, Core Logic and

PLL

I

DD

Normal Operating

210

mA

Input Voltage, High

V

IH

2.0

-

Volts

Input Voltage, Low

V

IL

-

-

0.8

Volts

Input Current

I

IN

V

IN

= V

DD

or V

SS

-1

-

1

�

A

Input Pull up/down resistor

R

I

-

75

-

K

Output Voltage, High

V

OH

@ buffer rating

2.2

-

-

Volts

Output Voltage, Low

V

OL

@ buffer rating

-

-

0.4

Volts

High-Z-state Leakage

I

OZ

V

OUT

= V

SS

or V

DD

-1

-

1

�

A

Video DACs

1

R

SET

= 174

DAC Resolution

10

bits

DAC to DAC matching

2

MAT

2

%

Output Voltage Range

V

out

R

LOAD

= 37.5

3

1.28

Volts

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

9

CS98200

Next Generation DVD Processor

Differential Gain

DG

1

%

Differential Phase

DP

0.5

%

Signal to Noise

SNR

74

dB

Chrominance AM Noise

AM

80

dB

Chrominance PM Noise

PM

75

dB

1.

Video parameters guaranteed only with 1% tolerance resistors or better for Rset and RLoad.

2.

Only applies to each set of three DACs.

3.

RLoad is a double terminated load, which includes a 75

resistor at the video DAC and a 75

resistor at the video monitor.

10

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

2. TIMINGS

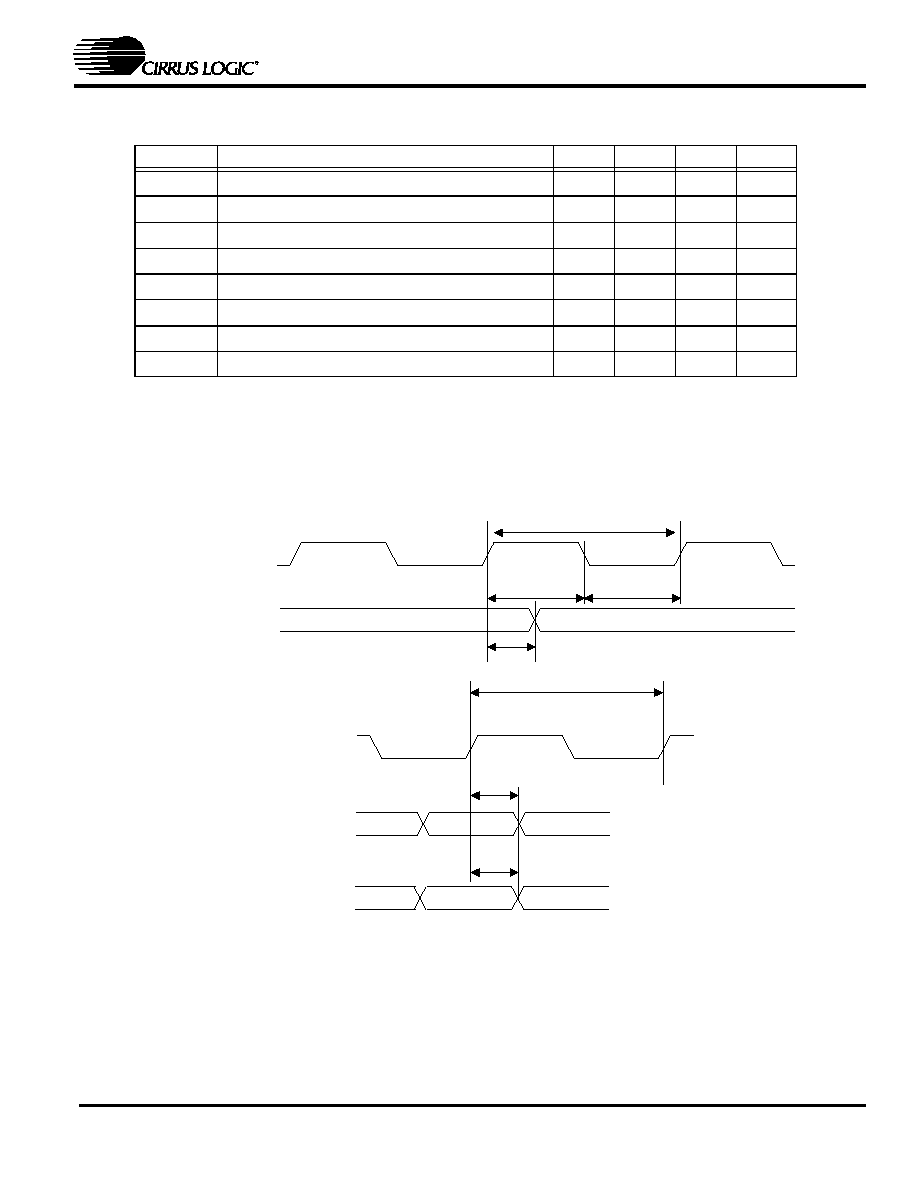

2.1

Timing Diagram Conventions

This data sheet contains timing diagrams. The following key explains the components used in

these diagrams. Any variations are clearly labeled when they occur. Therefore, no additional

meaning should be attached unless specifically stated.

C l o c k

H i g h t o L o w

H i g h / L o w t o H i g h

B u s C h a n g e

B u s V a l i d

U n d e f i n e d / I n v a l i d

V a l i d B u s t o T r i s t a t e

B u s / S i g n a l O m i s s i o n

Figure 1. Legend for Timing Diagrams

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

11

CS98200

Next Generation DVD Processor

2.2

DC CHARACTERISTICS

(

T

A

= 25� C; V

PLL

=V

DD

=1.8V�10%, V

IO

=V

AA

=3.3 V�10%)

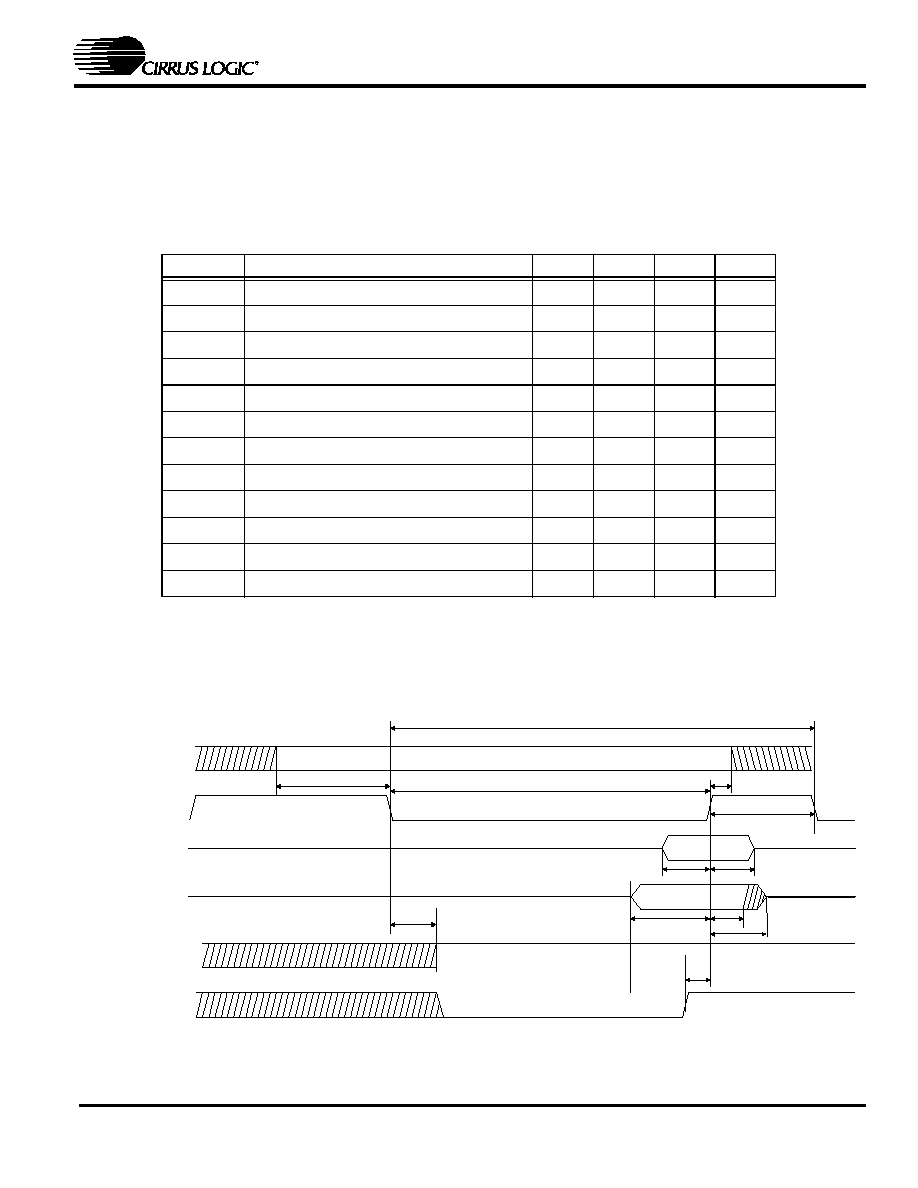

2.2.1

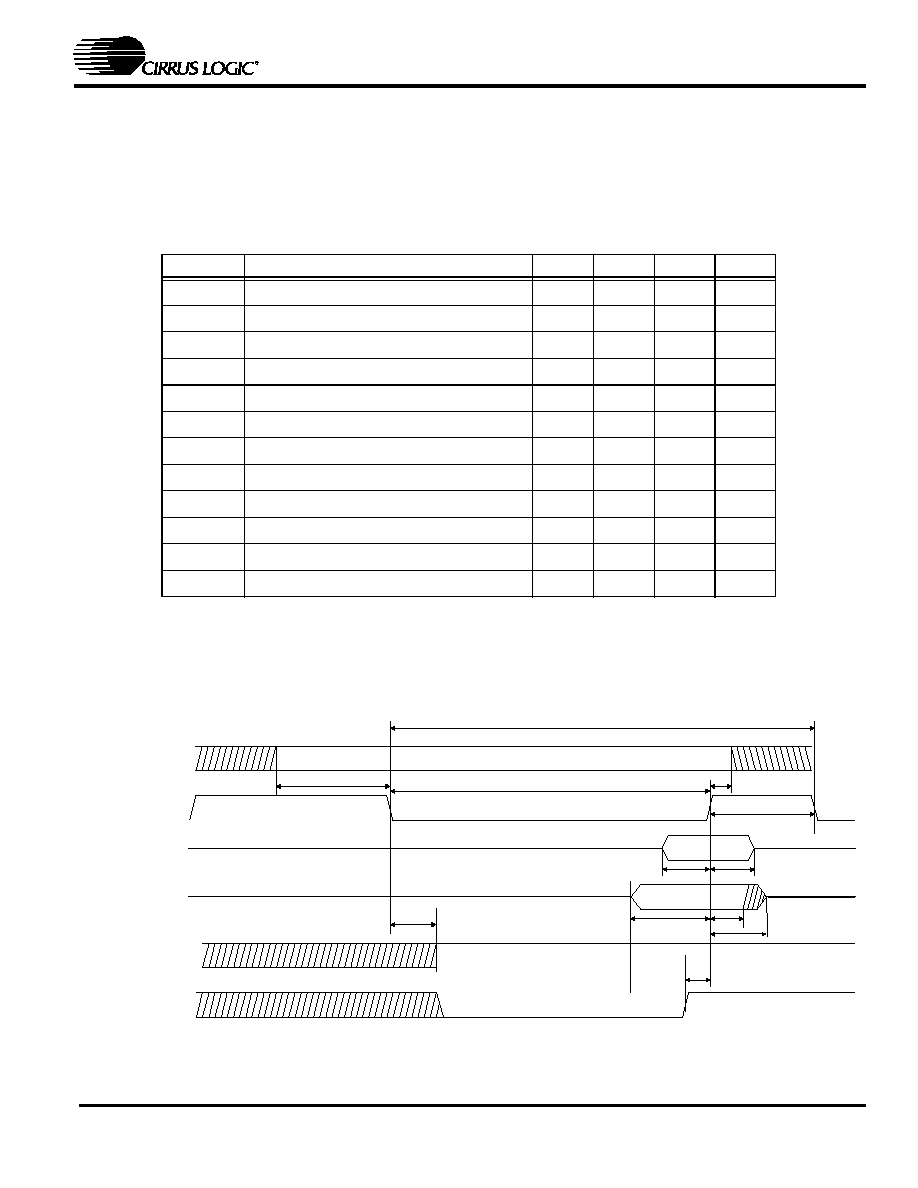

ATAPI Interface

CS98200 can interface with a ATAPI-type slave loader gluelessly.

Figure 2

illustrates a read ATAPI

transaction and a write ATAPI transaction.

Symbol

Description

Min

Typ

Max

Unit

t

acyc

1

1.

Values are guaranteed by design only

Cycle Time

87

ns

t

aavr

Address Valid to HMRD-/HMWR- Setup

7

ns

t

ah

Address Hold from HMRD-/HMWR Setup

11

ns

t

arww

H_RD/H_WR Pulse Width

63

ns

t

arec

H_RD/H_WR Recovery Time

21

ns

t

awsu

H_WR Data Setup

30

ns

t

awh

H_WR Data Hold

8

ns

t

ardsu

H_RD Data Setup

20

ns

t

arddh

H_RD Data hold

0

ns

t

ardts

H_RD Data High-Z-state

8

ns

t

arsu

H_RDY Setup Time

14

ns

t

arh

1

H_RDY Hold Time

0

ns

Table 1. ATAPI Interface Characteristics

H_A[2:0] ,

H_CS[3:0]

H_D[15:0](WRITE)

H_D[15:0](READ)

H_RD/H_WR

t

acyc

t

aavr

t

arww

t

ah

t

arec

t

arsu

t

awh

t

awsu

t

ardsu

t

arddh

t

ardts

t

arh

H_RDY(deasserted

before tarsu)

H_RDY(asserted

before tarsu)

Figure 2. ATAPI Interface Timing Diagram

12

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

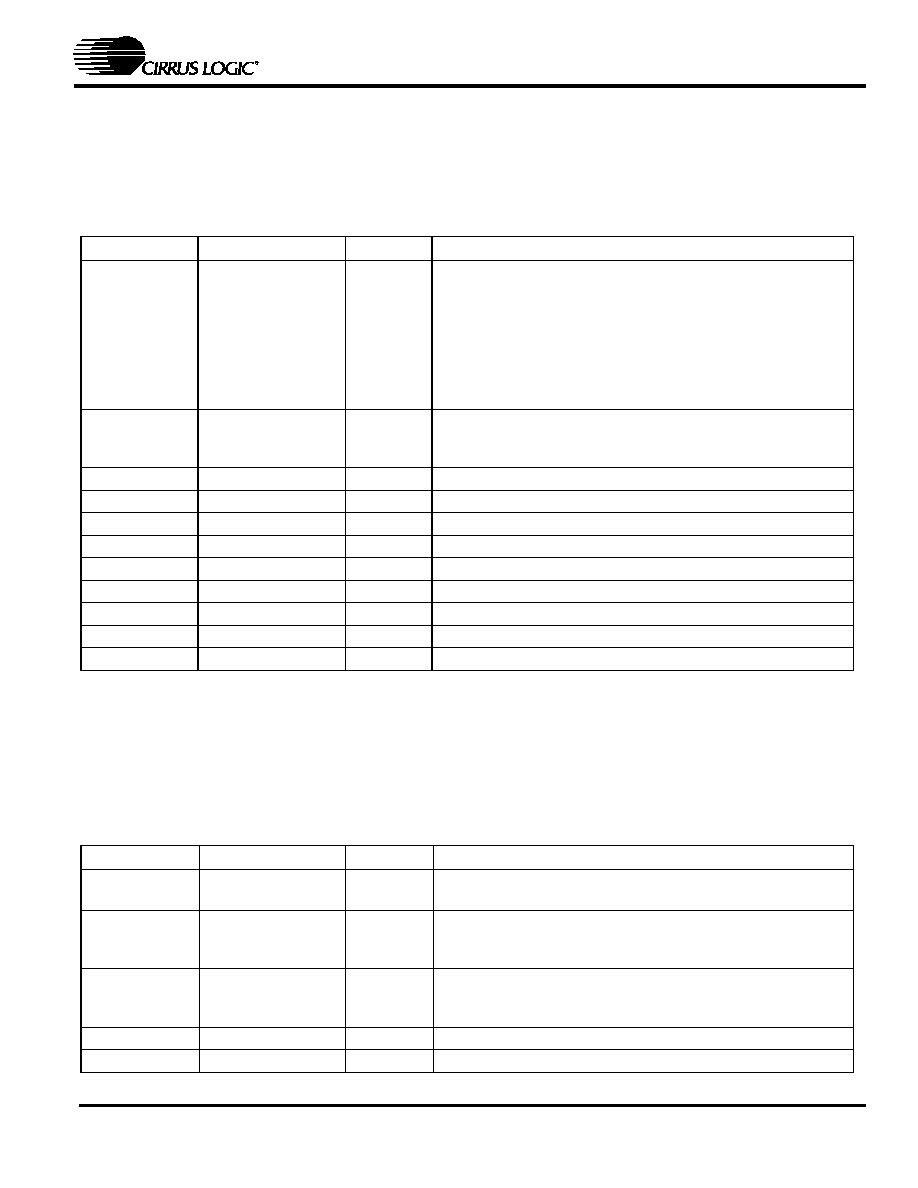

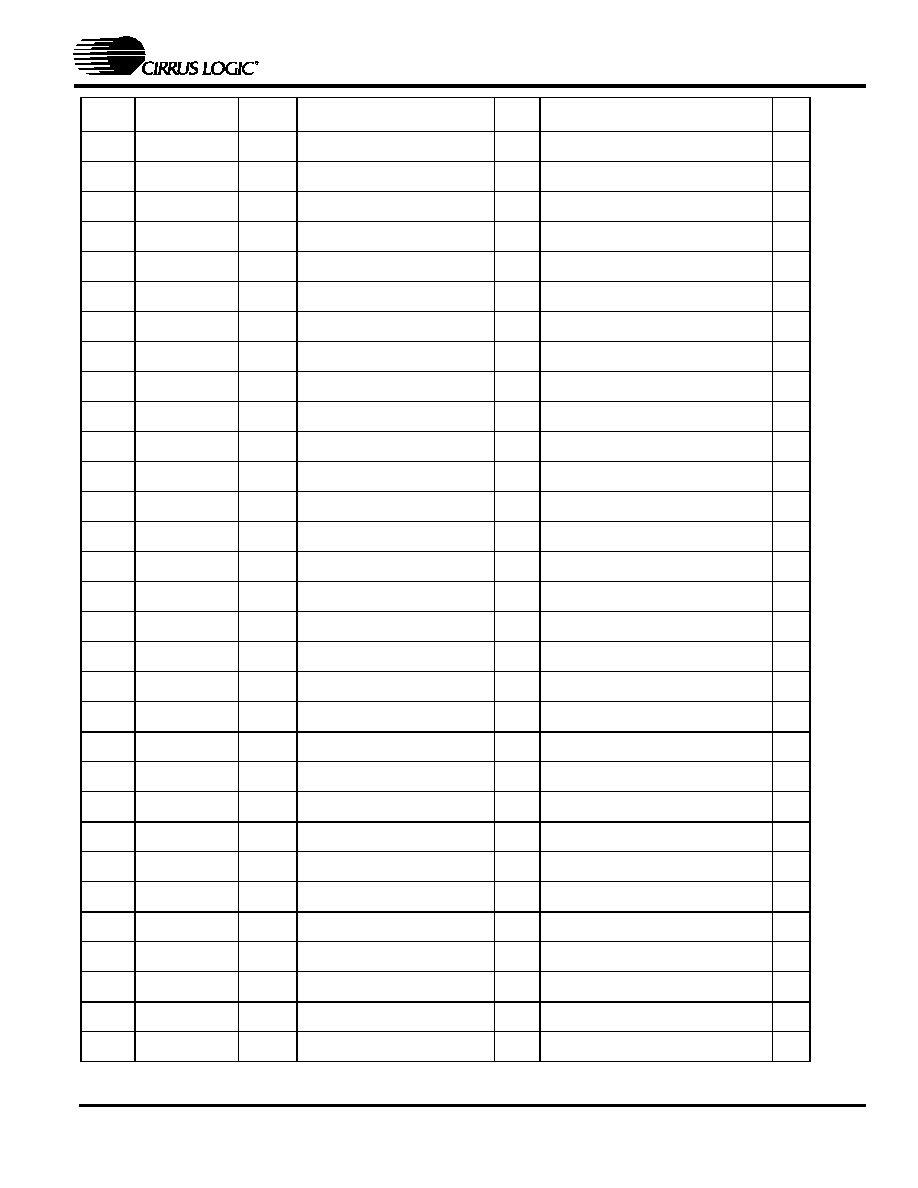

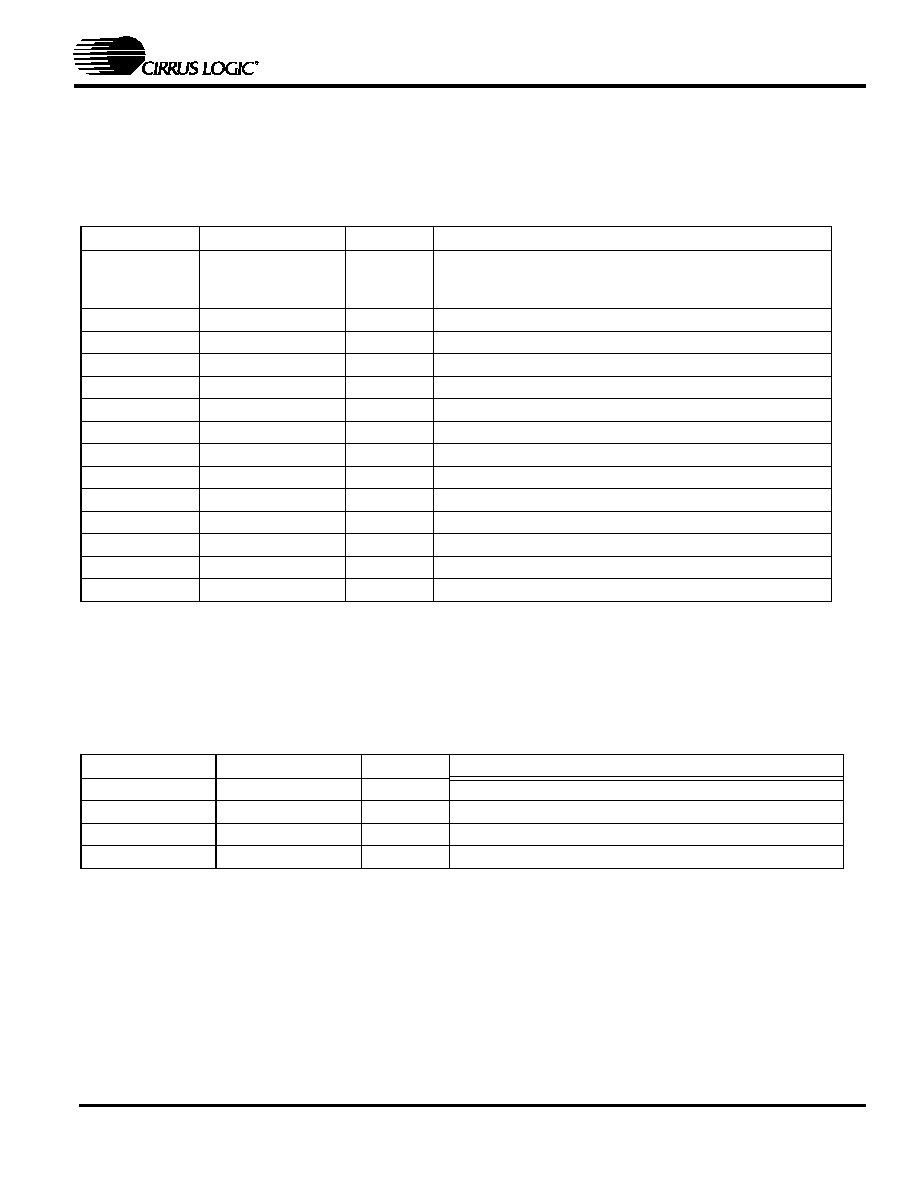

2.2.2

DVD Loader Interface

Symbol

Description

Min

Typ

Max

Unit

t

dlckper

DVDL_CK Period

400

ns

t

dldisu

DVDL_DI Setup Time

5

ns

t

dldih

DVDL_DI Hold Time

10

ns

t

dldod

DVDL_DO Output Delay from Falling

Edge

5

ns

t

dlstbwd

DVD_STB Width

250

ns

t

dlstbl

DVD_STB Low Time

40

%

t

dlstbh

DVD_STB High Time

40

%

t

dlreqod

DVD_RDY Output Delay

90

ns

t

dlensu

DVD_ENA Setup Time

5

ns

t

dlenh

DVD_ENA Hold Time

5

ns

t

dldsu

DVD_D[7:0] Setup Time

5

ns

t

dldh

DVD_D[7:0] Hold Time

5

ns

t

dlsossu

DVD_SOS Setup Time

5

ns

t

dlsosh

DVD_SOS Hold Time

5

ns

t

lrcksu

CD_LRCK Setup Time

5

ns

t

cddsu

CD_DATA Setup Time

5

ns

t

cddh

CD_DATA Hold Time

5

ns

t

cdcpsu

CD_C2PO Setup Time

5

ns

t

cdcph

CD_C2PO Hold Time

5

ns

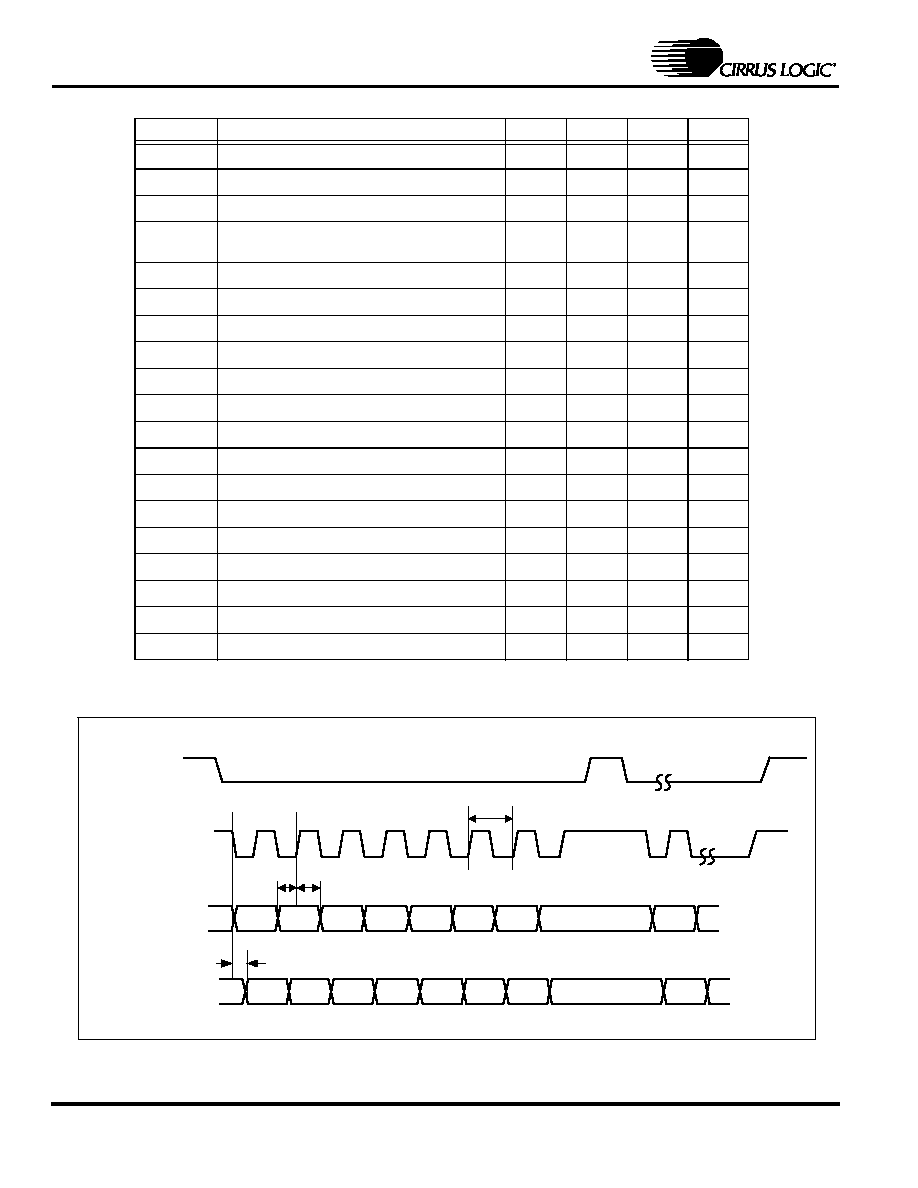

Figure 3. DVD Loader Host Interface

D VD L -C K

(O u tpu t)

D VD L _R D Y

(Inp ut)

D VD L _D I

(Inp ut)

D VD L _D O

(O u tpu t)

D 0

D 1

D 2

D 3

D 4

D 5

D 6

D 7

D 0

D 1

D 2

D 3

D 4

D 5

D 6

D 7

t

dlckper

t

dldisu

t

dldih

t

dldo d

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

13

CS98200

Next Generation DVD Processor

Figure 4. DVD Loader Data Interface

D V D _R E Q

(O utp u t)

D V D _S T B

(In p ut)

D V D _E N A

(In p ut)

D V D _D [7:0 ]

(In p ut)

D V D _S O S

(In p ut)

D V D _E R R

(In p ut)

t

d lstbw d

t

d lstbl

t

d lstbh

t

d lre qo d

t

d le nsu

t

d le nh

t

d ld su

t

d ld h

t

d lso ssu

t

d lso sh

Figure 5. DVD Loader CD Interface

C D _ B C LK (Inp ut)

C D _ D A T A (Inp ut)

C D _ L R C K (In p ut)

C D _ C 2P O (Inp ut)

t

lrcksu

t

cddsu

t

cddh

t

c2poh

t

c2posu

14

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

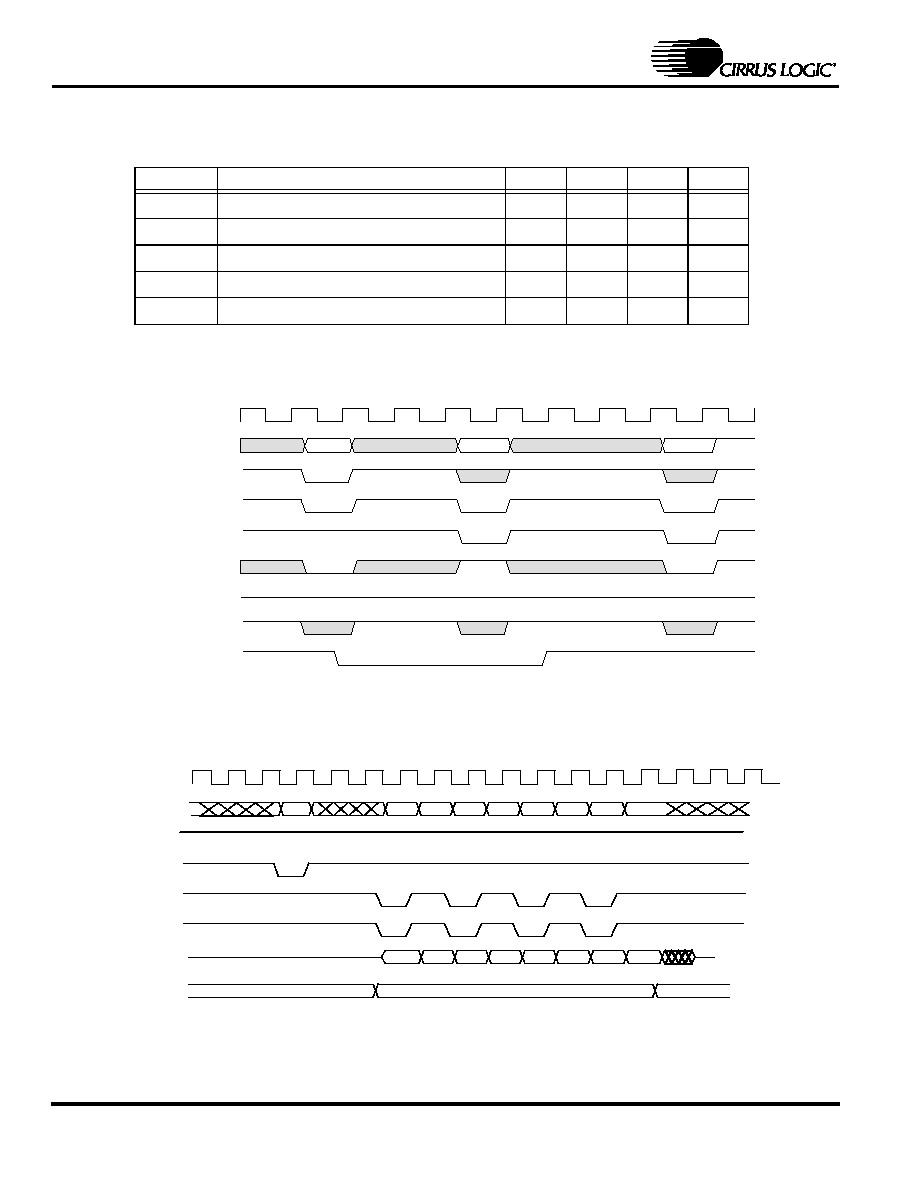

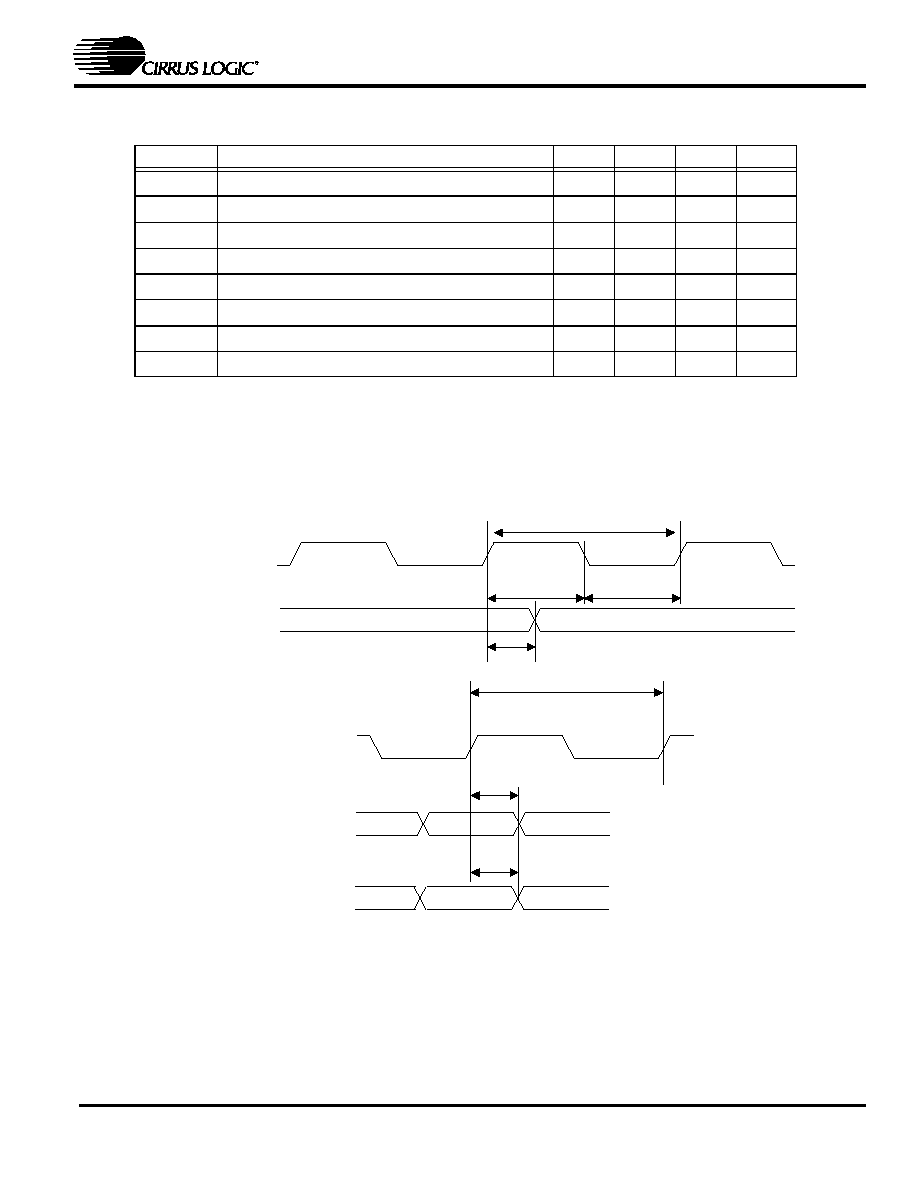

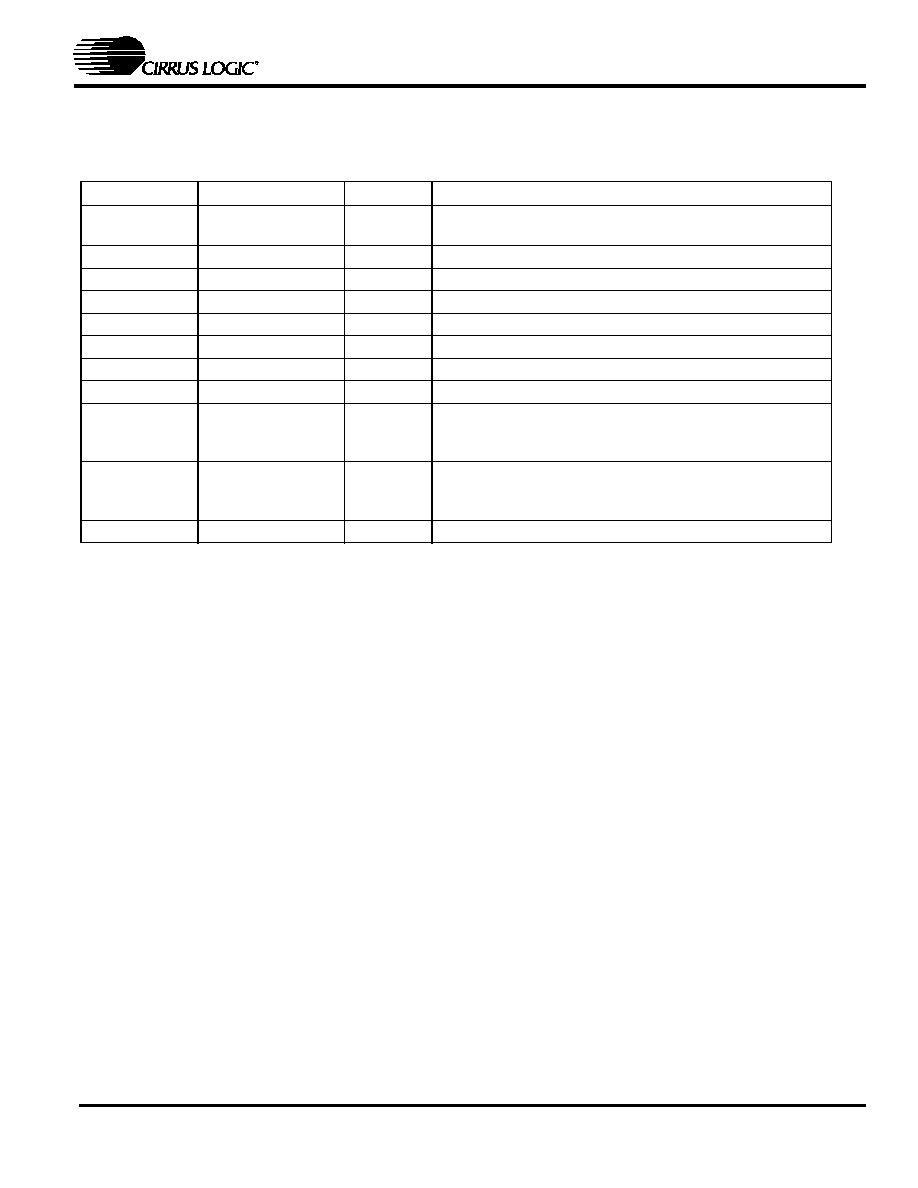

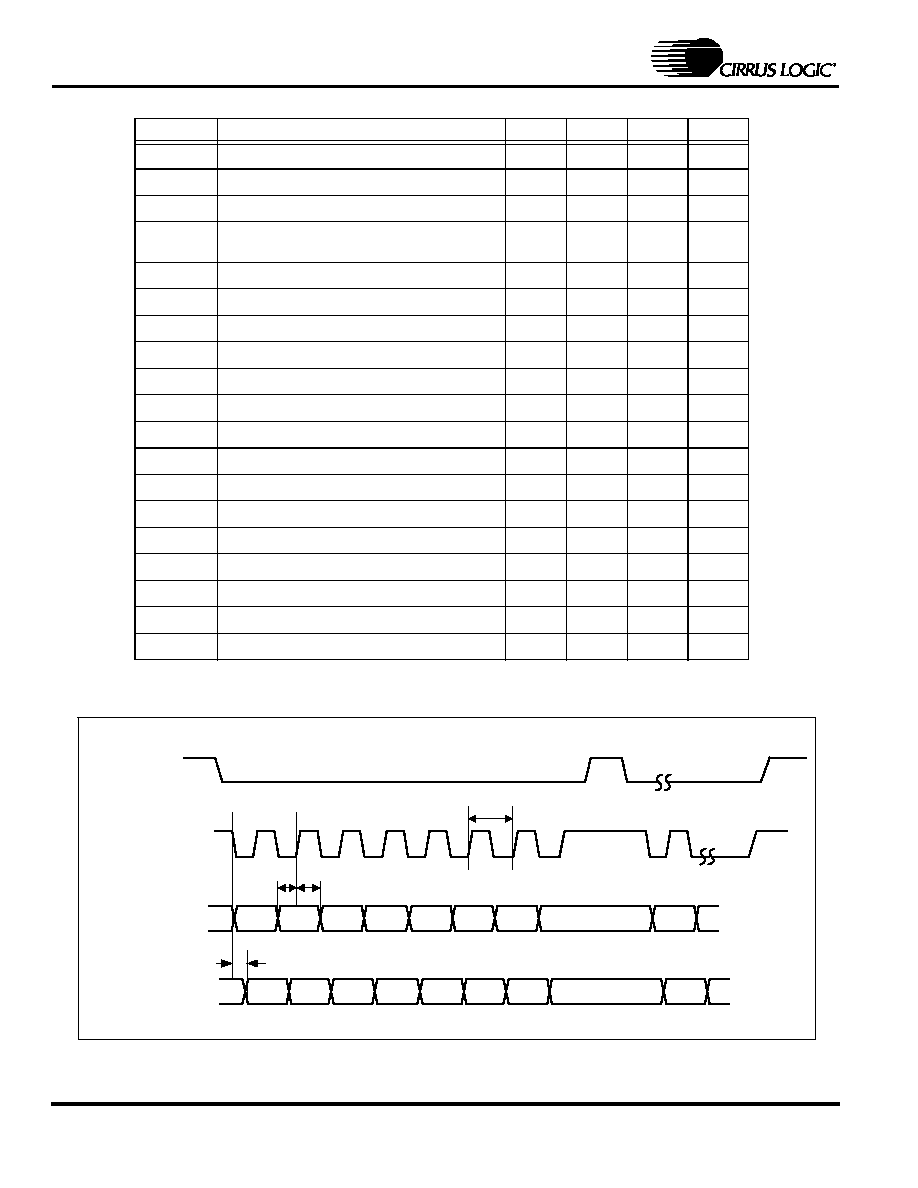

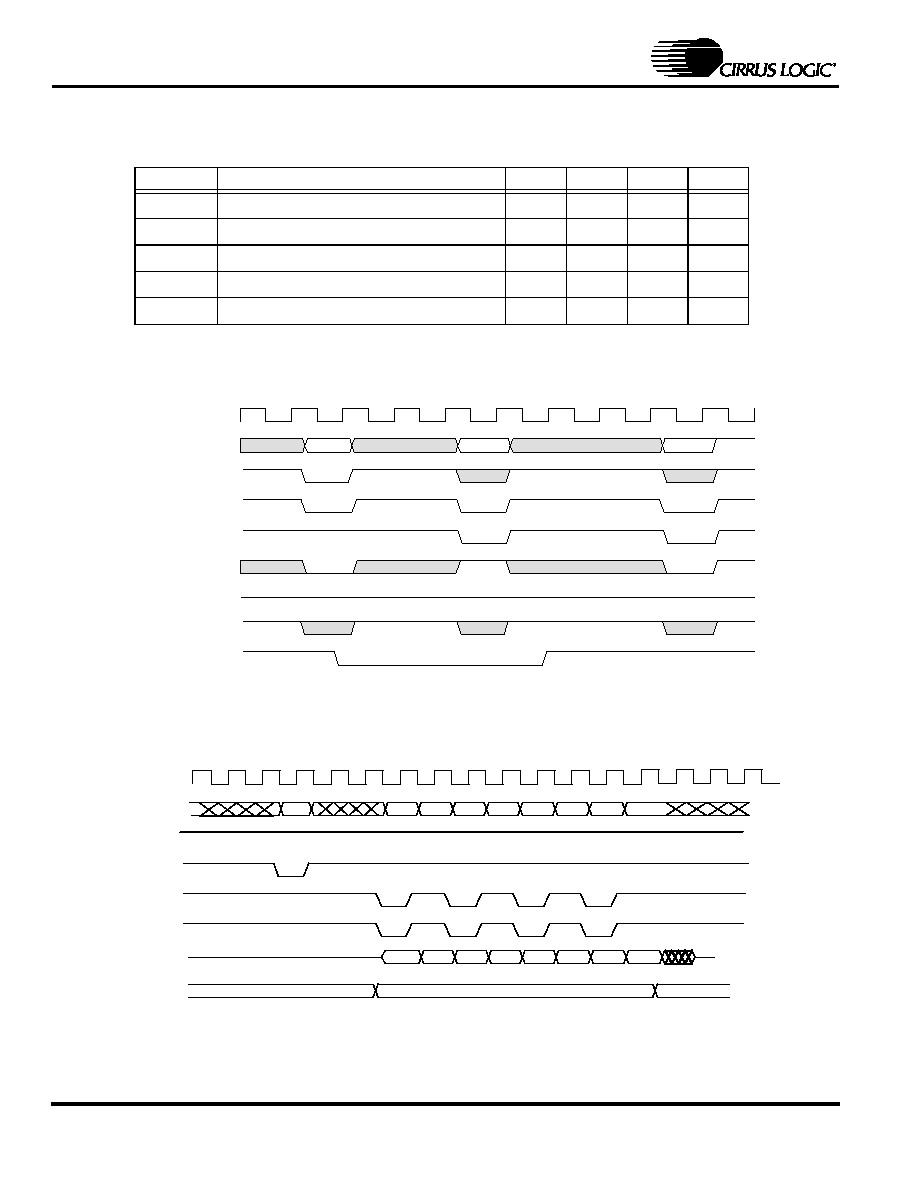

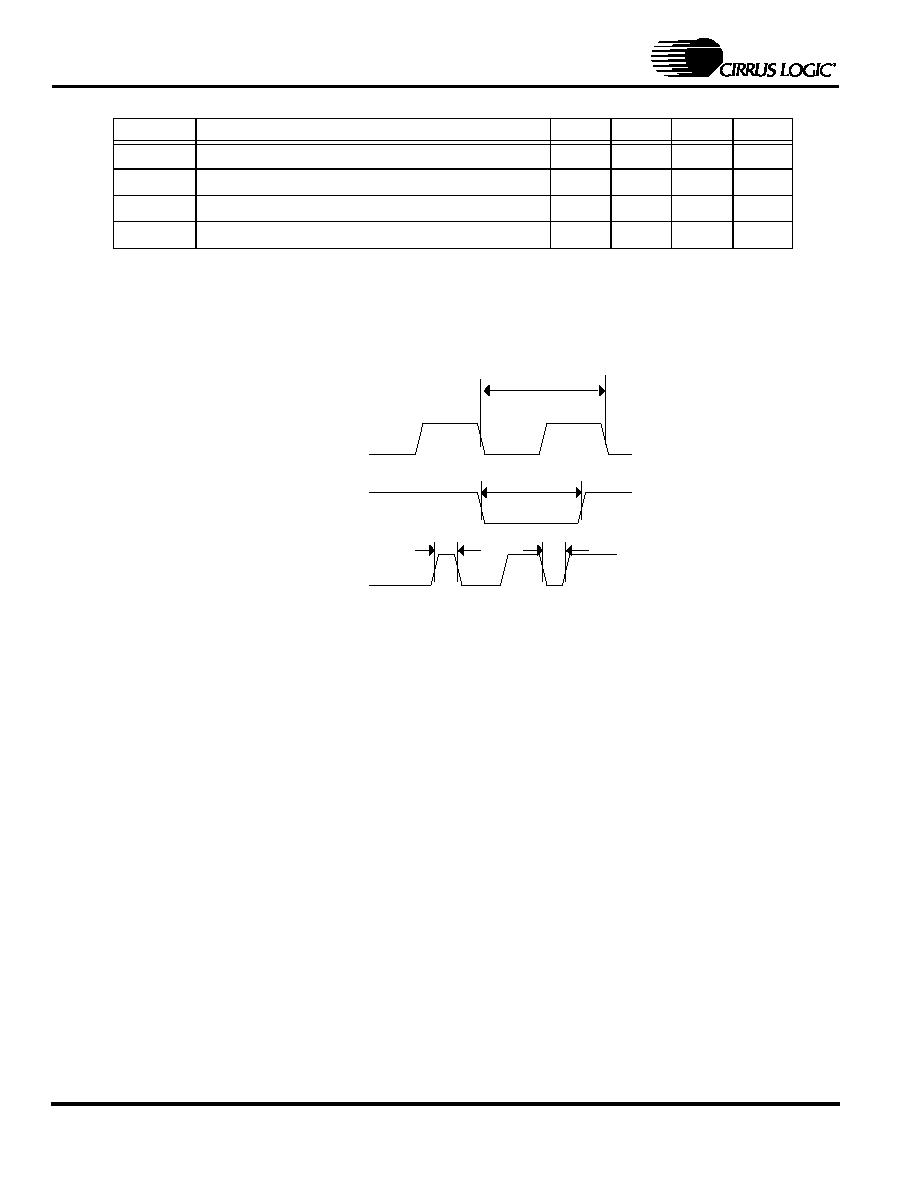

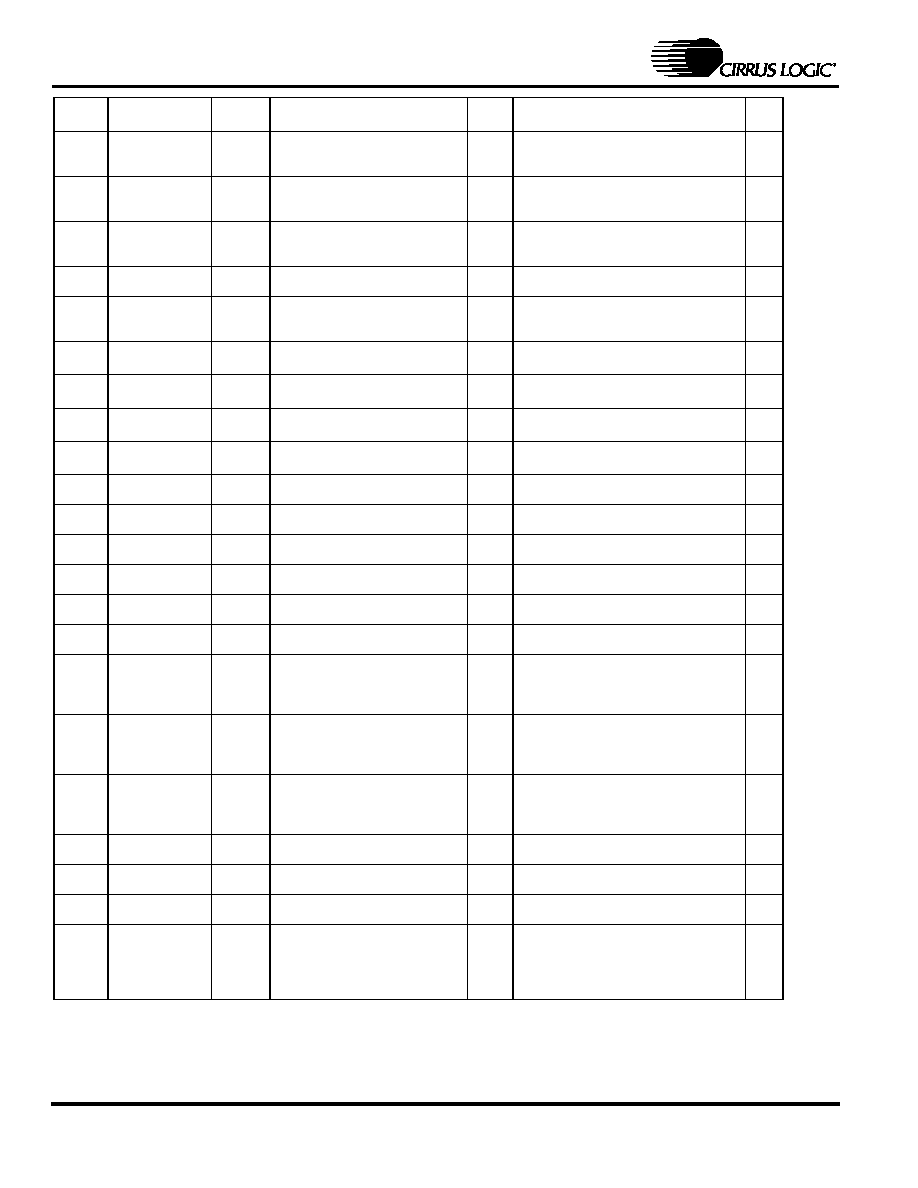

Figure 6. DVD Loader CD Interface Formats

15

0

1

C D _ B C K

C D _ LR C K

D A T A

C 2 P 0

14 13 12 11 10 9

8

7

6

5

4

3

2

Invalid

0

15

0

1

14 13 12 11 10 9

8

7

6

5

4

3

2

In va lid

M S B

LSB

MSB

LS B

Lo wer (L eft Channel)

Upper (Left Channe l)

Lower (Right Channel)

Uppe r (Righ t Channel)

32-bit B C K , MS B First, R ig ht C han nel L ow , C 2P 0 LS B F irst, D a ta latch tim ing high

15

0

1

C D _ B C K

C D _ LR C K

D A T A

C 2 P 0

14 13 12 11 10 9

8

7

6

5

4

3

2

Invalid

0

15

0

1

14 13 12 11 10 9

8

7

6

5

4

3

2

In va lid

M S B

LSB

MSB

LS B

Up per (Right Channel)

Lower (Right Chann el)

Upper (Left Channel)

Lower (Left Cha nnel)

32-bit B C K , MS B First, Left C hann el L ow , C 2P 0 MS B F irst, D a ta latch tim ing lo w

15

0

1

C D _ B C K

C D _ LR C K

D A T A

C 2 P 0

14 13 12 11 10 9

8

7

6

5

4

3

2

Invalid

0

M SB

LS B

Lower (Left Channel)

Upper (Left Channe l)

Lower (Right Chan nel)

Upper (Righ t Chan nel)

24-bit B C K , MS B First, R ig ht C han nel L ow , C 2P 0 M S B F irst, D ata la tc h tim ing high

Left Channel

Righ t Channel

Right Ch annel

Le ft Channel

Left Channel

Righ t Channel

15

0

1

14 13 12 11 10 9

8

7

6

5

4

3

2

In va lid

M SB

LS B

15 14 13 12 11 10 9

8

7

6

5

Invalid

MSB

Upper (Left Channel)

Left Channel

C D _ B C K

C D _ LR C K

D A T A

C 2 P 0

Invalid

0

L SB

M SB

Lower (Left Channel)

Upper (Left Channe l)

Lower (Right Chan nel)

Upper (Righ t Chan nel)

24-bit B C K , LS B F irst, R ight C hann el L ow , C 2P 0 MS B F irst, D a ta latch tim ing lo w

Left Channel

Righ t Channel

In va lid

LSB

MS B

Invalid

LSB

Upper (Left Channel)

Left Channel

0

15

1

14

13

1 2

11

10

9

8

7

6

5

4

3

2

0

15

1

14

13

12

11

10

9

8

7

6

5

4

3

2

0

1

10

9

8

7

6

5

4

3

2

15

0

1

C D _ B C K

C D _ LR C K

D A T A

14 13 12 11 10 9

8

7

6

5

4

3

2

Invalid

0

M SB

LS B

2 4-bit B C K , M S B F irst, R ight C hanne l Low , D a ta latch tim ing high (N ote: no C 2P 0 for this fo r m at)

Left Channel

Righ t Channel

15

0

1

14 13 12 11 10 9

8

7

6

5

4

3

2

In va lid

M SB

LS B

15 14 13 12 11 10 9

8

7

6

5

Invalid

MSB

Left Channel

15

0

1

C D _ B C K

C D _ LR C K

D A T A

C 2 P 0

14 13 12 11 10 9

8

7

6

5

4

3

2

0

MS B

LSB

Lower (Left Cha nnel)

Upper (Left Channel)

Lower (Right Channel)

Upper (Right Channel)

16-bit B C K , MS B First, Left C hann el L ow , C 2P 0 LS B Firs t, D ata la tch ti m in g high

Left Ch annel

Right Channel

15

0

1

14 13 12 11 10 9

8

7

6

5

4

3

2

M S B

L SB

15

0

1

14 13 12 11 10 9

8

7

6

5

4

3

2

M SB

L SB

Lower (Left Channel)

Upper (Left Channel)

Lower (Right Chan nel)

Upper (Right Chan nel)

Left Ch annel

Righ t Chan nel

15

0

1

14 13 12 11 10 9

8

7

6

5

4

3

2

MSB

LSB

15 14 13

MSB

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

15

CS98200

Next Generation DVD Processor

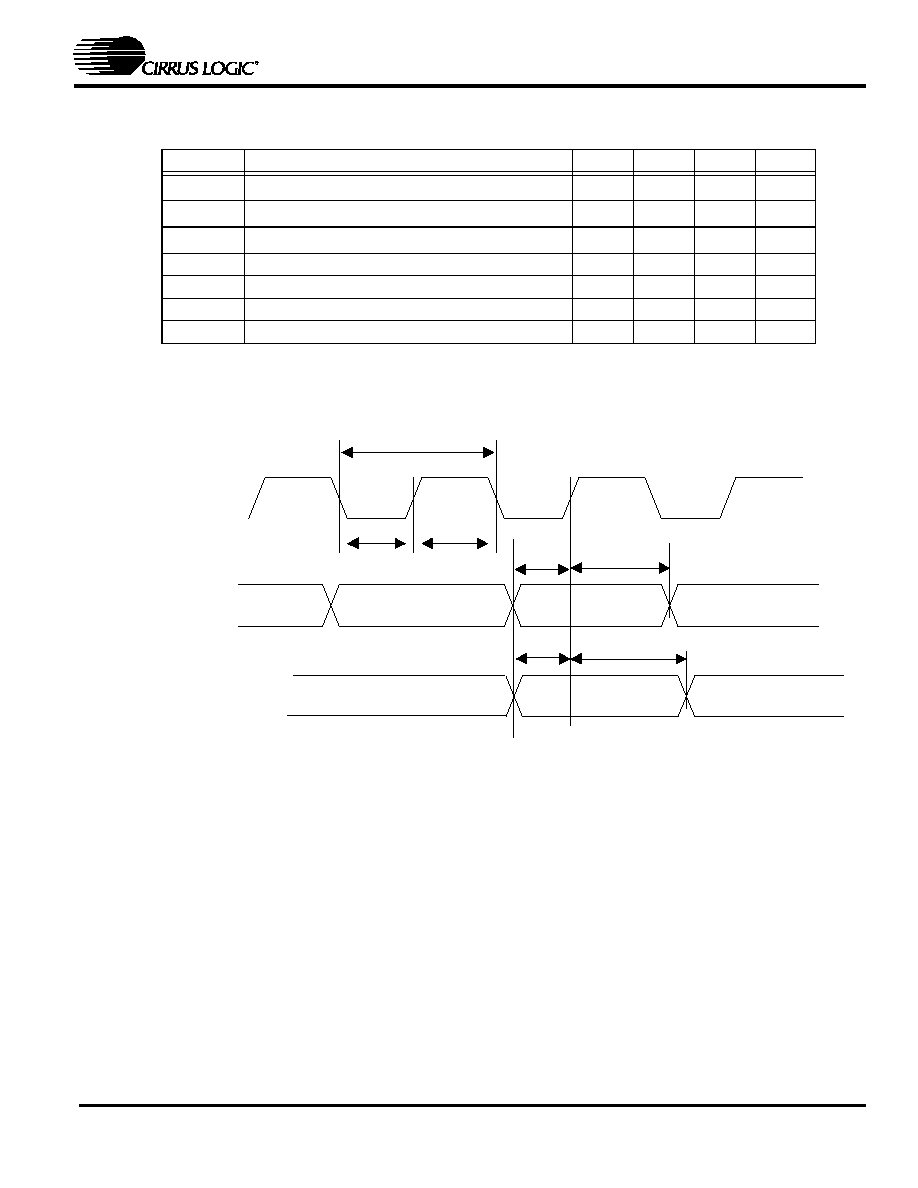

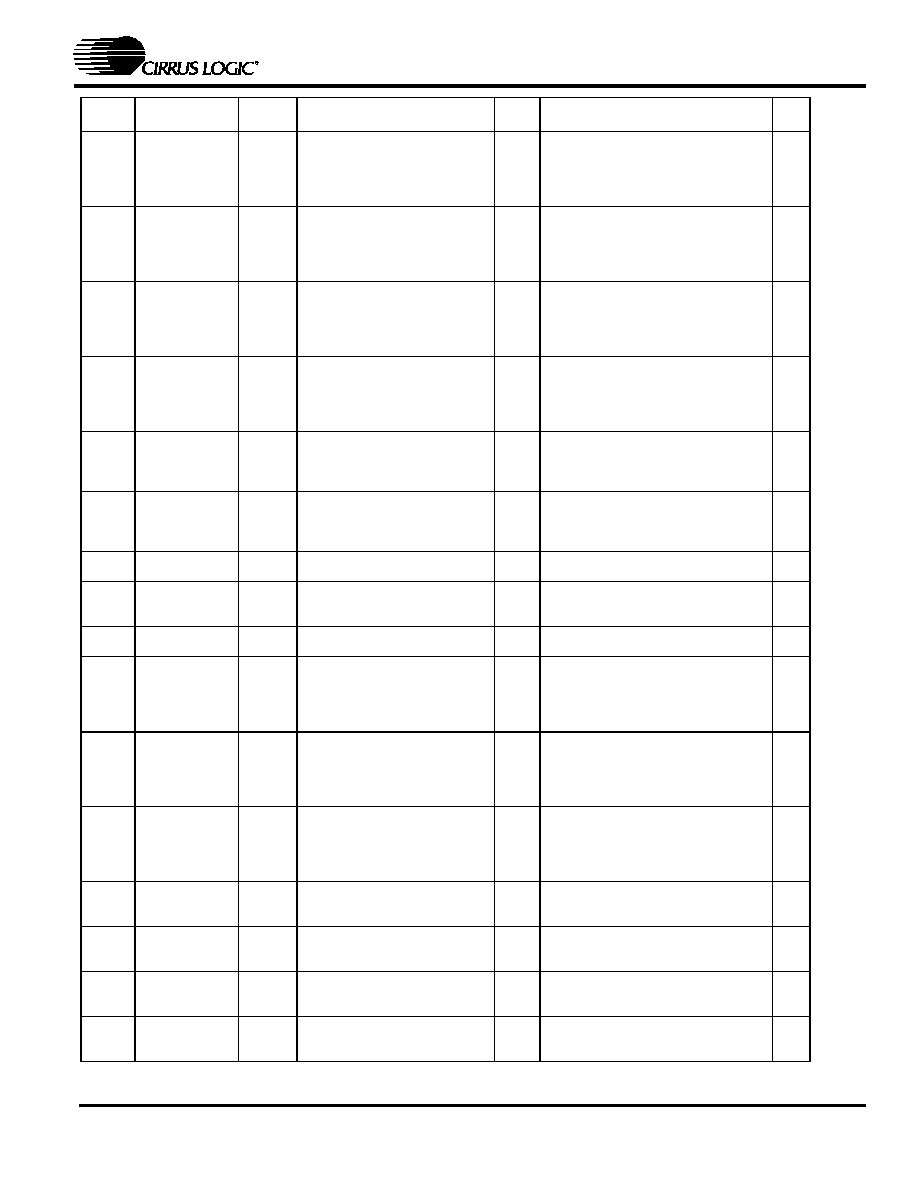

2.2.3

DVD Serial Interface Timing

Symbol

Description

Min

Typ

Max

Unit

tdsckper

1

DVDS_CLK Period

33

ns

tdsckl

1

DVDS_CLK Low Time

40

50

%

tdsckh

1

DVDS_CLK High Time

40

50

%

tdsdsu

DVDS_DATA Setup to DVDS_CLK active edge

5

ns

tdsdhd

DVDS_DATA Hold after DVDS_CLK active edge 5

ns

tdscdsu

DVDS_VLD, DVDS_SOS Setup to DVDS_CLK

5

ns

tdscdhd

DVDS_VLD, DVDS_SOS Hold after DVDS_CLK 5

ns

1.

Values are guaranteed by design only

Figure 7. DVD Serial Interface Timing

D V D S_C L K

(Input)

D V D S_D A T A

(Input)

D V D S_V L D , D V D S_S O S

(Input)

dsckl

dsckh

dsdhd

dscdhd

dsckper

t

t

t

t

dsdsu

t

dscdsu

t

t

16

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

2.2.4

SDRAM Interface

CS98200 interfaces with either SDRAM or SGRAM for high data bandwidth transfer.

Figure 8

shows

the refresh cycle performed by CS98200.

Symbol

Description

Min

Typ

Max

Unit

t

mco

Output Delay from M_CKO active edge

9

ns

t

mper

M_CKO Period

8

ns

t

mdow

M_D[31:0] delay from M_CKO

9

ns

t

msur

M_D[31:0] setup to M_CKO

3

ns

t

mhr

M_D[31:0] hold time after M_CKO

2.5

ns

Table 2. SDRAM Interface Characteristics

M_CKO

M_A[10:0]

M_BS0_N,

M_RAS_N

M_CAS_N

M_W E_N

M_D[31:0]

M_DQM_[3:0]

M_AP

M_BS1_N

Figure 8. SDRAM Refresh Transaction

D 0

D 1

D 2

D 3

D 4

D 5

D 6

D 7

C 1

C 2

C 3

C 4

C 5

C 6

C 7

C 0

R 0

M _ C KO

M _ A_ [1 0:0]

M _ C KE

M _ R AS _N

M _ C AS _N

M _ W E_ N

M _ D [3 1:0]

M _ D Q M [3:0]

0

F

F

Figure 9. SDRAM Burst Write Transaction

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

17

CS98200

Next Generation DVD Processor

D 0

D 1

D 2

D 3

D 4

D 5

D 6

D 7

C 1

C 2

C 3

C 4

C 5

C 6

C 7

C 0

R 0

M _ C KO

M _ A_ [1 0:0]

M _ C KE

M _ R AS _N

M _ C AS _N

M _ W E_ N

M _ D [3 1:0]

M _ D Q M [3:0]

0

F

F

Figure 10. SDRAM Burst Read Transaction

M_RAS_N,M_CAS_N

M_WE_N,M_AP,M_DQM[3:0],

M_CKE,M_A[10:0]

t

mper

t

mco

M_D[31:0](WRITE)

M_D[31:0](READ)

M_CKO

t

msur

t

mhr

t

mdow

Figure 11. SDRAM Timing

18

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

2.2.5

ROM/NVRAM Interface

Symbol

Description

Min

Typ

Max

Unit

t

rc

Read Cycle Time

75

ns

t

cds

CE to Data Setup

80

ns

t

ods

OE to Data Setup

70

ns

t

ads

Address to Data Setup

80

ns

t

aws

Address to WE setup (Write)

64

ns

t

cws

CE to WE setup (Write)

64

ns

t

wp

WE Pulse Width (Write)

160

ns

t

cdo

CE to Data Output (Write)

0

ns

t

dh

WE to Data Hold (Write)

10

ns

Table 3. RAM/NVROM Characteristics

Figure 12. ROM/NVRAM Reading Timing

N V_C E_N

N V_W E_N

N V_O E_N

(M _A P)

A ddress[22:0]

M _D [7:0]

t

rc

t

ads

t

cds

t

ods

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

19

CS98200

Next Generation DVD Processor

N V _ C E _ N

N V _ W E _ N

N V _ O E _ N

(M _ A P )

A d d r[2 2 :0 ]

M _ D [7 :0 ]

t

aw s

t

cw s

t

w dh

t

w p

t

cdo

Figure 13. ROM/NVRAM Write Timing

20

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

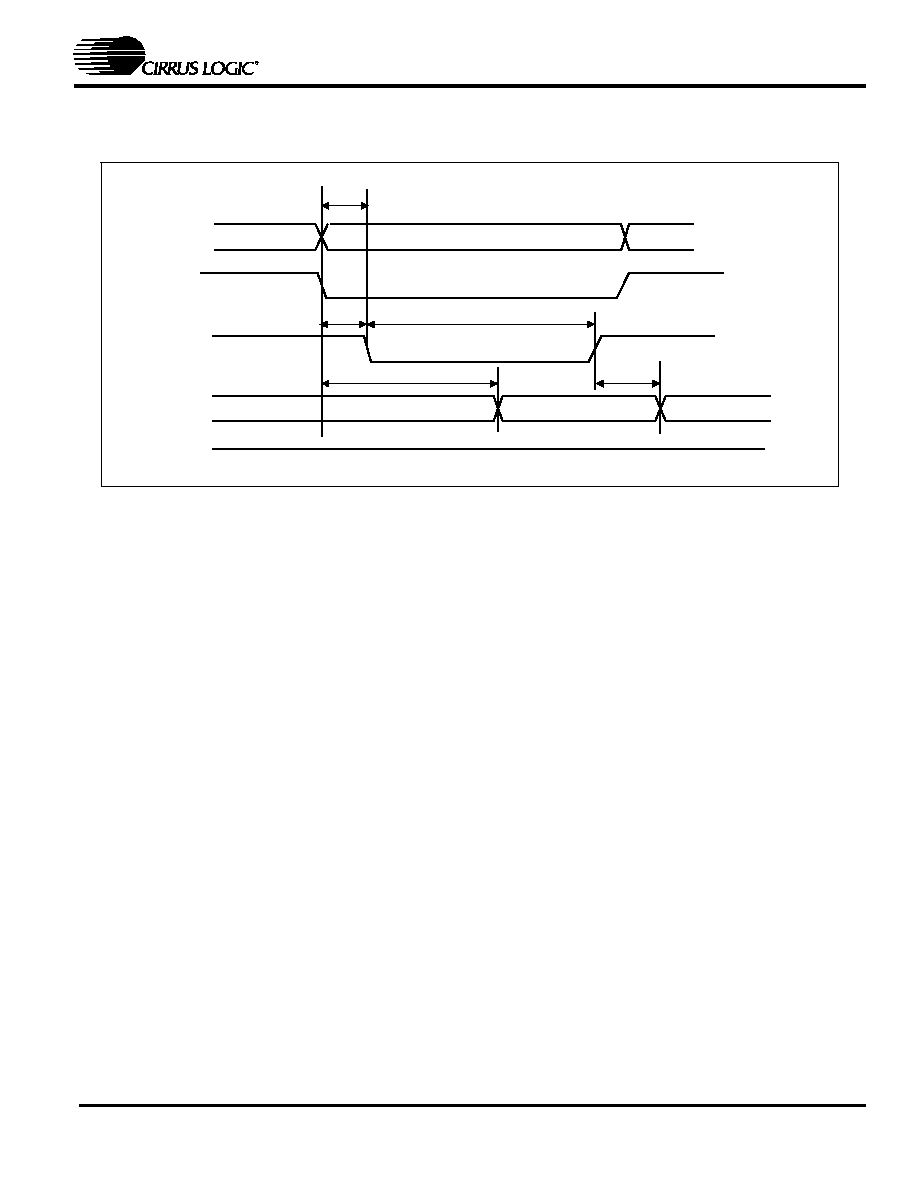

2.2.6

Digital Video Output Interface

Figure 14

illustrates the signal timing for the digital video interface pins.

Symbol

Description

Min

Typ

Max

Unit

t

vocper

1

1.

Values are guaranteed by design only

XTLCLK period

37.037

ns

t

covo1

2

2.

It is recommanded that the output data should be taken at the opposite edge of the CLK27_O.

VDAT[7:0] delay from XTLCLK

-10

10

ns

t

covo2

2

Vsync/Hsync delay from XTLCLK

-10

10

ns

Table 4. CS98200 Digital Video Interface Characteristics

V o u t_ C L K

(O u tp u t)

V o u t_ D 7:0 ]

(O u tp u t)

V o u t_ H S /V o u t_V S

(O u tp u t)

t

vocper

t

covo1

t

covo2

Figure 14. CS98200 Digital Video Interface Timing Diagram

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

21

CS98200

Next Generation DVD Processor

2.2.7

Video Input Interface

.

Symbol

Description

Min

Typ

Max

Unit

t

vicper

Video Clock input period

37.037

ns

t

sutc1

VIN_D[7:0] setup time

5

ns

t

hvi

VIN_D[7:0] hold time

5

ns

t

sutc2

VIN_HS/VS setup time

5

ns

Table 5. Video Input Interface Symbols and Characterization Data

V IN _C L K

V IN _D [7 -0 ]

t

sutc1

t

hvi

t

vicper

V IN _H S ,V IN _ VS

t

sutc2

Figure 15. Video Input Timing

22

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

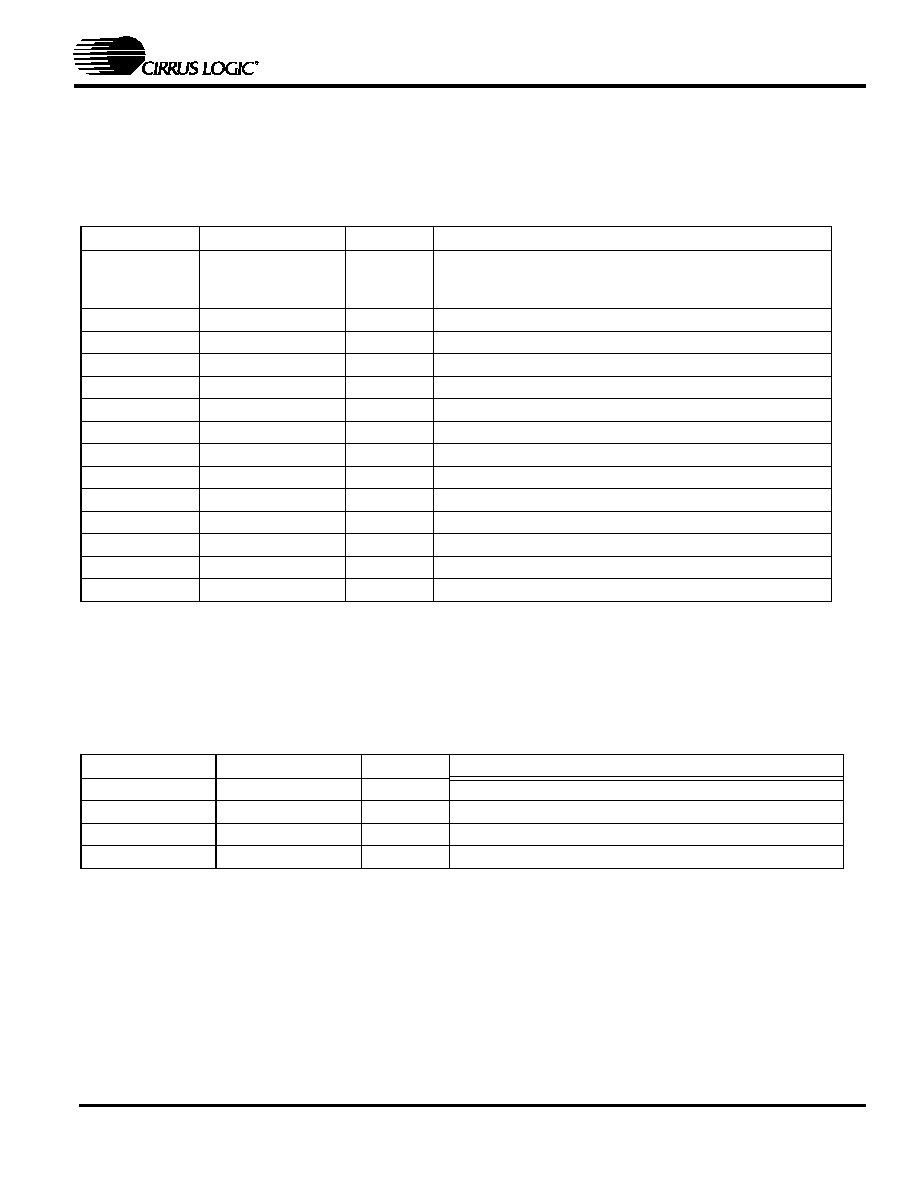

2.2.8

Audio Input Interface Timing

Symbol

Description

Min

Typ

Max

Units

t

aicl

AUDI_BCK Low Time

1,

2

1.

Values are guaranteed by design only

2.

Active clock edge is programmable. Timing is referenced from active edge

40

50

%

t

aich

AUDI_BCK High Time

1, 2

40

50

%

t

aiper

AUDI_BCK period

1, 2

80

ns

t

lrts

AUDI_LR setup time

5

-

ns

t

sdsus

AUDI_D setup time

5

-

ns

t

sdhs

AUDI_D hold time

5

-

ns

Table 6. Audio Input Interface Symbols and Characterization Data

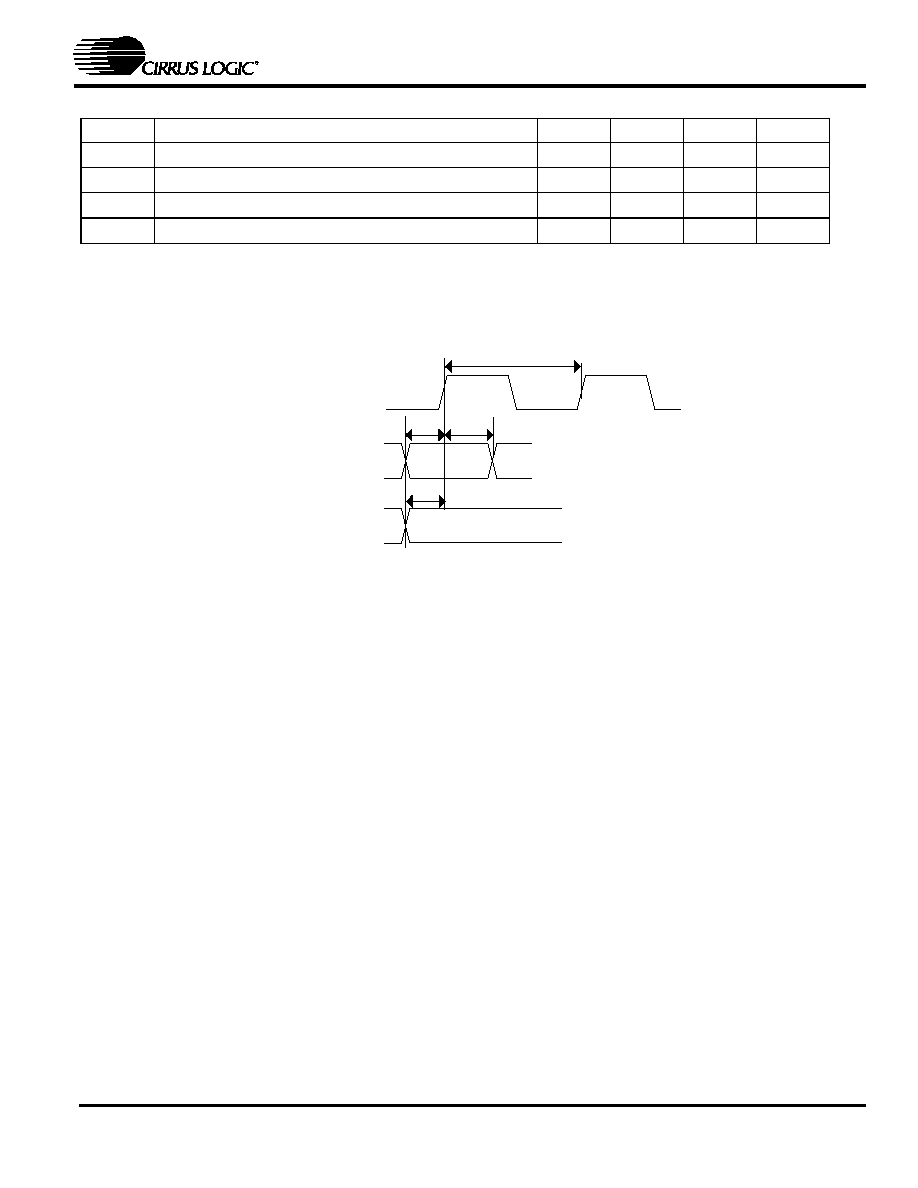

Figure 16. Audio Input Timings

AUDI_BCK (Input)

AUDI_DATA (Input)

AUDI_LRCK (Input)

t

lrts

t

sdsus

t

sdhs

t

aich

t

aicl

t

aiper

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

23

CS98200

Next Generation DVD Processor

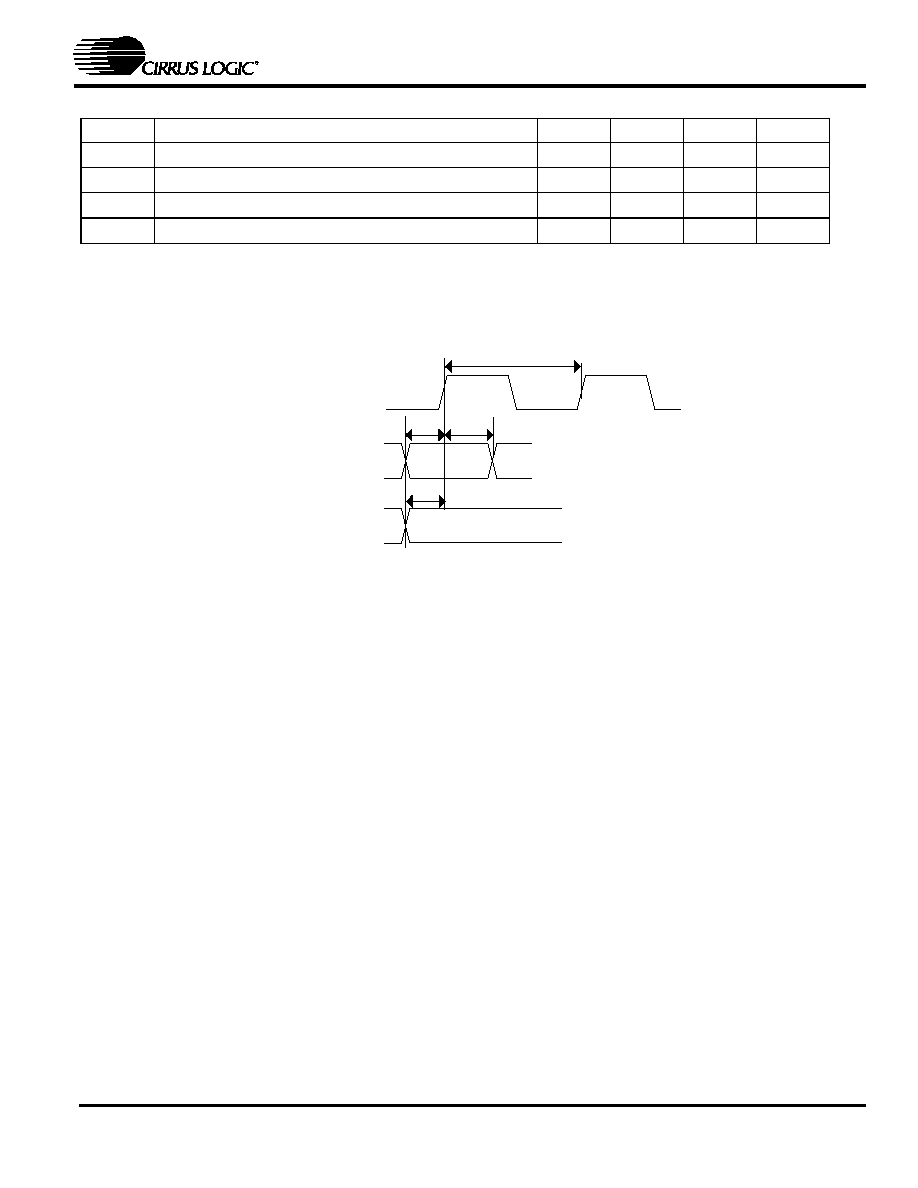

2.2.9

Audio Output Interface Timing

Figure 17

and

Figure 16

illustrate the signal timing for the digital audio pins.

Symbol

Description

Min

Typ

Max

Unit

t

axper

AUD_XCLK period (Input/Output)

1, 2

13

-

ns

t

axch

AUD_XCLK High Time (Input/Output)

1,

2

1.

Values are guaranteed by design only

2.

Active clock edge is programmable. Timing is referenced from active edge

40

50

%

t

axcl

AUD_XCLK Low Time (Input/Output)

1, 2

47

50

%

t

sdmo

AUDO_BCK delay from AUD_XCLK output rise

10

t

sdmi

AUDO_BCK delay from AUD_XCLK input rise

20

t

aoper

AUDO_BCK period (Output)

1, 2

104

t

lrds

AUDO_LR delay from AUDO_BCK output rise

-10

10

ns

t

adsm

AUDO_D[3:0] delay from AUDO_BCK output rise -10

10

ns

Table 7. Digital Audio Out Characteristics

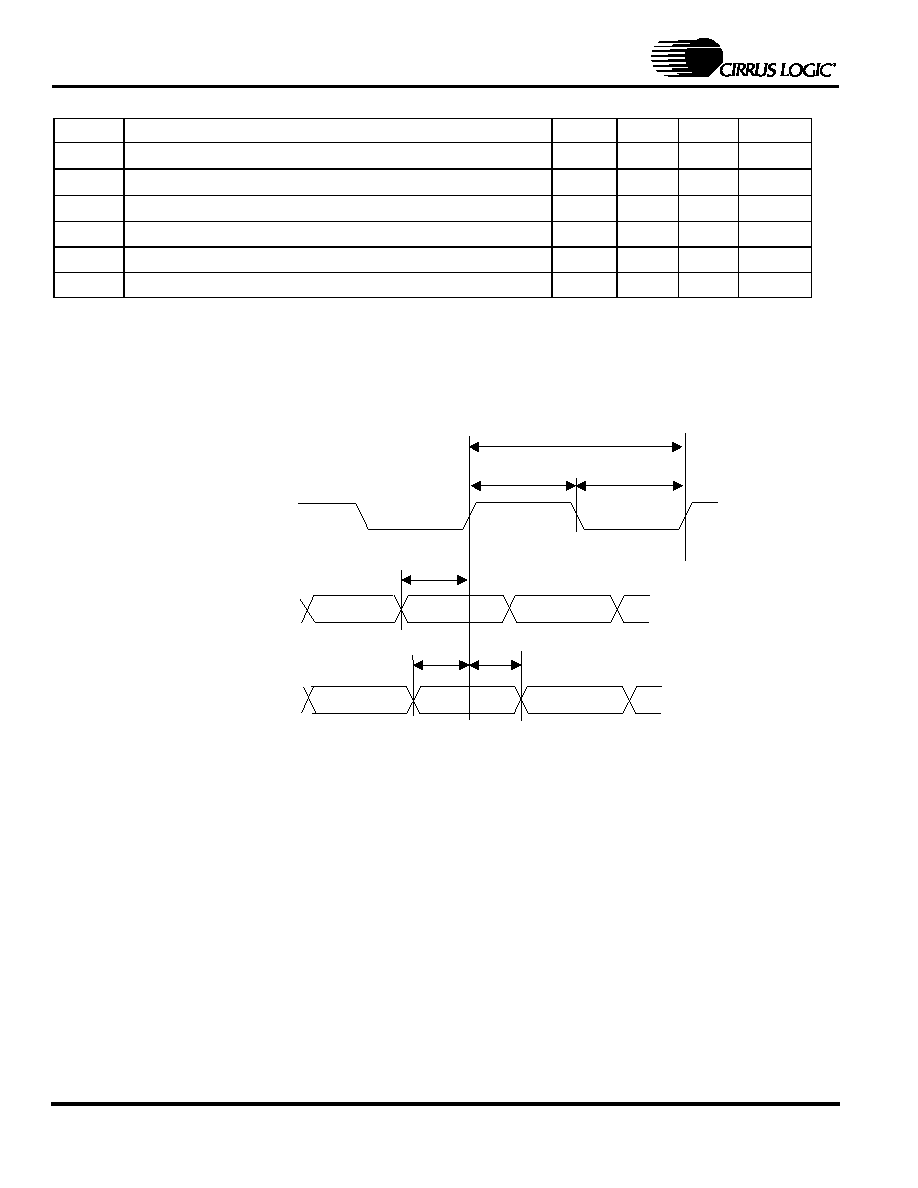

Figure 17. Digital Audio Out Timing Diagram

AUDO_BCK(Output)

AUD_XCLK(Input/Output)

t

sdm

t

axch

AUDO_BCK(Output)

AUDO_DO[3:0] (Output)

AUDO_LR(Output)

t

lrds

t

adsm

t

axcl

t

axper

t

aoperl

24

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

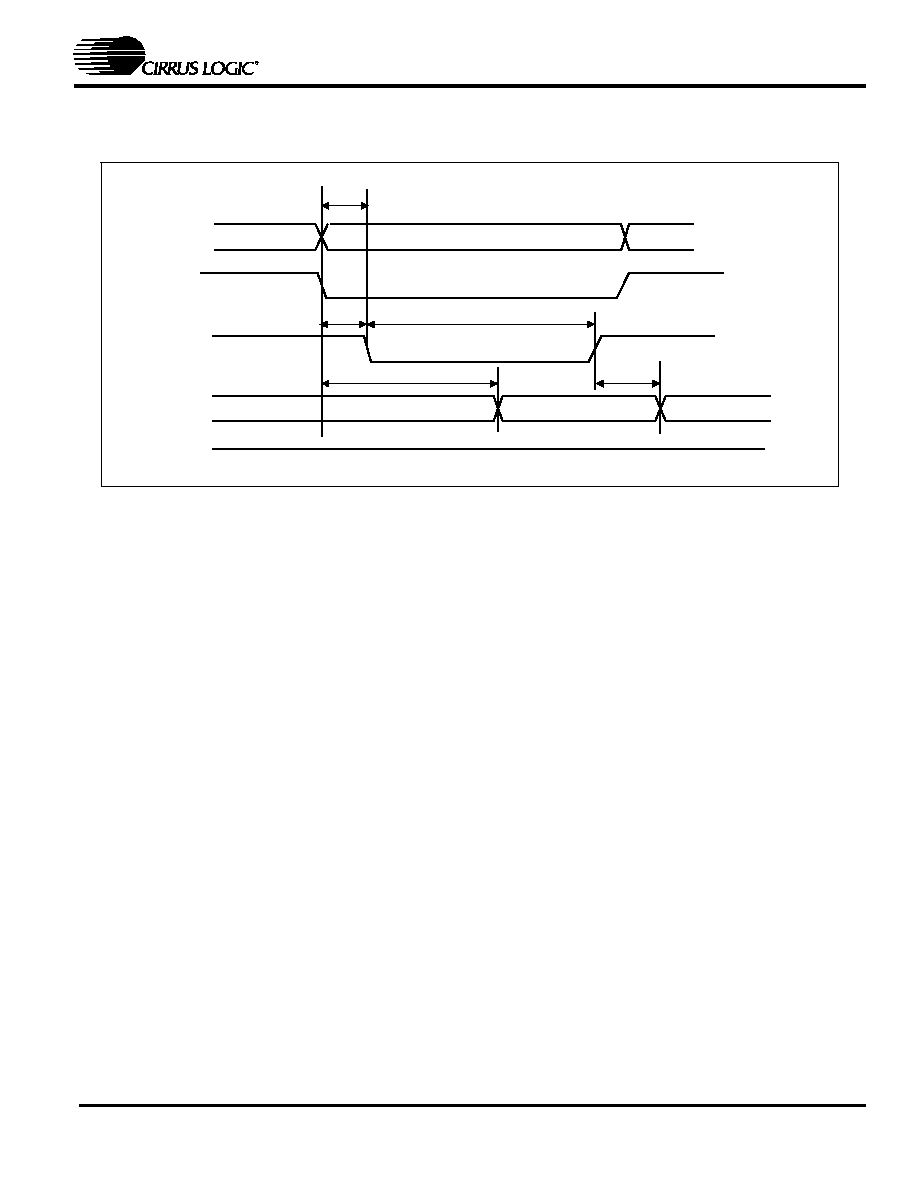

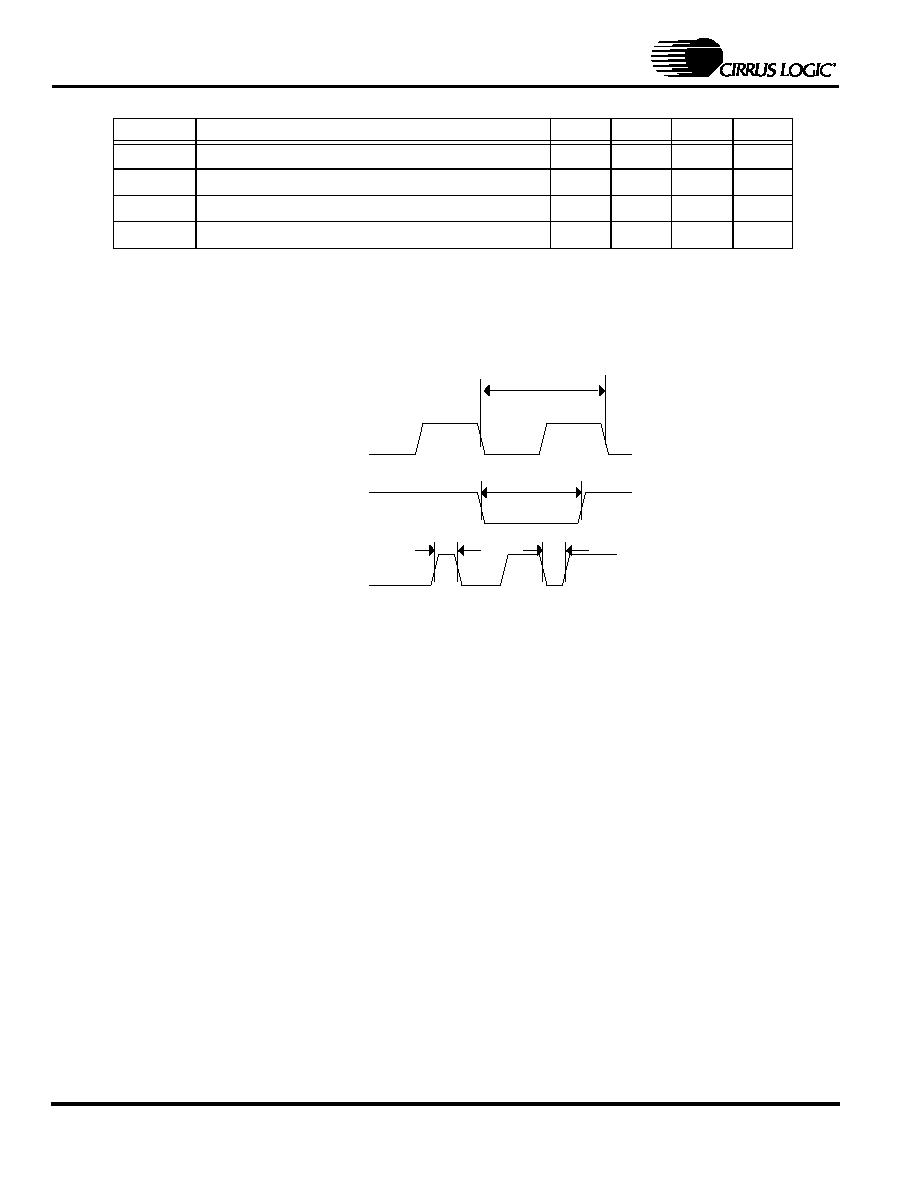

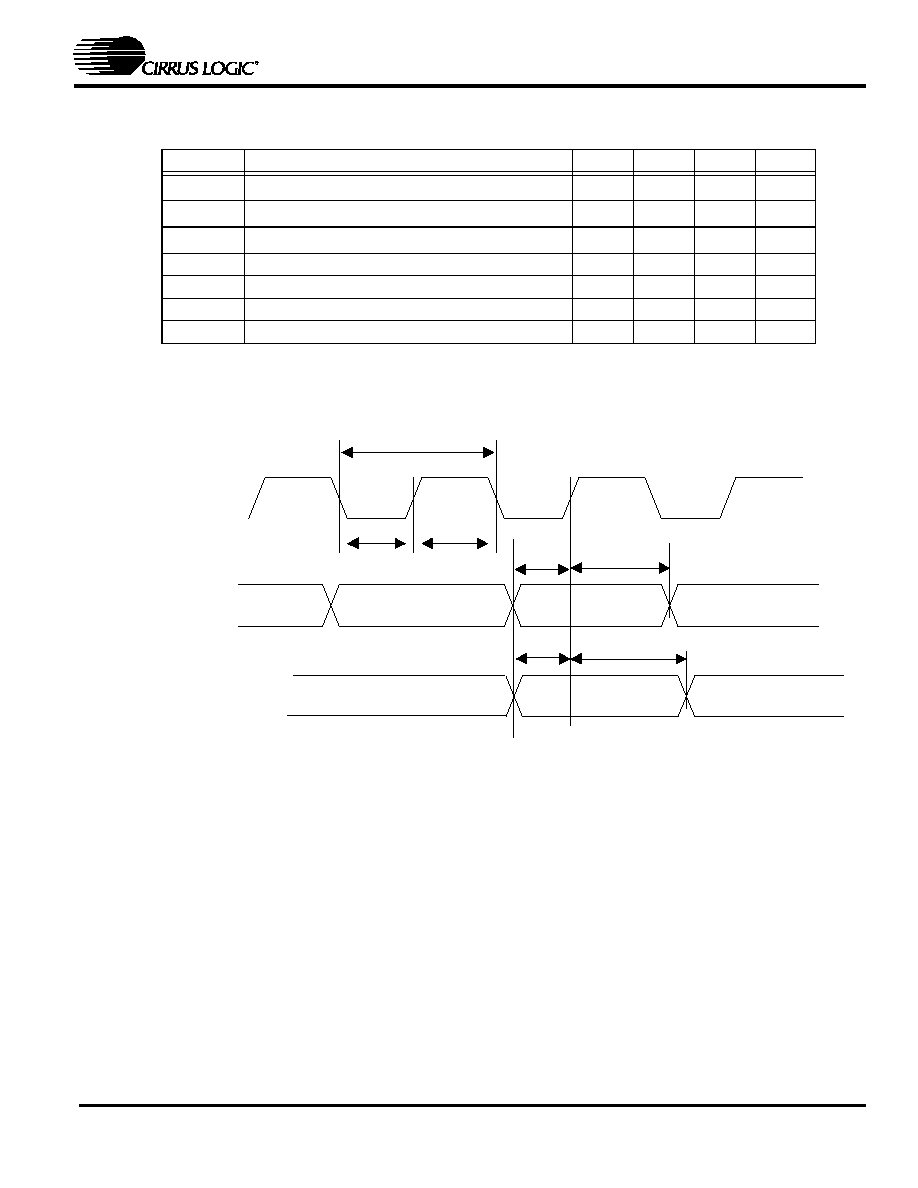

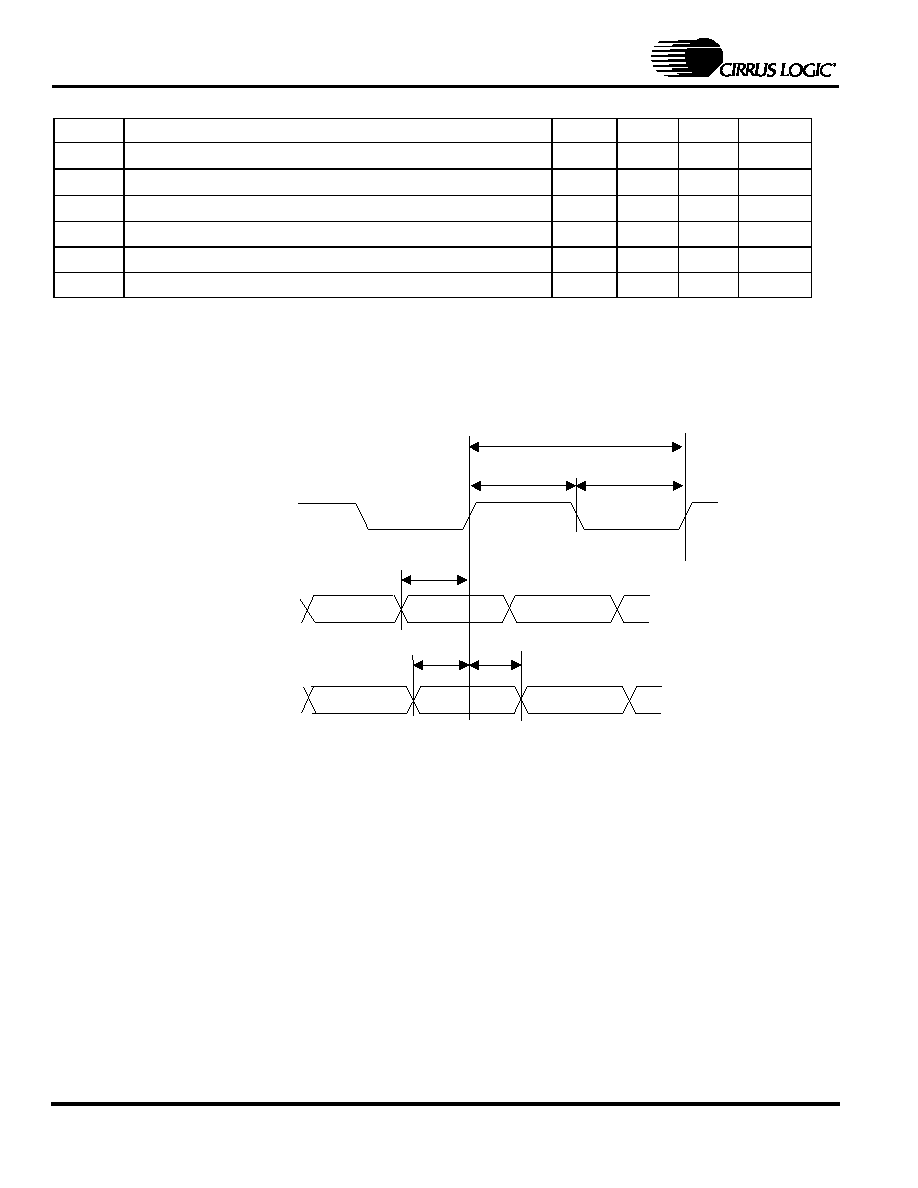

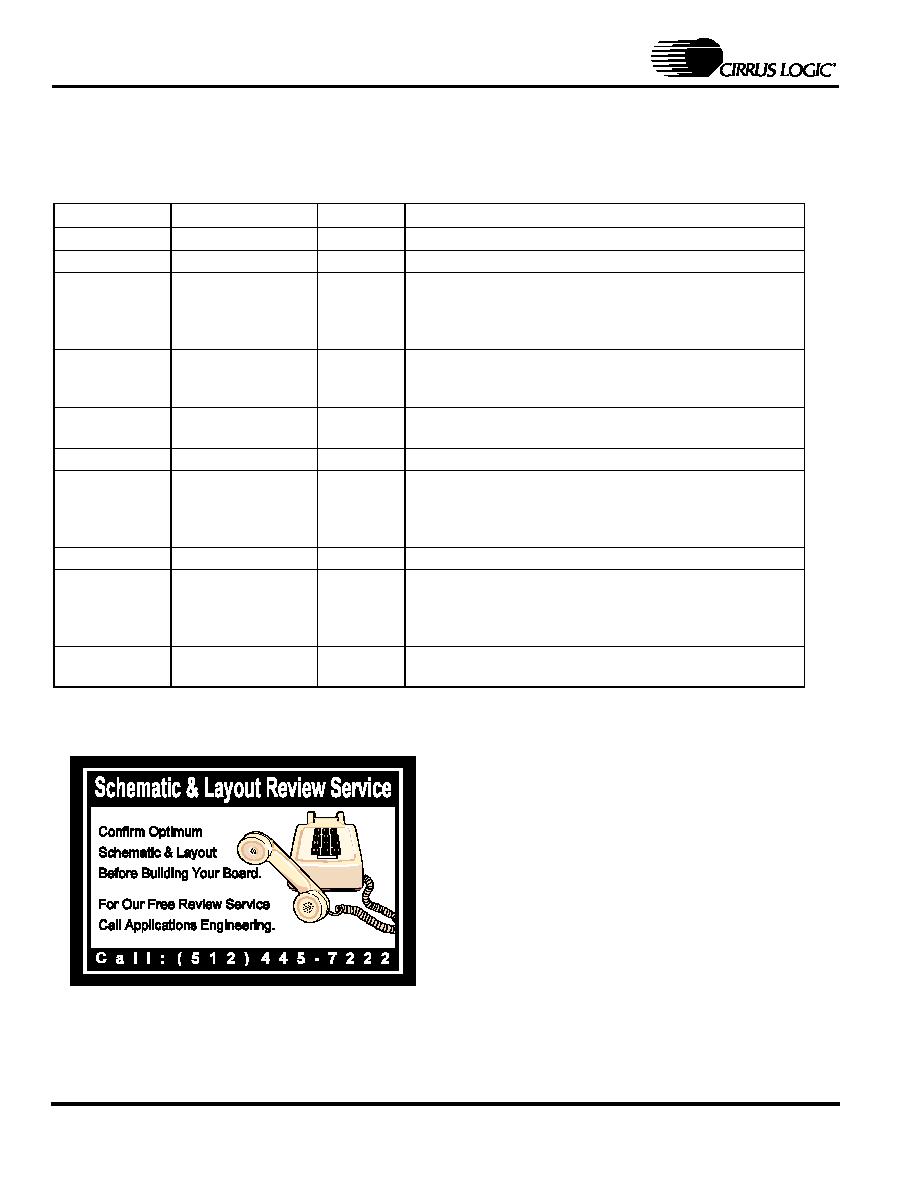

2.2.10

Miscellaneous Timings

Symbol

Description

Min

Typ

Max

Unit

t

xccper

1

1.

XTLCLK must meet the requirement of external the video encoder for correct chroma (27 MHz

�

1

KHz).

XTLCLK period

37.037

ns

t

rstl

RST_N Low Pulse Width

1000

ns

t

gph

GPIO PW High

50

ns

t

gpl

GPIO PW Low

50

ns

Table 8. Miscellaneous Timing Characteristics

RESET-N

t

gph

t

gpl

t

rstl

XTLCLOCK

GPIO

xccper

t

Figure 18. Miscellaneous Timings

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

25

CS98200

Next Generation DVD Processor

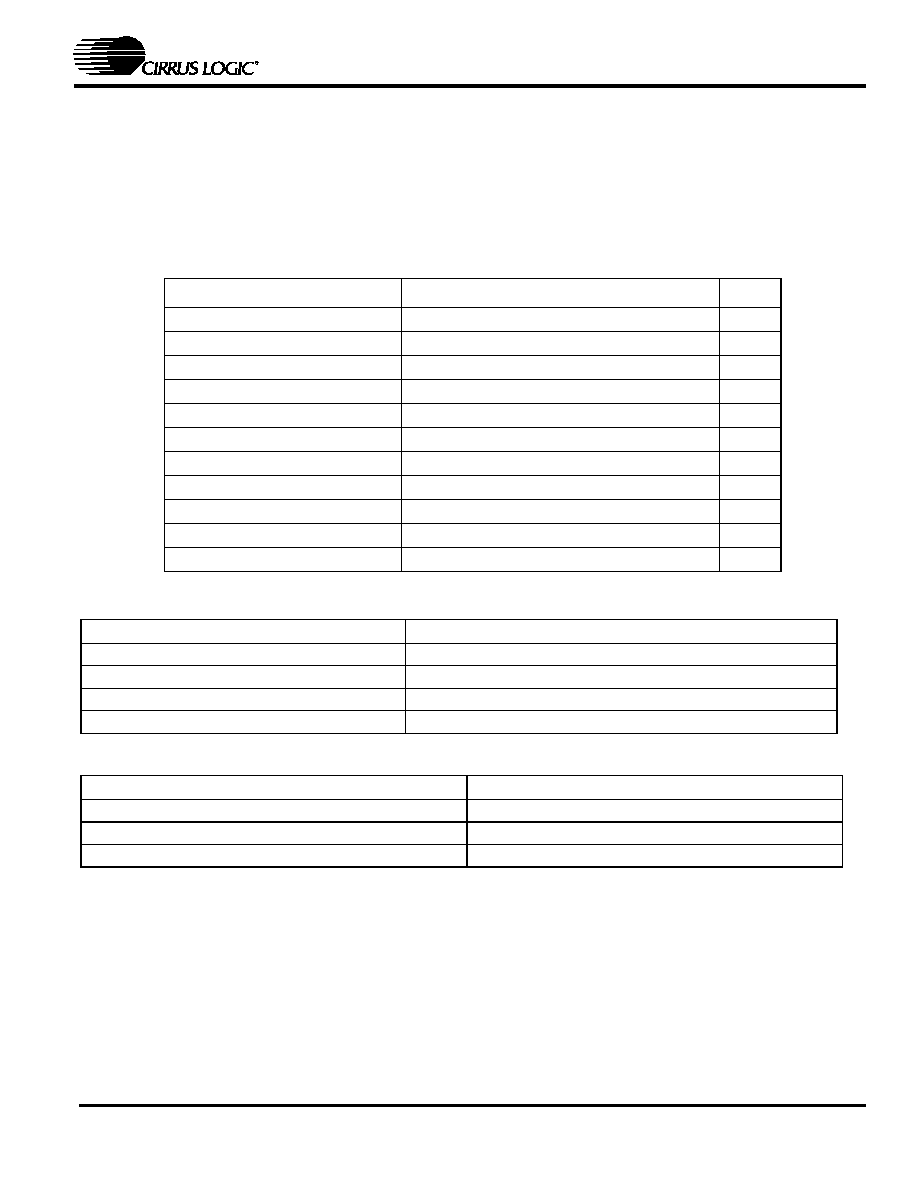

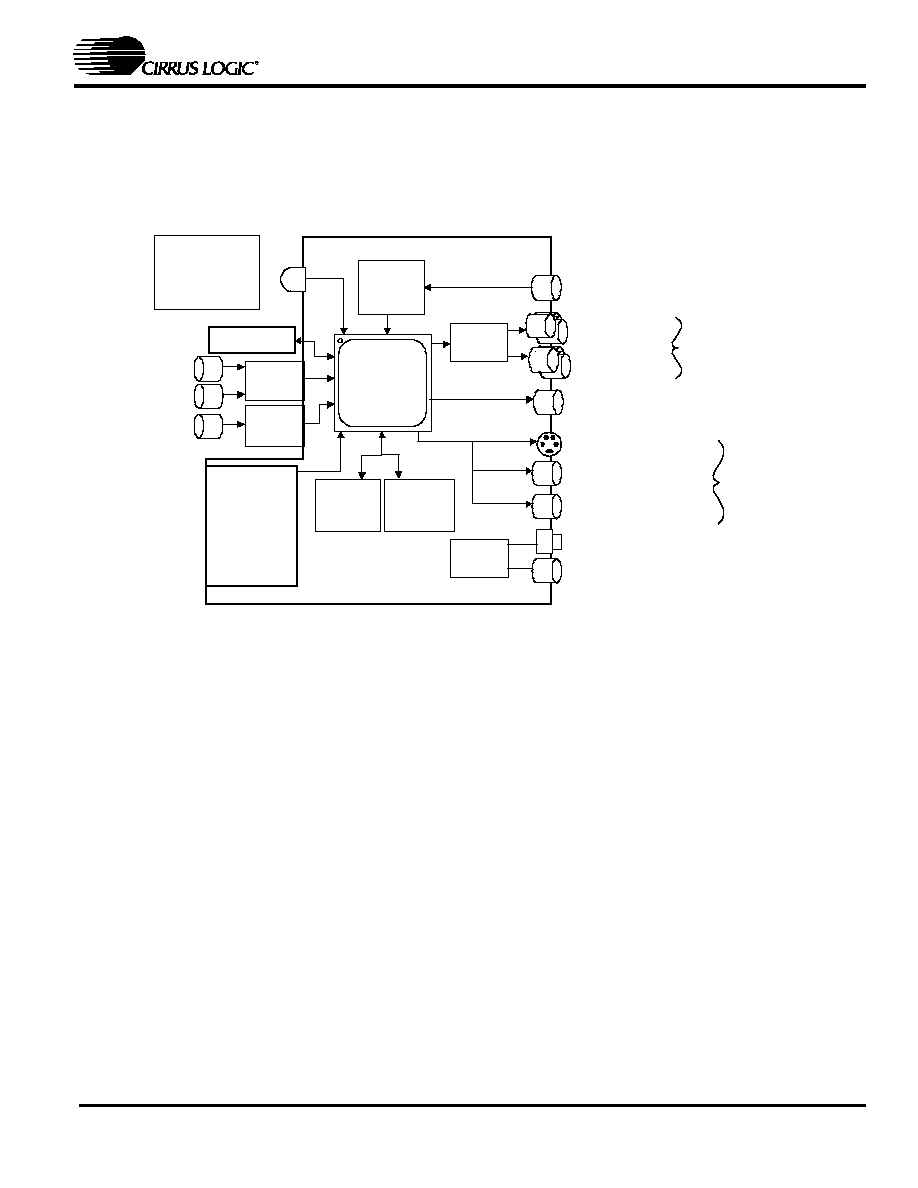

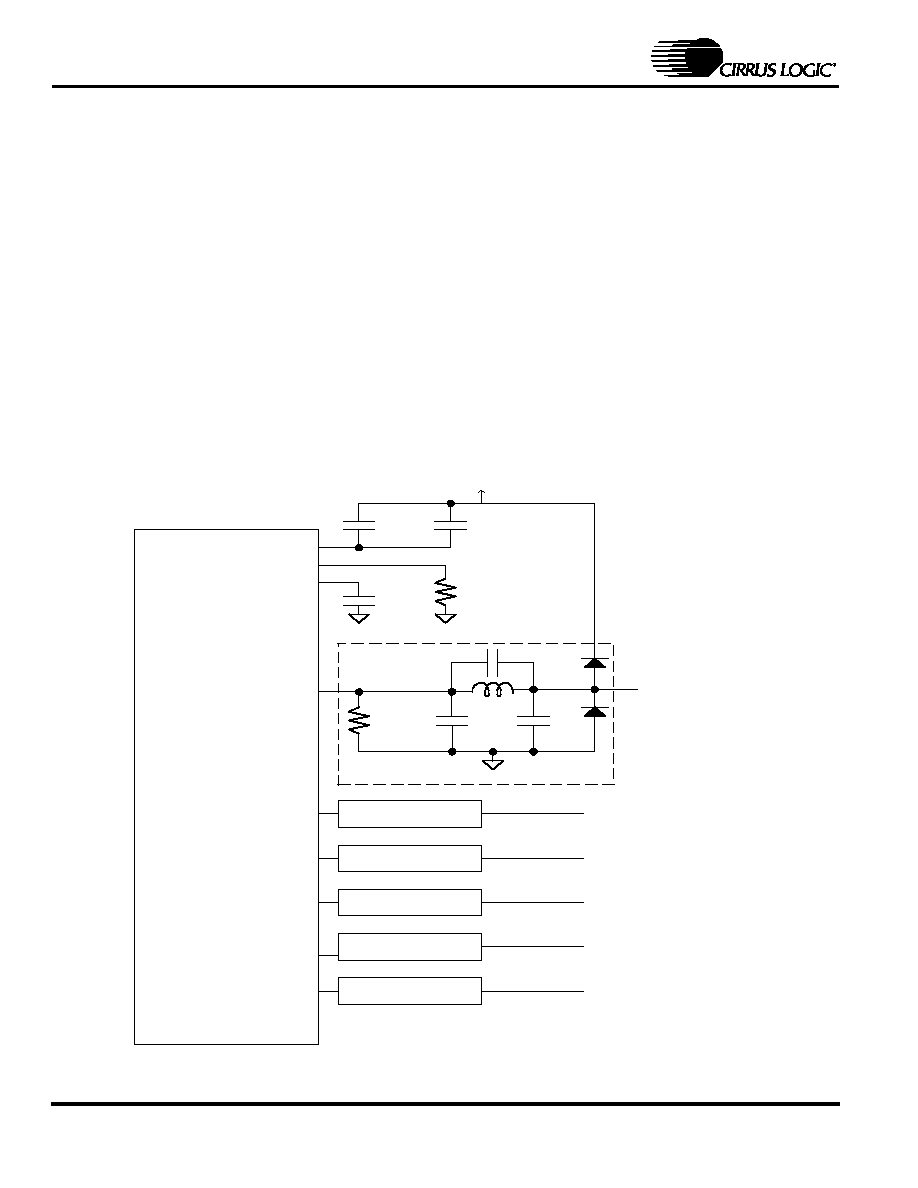

3. TYPICAL APPLICATION

The

Figure 19

shows a typical example of a complete DVD Receiver solution using the CS98200.

F L A S H

2 M

(U p to 8 M B)

S D R A M

8 M

(U p to 3 2 M B)

..

.

.

D ig ita l

In te rf a c e

R e c e iv e r

IR

(4 )A u d io

D A C s

P o w e r

R e g .

A u d io

A D C

V id e o

D e c o d e r

F ro n t P a n e l

C S 9 82 00

S /P D IF In pu t

A u dio-L(4 )

A u dio-R (4 )

S -V ide o

C o m po site V ide o

S w itch

P o w er

C D L o a d e r

(A T A P I ,

A / V )

A u dio-L

A u dio-R

V ide o

C o m po nen t V id eo

6 V id eo D A C s

A u dio u p to

8 C ha nn els

S /P D IF O utpu t

R em ote

K eybo ard

C on trol

Figure 19. CS98200 Typical Application

26

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

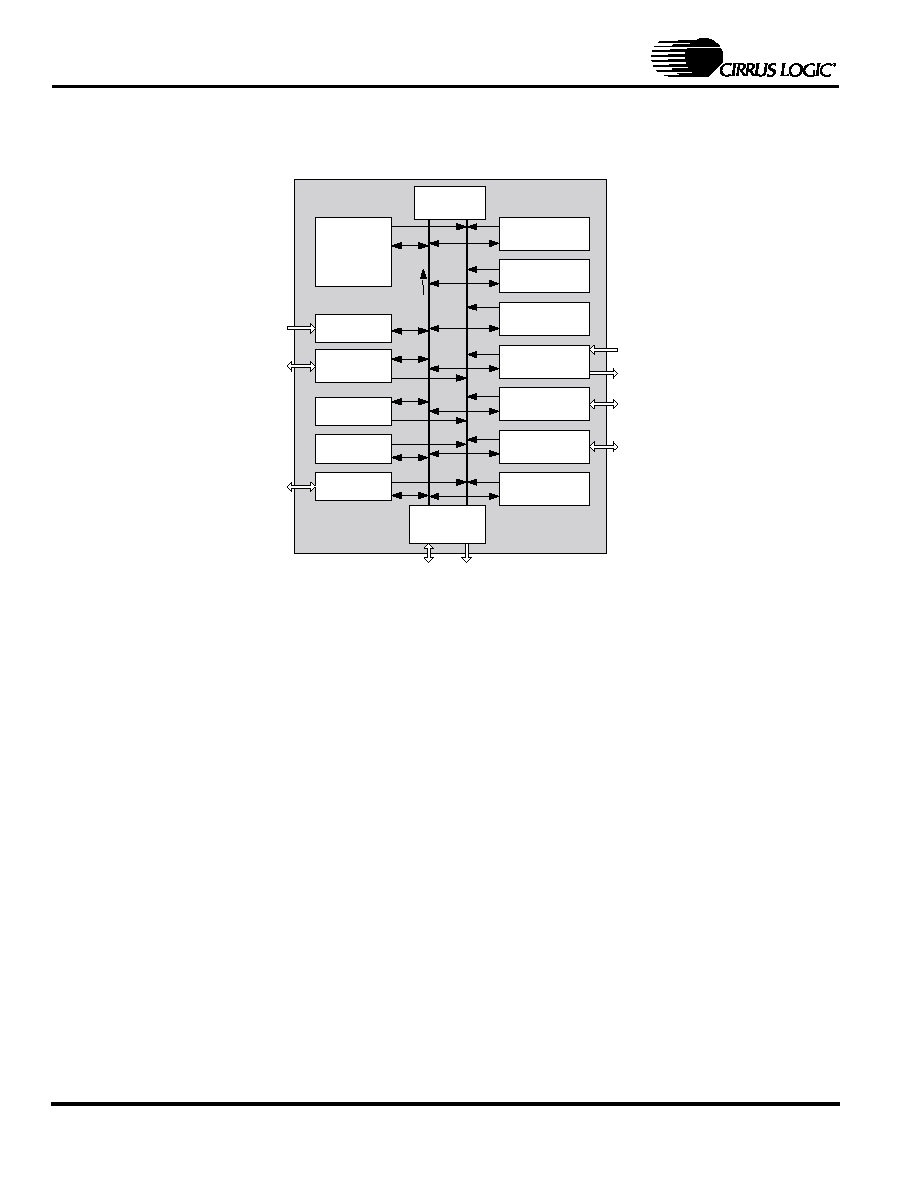

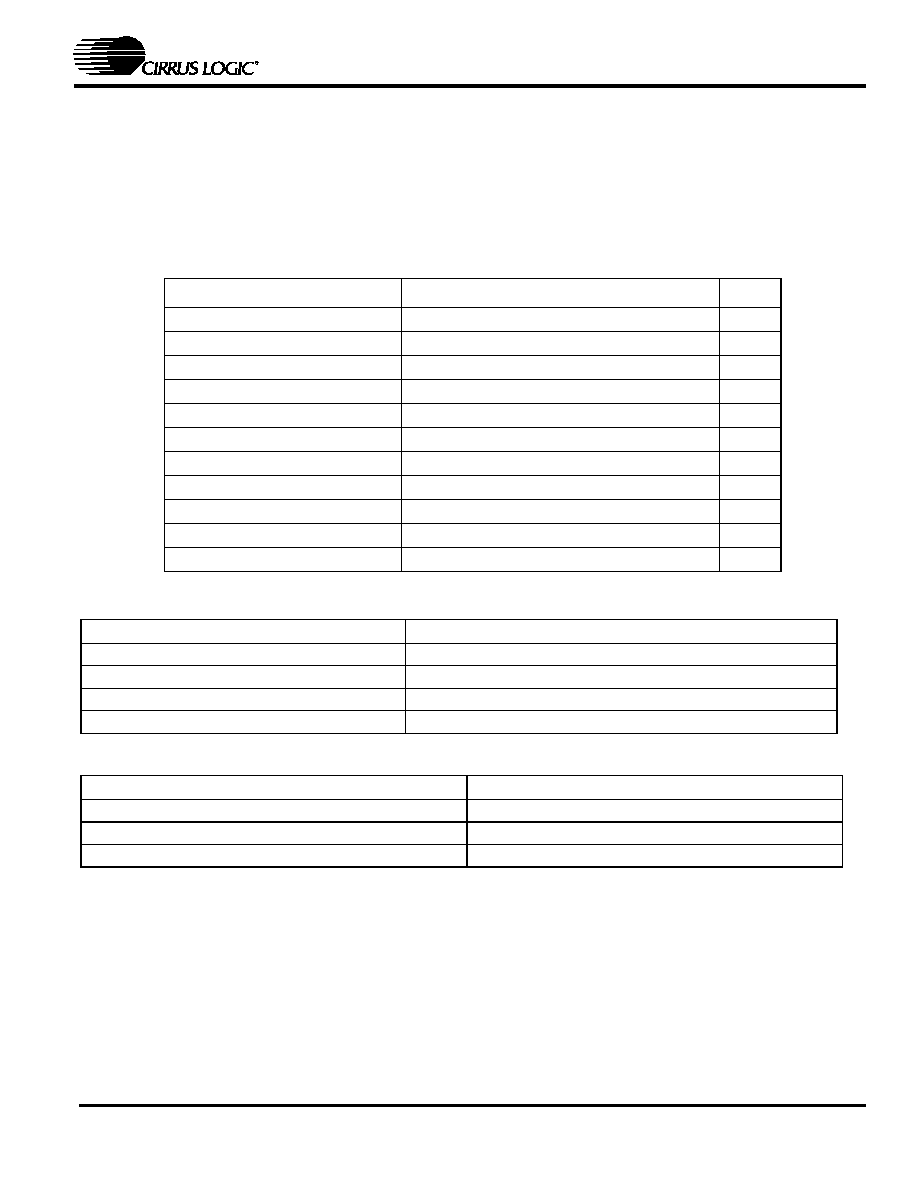

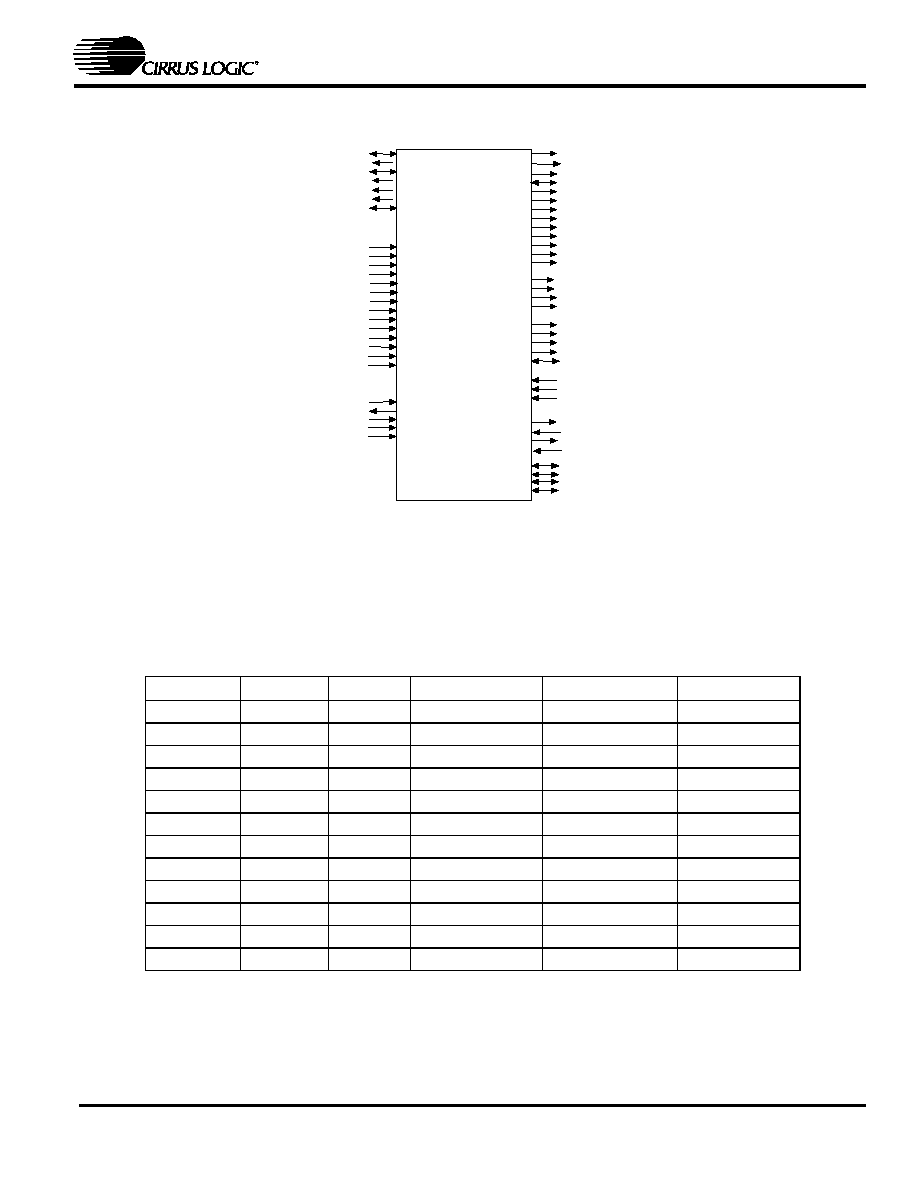

4. CS98200 DEVICE SUMMARY

4.1

Block Diagram

The CS98200 block diagram is shown in

Figure 20

.

4.2

CS98200 Device Details

4.2.1

RISC-32 Processors

� Two Powerful 32-bit RISC processors (RISC0

and RISC1), Generation III

� Virtual memory support

� Optimizing C compiler

� Big or little endian data formats support

� MAC multiply/accumulate in 2 cycles with

C support

� 4 Kbyte instruction cache, 2 Kbyte data

cache

� Single cycle instructions, runs at 180 Mhz

4.2.2

Powerful 24/32-Bit DSP

� Powerful 24/32-bit DSP processor

� 24-bit fixed point logic, with 54-bit accumu-

lator

� Single-cycle throughput, 2-cycle latency

multiply accumulate, 32-bit simple integer

logic. 8-Kbyte instruction cache

� Single cycle instructions, runs at 180 Mhz

� Expanded 4 Kbyte X + 16 KByte Y paged

program visible local memory, Total data

RAM = 20 KBytes

4.2.3

System Controls

� Includes several hardware lockable sema-

phore registers

� General-purpose register for inter-processor

communication

� 32-bit timers for I/O and other uses, with

programmable interval rates

� Both hardware and software interrupts on

data or debug

� Built in PLLs generate all required clocks

from 27 Mhz input clock

4.2.4

Memory Controller

� Supports standard SDRAM and SGRAM,

32-bit data mode only, from 4 MByte to 32

MByte

� Includes a separate dedicated DRAM clock,

so memory can run asynchronous to the sys-

tem clock

PLL

(Main,

Audio, SDRAM)

MPEG2 Video

Decoder

2/4/8/16 Bit OSD

t

Video Processor

(I/O, Scale, PIP, Mix)

SubPicture

Decoder

RISC1

(Application)

PCM, SPDIF

Interface

AUDIO DSP

DMA Control

(BitBlt, CSS)

Mem Control

(SDRAM,ROM)

Host Interface

(ATAPI,AV,ISA)

External IO

(GPIO, IR)

Registers

DATA

ADDR

Graphics

RISC0

(Navigation

and Control

)

Figure 20. CS98200 Block Diagram

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

27

CS98200

Next Generation DVD Processor

� High speed, can handle up to 120 MHz

DRAM speeds

� Supports 8-bit parallel ROM or FLASH, up

to 8 MB

� Single bank of SDRAM only. Single bank of

ROM/FLASH only

� Separate data bus for ROM, reduces loading

for improved speed, Also handles 5 V easier.

4.2.5

Data Flow Engine

� 2432 bytes of internal memory

� DMA to/from main RAM into local SRAM

� Supports endian conversion and byte, short,

long data formats on DMA

� Supports block transfers for graphics bit

blits

4.2.6

MPEG Video Decoder

� Supports VCD, VCD 2.0, DVD video stan-

dards

� Supports trick features, including smooth 2x

play and reverse play

� Special anti-tearing logic controls picture de-

code and presentation

� Advanced error concealment hardware

� New acceleration modules for MPEG-4 Sim-

ple Profiles support

4.2.7

System Synchronization

� System time clock (STC) for audio/video

synchronization

� Flexible interrupt structure for controlling

decode and presentation times

� Hardware scheduling of subpicture and

highlight events

4.2.8

Audio Interface

� Supports 8 channels PCM output at up to 24

bits and 192 kHz output rate.

� Supports 2 channels I

2

S input at up to 24 bits

and 96 kHz input rate.

� Simultaneous IEC-958 (SPDIF) output with

programmable channel status and user data.

� SPDIF, PCM input, and PCM output can all

have different XCLK dividers.

� Supports simultaneous 192 Khz front and 96

Khz surround, for DVD audio

4.2.9

Video Input

� NTSC/PAL video decoder input interface

� Video input image can be displayed in small

window, or as main picture

4.2.10

External Interface

� Serial I

2

C

�

master and slave port

� 29 independent fully programmable bi-di-

rectional I/O pins

� 8 edge or level detection interrupt pins

� Hardware assisted support for infrared re-

mote devices, such as remote control, infra-

red keyboard

� Dual UART

4.2.11

Video Processor

� Supports 24-bit 4:2:0 and 4:2:2 video modes

and 16-bit true color graphics modes.

� Picture-in-picture module includes horizon-

tal and vertical downscaling with program-

mable output sizes, positions, and borders

� Overlay mixer with RGB to YUV conversion

and output formatting

� Supports 4:2:0, 4:2:2, YUV655, RGB565 and

RGB555 frame buffer inputs

� Outputs 4:2:2 video in CCIR-601 or CCIR-

656 format

� High quality scaling using a vertical and a

horizontal 16 taps polyphase programmable

filter and supports any size image up to

768x576

� 3 taps adaptative anti-flicker filtering

� Master or Slave video sync configuration

� Multiple video plains overlay (main video /

video input / picture_in_picture / pic-

ture/on-screen / display)

� Gamma correction

4.2.12

Sub-Picture Processor

� Run-length decode DVD sub-pictures

� Hardware vertical scaling supports NTSC-

PAL format conversion

� 16-level alpha blending

4.2.13

Graphics Engine

� 16 bit true color

� Progressive and interlaced mode support

28

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

� Supports gamma correction

� Color-key type transparency support

� Global blending support

� Frame buffer wrap around support for

scrolling

� 3 tap horizontal and vertical filtering

4.2.14

On Screen Display Module

� Supports 2-bit and 4-bit pixel modes

� 3 separate regions support

� 16 transparency overlay levels support

4.2.15

DVD Loader Interface

� 4-pin serial interface to low-cost DVD load-

ers

� Loader control via separate 2-wire serial

master control port

� IO channel interface supports standard 8 bit

DVD loader protocols

4.2.16

CPU Interface and SRAM Controller

� Internal SRAM of 32 KByte, and controller,

synchronous with the CPUs at 180 Mhz

� Fast interfaces to RISCs and DSP

� Asynchronous interfaces to the main system

clock

� Special DMA engine, with multiple software

clients, and command FIFO

� Special interface to MPEG-4 video module

4.2.17

Host Bus Interface

� Programmable parallel host master interface

supports formats including ATAPI, ISA, and

more

� Internal DMA module, for I/O type reads

and writes on the host bus

� Extra chip selects, for more external devices

4.2.18

Video Encoder

� Six 10-bit video DACs, drive 37.5 W load di-

rectly without external buffering

� Supports PAL (B, D, G, H, I, N, M, 60) and

NTSC

� Component (RBG or YUV) or composite + S-

Video output

� Progressive or interlaced mode output

� Macrovision 7.1 support (interlaced) and

Macrovision 1.03 support (progressive)

� Wide-screen signalling support (interlaced

and progressive) and CGMS support

� Closed captioning support

4.2.19

System Functions

� 240-pin MQFP package

� All I/O pins are 3 V with 5V tolerance

� Advanced 0.18 micron CMOS technology

� Internal processors run at 180 MHz

� Supports Low Power modes and clock shut-

off

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

29

CS98200

Next Generation DVD Processor

5. FUNCTIONAL DESCRIPTION

5.1

RISC Processor

The CS98200 includes two powerful, third-gen-

eration proprietary 32-bit RISC processors,

RISC0 and RISC1, with optimizing C compiler

support and source level debugger. The RISC

processors fully support many Real Time Oper-

ation Systems (RTOS). The DVD application

user interface resides on RISC1 and is customer

programmable. The real time control of low lev-

el DVD functions is performed by RISC0. RISC1

gains access to system resources controlled by

RISC0 via calls through an Applications Pro-

gramming Interface, See the

CS98200 Software

API. All RISC0 firmware, API and sample appli-

cation code are supplied with the CS98200.

The RISC processors also have a MAC engine,

which performs multiply/accumulate in 2 cy-

cles in a pipelined fashion with C support, effec-

tively achieving single cycle throughout. The

RISC0 processor coordinates on-chip multi-

threaded tasks, as well as system activities such

as remote control and front panel control. The

DVD application end-user interface resides on

RISC1, and any modifications to that interface

occur through the CS98200 API.

5.2

DSP Processor

The CS98200 contains a proprietary digital sig-

nal processor (DSP), which is optimized for au-

dio applications. The DSP performs 32-bit

simple integer operations, and has a 24-bit fixed

point logic unit, with a 54-bit accumulator. The

multiply-accumulator has single-cycle through-

put, with two cycle latency. The DSP is opti-

mized for bit packing and unpacking

operations. The interface to main memory is de-

signed for handling flexible block sizes and skip

counts.

5.3

Memory Control

The DRAM Interface performs the SDRAM con-

trol and arbitration functions for all the other

modules in the CS98200. The DRAM interface

services and arbitrates a number of clients and

stores their code and/or data within the local

memory. This arbitration and scheduling guar-

antees the allocation of sufficient bandwidth to

the various clients. The DRAM Interface sup-

ports up to 32 Mbytes. For a typical DVD player

application, CS98200 requires 8 Mbytes memo-

ry space.

Sharing the same interface, CS98200 also sup-

ports FLASH ROM, OTP, or mask ROM inter-

face. Code is stored in ROM. After the system is

booted, the code is shadowed inside SDRAM

for execution. The FLASH ROM interface is pro-

vided so that the code can be upgraded in the

field once the communications channel is estab-

lished. Utility software will be provided to de-

bug and upgrade code for the system

manufacturer.

5.4

Dataflow Control (DMA)

The DMA controller moves data between the

external memory and internal memory. The ex-

ternal memory address can be specified using a

register, or in FIFO mode, using start and end

address registers. Separate start/end address

registers are used for DMA read and write oper-

ations. The DMA interface also has a block

transfer function, which allows for the transfer

of one block of data from one external memory

location to another external memory location. In

effect, this feature combines a DMA read and

write into one operation. In addition, the DMA

write operation allows for byte, short, word,

and other types of masking.

5.5

System Control Functions

The system control functions are used to coordi-

nate the activities of the multiple processors,

and to provide the supporting system opera-

tions. Eight 32-bit communication registers are

available for inter-processor communication,

and 32 semaphore registers are used for re-

source locking. Timers are available for general-

purpose functions, as well as more specialized

30

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

functions such as watchdog timers and perfor-

mance monitoring.

The large number of general purpose I/Os of-

fers flexibility in system configurations. An I

2

C

master allows for control of other I

2

C devices,

such as a video encoder. An I

2

C slave port

shares the same pins, and can be used for debug

functions. Interrupts can be generated on specif-

ic or generic events. Infrared inputs can be fil-

tered to make them free of glitches or stored

unfiltered into memory. Control of all the inter-

nal clocks is also possible. There are two sepa-

rate PLLs that are clocked by the 27 MHz clock

input. One PLL generates the main clock and

DRAM interface clock, and the second gener-

ates the Audio 256X/384X clock.

5.6

DVD/ATAPI Interface

The CS98200 has a programmable interface port

which can be configured to connect to industry

standard CD/DVD loaders without external

glue logic. The CD/DVD interface fully sup-

ports many popular CD/DVD loaders. The in-

terface consists of DVD control and data ports

and an optional CD control/data port.

The CS98200 hardware manages the DVD inter-

face and moving data to an arbitrary size input

FIFO in DRAM. The same interface pins can be

optionally configured as a generic 16-bit host

master port. In this mode, the CS98200 can con-

trol up to four devices (using 4 chip select out-

puts), each of which may use different protocol

and timing. The interface can be set up in ATA-

PI mode, to connect directly to any

ATAPI DVD loader (using two chip selects). Si-

multaneously, the other two chip selects can be

configured to connect to other devices, such as a

super I/O chip or hard disk.

A third option is to configure the interface for

micro-less DVD loader operation, which may

also be configured to connect without external

glue logic.

5.7

Serial DVD Interface

The CS98200 has a 4-pin serial port which inter-

faces to the data port of popular low-cost DVD

loaders. This type of loader provides for low

system cost by eliminating the track buffer, in-

terface FIFO, and flow control logic. The

CS98200 contains a large internal SRAM to han-

dle high burst data rates, without requiring re-

verse flow control. The CS98200 performs error

detection, sector number tracking, and interrupt

generation.

5.8

MPEG Video Decoding

Compressed MPEG data is read from the DVD

disk into an input FIFO in DRAM. The data flow

(DMA) controller moves Video packets from the

input FIFO into the MPEG decoder's input FIFO

(also in DRAM). The DMA controller can also

perform advanced functions such as start code

search, relieving the RISC processors. The Sys-

tem Synchronization function is used to control

the timing of MPEG picture decoding. The

MPEG Video decoder processes I, B, and P

frames, and writes to video frame buffers in

DRAM for output to the display. Special anti-

tearing logic ensures that currently displayed

frame buffers are not overwritten.

5.9

Audio Processing

Compressed Audio data is read from the DVD

disk into an input FIFO in DRAM. The data is

decompressed, then written to a PCM output

FIFO, also in DRAM. Presentation time stamps

(PTS) are extracted from the stream to update

the STC, in order to maintain audio/video syn-

chronization.

The DMA and decompression stages of audio

processing can be done with a combination of

the DMA unit, DSP, and RISC processors. The

DSP is optimized for audio processing, so most

common formats can be handled by the DSP

alone, including AC-3, DTS, MPEG2 audio, and

MP3. The DSP has enough reserve bandwidth

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

31

CS98200

Next Generation DVD Processor

to handle the Karaoke echo-mix and pitch shift,

and AC-3 down-mix functions.

The audio output data is written into a DRAM

FIFO in 16-, 18-, 20- or 24-bit PCM format. A

flexible audio output stage can simultaneously

output 8 channels of PCM data to audio DACs

up to 192 KHz sample rate, plus an IEC-958 en-

coded output at up to 48 KHz. The audio inter-

face also includes a flexible audio input

interface, which can input a wide range of pro-

tocols from an audio ADC or an IEC-958 receiv-

er at up to 96 KHz.

32

Copyright 2002 Cirrus Logic (All Rights Reserved)

DS581PP2

CS98200

Next Generation DVD Processor

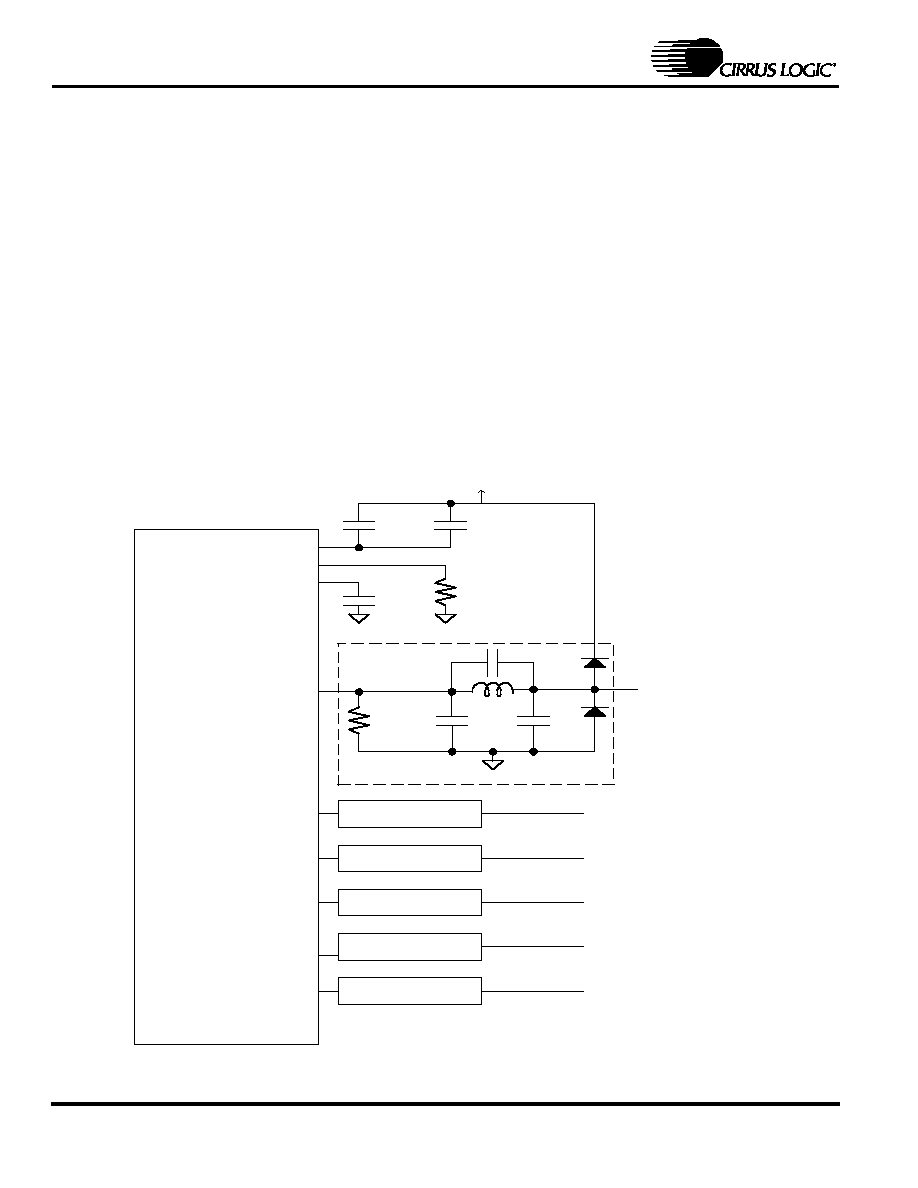

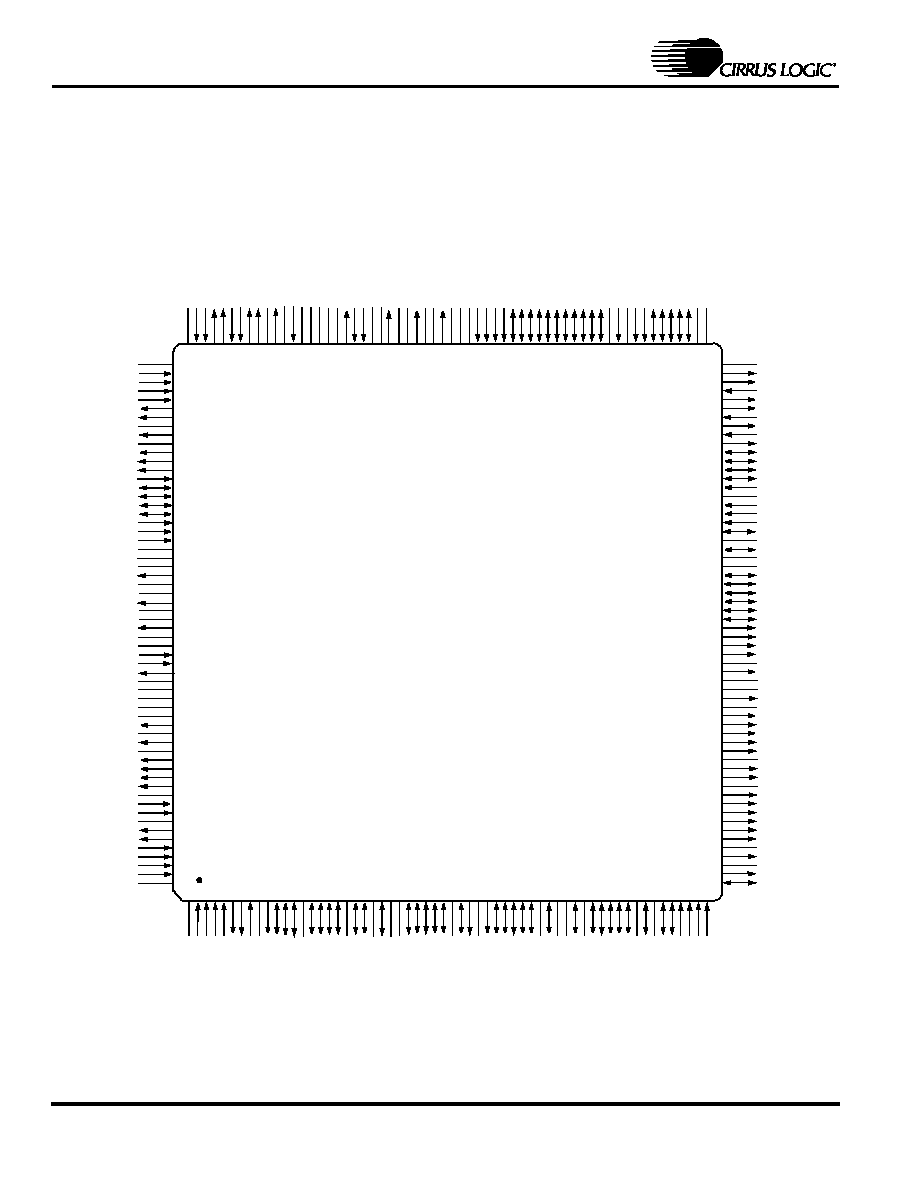

5.10

Video Encoder with Progressive Video

DACs

The CS98200 incorporates an enhanced video

encoder with six 10-bit video DACs that drive

double terminated 75

directly without exter-

nal buffering. These termination resistors

should be located as close as possible to the

CS98200. All analog video outputs should be

connected through filters to video connectors

(TV/Monitor). The video filters should be locat-

ed as close as possible to the video connectors.

Two schottky diodes should be connected to

each output in order to protect the CS98200

from surges caused by being connected and dis-

connected to the external devices.

Figure 21

shows the video DAC connections.

Six 10-bit DACs provide two channels for an S-

Video output port, one composite video output,

and three RGB or Y, Pb, Pr outputs. Video out-

put can be formatted to be compatible with

NTSC (M,J), PAL (B, D, G, H, I, M, 60), and 480P.

The video encoder is compliant with both Mac-

rovision 7.1 for the interlaced video (NTSC,

PAL) and 1.03 for the progressive scan (480p).

The video encoder also supports WSS (Wide-

Screen Signaling), CGMS (Copy Generation

Management System), and Closed Caption.

C S 9 8 2 0 0

C O M P 1 & 2

R S E T 1 & 2

V R E F 1 & 2

Y

C

C V

Y G

V R

U B

3 . 3 V

1 7 4

1 %

0 . 0 1 u F

0 . 0 1 u F

Y o u t

V i d o e F il t e r

V id e o F ilt e r

V id e o F ilt e r

V id e o F ilt e r

V id e o F ilt e r

V id e o F ilt e r

C o u t

C V o u t

V R o u t

Y G o u t

U B o u t

7 5

1 %

2 7 0 p F

3 3 0 p F

1 . 8 u H

2 2 p F

1 0 u F

Figure 21. Video DAC Connections

DS581PP2

Copyright 2002 Cirrus Logic (All Rights Reserved)

33

CS98200

Next Generation DVD Processor

5.11

Video Input/Output Interface

In addition to the six 10-bit video DACs, the

CS98200 provides a separate Digital Video In-

terface that will give you flexible and powerful

means of outputting digital video data to exter-

nal devices in CCIR601/3 and CCIR656 formats.

The interface directly supports NTSC/PAL vid-

eo encoding, in both master and slave synchro-

nization configurations. The internal frame

buffer format could be 4:2:0, 4:2:2, YUV655,

RGB565 and RGB555.

The CS98200 also features an NTSC/PAL video

decoder input interface. The interface accepts

CCIR601, CIF, and QCIF formats, out of many

TV decoders on the market. The video processor