Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

1

Copyright

�

Cirrus Logic, Inc. 2004

(All Rights Reserved)

www.cirrus.com

CS5340

101 dB, 192 kHz, Multi-Bit Audio A/D Converter

Features

Advanced multi-bit Delta-Sigma architecture

24-bit conversion

Supports all audio sample rates including

192 kHz

101 dB Dynamic Range at 5 V

-94 dB THD+N

High-pass filter to remove DC offsets

Analog/digital core supplies from 3.3 V to 5 V

Supports logic levels between 1.8 V and 5 V

Low-latency digital filter

Auto-mode selection

Pin compatible with the CS5341

General Description

The CS5340 is a complete analog-to-digital converter for

digital audio systems. It performs sampling, analog-to-

digital conversion, and anti-alias filtering, generating

24-bit values for both left and right inputs in serial form at

sample rates up to 200 kHz per channel.

The CS5340 uses a 5th-order, multi-bit Delta-Sigma

modulator followed by digital filtering and decimation,

which removes the need for an external anti-alias filter.

The CS5340 is ideal for audio systems requiring wide dy-

namic range, negligible distortion and low noise, such as

set-top boxes, DVD-karaoke players, DVD recorders,

A/V receivers, and automotive applications.

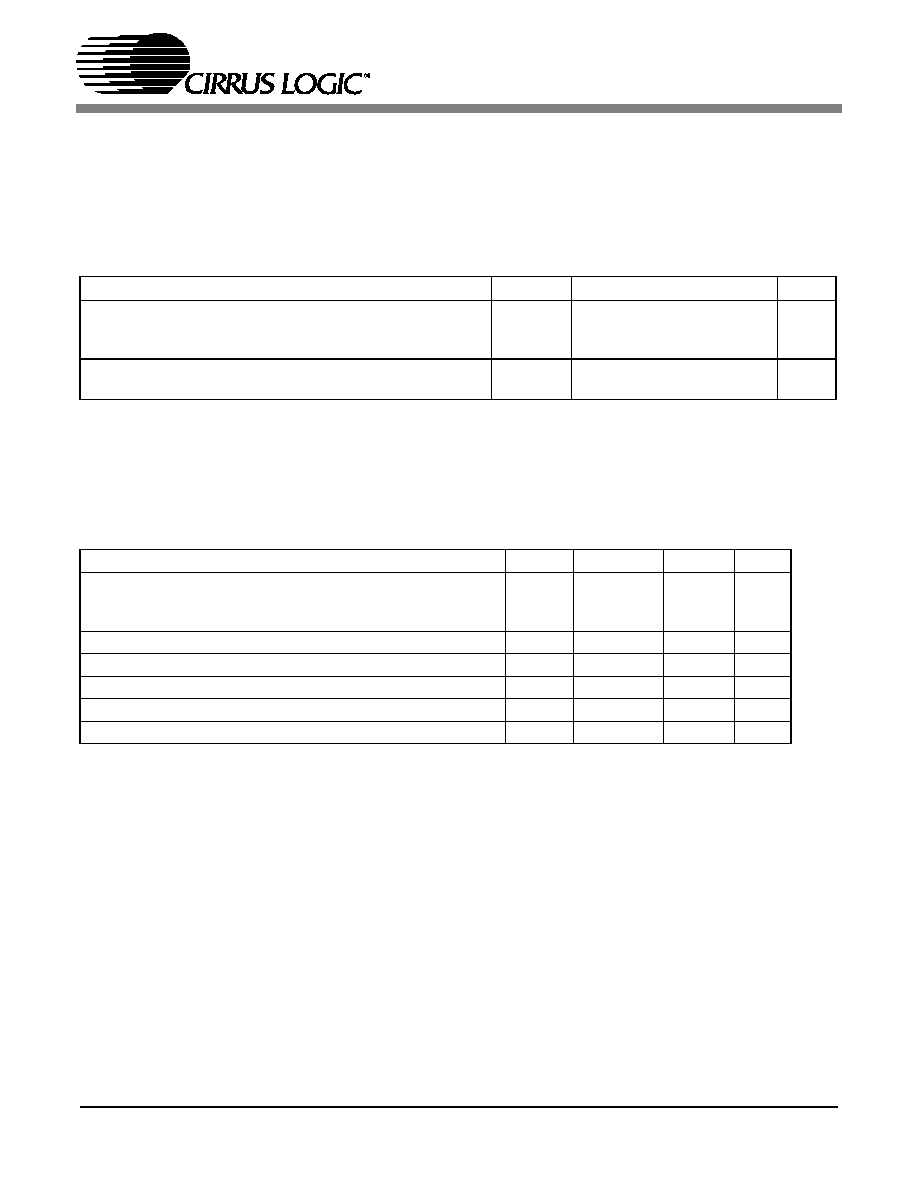

ORDERING INFORMATION

CS5340-CZZ, Lead Free -10� to 70� C 16-pin TSSOP

CS5340-DZZ, Lead Free -40� to 85� C 16-pin TSSOP

CDB5340

Evaluation Board

Voltage Reference

Serial Output Interface

Digital

Filter

High

Pass

Filter

High

Pass

Filter

Decimation

Digital

Filter

Decimation

DAC

-

+

S/H

DAC

-

+

S/H

AINR

SCLK

SDOUT

MCLK

RST

VQ

LRCK

AINL

FILT+

M0

REFGND

V

L

Q

LP Filter

Q

LP Filter

M1

VD

GND

VA

3.3V - 5.0V

3.3V - 5.0V

1.8V - 5.0V

Aug `04

DS601PP2

CS5340

2

DS601PP2

TABLE OF CONTENTS

1 CHARACTERISTICS AND SPECIFICATIONS ......................................................................... 4

SPECIFIED OPERATING CONDITIONS ................................................................................. 4

ABSOLUTE MAXIMUM RATINGS ........................................................................................... 4

ANALOG CHARACTERISTICS (CS5340-CZ/CZZ).................................................................. 5

ANALOG CHARACTERISTICS (CS5340-DZZ) ....................................................................... 7

DIGITAL FILTER CHARACTERISTICS (CS5340-CZ/CZZ/DZZ) ............................................. 9

DC ELECTRICAL CHARACTERISTICS................................................................................. 12

DIGITAL CHARACTERISTICS ............................................................................................... 12

THERMAL CHARACTERISTICS............................................................................................ 12

SWITCHING CHARACTERISTICS - SERIAL AUDIO PORT ................................................. 13

2 PIN DESCRIPTION ................................................................................................................. 15

3 TYPICAL CONNECTION DIAGRAM ....................................................................................... 16

4 APPLICATIONS ....................................................................................................................... 17

4.1 Single, Double, and Quad Speed Modes ......................................................................... 17

4.2 Operation as Either a Clock Master or Slave ................................................................... 17

4.2.1 Operation as a Clock Master ............................................................................... 18

4.2.2 Operation as a Clock Slave ................................................................................. 18

4.2.3 Master Clock ....................................................................................................... 19

4.3 Serial Audio Interface ....................................................................................................... 19

4.4 Power-up Sequence ........................................................................................................ 20

4.5 Analog Connections ......................................................................................................... 20

4.6 Grounding and Power Supply Decoupling ....................................................................... 20

4.7 Synchronization of Multiple Devices ................................................................................ 21

4.8 Capacitor Size on the Reference Pin (FILT+) .................................................................. 21

5 PARAMETER DEFINITIONS ................................................................................................... 22

6 PACKAGE DIMENSIONS ....................................................................................................... 23

7 REVISION HISTORY ............................................................................................................... 24

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find one nearest you go to

www.cirrus.com/

IMPORTANT NOTICE

"Preliminary" product information describes products that are in production, but for which full characterization data is not yet available. Cirrus Logic, Inc.

and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to

change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of

relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms

and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items,

or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no

license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns

the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your

organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for

general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SE-

VERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED

OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, LIFE

SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS (INCLUDING MEDICAL DEVICES, AIRCRAFT SYSTEMS OR COMPONENTS AND

PERSONAL OR AUTOMOTIVE SAFETY OR SECURITY DEVICES). INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDER-

STOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IM-

PLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY

CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF

CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DI-

RECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS,

THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may

be trademarks or service marks of their respective owners.

CS5340

DS601PP2

3

LIST OF FIGURES

Figure 1. Single Speed Mode Stopband Rejection ....................................................................... 10

Figure 2. Single Speed Mode Stopband Rejection ....................................................................... 10

Figure 3. Single Speed Mode Transition Band (Detail)................................................................. 10

Figure 4. Single Speed Mode Passband Ripple ........................................................................... 10

Figure 5. Double Speed Mode Stopband Rejection...................................................................... 10

Figure 6. Double Speed Mode Stopband Rejection...................................................................... 10

Figure 7. Double Speed Mode Transition Band (Detail) ............................................................... 11

Figure 8. Double Speed Mode Passband Ripple .......................................................................... 11

Figure 9. Quad Speed Mode Stopband Rejection ........................................................................ 11

Figure 10. Quad Speed Mode Stopband Rejection ...................................................................... 11

Figure 11. Quad Speed Mode Transition Band (Detail) ................................................................ 11

Figure 12. Quad Speed Mode Passband Ripple........................................................................... 11

Figure 13. Master Mode, Left Justified SAI ................................................................................... 14

Figure 14. Slave Mode, Left Justified SAI ..................................................................................... 14

Figure 15. Master Mode, I

2

S SAI .................................................................................................. 14

Figure 16. Slave Mode, I

2

S SAI .................................................................................................... 14

Figure 17. Typical Connection Diagram ........................................................................................ 16

Figure 18. CS5340 Master Mode Clocking ................................................................................... 18

Figure 19. Left-Justified Serial Audio Interface ............................................................................. 19

Figure 20. I

2

S Serial Audio Interface............................................................................................. 19

Figure 21. CS5340 Recommended Analog Input Buffer............................................................... 20

Figure 22. CS5340 THD+N versus Frequency ............................................................................. 21

LIST OF TABLES

Table 1. Speed Modes and the Associated Output Sample Rates (Fs)........................................ 17

Table 2. CS5340 Mode Control..................................................................................................... 17

Table 3. Master Clock (MCLK) Ratios........................................................................................... 19

Table 4. Master Clock (MCLK) Frequencies for Standard Audio Sample Rates .......................... 19

Table 5. Revision History .............................................................................................................. 24

CS5340

4

DS601PP2

1

CHARACTERISTICS AND SPECIFICATIONS

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical

performance characteristics and specifications are derived from measurements taken at typical supply voltages

and T

A

= 25

�C.)

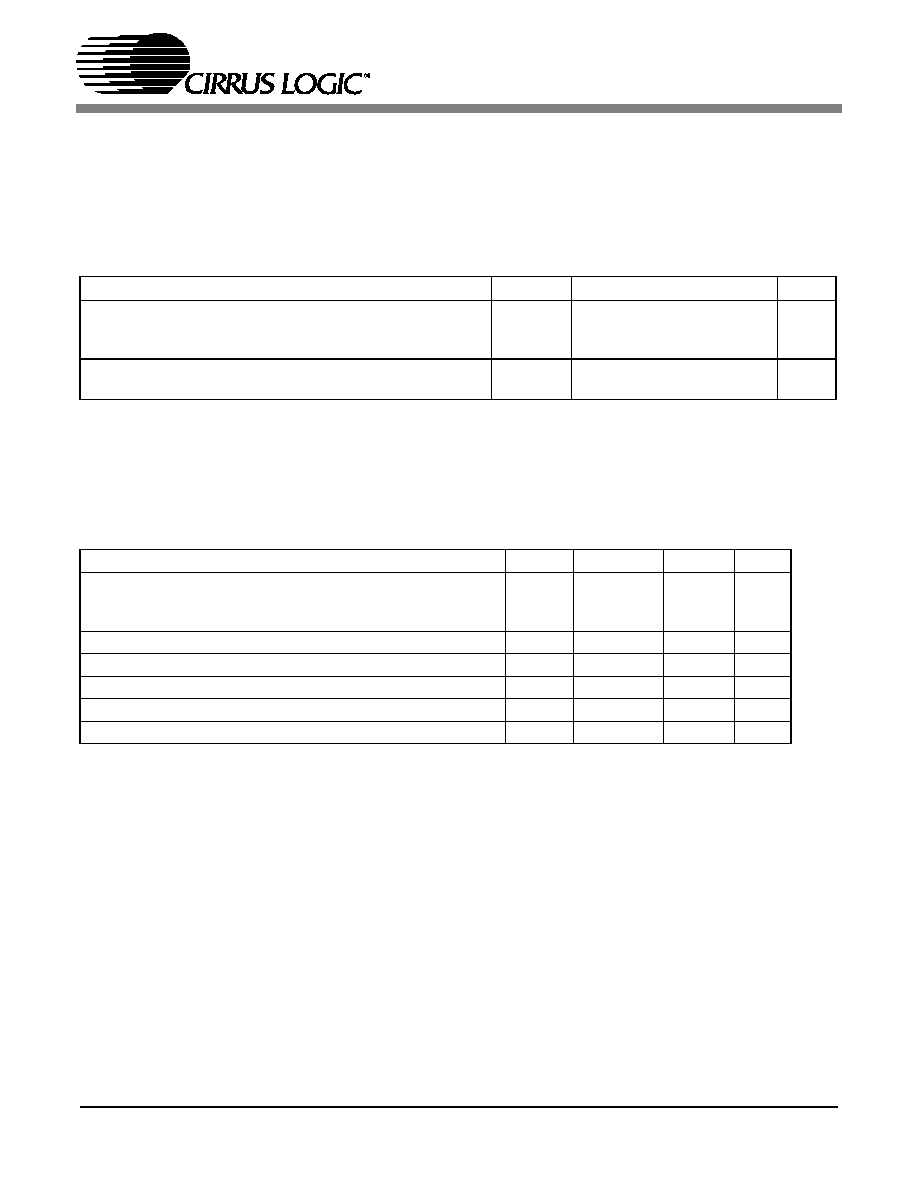

SPECIFIED OPERATING CONDITIONS

(GND = 0 V, all voltages with respect to 0 V.)

Notes: 1. This part is specified at typical analog voltages of 3.3 V and 5.0 V. See

Analog Characteristics (CS5340-

CZ/CZZ)

and

Analog Characteristics (CS5340-DZZ),

below, for details.

ABSOLUTE MAXIMUM RATINGS

(GND = 0 V, All voltages with respect to ground.) (Note 4)

Notes: 2. Any pin except supplies. Transient currents of up to �100 mA on the analog input pins will not cause SRC

latch-up.

3. The maximum over/under voltage is limited by the input current.

4. Operation beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Parameter

Symbol Min Typ

Max

Unit

Power Supplies

Analog

Digital

Logic

VA

VD

VL

3.1

3.1

1.7

(Note 1)

3.3

3.3

5.25

5.25

5.25

V

V

V

Ambient Operating Temperature

Commercial (-CZ/CZZ)

(-DZZ)

T

AC

T

AC

-10

-40

-

-

70

85

�C

�C

Parameter

Symbol

Min

Max

Units

DC Power Supplies:

Analog

Logic

Digital

VA

VL

VD

-0.3

-0.3

-0.3

+6.0

+6.0

+6.0

V

V

V

Input Current

(Note 2)

I

in

-

�10

mA

Analog Input Voltage

(Note 3)

V

IN

GND-0.7

VA+0.7

V

Digital Input Voltage

(Note 3)

V

IND

-0.7

VL+0.7

V

Ambient Operating Temperature (Power Applied)

T

A

-50

+95

�C

Storage Temperature

T

stg

-65

+150

�C

CS5340

DS601PP2

5

ANALOG CHARACTERISTICS (CS5340-CZ/CZZ)

Test conditions (unless otherwise speci-

fied): Input test signal is a 1 kHz sine wave; measurement bandwidth is 10 Hz to 20 kHz.

Parameter

Symbol

Min

Typ Max

Unit

VA = 3.3 V

Single Speed Mode Fs = 48 kHz

Dynamic Range

A-weighted

unweighted

92

89

98

95

-

-

dB

dB

Total Harmonic Distortion + Noise (Note 5)

-1 dB

-20 dB

-60 dB

THD+N

-

-

-

-91

-75

-35

-85

-

-

dB

dB

dB

Double Speed Mode Fs = 96 kHz

Dynamic Range

A-weighted

unweighted

40 kHz bandwidth unweighted

92

89

-

98

95

92

-

-

-

dB

dB

dB

Total Harmonic Distortion + Noise (Note 5)

-1 dB

-20 dB

-60 dB

40 kHz bandwidth -1 dB

THD+N

-

-

-

-

-91

-75

-35

-85

-85

-

-

-

dB

dB

dB

dB

Quad Speed Mode Fs = 192 kHz

Dynamic Range

A-weighted

unweighted

40 kHz bandwidth unweighted

92

89

-

98

95

92

-

-

-

dB

dB

dB

Total Harmonic Distortion + Noise (Note 5)

-1 dB

-20 dB

-60 dB

40 kHz bandwidth -1 dB

THD+N

-

-

-

-

-91

-75

-35

-85

-85

-

-

-

dB

dB

dB

dB

VA = 5.0 V

Single Speed Mode Fs = 48 kHz

Dynamic Range

A-weighted

unweighted

95

92

101

98

-

-

dB

dB

Total Harmonic Distortion + Noise (Note 5)

-1 dB

-20 dB

-60 dB

THD+N

-

-

-

-94

-78

-38

-88

-

-

dB

dB

dB

Double Speed Mode Fs = 96 kHz

Dynamic Range

A-weighted

unweighted

40 kHz bandwidth unweighted

95

92

-

101

98

95

-

-

-

dB

dB

dB

Total Harmonic Distortion + Noise (Note 5)

-1 dB

-20 dB

-60 dB

40 kHz bandwidth -1 dB

THD+N

-

-

-

-

-94

-78

-38

-91

-88

-

-

-

dB

dB

dB

dB