| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: CY2037 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

PRELIMINARY

High Accuracy EPROM Programmable

PLL Die for Crystal Oscillators

CY2037

Cypress Semiconductor Corporation

∑

3901 North First Street

∑

San Jose

∑

CA 95134

∑

408-943-2600

December 24, 1997

Features

Benefits

∑ EPROM-programmable die for in-package programming of

crystal oscillators

Enables quick turnaround of custom oscillators

Lowers inventory costs through stocking of blank parts

∑ High resolution PLL with 12 bit multiplier and 10 bit divider

Enables synthesis of highly accurate and stable output clock

frequencies with zero or low PPM

∑ EPROM-programmable capacitor tuning array

Enables fine-tuning of output clock frequency by adjusting

C

Load

of the crystal

∑ Twice programmable die

Enables reprogramming of programmed part, to correct errors,

and control excess inventory

∑ Simple 4-wire programming interface

Enables programming of output frequency after packaging

∑ On-chip oscillator runs from 10≠30 MHz crystal

Lowers cost of oscillator as PLL can be programmed to a high

frequency using a low-frequency, low-cost crystal

∑ EPROM-selectable TTL or CMOS duty cycle levels

Duty cycle centered at 1.5V or V

DD

/2

Provides flexibility to service most TTL or CMOS applications

∑ Operating frequency

-- 1≠200 MHz at 5V

-- 1≠100 MHz at 3.3V

-- 1≠66.67 MHz at 2.7V

Services most PC, networking, and consumer applications

∑ Sixteen selectable post-divide options, using either PLL or

reference oscillator output

Provides flexibility in output configurations and testing

∑ Programmable PWR_DWN or OE pin

Enables low-power operation or output enable function

∑ Programmable asynchronous or synchronous OE and

PWR_DWN modes

Provides flexibility for system applications, through selectable

instantaneous or synchronous change in outputs

∑ Low Jitter outputs

-- < ±100ps (pk-pk) at 5V

-- < ±125ps (pk-pk) at 3.3V

Suitable for most PC, consumer, and networking applications

∑ 3.3V or 5V operation

Lowers inventory cost as same die services both applications

∑ Small Die

Enables encapsulation in small-size, surface mount packages

∑ Controlled rise and fall times and output slew rate

Has lower EMI than oscillators

Die Configuration

CY2037 Logic Block Diagram

AV

DD

Top View

V

SS

V

DD

X

G

PWR_DWN

CLKOUT

AV

SS

X

G

PWR_DWN

X

D

CONFIGURATION

X

D

CRYSTAL

CLKOUT

/ 1, 2, 4, 8, 16, 32, 64, 128

X

D

X

D

N/C

OSCILLATOR

1

2

3

4

5

6

7

8

9

10

or OE

or OE

MUX

HIGH

ACCURACY

PLL

EPROM

CY2037

PRELIMINARY

2

Functional Description

The CY2037 is an EPROM programmable, high accuracy,

PLL-based die designed for the crystal oscillator market. The

die attaches directly to a low-cost 10-30MHz crystal and can

be packaged into 4-pin through-hole or surface mount pack-

ages. The oscillator devices can be stocked as blank parts and

custom frequencies programmed in-package at the last stage

before shipping. This enables fast-turn manufacture of custom

and standard crystal oscillators without the need for dedicated,

expensive crystals.

The CY2037 contains an on-chip oscillator and a unique oscil-

lator tuning circuit for fine-tuning of the output frequency. The

crystal C

load

can be selectively adjusted by programming a set

of seven EPROM bits. This feature can be used to compen-

sate for crystal variations or to obtain a more accurate synthe-

sized frequency.

The CY2037 uses EPROM programming with a simple 2-wire,

4-pin interface that includes V

SS

and V

DD

. Clock outputs can

be generated up to 200 MHz at 5V or up to 100 MHz at 3.3V.

The entire configuration can be reprogrammed one time allow-

ing programmed inventory to be altered or reused.

The CY2037 PLL die has been designed for very high resolu-

tion. It has a 12 bit feedback counter multiplier and a 10 bit

reference counter divider. This enables the synthesis of highly

accurate and stable output clock frequencies with zero or low

PPM. The clock can be further modified by eight output divider

options of 1, 2, 4, 8, 16, 32, 64 and 128. The divider input can

be selected as either the PLL or crystal oscillator output pro-

viding a total of sixteen separate output options. For further

flexibility, the ouput is selectable between TTL and CMOS duty

cycle levels.

The CY2037 also contains flexible power management con-

trol. The part includes both PWR_DWN and OE features with

integrated pull-up resistors. The PWR_DWN and OE modes

have an additional setting to determine timing (asynchronous

or synchronous) with respect to the output signal.

Controlled rise and fall times, unique output driver circuits, and

innovative circuit layout techniques enable the CY2037 to

have low jitter and accurate outputs making it suitable for most

PC, networking and consumer applications

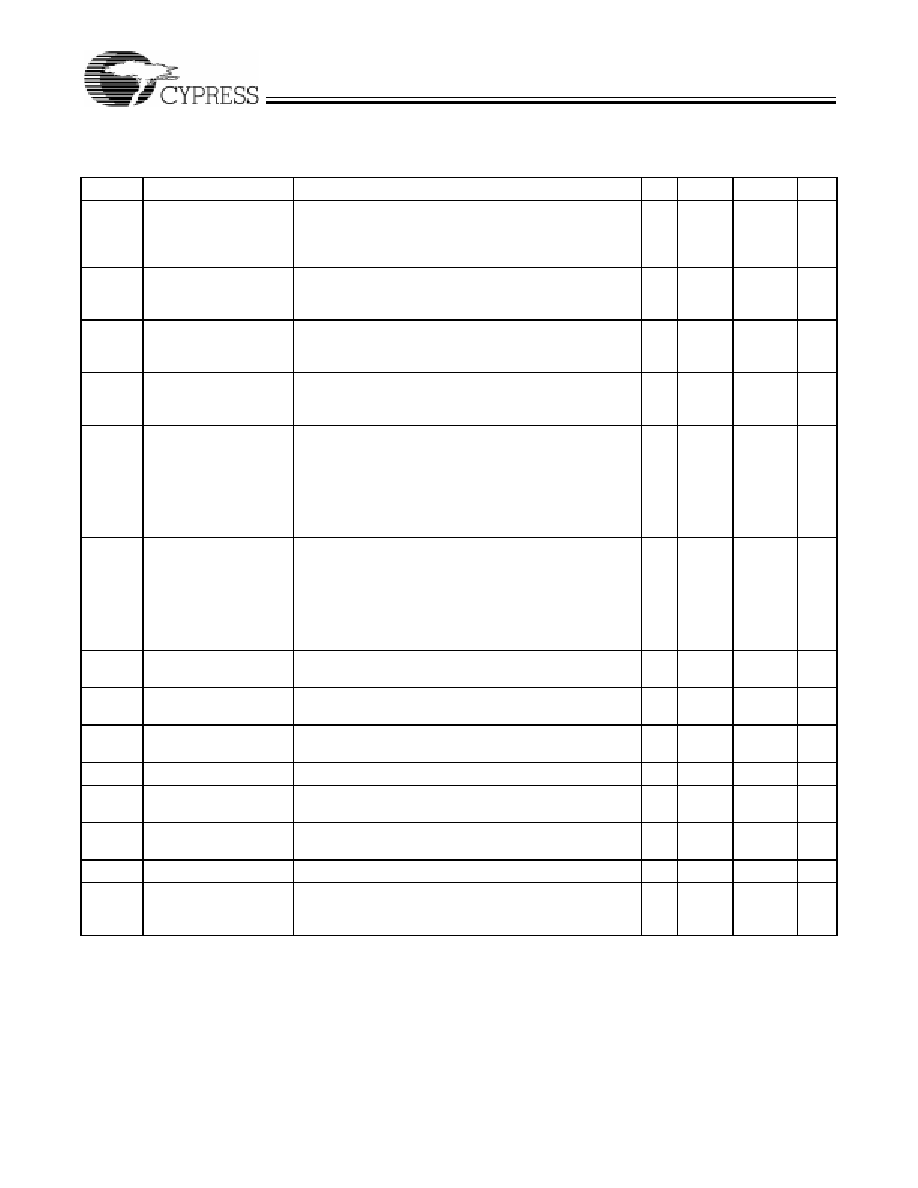

EPROM Configuration Block

The following table summarizes the features which are config-

urable by EPROM. Please refer to the "CY2037 Programming

Specification" for further details. The specification can be ob-

tained from your local Cypress representative.

PLL Output Frequency

The CY2037 contains a high resolution PLL with 12 bit multi-

plier and 10 bit divider.The output frequency of the PLL is de-

termined by the following formula:

where P is the feedback counter value and Q is the reference

counter value. P and Q are EPROM programmable values.

Power Management features

The CY2037 contains EPROM programmable PWR_DWN

and OE functions. If Powerdown is selected, all active circuitry

on the chip is shut down when the control pin goes low. The

output is forced to a hard low in this mode and the oscillator

and PLL circuits must re-lock when the part leaves the Power-

down mode. If Output Enable mode is selected, the output is

three-stated when the Control pin goes low. In this mode the

oscillator and PLL circuits continue to operate, allowing a rapid

return to normal operation when the Control input is

deasserted.

In addition, the PWR_DWN and OE modes can be pro-

grammed to occur synchronously or asynchronously with re-

spect to the output signal. When the asynchronous setting is

used, the powerdown or output three-state occurs immediately

(allowing for logic delays) irrespective of position in the clock

cycle. However, when the synchronous setting is used, the

part waits for a falling edge at the output before powerdown or

output enable is initiated, thus preventing output glitches.

Crystal Oscillator Tuning Circuit

The CY2037 contains a unique tuning circuit to fine-tune the

output frequency of the device. The tuning circuit consists of

an array of seven load capacitors on the input side of the os-

cillator drive inverter. The capacitor load values are EPROM

programmable and can be increased in small increments. As

the capacitor load is increased the circuit is fine-tuned to a

lower frequency. The capacitor load values vary from 0.17pF

to 8 pF for a 100:1 total control ratio. The tuning increments

are shown in the table below

Table 1. Crystal Tuning Increments

EPROM Adjustable Features

Feedback counter value (P)

Reference counter value (Q)

Output divider selection

Oscillator Tuning (load capacitance values)

Duty cycle levels (TTL or CMOS)

Power management mode (OE or PWR_DWN)

Power management timing

(synchronous or asynchronous)

+8pF +4.2pF +2.2pF +1.2pF +0.6pF +0.3pF +0.17pF

F

PLL

2

P

5

+

(

)

∑

Q

2

+

(

)

---------------------------

F

REF

∑

=

CY2037

PRELIMINARY

3

Crystal Oscillator Tuning Circuit

Die Pad Summary

Name

Die Pad

Description

V

DD

1

Digital voltage supply

AV

DD

2

Analog voltage supply, 3.3V or 5V

V

SS

8

Digital Ground

AV

SS

9

Analog Ground

X

D

3,4

Crystal connection, drain pad. Bond to crystal drain.

X

G

6

Crystal connection, gate pad. Bond to crystal gate.

PWR_DWN / OE 7

EPROM programmable power down or output enable pad. Serves as V

PP

in programming mode.

CLKOUT

10

Clock output. Also serves as three-state input during programming.

N/C

5

No Connect. Do not connect.

Device Functionality: Output Frequencies

Symbol

Description

Condition

Min.

Max.

Unit

Fo

Output frequency

V

DD

= 4.5≠5.5V

1

200

MHz

V

DD

= 3.0≠3.6V

1

100

MHz

V

DD

= 2.7≠3.6V

1

66

MHz

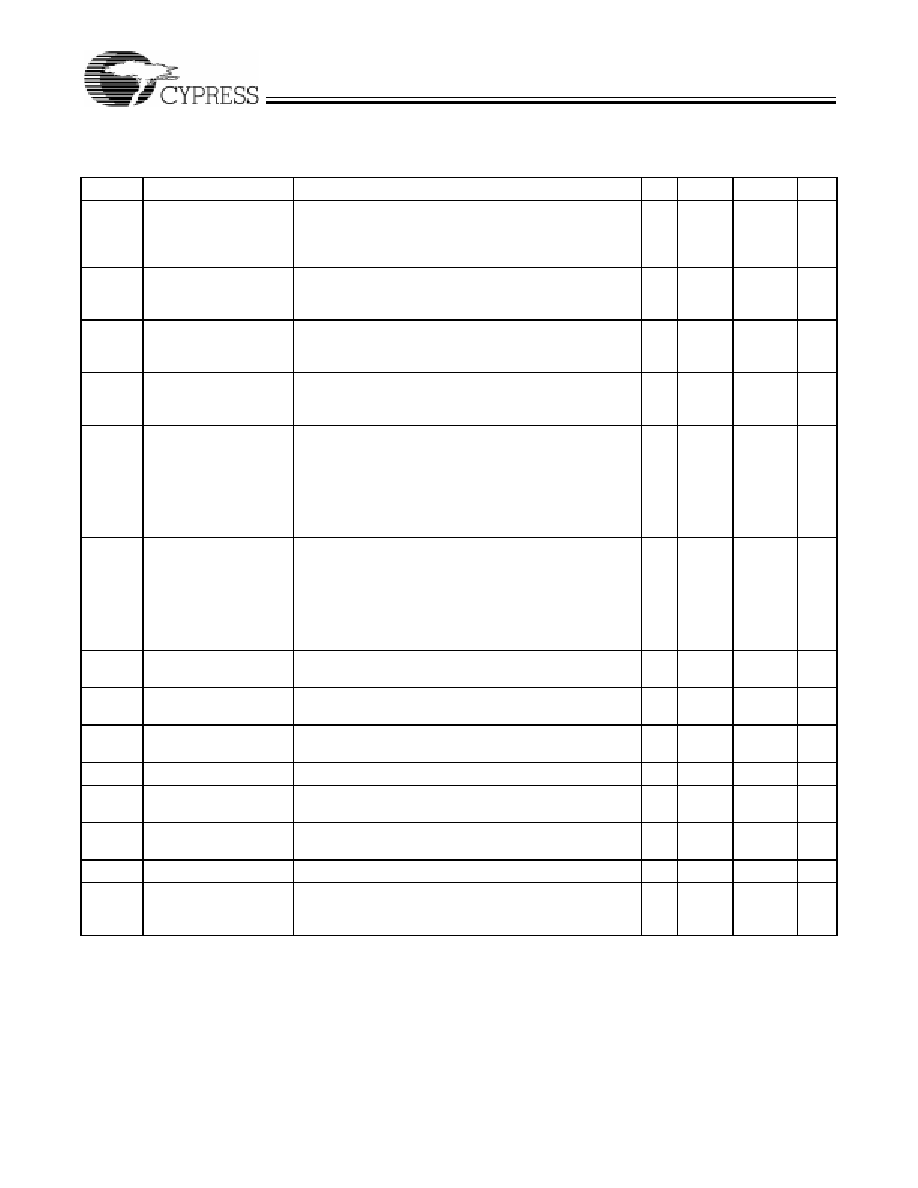

Symbol

Description

Min

Typ

Max

Unit

R

f

Feedback resistor, V

DD

= 4.5≠5.5V

Feedback resistor, V

DD

= 3.0≠3.6V

0.5

1.0

2

4

3.5

9.0

M

M

C

g

Gate capacitor

6.4

8

9.6

pF

C

d

Drain Capacitor

12

15

18

pF

C

0

Series Cap

0.14

0.17

0.20

pF

C

1

Series Cap

0.26

0.32

0.38

pF

C

2

Series Cap

0.49

0.61

0.73

pF

C

3

Series Cap

0.93

1.16

1.39

pF

C

4

Series Cap

1.77

2.21

2.65

pF

C

5

Series Cap

3.36

4.2

5.04

pF

C

6

Series Cap

6.4

8

9.6

pF

C

0

T

0

CD

0

C

1

T

1

CD

1

C

2

T

2

CD

2

C

3

T

3

CD

3

C

4

T

4

CD

4

C

5

T

5

CD

5

C

6

T

6

CD

6

C

g

C

d

R

f

EXTERNAL

TO DIE

LOCATED

CRYSTAL

CD = EPROM BIT

T = TRANSISTOR

C = LOAD CAPACITOR

CY2037

PRELIMINARY

4

Absolute Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Supply Voltage..................................................≠0.5 to +7.0V

Input Voltage.............................................. ≠0.5V to V

DD

+0.5

Storage Temperature (Non-Condensing) ... ≠55

∞

C to +150

∞

C

Junction Temperature ............................... ≠55

∞

C to +150

∞

C

Static Discharge Voltage ........................................... >2000V

(per MIL-STD-883, Method 3015)

Operating Conditions

Parameter

Description

Min.

Max.

Unit

AV

DD

, V

DD

Analog and Digital Supply Voltage

2.7

5.5

V

T

AJ

[1]

Operating Temperature, Junction

≠40

+100

∞

C

C

TTL

Max. Capacitive Load on outputs for TTL levels

V

DD

= 4.5≠5.5V, Output frequency = 1≠40 MHz

V

DD

= 4.5≠5.5V, Output frequency = 40≠125 MHz

V

DD

= 4.5≠5.5V, Output frequency = 125≠200 MHz

50

25

15

pF

pF

pF

C

CMOS

Max. Capacitive Load on outputs for CMOS levels

V

DD

= 4.5≠5.5V, Output frequency = 1≠66.6 MHz

V

DD

= 4.5≠5.5V, Output frequency = 66.6≠125 MHz

V

DD

= 4.5≠5.5V, Output frequency = 125≠200 MHz

V

DD

= 3.0≠3.6V, Output frequency = 1≠50 MHz

V

DD

= 3.0≠3.6V, Output frequency = 50≠100 MHz

V

DD

= 2.7≠3.6V, Output frequency = 1≠66.6 MHz

50

25

15

30

15

15

pF

pF

pF

pF

pF

pF

X

REF

Reference Frequency, input crystal

10

30

MHz

Electrical Characteristics

Over the Operating Range

Parameter Description

Test Conditions

Min.

Typ.

Max.

Unit

V

IL

Low-level Input Voltage

V

DD

= 4.5≠5.5V

V

DD

= 3.0≠3.6V

V

DD

= 2.7≠3.6V

0.8

0.2V

DD

0.2V

DD

V

V

V

V

IH

High-level Input Voltage

V

DD

= 4.5≠5.5V

V

DD

= 3.0≠3.6V

V

DD

= 2.7≠3.6V

2.0

0.5V

DD

0.5V

DD

V

V

V

V

OL

Low-level Output Voltage

V

DD

= 4.5≠5.5V, I

OL

= 16 mA

V

DD

= 3.0≠3.6V, I

OL

= 8 mA

V

DD

= 2.7≠3.6V, I

OL

= 8 mA

0.4

0.4

0.4

V

V

V

V

OHCMOS

High-level Output Voltage,

CMOS levels

V

DD

= 4.5≠5.5V, I

OH

= ≠16 mA

V

DD

= 3.0≠3.6V, I

OH

= ≠8 mA

V

DD

= 2.7≠3.6V, I

OH

= ≠8 mA

V

DD

≠0.4

V

DD

≠0.4

V

DD

≠0.4

V

V

V

V

OHTTL

High-level Output Voltage,

TTL levels

V

DD

= 4.5≠5.5V, I

OH

= ≠16 mA

2.4

V

I

IL

Input Low Current

V

IN

= 0V

10

µ

A

I

IH

Input High Current

V

IN

= V

DD

5

µ

A

I

DD

Power Supply Current,

Unloaded

V

DD

= 4.5≠5.5V, Output frequency <= 200 MHz

V

DD

= 3.0≠3.6V, Output frequency <= 100 MHz

V

DD

= 2.7≠3.6V, Output frequency <= 66.6 MHz

45

25

20

mA

mA

mA

I

DDS

Stand-by current

V

DD

= 4.5≠5.5V

V

DD

= 3.0≠3.6V

V

DD

= 2.7≠3.6V

10

2

2

50

20

20

µ

A

µ

A

µ

A

Rup

Input pull-Up resistor

V

DD

= 4.5≠5.5V, V

IN

= 0V

V

DD

= 4.5≠5.5V, V

IN

= 0.7V

DD

1.1

15

3.0

30

8.0

100

M

k

Note:

1.

This product is sold in die form so operating conditions are specified for the die, or junction temperature

CY2037

PRELIMINARY

5

Output Clock Switching Characteristics

Over the Operating Range

Symbol

Description

Test Conditions

Min

Typ

Max

Unit

t

1w

Output Duty Cycle at

1.4V, V

DD

= 4.5≠5.5V

t

1w

= t

1A

˜

t

1B

1≠27 MHz, C

L

<= 50 pF

27≠80 MHz, C

L

<= 15pF

27≠125 MHz, C

L

<= 25pF

125≠200 MHz, C

L

<= 15pF

45

45

40

40

55

55

60

60

%

%

%

%

t

1x

Output Duty Cycle at

V

DD

/2, V

DD

= 4.5≠5.5V

t

1x

= t

1A

˜

t

1B

1≠66.6 MHz, C

L

<= 50 pF

66.6≠125 MHz, C

L

<= 25 pF

125≠200 MHz, C

L

<= 15pF

45

40

40

55

60

60

%

%

%

t

1y

Output Duty Cycle at

V

DD

/2, V

DD

= 3.0≠3.6

t

1y

= t

1A

˜

t

1B

1≠50 MHz, C

L

<= 30 pF

50≠100 MHz, C

L

<= 15pF

45

40

55

60

%

%

t

1z

Output Duty Cycle at

V

DD

/2, V

DD

= 2.7≠3.6V

t

1z

= t

1A

˜

t

1B

1≠40 MHz, C

L

<= 15 pF

40≠66.6 MHz, C

L

<= 15 pF

45

40

55

60

%

%

t

2

Output Clock Rise time

Between 0.8 ≠2.0V, V

DD

= 4.5V≠5.5V, C

L

= 50 pF

Between 0.8 ≠2.0V, V

DD

= 4.5V≠5.5V, C

L

= 25 pF

Between 0.8 ≠2.0V, V

DD

= 4.5V≠5.5V, C

L

= 15 pF

Between 0.2V

DD

≠ 0.8V

DD

, V

DD

= 4.5V≠5.5V, C

L

= 50 pF

Between 0.2V

DD

≠ 0.8V

DD

, V

DD

= 3.0V≠3.6V, C

L

= 30 pF

Between 0.2V

DD

≠ 0.8V

DD

, V

DD

= 3.0V≠3.6V, C

L

= 15 pF

Between 0.2V

DD

≠ 0.8V

DD

, V

DD

= 2.7V≠3.6V, C

L

= 15 pF

1.8

1.2

0.9

3.4

4.0

2.4

4.0

ns

ns

ns

ns

ns

ns

ns

t

3

Output Clock Fall time

Between 0.8V≠2.0V, V

DD

= 4.5V≠5.5V, C

L

= 50 pF

Between 0.8 ≠2.0V, V

DD

= 4.5V≠5.5V, C

L

= 25 pF

Between 0.8 ≠2.0V, V

DD

= 4.5V≠5.5V, C

L

= 15 pF

Between 0.2V

DD

≠ 0.8V

DD

, V

DD

= 4.5V-5.5V, C

L

= 50 pF

Between 0.2V

DD

≠ 0.8V

DD

, V

DD

= 3.0V≠3.6V, C

L

= 30 pF

Between 0.2V

DD

≠ 0.8V

DD

, V

DD

= 3.0V≠3.6V, C

L

= 15 pF

Between 0.2V

DD

≠ 0.8V

DD

, V

DD

= 2.7V≠3.6V, C

L

= 15 pF

1.8

1.2

0.9

3.4

4.0

2.4

4.0

ns

ns

ns

ns

ns

ns

ns

t

4

Start-up time out of

power-down

PWR_DWN or OE pin LOW to HIGH

[2]

1

2

ms

t

5a

Power Down delay time

(synchronous setting)

PWR_DWN pin HIGH to output LOW

(T=frequency oscillator period)

T/2

T+10

ns

t

5b

Power Down delay time

(asynchronous setting)

PWR_DWN pin HIGH to output LOW

10

15

ns

t

6

Power Up time

From power on

[2]

1

2

ms

t

7a

Output disable time

(synchronous setting)

OE pin HIGH to output Hi-Z

(T=frequency oscillator period)

T/2

T+10

ns

t

7b

Output disable time

(asynchronous setting)

OE pin HIGH to output Hi-Z

10

15

ns

t

8

Output enable time

PWR_DWN or OE pin LOW to HIGH

100

ns

t

9

Peak-to-Peak Period

Jitter

V

DD

= 4.5V≠5.5V, Fo > 33 MHz, VCO > 100 MHz

V

DD

= 3.0V≠3.6V, Fo > 33 MHz, VCO >100 MHz

V

DD

= 3.0V≠5.5V, Fo <33 MHz

±50

±75

±100

±100

±125

±250

ps

ps

ps

Note:

2.

Oscillator start time cannot be guaranteed for all crystal types. This specification is for operation with AT cut crystals with ESR < 70 ohms.

CY2037

PRELIMINARY

6

Switching Waveforms

Notes:

3.

In synchronous mode the powerdown or output 3-state is not initiated until the next falling edge of the output clock.

4.

In asynchronous mode the powerdown or output 3-state occurs within 25ns irrespective of position in the ouput clock cycle.

Duty Cycle Timing (t

1w,

t

1x,

t

1y,

t

1z

)

t

1A

t

1B

OUTPUT

Output Rise/Fall Time

OUTPUT

t

2

V

DD

0V

t

3

Power Down Timing (synchronous and asynchronous modes)

CLKOUT

V

DD

t

4

1/f

t

5a

V

IL

V

IH

POWER

DOWN

0V

1/f

t

5b

CLKOUT

T

(synchronous

[3

]

)

(asynchronous

[4

]

)

Power Up Timing

CLKOUT

V

DD

t

6

1/f

V

DD

-10%

POWER

UP

0V

min 2ns

CY2037

PRELIMINARY

© Cypress Semiconductor Corporation, 1997. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use

of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize

its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress

Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.

Ordering Information

Document #: 38≠00679

Die Size Dimensions

Switching Waveforms

(continued)

CLKOUT

V

DD

OUTPUT

ENABLE

0V

Output Enable Timing (synchronous and asynchronous modes)

V

IL

V

IH

t

7a

t

8

High Impedance

CLKOUT

t

7b

t

8

High Impedance

T

(synchronous

[3

]

)

(asynchronous

[4

]

)

Ordering Code

Type

Operating Range

CY2037WAF

Wafer

Industrial

x by y

1497x1105 microns

Wafer Thickness

14 ±0.5 mils