256 Megabit CMOS DRAM

DPnnD8MX32RY5

PRELIMINARY

DESCRIPTION:

The DPnnD8MX32RY5 is the 8 Meg x 32 Dynamic RAM

module that utilize the new and innovative space saving TSOP

stacking technology. The module is constructed of four 4 Meg

x 16 Dynamic RAM's that are configured as 2 banks of 4 Meg x

32.

The DPnnD8MX32RY5 provides for a compatible upgrade path

to lower density compatible modules. The module features high

speed access times, common data inputs and outputs, and three

standard refresh modes.

FEATURES:

∑

Access Times: 60, 70, 80ns (max.)

∑

5.0V or 3.3V Supply

∑

Common Data Inputs and Outputs

∑

EDO or Fast Page Mode Capability

∑

4096 Cycles / 64 ms

∑

3 Variations of Refresh: - RAS only Refresh

- CAS before RAS Refresh

- Hidden Refresh

∑

Package: TSOP Leadless Stack

PIN-OUT DIAGRAM

NOTE: Pin 43 and Pin 46 are connected together,

Pin 42 and Pin 45 are connected together.

FUNCTIONAL BLOCK DIAGRAM

NOTE: LCAS controls DQ0-DQ15, UCAS controlls DQ16-DQ31.

2Mx32, 50 - 80ns, TSTACK

30A165-15

A

This document contains information on a product presently under

development at Dense-Pac Microsystems, Inc. Dense-Pac reserves the

right to change products or specifications herein without prior notice.

PIN NAMES

A0 - A11

Row Address:

A0 - A11

Column Address: A0 - A9

Refresh Address: A0 - A11

DQ0 - DQ31

Data In / Data Out

UCAS

Upper Column Addres Strobe

LCAS

Lower Column Addres Stobe

RAS0 - RAS1

Row Address Enables

WE0 - WE1

Data Write Enables

OE0 - OE1

Data Output Enables

V

DD

Power Supply (+5V)

V

SS

Ground

N.C.

No Connect

30A165-15

REV. A

1

DPnnD8MX32RY5

Dense-Pac Microsystems, Inc.

PRELIMINARY

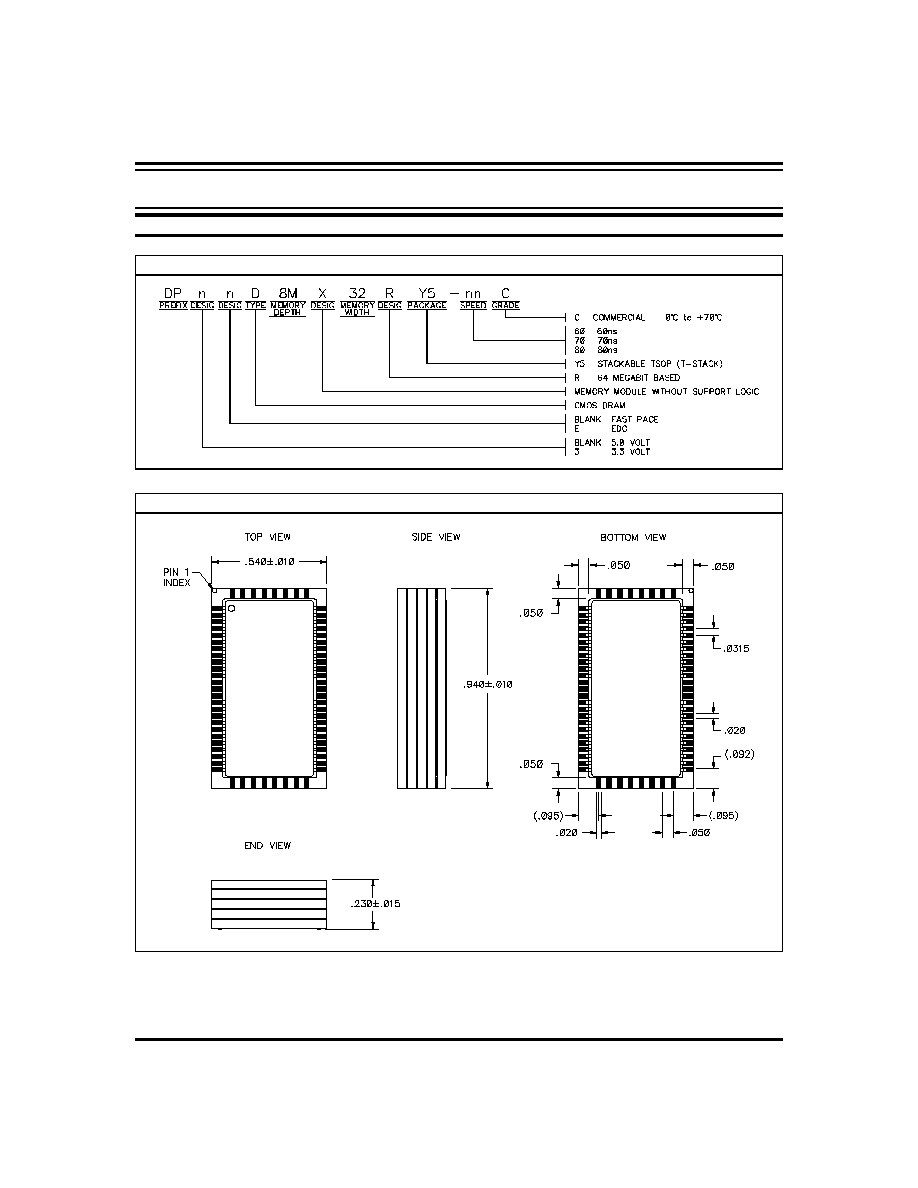

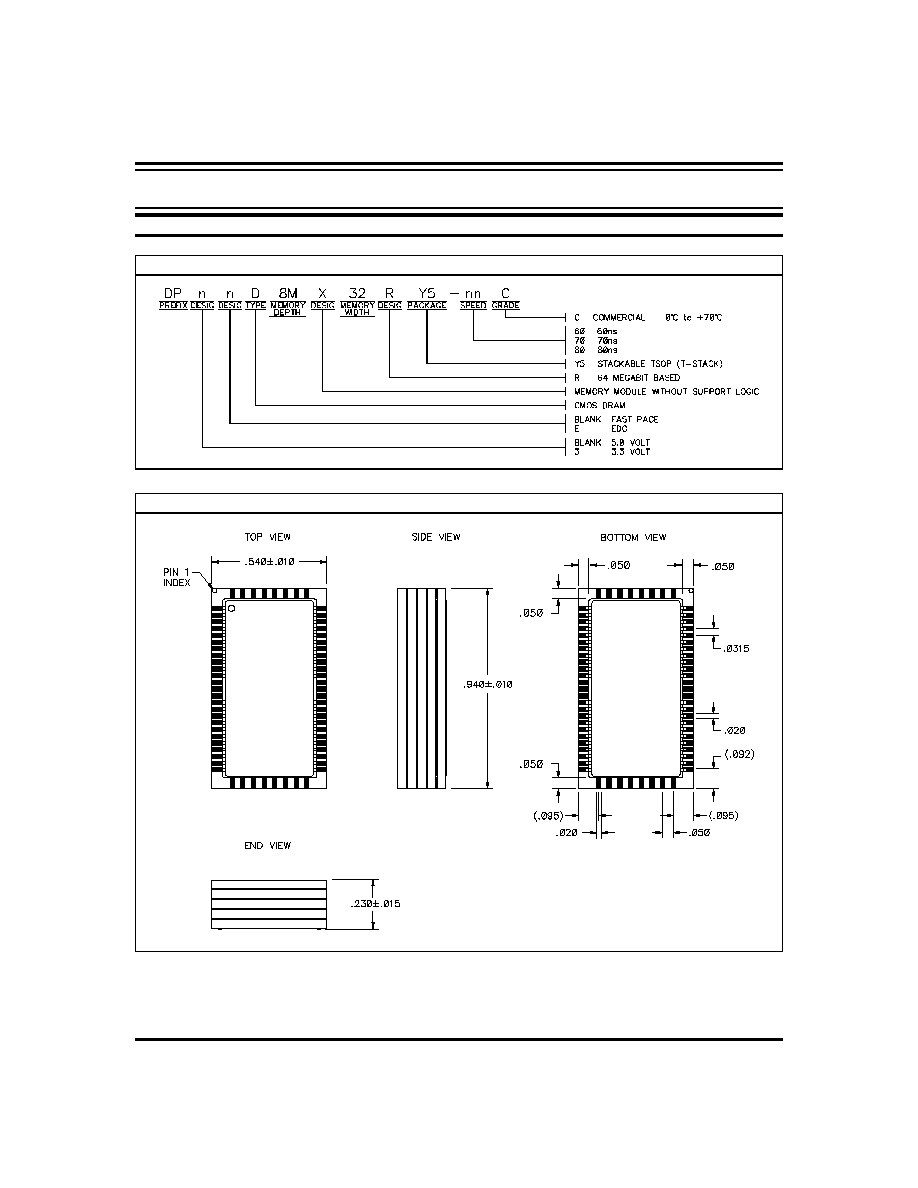

MECHANICAL DRAWING

Dense-Pac Microsystems, Inc.

7321 Lincoln Way ø Garden Grove , California 92841-1431

(714) 898-0007 (800) 642-4477

(Outside CA)

ø FAX: (714) 897-1772 ø http://www.dense-pac.com

ORDERING INFORMATION

30A165-15

REV. A

2