| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: BT869KRF | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- Bt868/Bt869

- Functional Block Diagram

- Distinguishing Features

- Applications

- Table of Contents

- List of Figures

- List of Tables

- 1.0 Functional Description

- 1.1 Pin Descriptions

- 1.2 GUI Controller Programmability and Frequency Requirement

- 1.3 Circuit Description

- 1.3.1 Overview

- 1.3.2 Reset

- 1.3.3 Timing Registers

- 1.3.4 Device Initialization

- 1.3.5 Auto Configuration

- 1.3.6 Clocking and Timing Generation

- 1.3.7 Master and Slave Modes

- 1.3.8 Input Formats

- 1.3.9 Pixel Input Timing

- 1.3.10 Output Modes

- 1.3.11 YCrCb Inputs

- 1.3.12 RGB Inputs

- 1.3.13 Video Amplitude Scaling

- 1.3.14 Input Pixel Horizontal Sync

- 1.3.15 Input Pixel Vertical Sync

- 1.3.16 Input Pixel Blanking

- 1.3.17 Overscan Compensation and Flicker Filtering

- 1.3.18 VGA Compatibility

- 1.3.19 Analog Horizontal Sync

- 1.3.20 Analog Vertical Sync

- 1.3.21 Analog Video Blanking

- 1.3.22 Video Standards

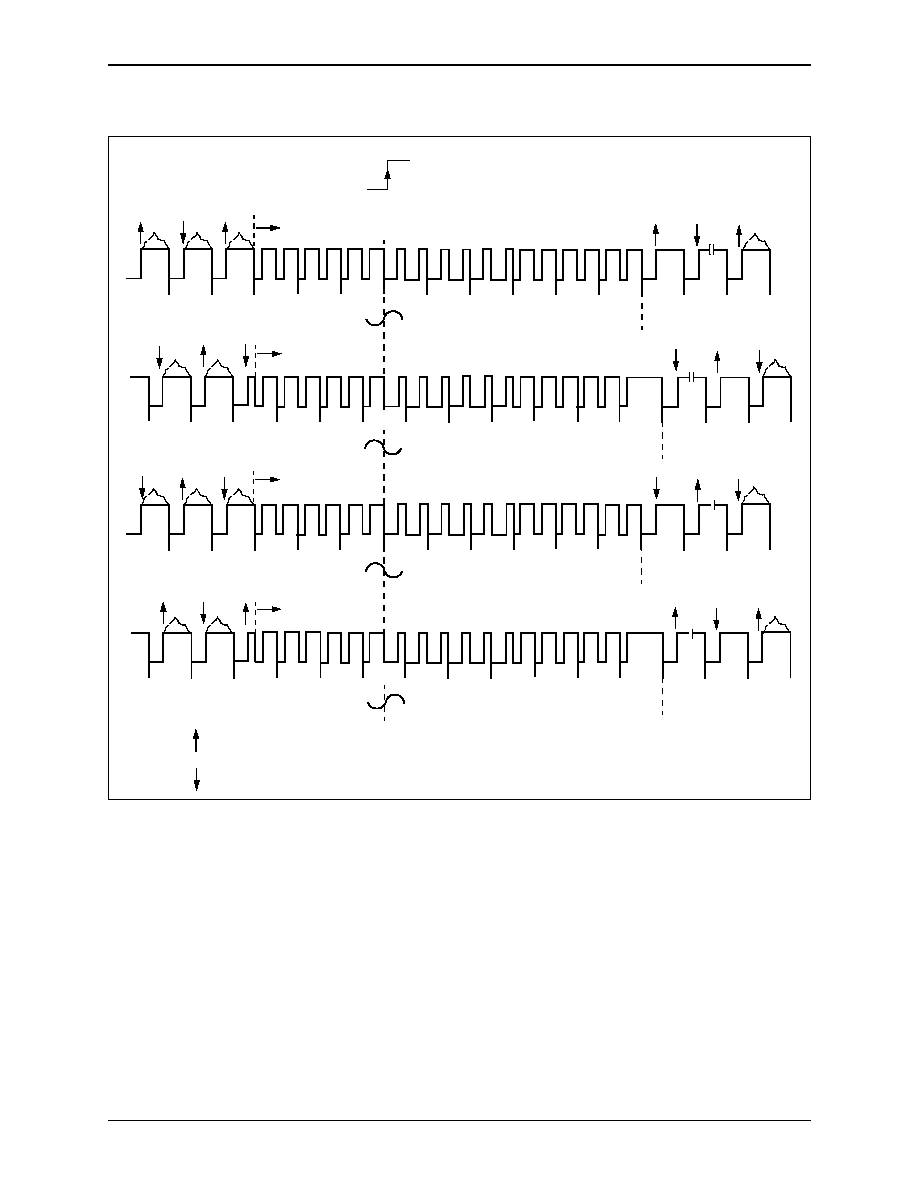

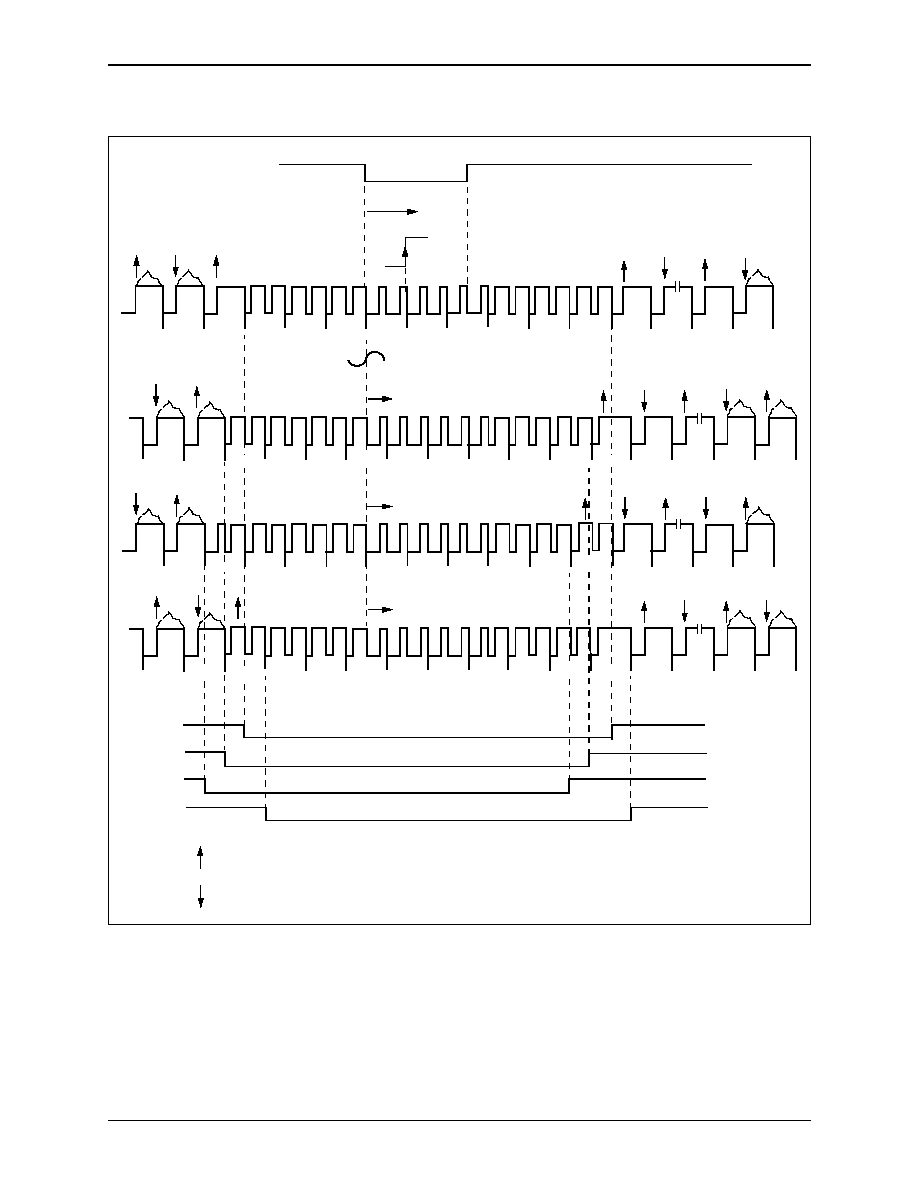

- Figure 1�5. Interlaced 525-Line (NTSC) Video Timing

- Figure 1�6. Interlaced 525-Line (PAL-M) Video Timing

- Figure 1�7. Interlaced 625-Line (PALÖB, D, G, H, I, Nc) Video Timing (Fields 1Ö4)

- Figure 1�8. Interlaced 625-Line (PALÖB, D, G, H, I, Nc) Video Timing (Fields 5Ö8)

- Figure 1�9. Interlaced 625-Line (PALÖN) Video Timing (Fields 1Ö4)

- Figure 1�10. Interlaced 625-Line (PALÖN) Video Timing (Fields 5Ö8)

- Figure 1�11. Noninterlaced 262-Line (NTSC) Video Timing

- Figure 1�12. Noninterlaced 262-Line (PALÖM) Video Timing

- Figure 1�13. Noninterlaced 312-Line (PALÖB, D, G, H, I, N, Nc) Video Timing

- 1.3.23 Subcarrier Generation

- 1.3.24 Burst Generation

- 1.3.25 Chrominance Disable

- 1.3.26 Digital Processing

- 1.3.27 Subcarrier Phasing

- 1.3.28 Noninterlaced Operation

- 1.3.29 Closed Captioning

- 1.3.30 Internal Color Bars

- 1.3.31 Macrovision Encoding

- 1.3.32 Outputs

- 1.3.33 Output Connection Status

- 1.3.34 Output Filtering and SINX/X Compensation

- 1.3.35 Power-Down Modes

- 1.3.36 Serial Interface

- 2.0 Internal Registers

- 3.0 PC Board Considerations

- 4.0 Parametric Information

- Appendix A . Scaling and I/O Timing Register Calculations

- Table A-1. Video Formats

- Table A-2. Constant Values Dependent on Encoding Mode

- Figure A-1. Overscan Compensation, 640x480 NTSC, 20 Clock Hblank

- Figure A-2. Overscan Compensation, 640x480 PAL, 20 Clock Hblank

- Figure A-3. Overscan Compensation, 800x600 NTSC

- Figure A-4. Overscan Compensation, 800x600 PAL

- Table A-3. Overscan Values, 640x480 NTSC, 1 Pixel Resolution, 2.5 ms Hblank� (1 of 3)

- Table A-4. Overscan Values, 640x480 NTSC, 8 Pixel Resolution, 2.5 ms Hblank�

- Table A-5. Overscan Values, 640x480 NTSC, 9 Pixel Resolution, 2.5 ms Hblank�

- Table A-6. Overscan Values, 640x480 PAL, 1 Pixel Resolution, 2.5 ms Hblank� (1 of 4)

- Table A-7. Overscan Values, 640x480 PAL, 8 Pixel Resolution, 2.5 ms Hblank (1 of 2)

- Table A-8. Overscan Values, 640x480 PAL, 9 Pixel Resolution, 2.5 ms Hblank�

- Table A-9. Overscan Values, 800x600 NTSC� (1 of 5)

- Table A-10. Overscan Values, 800x600, PAL, > 2.5 ms Hblank� (1 of 3)

- Appendix B . Approved Crystal Vendors

- Sales Offices

Data Sheet

100123B

September 2000

Bt868/Bt869

Flicker-Free Video Encoder with Ultrascale

TM

Technology

The Bt868/869 is specifically designed for video systems requiring the generation of

high-quality flicker-free composite and Y/C (S-video) signals from various YCrCb or

RGB digital streams. The Bt868/869 accepts any input format from 640 x 480 to

800 x 600 resolution.

The Bt868/869 uses Conexant's UltraScaleTM technology to provide the most

advanced vertical and horizontal scaling necessary for the display of non-interlaced

data on interlaced devices such as the TV. The UltraScaleTM technology converts the

lines of input pixel data to the appropriate number of output lines for producing a

full-screen, high-quality image.

The Bt868/869 performs 5-line vertical filtering, which includes poly phase

interpolation scaling for overscan compensation and flicker filtering. Horizontal

scaling for overscan compensation is achieved by altering the encoder clock

frequency. This approach preserves all of the high frequency components of the

input signals, which are essential for the highest quality display of text intensive

images such as web pages on TVs. The amount of flicker filtering and overscan

compensation is programmable.

Worldwide video standards are supported, including NTSC-M (N. America,

Taiwan, Japan), PAL-B,D,G,H,I (Europe, Asia), PAL-M (Brazil), PAL-N (Uruguay,

Paraguay), and PAL-Nc (Argentina). Bt868 and Bt869 are functionally identical, with

the exception that Bt869 can output Macrovision Level 7.0 anticopy algorithm.

Functional Block Diagram

Input

Flicker

FIFO

Video

XTAL

PLL

DAC

DACA

DACB

Internal

COMP

FSADJUST

VREF

BIAS

VBIAS

P[23:0]

XTALIN

XTALOUT

CLKO

CLKI

SIC

SID

ALTADDR

HSYNC*

VSYNC*

BLANK*

FIELD

RESET*

SLEEP

SLAVE

PAL

MUX

Encoder

Color Space

DACC

Timing

Serial

Clock

DEMUX

Interface

Filter/Scaler

Conversion

Reference

Generation

OSC

GEN

Distinguishing Features

∑

Digital RGB or YCrCb non-interlaced

input to interlaced or non-interlaced

analog TV output modes:

YCrCb Modes:

≠ 16-bit 4:2:2 multiplexed 8-bit

≠ 24-bit 4:4:4 multiplexed 12-bit

≠ 24-bit 4:4:4 non-multiplexed 24-bit

RGB Modes:

≠ 15/16 bit 5:6:5 RGB multiplexed 8-bit

≠ 24-bit 8:8:8 RGB mulitplexed 12-bit

≠ 24-bit 8:8:8 RGB non-multiplexed

24-bit

∑

Digital RGB non-interlaced input to

analog RGB noninterlaced (VGA/SVGA)

output modes:

≠ 15/16 bit 5:6:5 RGB multiplexed 8-bit

≠ 24-bit 8:8:8 RGB mulitplexed 12-bit

≠ 24-bit 8:8:8 RGB non-multiplexed

24-bit

∑

Support for NTSC/PAL outputs in the

following modes:

≠ Interlaced and non-interlaced outputs

≠ S-video output (simultaneous with

composite NTSC or PAL outputs)

≠ Component YUV analog output mode

∑

5-line vertical filtering scaling for

overscan compensation and flicker

filtering

∑

CCIR601 compatible input mode

∑

Luma and chroma comb filtering

∑

3 x 10-bit DACs

∑

6 MHz Luma bandwidth

∑

Macrovision 7.0 copy protection

∑

80-pin PQFP package

∑

3.3 V operation with 5 V tolerant IOs

∑

2-line serial programming interface

∑

Power-Down modes

∑

Master/slave video timing operation

∑

TV connected register flag

∑

Automatic configuration

Applications

∑

Desktop/Portable PCs with TV-Out

∑

Living-room PCs

∑

Internet PC/TVs

∑

Internet Appliances

100123B

Conexant

© 2000,

Conexant Systems, Inc.

All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are

provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no

responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at

any time, without notice. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for

conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as

provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING

TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A

PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY

PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE

ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE

MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL

DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE

OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling

Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages

resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: ConexantTM, the Conexant C symbol, and "What's Next in Communications

Technologies"TM. Product names or services listed in this publication are for identification purposes only, and may be trademarks of

third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at

www.conexant.com

, which is

incorporated by reference.

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and

suggestions to

tech.pubs@conexant.com

. For technical questions, contact your local Conexant

sales office

or field applications

engineer.

Ordering Information

Model Number

Package

Ambient Temperature Range

Reduced Features

Bt868KRF

80-pin PQFP

0

∞

C to +70

∞

C

No Macrovision Feature

Bt869KRF

80-pin PQFP

0

∞

C to +70

∞

C

--

100123B

Conexant

iii

Table of Contents

List of Figures

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

List of Tables

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ix

1.0

Functional Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1

Pin Descriptions

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.2

GUI Controller Programmability and Frequency Requirement

. . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.3

Circuit Description

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.3.1

Overview

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.3.2

Reset

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.3.3

Timing Registers

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.3.4

Device Initialization

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.3.5

Auto Configuration

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1.3.6

Clocking and Timing Generation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1.3.7

Master and Slave Modes

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.3.8

Input Formats

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

1.3.9

Pixel Input Timing

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

1.3.10

Output Modes

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

1.3.11

YCrCb Inputs

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

1.3.12

RGB Inputs

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

1.3.13

Video Amplitude Scaling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

1.3.14

Input Pixel Horizontal Sync

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

1.3.15

Input Pixel Vertical Sync

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

1.3.16

Input Pixel Blanking

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

1.3.17

Overscan Compensation and Flicker Filtering

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

1.3.18

VGA Compatibility

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

1.3.19

Analog Horizontal Sync

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

1.3.20

Analog Vertical Sync

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

1.3.21

Analog Video Blanking

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

1.3.22

Video Standards

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

1.3.23

Subcarrier Generation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-29

1.3.24

Burst Generation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-30

1.3.25

Chrominance Disable

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-30

1.3.26

Digital Processing

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-30

1.3.27

Subcarrier Phasing

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-31

Table of Contents

Bt868/Bt869

Flicker-Free Video Encoder with Ultrascale

TM

Technology

iv

Conexant

100123B

1.3.28

Noninterlaced Operation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-31

1.3.29

Closed Captioning

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-32

1.3.30

Internal Color Bars

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-32

1.3.31

Macrovision Encoding

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-32

1.3.32

Outputs

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-33

1.3.33

Output Connection Status

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-33

1.3.34

Output Filtering and SINX/X Compensation

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-33

1.3.35

Power-Down Modes

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-34

1.3.36

Serial Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-34

2.0

Internal Registers

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.1

Essential Registers

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2

Writing Addresses

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.3

Reading Information

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

3.0

PC Board Considerations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.1

Component Placement

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2

Power and Ground Planes

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.3

Decoupling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.3.1

Device Decoupling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.3.2

Power Supply Decoupling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.3.3

COMP Decoupling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.3.4

VREF Decoupling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.3.5

VBIAS Decoupling

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.4

Signal Interconnect

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.4.1

Digital Signal Interconnect

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.4.2

Analog Signal Interconnect

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.5

Applications Information

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.5.1

Electrostatic Discharge and Latchup Considerations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.5.2

Clock and Subcarrier Stability

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.5.3

Filtering Radio Frequency Modulator Connection

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.6

Bt868/Bt869 Evaluation Board

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.7

Serial Interface

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

3.7.1

Data Transfer on the Serial Interface Bus

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

4.0

Parametric Information

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1

DC Electrical Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2

AC Electrical Parameters

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

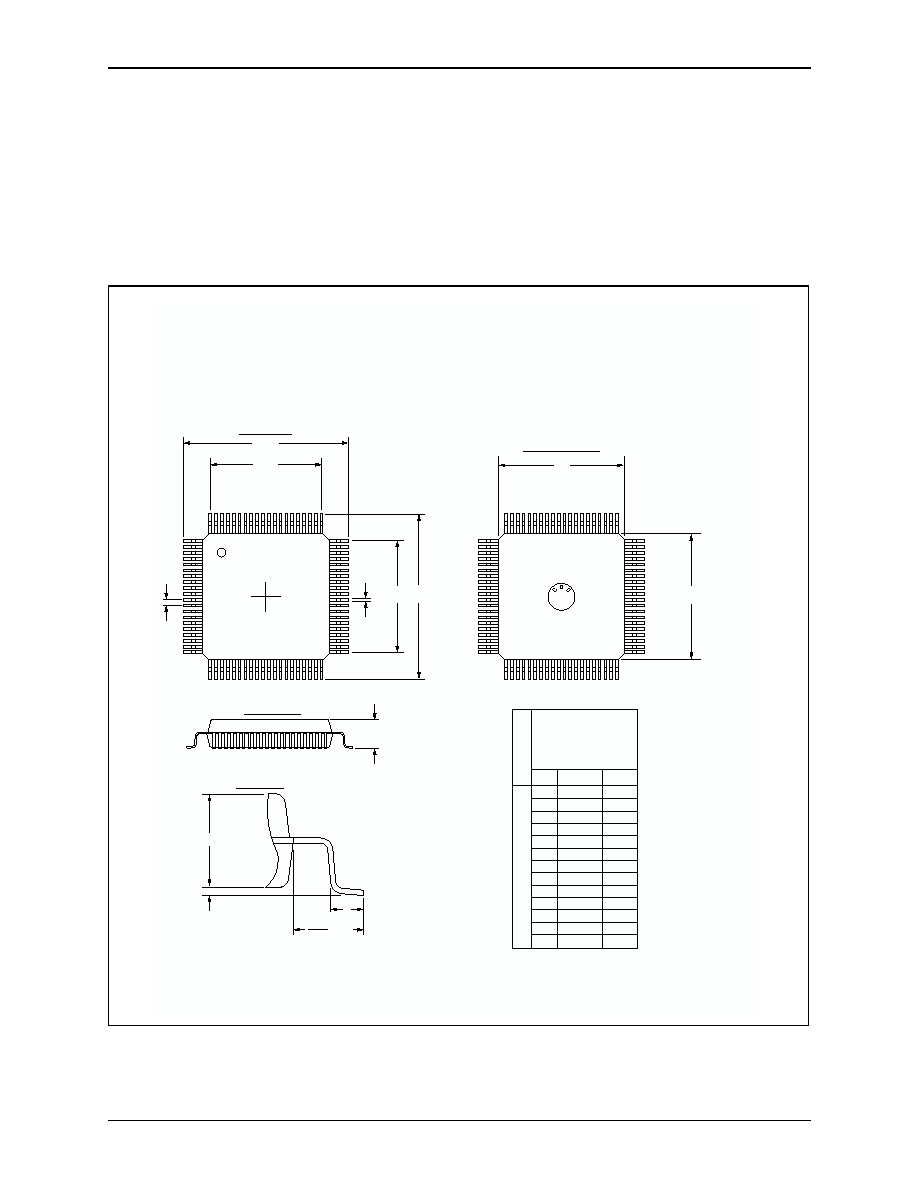

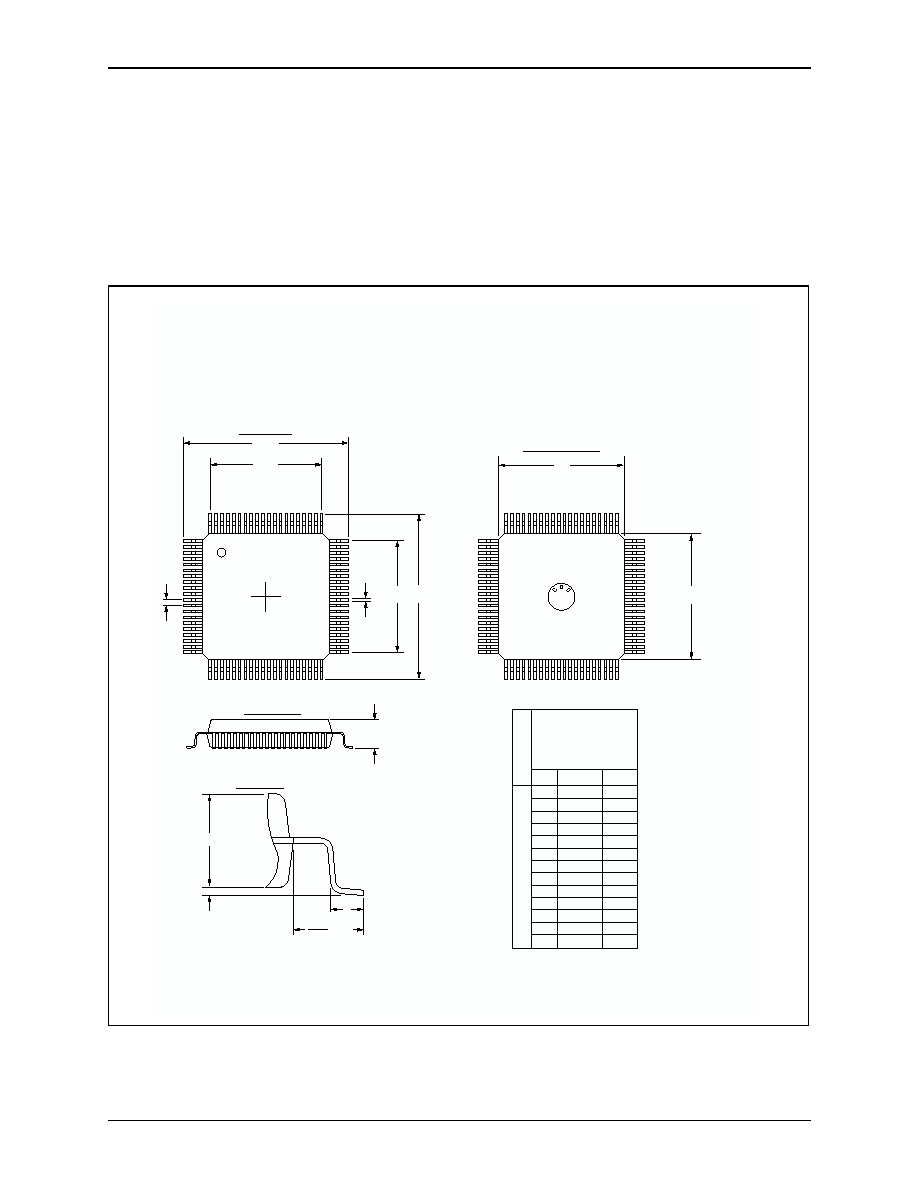

4.3

Mechanical Drawing

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Appendix A. Scaling and I/O Timing Register Calculations

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Appendix B. Approved Crystal Vendors

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-1

Bt868/Bt869

List of Figures

Flicker-Free Video Encoder with Ultrascale

TM

Technology

100123B

Conexant

vii

List of Figures

Figure 1-1.

Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

Figure 1-2.

Flicker Filter Control Diagram--External Use . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

Figure 1-3.

Encoder Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

Figure 1-4.

Decimation Filter at Fs=27 MHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

Figure 1-5.

Interlaced 525-Line (NTSC) Video Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-22

Figure 1-6.

Interlaced 525-Line (PAL-M) Video Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-23

Figure 1-7.

Interlaced 625-Line (PAL≠B, D, G, H, I, Nc) Video Timing (Fields 1≠4) . . . . . . . . . . . . . . . 1-24

Figure 1-8.

Interlaced 625-Line (PAL≠B, D, G, H, I, Nc) Video Timing (Fields 5≠8) . . . . . . . . . . . . . . . 1-25

Figure 1-9.

Interlaced 625-Line (PAL≠N) Video Timing (Fields 1≠4) . . . . . . . . . . . . . . . . . . . . . . . . . . 1-26

Figure 1-10.

Interlaced 625-Line (PAL≠N) Video Timing (Fields 5≠8) . . . . . . . . . . . . . . . . . . . . . . . . . . 1-27

Figure 1-11.

Noninterlaced 262-Line (NTSC) Video Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-28

Figure 1-12.

Noninterlaced 262-Line (PAL≠M) Video Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-28

Figure 1-13.

Noninterlaced 312-Line (PAL≠B, D, G, H, I, N, Nc) Video Timing . . . . . . . . . . . . . . . . . . . 1-29

Figure 1-14.

Three-Stage Chroma Filter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-30

Figure 1-15.

Luminance Upsampling Filter Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-31

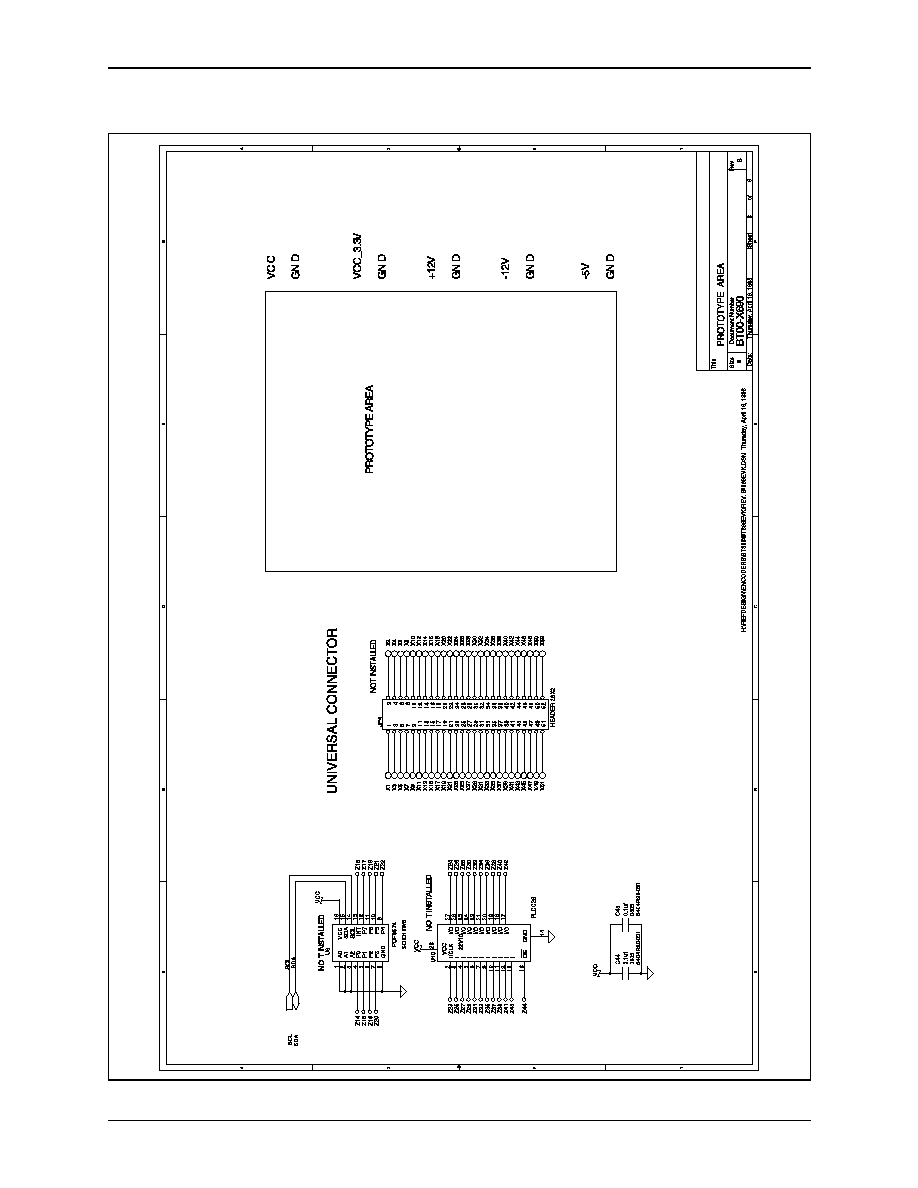

Figure 3-1.

Power Plane Illustration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

Figure 3-2.

Connection Diagram for Output Filters and Other Key Passive Components . . . . . . . . . . . . 3-3

Figure 3-3.

Complete Bt868/Bt869 Recommended Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

Figure 3-4.

Bt868/Bt869 Evaluation Board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

Figure 3-5.

SID/SIC Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

Figure 4-1.

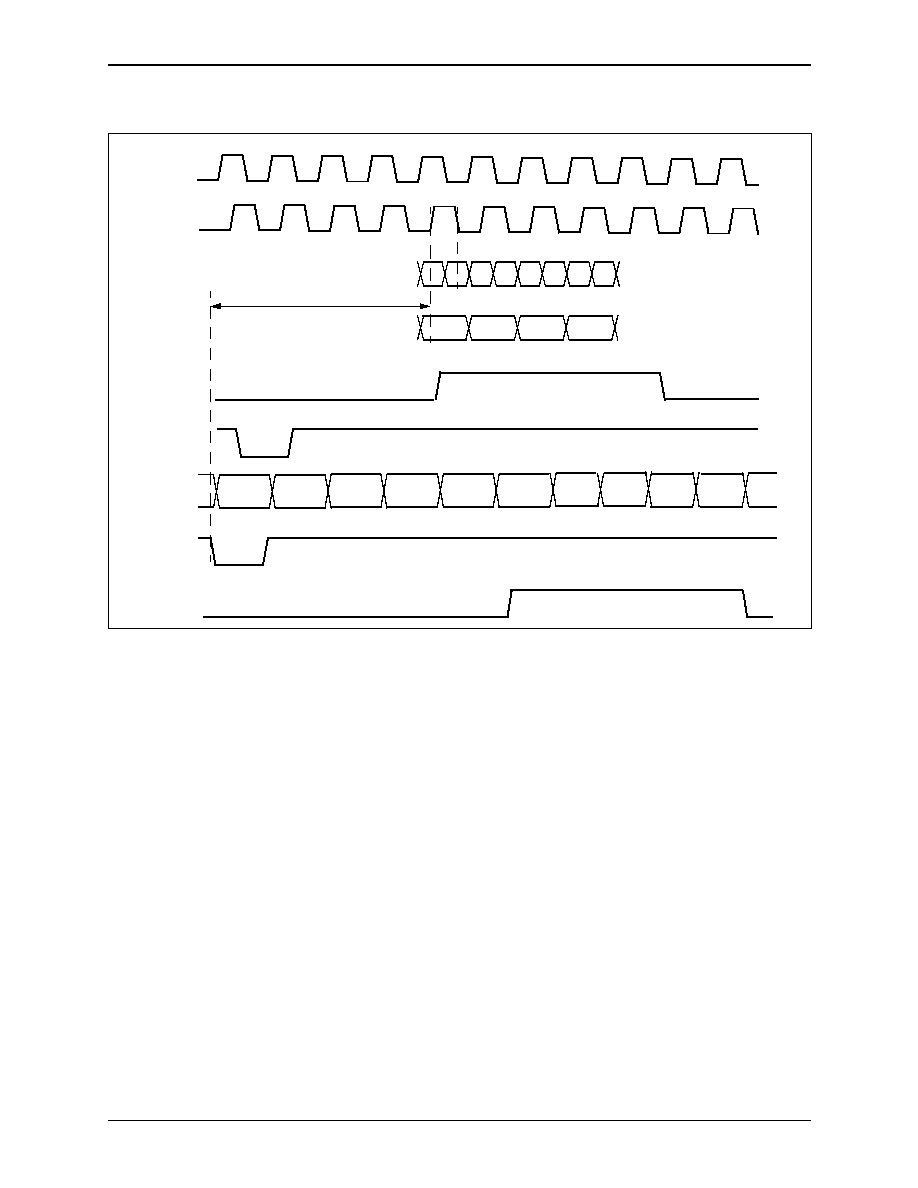

Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

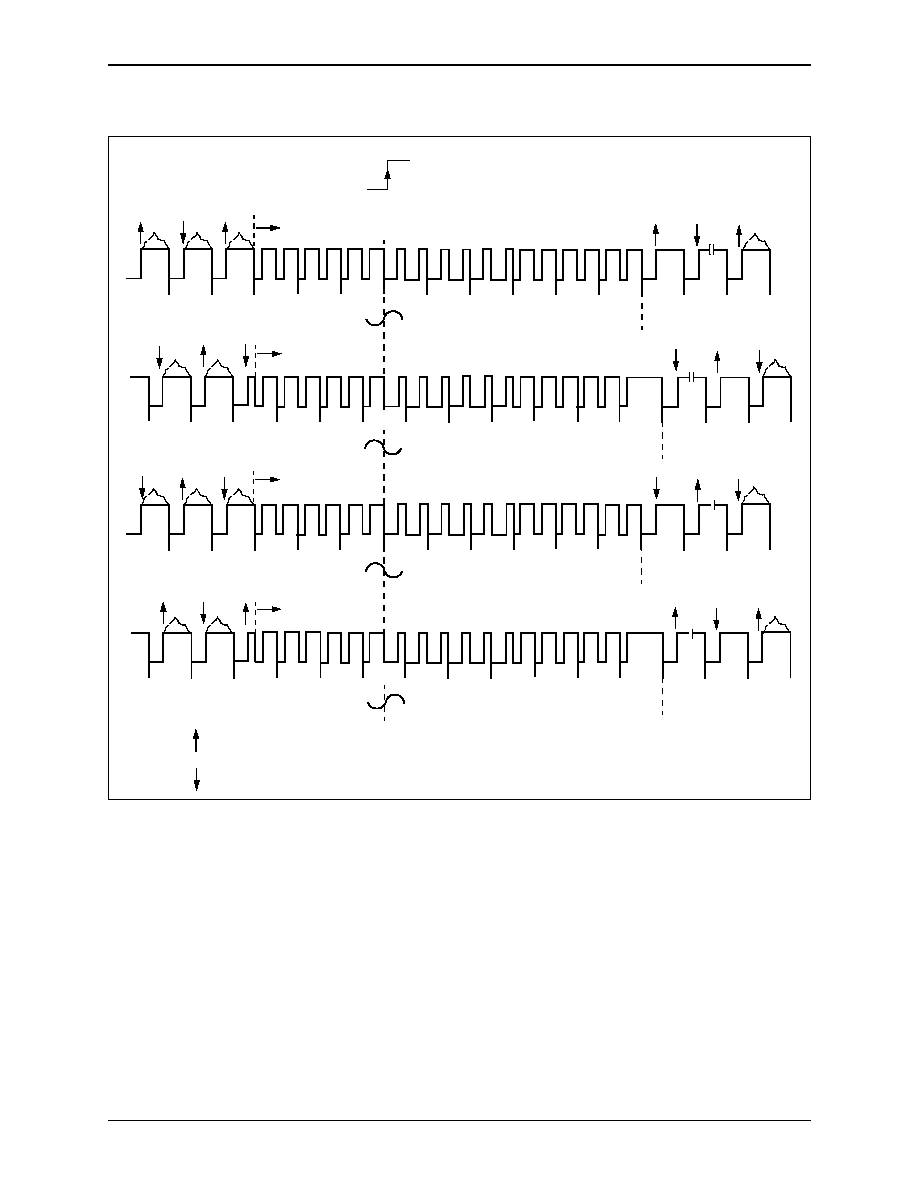

Figure 4-2.

Master Mode with Flicker Filter Interface Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

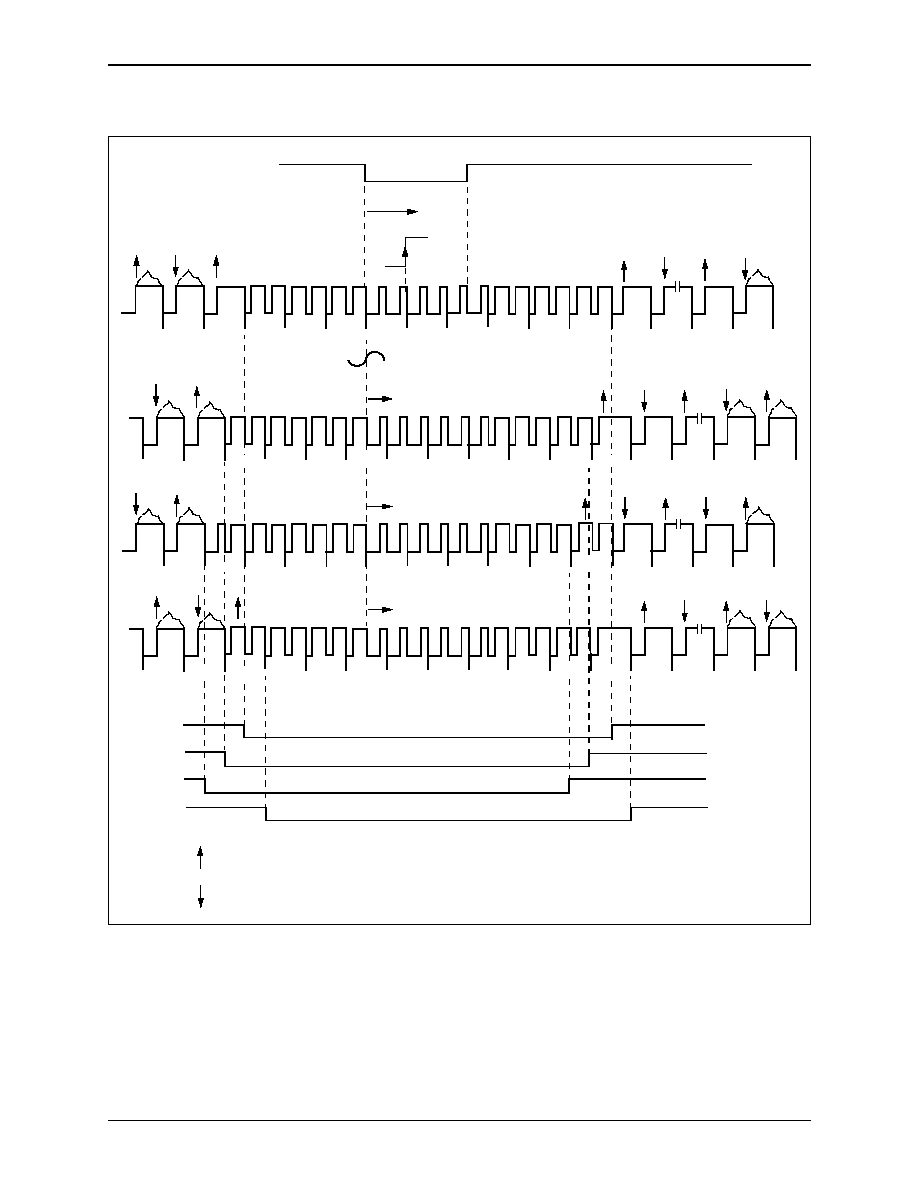

Figure 4-3.

Slave Mode with Flicker Filter Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

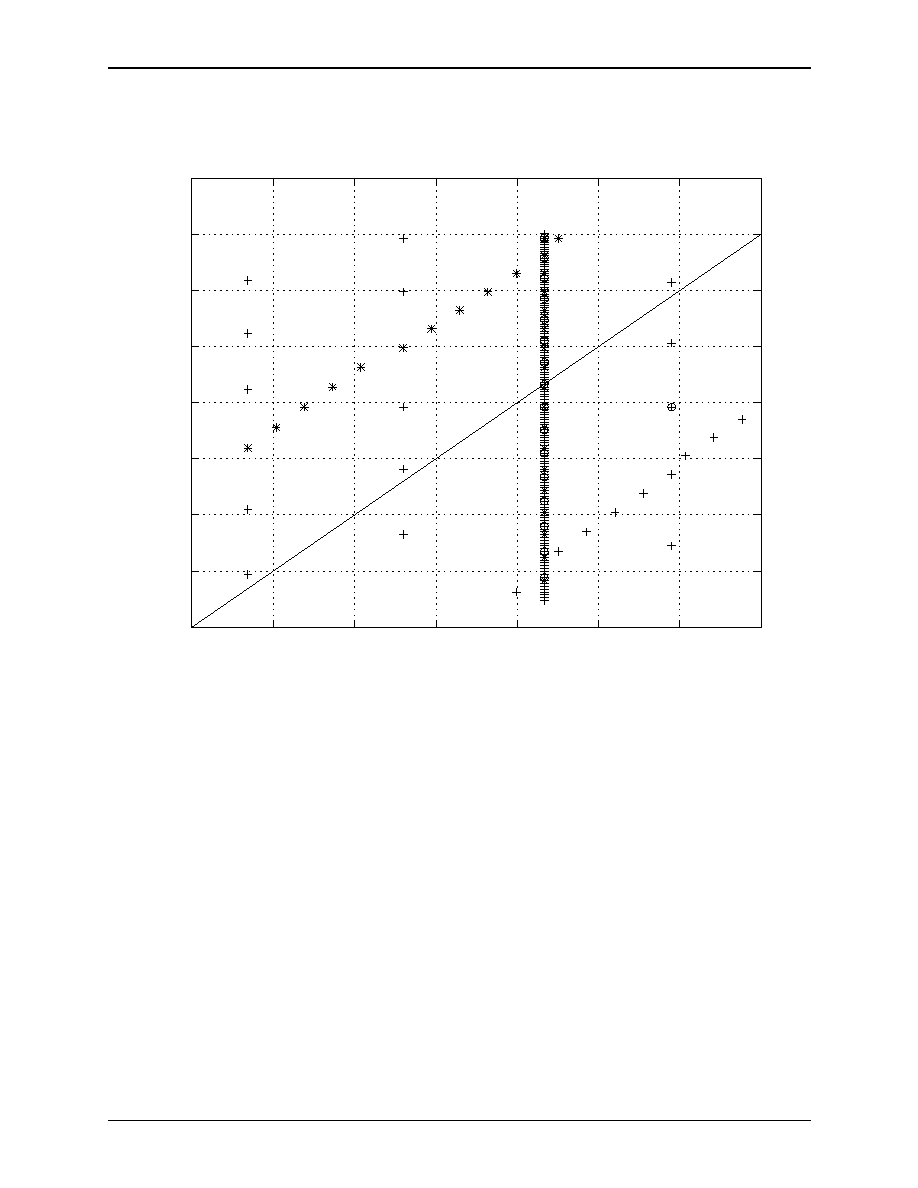

Figure A-1.

Overscan Compensation, 640x480 NTSC, 20 Clock Hblank . . . . . . . . . . . . . . . . . . . . . . . . A-2

Figure A-2.

Overscan Compensation, 640x480 PAL, 20 Clock Hblank . . . . . . . . . . . . . . . . . . . . . . . . . A-3

Figure A-3.

Overscan Compensation, 800x600 NTSC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

Figure A-4.

Overscan Compensation, 800x600 PAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

List of Figures

Bt868/Bt869

Flicker-Free Video Encoder with Ultrascale

TM

Technology

viii

Conexant

100123B

Bt868/Bt869

List of Tables

Flicker-Free Video Encoder with Ultrascale

TM

Technology

100123B

Conexant

ix

List of Tables

Table 1-1.

Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

Table 1-2.

Data Pin Assignments for Multiplexed Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Table 1-3.

Data Pin Assignments for Non-multiplexed Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

Table 1-4.

Programmability and Frequency Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

Table 1-5.

Auto-Configuration Modes 0≠3--RGB Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

Table 1-6.

Auto-Configuration Modes 4≠7--YCrCb Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

Table 1-7.

Video Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-17

Table 1-8.

Video Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

Table 2-1.

Register Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

Table 2-2.

Read-Back Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table 2-3.

Data Details Defined . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table 2-4.

Programming Detail . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

Table 3-1.

Typical Parts List for Key Passive Components. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

Table 4-1.

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 4-2.

Absolute Maximum Rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Table 4-3.

DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Table 4-4.

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Table A-1.

Video Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

Table A-2.

Constant Values Dependent on Encoding Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

Table A-3.

Overscan Values, 640x480 NTSC, 1 Pixel Resolution, 2.5 ms Hblank . . . . . . . . . . . . . . . . . A-5

Table A-4.

Overscan Values, 640x480 NTSC, 8 Pixel Resolution, 2.5 ms Hblank . . . . . . . . . . . . . . . . . A-7

Table A-5.

Overscan Values, 640x480 NTSC, 9 Pixel Resolution, 2.5 ms Hblank . . . . . . . . . . . . . . . . . A-8

Table A-6.

Overscan Values, 640x480 PAL, 1 Pixel Resolution, 2.5 ms Hblank. . . . . . . . . . . . . . . . . . . A-8

Table A-7.

Overscan Values, 640x480 PAL, 8 Pixel Resolution, 2.5 ms Hblank. . . . . . . . . . . . . . . . . . A-11

Table A-8.

Overscan Values, 640x480 PAL, 9 Pixel Resolution, 2.5 ms Hblank. . . . . . . . . . . . . . . . . . A-12

Table A-9.

Overscan Values, 800x600 NTSC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-13

Table A-10.

Overscan Values, 800x600, PAL, > 2.5 ms Hblank . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-17

List of Tables

Bt868/Bt869

Flicker-Free Video Encoder with Ultrascale

TM

Technology

x

Conexant

100123B

100123B

Conexant

1-1

1

1.0 Functional Description

1.1 Pin Descriptions

The pinout diagram is shown in

Figure 1-1

. Pin names, input/output assignments,

numbers and descriptions are listed in

Tables 1-2

and

1-3

.

Figure 1-1. Pinout Diagram

RESET

*

VDD

VDDM

AX

SI

C

P[0

]

P[1

]

P[2

]

P[3

]

P[4

]

P[5

]

P[6

]

P[7

]

SI

D

BLANK*

FIELD

VSYNC*

HSYNC*

VSS

P[23]

P[22]

P[21]

P[20]

P[19]

P[18]

SLEEP

AG

N

D

VDD_

I

80-pin PQFP

AGND

FSADJUST

VBIAS

VREF

COMP

VAA

AGND_DAC

DACA

VAA_DACA

DACB

VAA_DACB

DACC

VAA_DACC

CL

KI

VD

D_

CO

CL

K

O

VSS_

CO

VDD_

SO

VDD_X

XTALOUT

XTALIN

VSS_X

P[8

]

P[9

]

P[10

]

P[11

]

P[12

]

P[13

]

P[14]

P[15]

P[16]

P[17]

PA

L

SLA

V

E

AL

T

A

DDR

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

NC

NC

VSS

VDD

VSS_I

VSS_O

VDD_O

VDD

VSS_SI

VSS_

SO

16

17

18

19

20

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

V

AA_

PLL

A

G

ND_

PL

L

VDD_

SI

N/C

N/C

N/C

TEST

1.0 Functional Description

Bt868/Bt869

1.1 Pin Descriptions

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1-2

Conexant

100123B

Table 1-1. Pin Assignments (1 of 3)

Pin Name

I/O

Pin #

Description

XTALIN

I

63

A crystal can be connected to these pins. The pixel clock output (CLKO) is

derived from these pins with a PLL. XTALIN can be driven as a CMOS input

pin.

XTALOUT

O

62

VDD_X

--

61

Crystal oscillator supply pin. This pin should be tied to the digital supply.

VSS_X

--

64

Crystal oscillator ground pin. This pin should be tied to the digital ground

plane.

VAA_PLL

--

59

Analog power for PLL. All VAA and VDD pins must be connected together on

the same PCB plane to prevent latchup.

AGND_PLL

--

58

Analog ground for PLL. All AGND and VSS pins must be connected together

on the same PCB plane to prevent latchup.

CLKO

O

56

Pixel clock output (TTL compatible). This pin is three-state if the CLKI pin

provides the encoder clock.

VDD_CO

--

57

Clock output supply pin. This pin should be tied to the digital supply.

VSS_CO

--

55

Clock output ground pin. This pin should be tied to the digital ground plane.

CLKI

I

54

Pixel clock input (TTL compatible). This may be used as either the encoder

clock or a delayed version of the CLKO pin synchronized with the pixel data

input.

RESET*

I

53

Reset control input (TTL compatible). A logical 0 resets and disables video

timing (horizontal, vertical, subcarrier counters to the start of VSYNC of first

field) and resets the serial interface registers). RESET* must be a logical 1

for normal operation.

SLEEP

I

52

Power-down control input (TTL compatible). A logical 1 configures the

device for power-down mode. A logical 0 configures the device for normal

operation.

SLAVE

I

51

Slave/master mode select input (TTL compatible). A logical 1 configures the

device for slave video timing operation. A logical 0 configures the device for

master video timing operation.

PAL

I

50

PAL/NTSC mode select input (TTL compatible). A logical 1 configures the

device for PAL video format and Mode 1. A logical 0 configures the device

for NTSC video format and Mode 0.

VDDMAX

I

49

Input threshold adjustment. This pin should be tied to VDD for 3.3 V input

swings and GND for 5 V input swings. This pin does not affect the serial

interface pins (SID and SIC).

ALTADDR

I

48

Alternate slave address input (TTL compatible). A logical 0 configures the

device to respond to a serial programming address of 0x88; a logical 1

configures the device to respond to a serial programming address of

0x8A.

(1)

SIC

I

45

Serial interface clock input (TTL compatible). The maximum clock rate is

400 kHz.

SID

I/O

44

Serial interface data input/output (TTL compatible). Data is written to and

read from the device via this serial bus.

VDD_SI

--

47

Serial interface input supply pin. This pin should be tied to the proper supply

voltage for the desired serial interface operating voltage (i.e., tie to 5 V for

5 V serial interface compatibility).

Bt868/Bt869

1.0 Functional Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1.1 Pin Descriptions

100123B

Conexant

1-3

VSS_SI

--

42

Serial interface input ground pin. This pin should be tied to the digital

ground plane.

VDD_SO

--

46

Serial interface output supply pin. This pin should be tied to the proper

supply voltage for the desired serial interface operating voltage (i.e., tie to

5 V for 5 V serial interface compatibility).

VSS_SO

--

43

Serial interface output ground pin. This pin should be tied to the digital

ground plane.

TEST

I

39

Test pin. Should be tied to VSS.

BLANK*

I/O

38

Composite blanking control (TTL compatible). This can be generated by the

encoder or supplied from the graphics controller. If internal blanking is used,

this pin can be used to indicate the controller character clock edge.

FIELD

O

37

Field control output (TTL compatible) (Master Mode only three-state in slave

mode). FIELD transitions after the rising edge of CLK, two clock cycles

following falling HSYNC*. It is a logical 0 during odd fields and is a logical 1

during even fields.

VSYNC*

I/O

36

Vertical sync input/output (TTL compatible). As an output (master mode

operation), VSYNC* is output following the rising edge of CLK. As an input

(slave mode operation), VSYNC* is registered on the rising edge of CLK.

HSYNC*

I/O

35

Horizontal sync input/output (TTL compatible). As an output (master mode

operation), HSYNC* is output following the rising edge of CLK. As an input

(slave mode operation), HSYNC* is registered on the rising edge of CLK.

P[23:0]

I

32≠34, 23≠29, 5≠18

Pixel inputs. See

Table 1-2, "Data Pin Assignments for Multiplexed Modes,"

on page 1.05

. The input data is sampled on both the rising and falling edge

of CLK for multiplexed modes, and on the rising edge of clock in

non-multiplexed modes. A higher bit index corresponds to a greater bit

significance.

VDD

--

20,40,60

Digital power for core logic. All VAA and VDD pins must be connected

together on the same PCB plane to prevent latchup.

VDD_I

--

19

Digital power for digital inputs. All VAA and VDD pins must be connected

together on the same PCB plane to prevent latchup. This pin should be tied

to the 5 V supply for 5 V tolerant inputs,

VDD_O

--

30

Digital power for digital outputs. All VAA and VDD pins must be connected

together on the same PCB plane to prevent latchup.

VSS

--

4, 21, 41

Digital ground for core logic. All AGND and VSS pins must be connected

together on the same PCB plane to prevent latchup.

VSS_I

--

22

Digital ground for inputs. All AGND and VSS pins must be connected

together on the same PCB plane to prevent latchup.

VSS_O

--

31

Digital ground for outputs. All AGND and VSS pins must be connected

together on the same PCB plane to prevent latchup.

VAA

--

80

Analog power. All VAA and VDD pins must be connected together on the

same PCB plane to prevent latchup.

AGND

--

1, 79

Analog ground. All AGND and VSS pins must be connected together on the

same PCB plane to prevent latchup.

Table 1-1. Pin Assignments (2 of 3)

Pin Name

I/O

Pin #

Description

1.0 Functional Description

Bt868/Bt869

1.1 Pin Descriptions

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1-4

Conexant

100123B

FSADJUST

I

78

Full-scale adjust control pin. A resistor (RSET) connected between this pin

and GND controls the full-scale output current on the analog outputs.

VBIAS

O

77

DAC bias voltage. A 0.1 µF ceramic capacitor must be used to bypass this

pin to GND. The capacitor must be as close to the device as possible to keep

lead lengths to an absolute minimum.

VREF

O

76

Voltage reference pin. A 0.1 µF ceramic capacitor must be used to decouple

this pin to GND. The decoupling capacitor must be as close to the device as

possible to keep lead lengths to an absolute minimum.

COMP

O

75

Compensation pin. A 0.1 µF ceramic capacitor must be used to bypass this

pin to VAA. The capacitor must be as close to the device as possible to keep

lead lengths to an absolute minimum.

AGND_DAC

--

74

Common DAC Analog ground return. All AGND and VSS pins must be

connected together on the same PCB plane to prevent latchup.

VAA_DACC

--

73

DACC Analog power. All VAA and VDD pins must be connected together on

the same PCB plane to prevent latchup.

DACC

O

72

DACC output.

VAA_DACB

--

71

DACB Analog power. All VAA and VDD pins must be connected together on

the same PCB plane to prevent latchup.

DACB

O

70

DACB output.

VAA_DACA

--

69

DACA Analog power. All VAA and VDD pins must be connected together on

the same PCB plane to prevent latchup.

DACA

O

68

DACA output.

N/C

--

65, 66, 67

No connect pins

NOTE(S):

(1)

Any unused inputs should not be left floating.

Table 1-1. Pin Assignments (3 of 3)

Pin Name

I/O

Pin #

Description

Bt868/Bt869

1.0 Functional Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1.1 Pin Descriptions

100123B

Conexant

1-5

Table 1-2. Data Pin Assignments for Multiplexed Modes

Pin

Rising Edge of CLKI

Falling Edge of CLKI

24-bit

RGB

Mode

15/16-bit

RGB

Mode

16-bit

YCrCb

Mode

24-bit

YCrCb

Mode

24-bit

RGB

Mode

15/16-bit

RGB

Mode

16-bit

YCrCb

Mode

24-bit

YCrCb

Mode

P[11]

G4

G2

Cr/Cb7

Cr7

R7

R4

Y7

Y7

P[10]

G3

G1

Cr/Cb6

Cr6

R6

R3

Y6

Y6

P[9]

G2

G0

Cr/Cb5

Cr5

R5

R2

Y5

Y5

P[8]

B7

B4

Cr/Cb4

Cr4

R4

R1

Y4

Y4

P[7]

B6

B3

Cr/Cb3

Cr3

R3

R0

Y3

Y3

P[6]

B5

B2

Cr/Cb2

Cr2

G7

G5

(1)

Y2

Y2

P[5]

B4

B1

Cr/Cb1

Cr1

G6

G4

Y1

Y1

P[4]

B3

B0

Cr/Cb0

Cr0

G5

G3

Y0

Y0

P[3]

G0

--

--

Cb7

R2

--

--

Cb3

P[2]

B2

--

--

Cb6

R1

--

--

Cb2

P[1]

B1

--

--

Cb5

R0

--

--

Cb1

P[0]

B0

--

--

Cb4

G1

--

--

Cb0

NOTE(S):

(1)

G5 is ignored in 15-bit RGB mode.

Table 1-3. Data Pin Assignments for Non-multiplexed Modes

Pin

24-bit RGB Mode

24-bit YCrCb Mode

P[23:16]

B[7:0]

Cb[7:0]

P[15:8]

G[7:0]

Cr[7:0]

P[7:0]

R[7:0]

CY[7:0]

1.0 Functional Description

Bt868/Bt869

1.2 GUI Controller Programmability and Frequency Requirement

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1-6

Conexant

100123B

1.2 GUI Controller Programmability and

Frequency Requirement

Programmability and frequency requirements for the GUI Controller are defined

in

Table 1-4

.

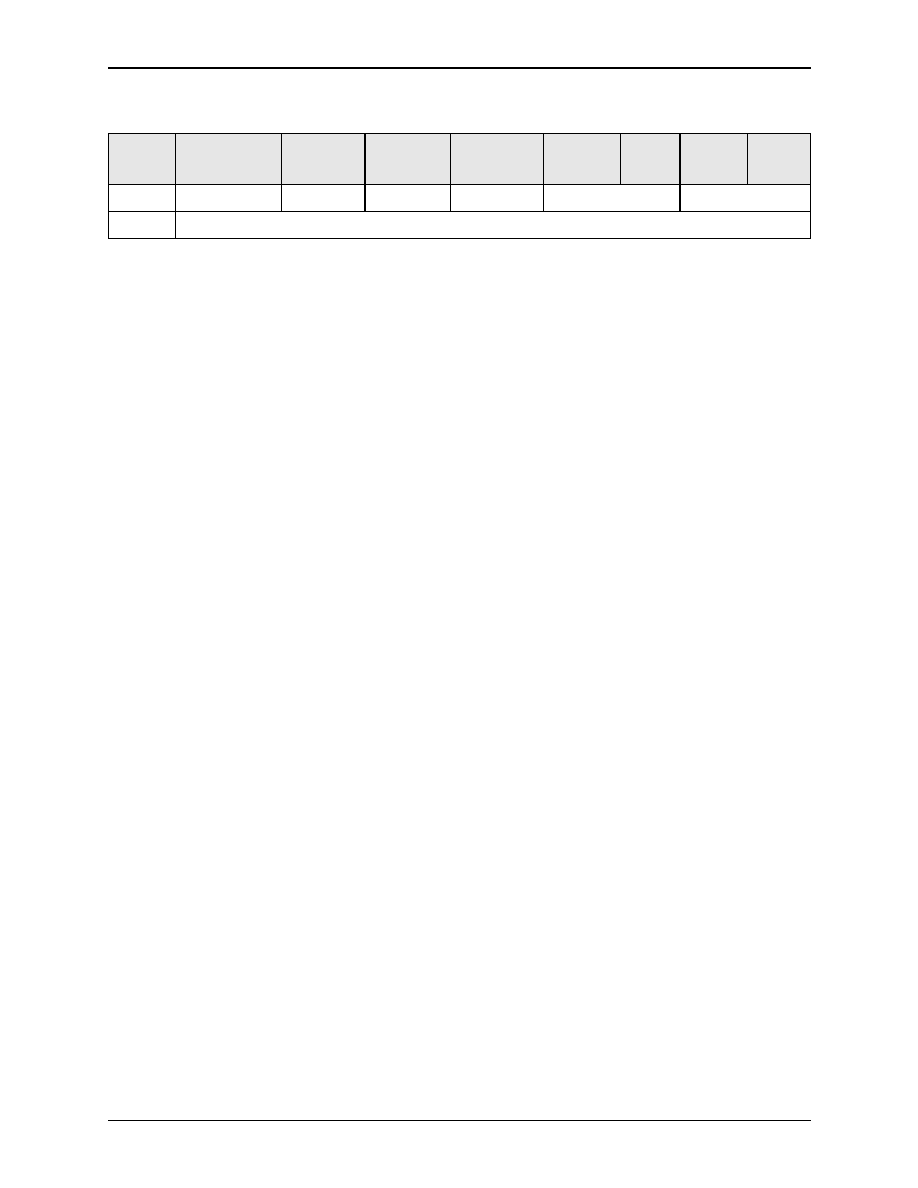

Table 1-4. Programmability and Frequency Requirement

Mode

Maximum Total

Maximum

Vsync to

Active

Maximum Frequencies

Pixels

Lines

Line (kHz)

Pixel (MHz)

640 x 480

1075

665

117

39.860

31.563

800 x 600

1075

835

147

49.451

40.000

Bt868/Bt869

1.0 Functional Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology 1.2 GUI Controller Programmability and Frequency Requirement

100123B

Conexant

1-7

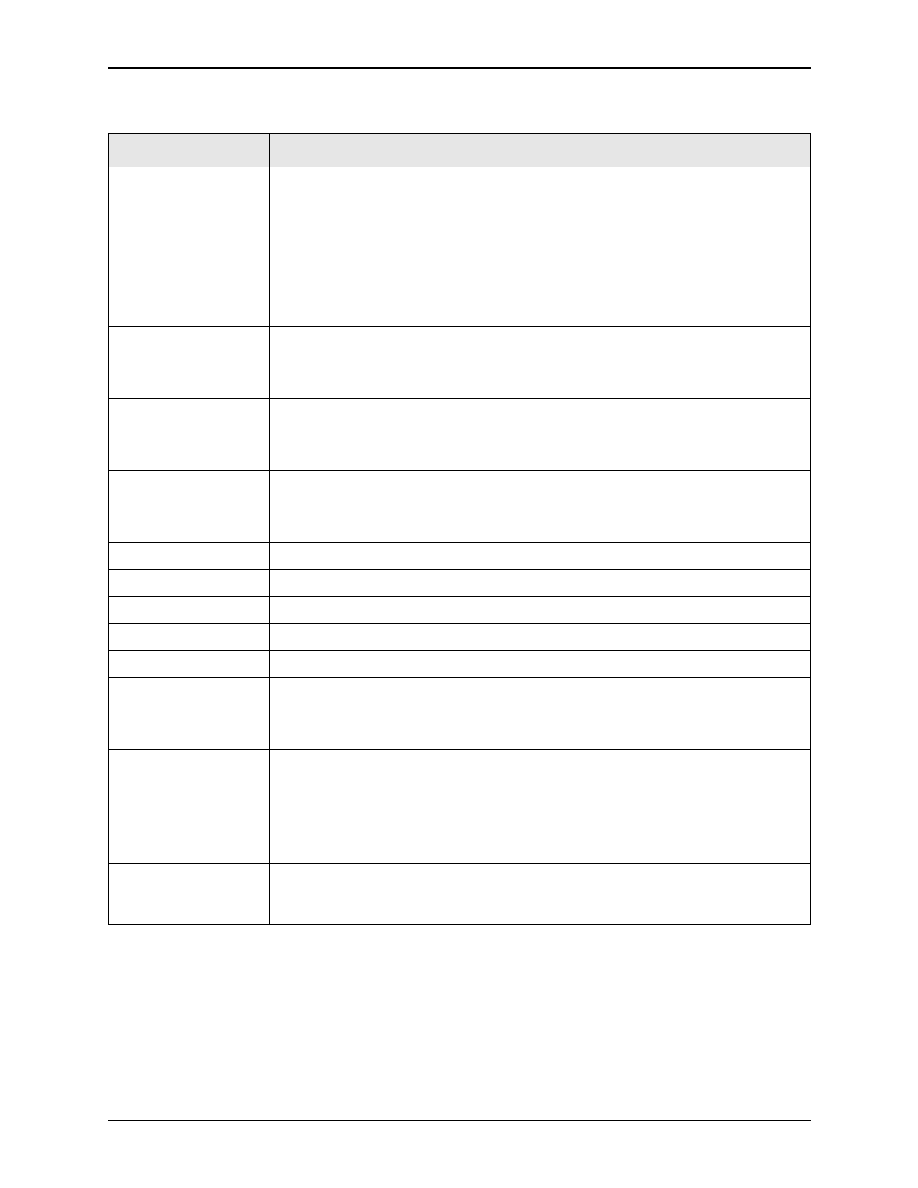

Figure 1-2

illustrates the concept of flicker filter control.

Figure 1-2. Flicker Filter Control Diagram--External Use

FI

FO

I

nput

IN_M

ODE

[

2

:

0]

0

00 =

24

-bi

t

F_

SEL

Y[

2

:

0

]

00

0 =

5 L

i

n

e

00

1 =

2 L

i

n

e

01

0 =

3 L

i

n

e

01

1 =

4 L

i

n

e

100

=

A

l

t. 5

Li

n

e

1

101

=

A

l

t. 5

Li

n

e

2

110

=

A

l

t. 5

Li

n

e

3

111

=

A

l

t. 5

Li

n

e

4

F

_

S

E

L

C

[2:0

]

0

0

0

=

5

Li

ne

0

0

1

=

2

Li

ne

0

1

0

=

3

Li

ne

0

1

1

=

4

Li

ne

10

0 =

A

l

t.

5 L

i

ne

1

10

1 =

A

l

t.

5 L

i

ne

2

11

0 =

A

l

t.

5 L

i

ne

3

11

1 =

A

l

t.

5 L

i

ne

4

DI

S_

G

M

SHY

Y

L

P

F

[1

:0]

00

=

B

y

pa

s

s

01

=

Lu

ma

,

YAT

T

E

N

U

AT

E

[

2

:

0

]

0

00

=

1.0

Ga

i

n

00

1 =

1

5

/1

6 G

a

i

n

0

10

=

7/8

Ga

i

n

0

11

=

3/4

Ga

i

n

1

00

=

1/2

Ga

i

n

1

01

=

1/4

Ga

i

n

1

10

=

1/8

Ga

i

n

1

11

=

0.0

Ga

i

n

CA

T

T

ENU

A

T

E

[2

:

0

]

00

0 =

1

.

0

Gai

n

001

=

15

/16

Ga

i

n

01

0 =

7

/

8

Gai

n

01

1 =

3

/

4

Gai

n

10

0 =

1

/

2

Gai

n

10

1 =

1

/

4

Gai

n

11

0 =

1

/

8

Gai

n

11

1 =

0

.

0

Gai

n

F

lic

k

e

r Fi

lte

r

/S

c

a

le

r

0 =

E

n

ab

l

e

Lu

ma

RGB M

u

x

0

01 =

16

-bi

t

RGB M

u

x

0

10 =

15

-bi

t

RGB M

u

x

0

11 =

24

-bi

t

RGB

No

n

-

M

u

x

1

01 =

16

-bi

t

Y

C

rC

b

Mu

x

11

0 =

R

e

ser

v

e

d

H

o

r

i

zont

al

LP

F1

10

=

Lu

ma

,

H

o

r

i

zont

al

LP

F2

11 =

Lu

ma,

Ho

r

i

z

o

n

t

a

l

LP

F3

CL

PF

[

1

:0

]

00 =

B

y

pa

ss

0

1

=

C

h

ro

ma,

Ho

r

i

z

o

n

t

a

l

LP

F1

1

0

=

C

h

ro

ma,

Ho

r

i

z

o

n

t

a

l

LP

F2

11 =

C

h

r

o

ma

,

H

o

r

i

zont

al

LP

F3

Y

C

O

R

ING[2

:0]

0

01 =

1/1

2

8

of R

ang

e

01

0 =

1

/

6

4

of R

ang

e

01

1 =

1

/

3

2

of R

ang

e

10

0 =

1

/

1

6

of R

ang

e

101

=

1

/

8

of R

ang

e

110

=

1

/

4

of R

ang

e

11

1 =

R

e

se

r

v

e

d

P

s

u

edo

Ga

m

m

a

Re

m

o

v

a

l

DI

S

_

GM

SHC

0 =

E

nabl

e

Ch

r

o

m

a

P

s

ue

do

Gam

m

a

Re

m

o

v

a

l

DIS_

G

M

USHY

0 =

E

nabl

e

Lum

a

A

n

ti-

P

se

ud

o

Gam

m

a

Re

m

o

v

a

l

DIS_

G

M

USHC

0 =

E

n

ab

l

e

C

h

ro

ma

A

n

ti

-P

su

edo

Ga

mm

a

Re

m

o

v

a

l

DIS_

Y

F

L

P

F

0 =

E

nabl

e

In

itia

l

Lum

a

Ho

r

i

z

o

n

t

a

l

Low

P

a

ss

F

ilte

r

CCO

RING[

2

:0

]

001

=

+

/

-

1

/2

56

of R

ang

e

01

0 =

+

/

- 1

/

12

8

of R

ang

e

011

=

+

/

-

1/6

4

of R

ang

e

100

=

+

/

-

1/3

2

of R

ang

e

101

=

+

/

-

1/1

6

of R

ang

e

11

0 =

+

/

- 1/

8

of R

ang

e

11

1 =

R

e

se

r

v

e

d

0

00 =

B

y

pa

ss

000

=

B

y

pa

ss

11

1 =

2

4

-

b

i

t

Y

C

r

C

b N

o

n-

Mu

x

10

0 =

2

4

-

b

i

t

Y

C

rC

b

Mu

x

Color

Spac

e

Conv

ert

e

r

1.0 Functional Description

Bt868/Bt869

1.2 GUI Controller Programmability and Frequency Requirement

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1-8

Conexant

100123B

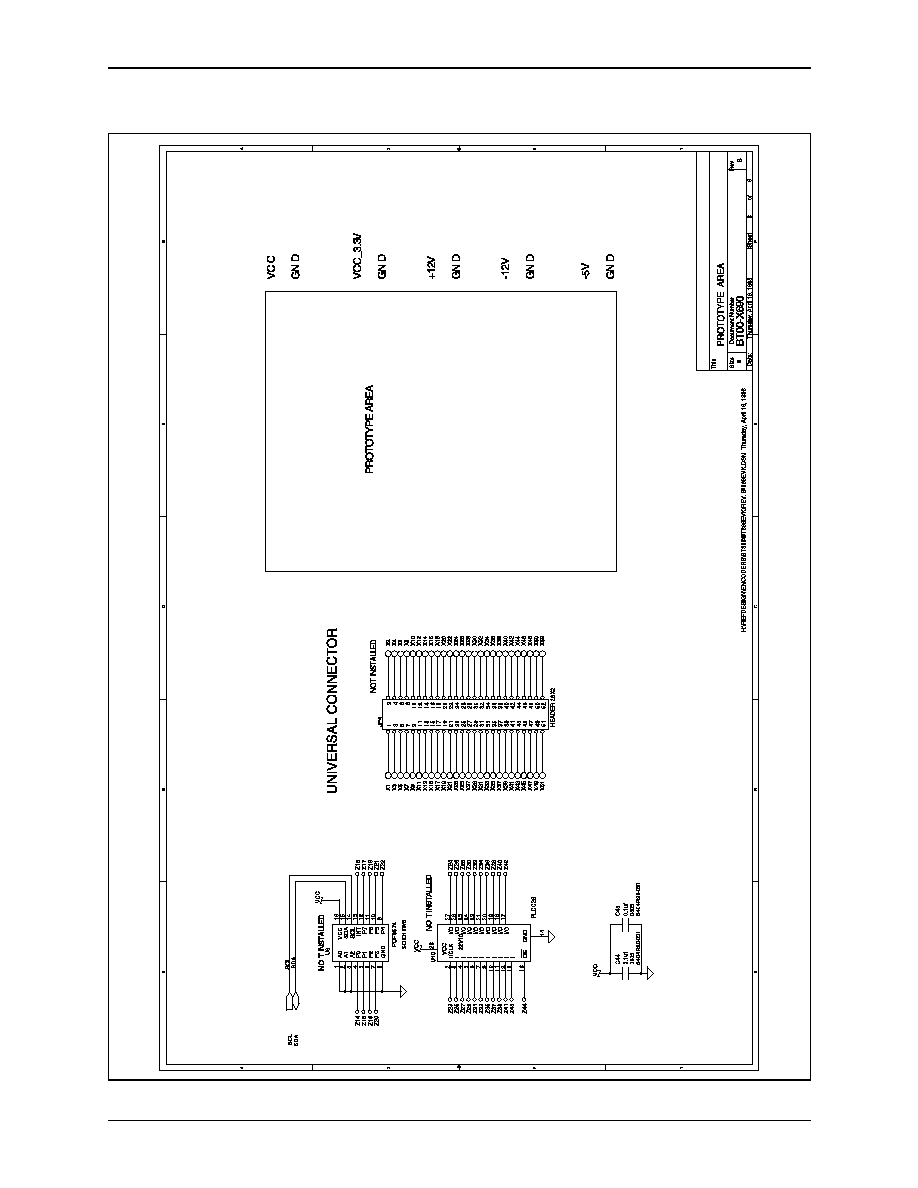

Figure 1-3

illustrates the Bt868/869 functional block diagram.

Figure 1-3. Encoder Core

I

n

t

e

r

nal

V

o

lt

age

Re

f

e

renc

e

2X

F

SADJU

S

T

DAC

A

Up

sam

p

l

e

V

i

deo

Ti

mi

ng

Co

ntrol

,

RESET

*

LP

F

U/V

M

odu

lat

o

r

10

an

d

Mi

x

e

r

10

FI

E

L

D

CO

M

P

Ca

pt

ion

i

ng,

M

a

c

r

ov

is

io

n

Cl

o

s

ed

Lum

a

9

+

+

DAC

B

10

DAC

C

10

Ou

t

Mu

x

Ou

t

Mo

d

e

2X

Up

sam

p

l

e

X

+

X

BST

_

A

MP

MC

R

MC

B

SYNC_

AMP

MY

Syn

c

P

r

oc

es

s

o

r

Bu

rst

P

r

oc

es

s

o

r

C1

0

Y1

0

RG

B 2

4

RG

B

Y

[

9:

0]

C

RCB[9

:0

]

9

CVBS

1

0

DAC

DAC

DAC

De

l

a

y

t

o

4:

4:

4

Con

v

ersi

o

n

4:

2:

2

Regist

ers

SI

D

VB

IA

S

Bt868/Bt869

1.0 Functional Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1.3 Circuit Description

100123B

Conexant

1-9

1.3 Circuit Description

1.3.1 Overview

The Bt868/869 is a video encoder designed for TV output of non-interlaced

graphics data, such as that found in a PC or some set-top boxes. It incorporates

advanced filtering technology for flicker removal and overscan compensation

which allows high-quality display of non-interlaced images on an interlaced TV

display. The Bt868/869 accomplishes this by minimizing the flicker and providing

control of the amount of overscan so that the entire image is viewable.

The Bt868/869 consists of a Color Space Converter/Flicker Filter engine

followed by a digital video encoder. The Color Space Converter/Flicker Filter

contains the following:

∑

A timing converter

∑

Various horizontal video processing functions

∑

Flicker filter and vertical scaler for overscan compensation

The output of this engine is fed into a FIFO for synchronization with the

digital video encoder.

1.3.2 Reset

If the RESET* pin is held low for a minimum of two clock cycles, a timing reset

and a software reset is performed. During a timing reset, the serial interface is

held in the reset condition, the subcarrier phase is set to zero, and the horizontal

and vertical counters are held to the beginning of VSYNC of Field 1 (both

counters equal to zero). Counting resumes the next clock after rising RESET*.

The serial interface registers are reset to zero.

A software reset, which can be generated by setting the SRESET register bit,

initializes all the serial interface registers to zero (except for PLL_INT, which is

initialized to 0x0C). As a result, all output pins are three-state. The first 32

registers are then initialized to auto-configuration mode 0 (see the Auto

Configuration section). The EN_OUT bit must be set to enable the outputs. The

software reset can also be generated by setting the SRESET register bit.

A power-on reset is generated on power-up. The power-on reset generates both

a timing and a software reset. The power-on reset is generated by a time delay

circuit triggered after the supply voltage reaches a value sufficiently high enough

for the circuit to operate. As such, the device may not initialize to the default state

unless the power supply ramp rate is sufficiently fast enough. Therefore, a

hardware reset is recommended if the default state is required.

1.3.3 Timing Registers

After writing any registers, a timing reset is recommended by setting the T-bit.

1.0 Functional Description

Bt868/Bt869

1.3 Circuit Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1-10

Conexant

100123B

1.3.4 Device Initialization

After a reset condition, the device must be programmed through the serial

interface to activate video or output one of the other video standards and to enable

the CLK0, HSYNC*, VSYNC*, and FIELD outputs.

1.3.5 Auto Configuration

The device can configure itself for one of eight combinations of video formats

and input modes with a single register write.

Tables 1-5

and

1-6

detail the eight

available auto configuration modes. This feature reduces the software support

required, yet allows full flexibility in generating video formats and timing. Once

the device is configured, all the registers are accessible to modify the modes. For

less common modes, the device can be configured for the closest mode, and only

those registers that differ need to be programmed. To auto-configure the device,

set the configuration bits (CONFIG[2:0]) to the desired mode. The device will

initialize the first 32 registers (registers 0x3B to 0x5A), setting the BUSY flag in

the process. When complete, the BUSY flag is cleared. The serial interface is not

available when the BUSY flag is high except for monitoring the status register.

If the mux mode is enabled, pins P[23:21] can also be used to externally

configure the device to any one of the eight configuration modes. These pins

directly emulate the CONFIG[2:0] register. In order to configure the device in

this way, the EN_PINCFG register must be set. The desired state must be present

on the P[23:21] pins for at least two clock cycles.

Bt868/Bt869

1.0 Functional Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1.3 Circuit Description

100123B

Conexant

1-11

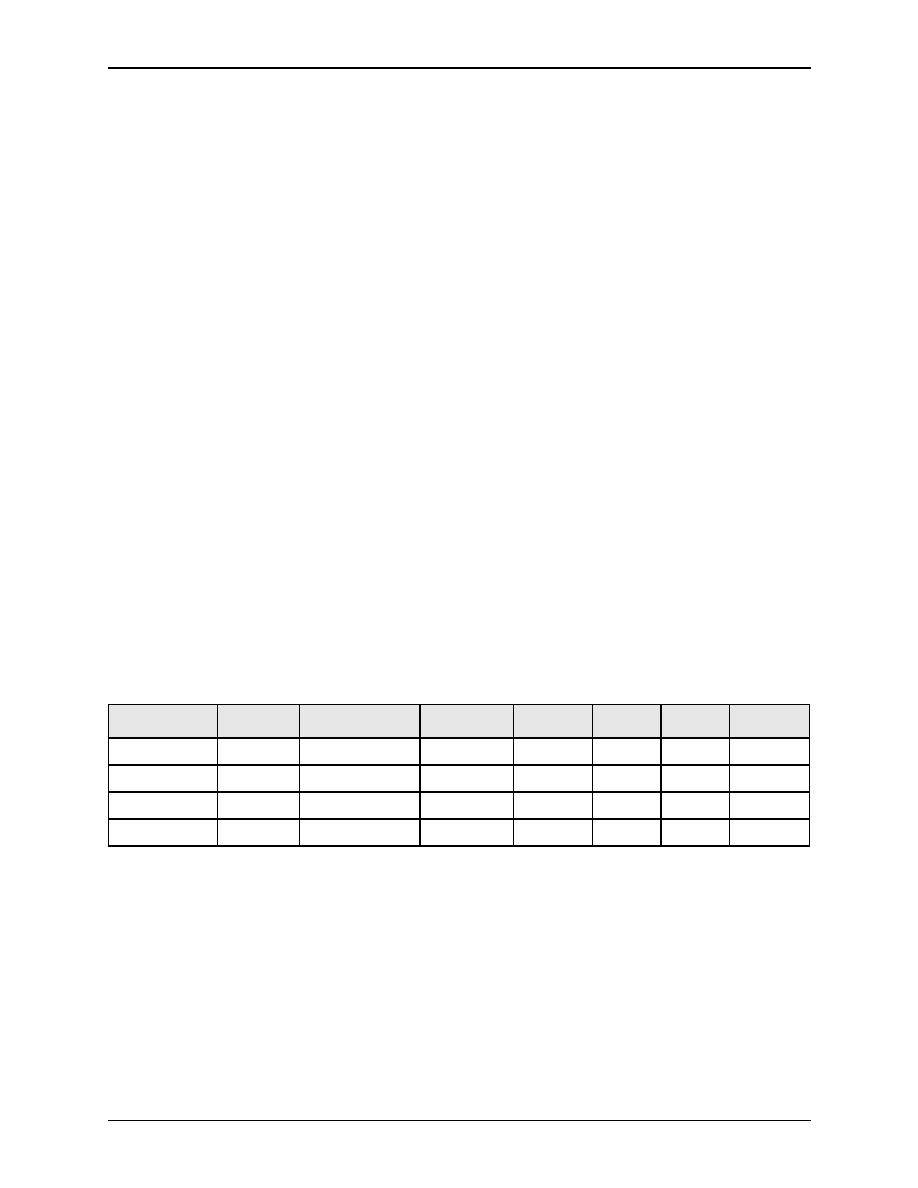

Table 1-5. Auto-Configuration Modes 0≠3--RGB Input (1 of 2)

Register Name

Mode 0

NTSC 640x480

(1)

CLKO=28.195793 MHz

Mode 1

PAL 640x480

CLKO=29.500008 MHz

Mode 2

NTSC 800x600

CLKO=38.769241 MHz

Mode 3

PAL 800x600

CLKO=36.000000 MHz

DEC

HEX

DEC

HEX

DEC

HEX

DEC

HEX

H_CLKO [11:0]

1792

700

1888

760

2464

9A0

2304

900

H_ACTIVE [9:0]

640

280

640

280

800

320

800

320

HSYNC_WIDTH

[7:0]

132

84

138

8A

182

B6

170

AA

HBURST_BEGIN

[7:0]

150

96

166

A6

206

CE

202

CA

HBURST_END

[7:0]

96

60

104

68

180

84

154

9A

H_BLANKO [10:0]

381

17D

449

1C1

597

255

525

20D

V_BLANKO [9:0]

34

22

46

2E

32

20

41

29

V_ACTIVEO [8:0]

212

D4

242

F2

216

D8

252

FC

H_FRACT [7:0]

0

0

0

0

0

0

0

0

H_CLKI [10:0]

784

310

944

3B0

880

370

960

3C0

H_BLANKI [8:0]

126

7E

266

10A

66

42

140

8C

V_BLANK_DLY

0

0

0

0

0

0

0

0

V_LINESI [9:0]

600

258

625

271

735

2DF

750

2EE

V_BLANKI [7:0]

75

4B

90

5A

86

56

95

5F

V_ACTIVEI [9:0]

480

1E0

480

1E0

600

258

600

258

CLPF [1:0]

0

0

0

0

0

0

0

0

YLPF [1:0]

3

3

3

3

3

3

3

3

V_SCALE [13:0]

5266

1492

4096

1000

7373

1CCD

5734

1666

PLL_FRACT [15:0]

34830

880E

7282

1C72

15124

3B14

0

0

EN_XCLK

0

0

0

0

0

0

0

0

BY_PLL

0

0

0

0

0

0

0

0

PLL_INT [5:0]

12

C

13

D

17

11

16

10

EN_SCART

0

0

0

0

0

0

0

0

ECLIP

0

0

0

0

0

0

0

0

PAL

0

0

1

1

0

0

1

1

DIS_SCRESET

0

0

0

0

0

0

0

0

VSYNC_DUR

1

1

0

0

1

1

0

0

625LINE

0

0

1

1

0

0

1

1

SETUP

1

1

0

0

1

1

0

0

1.0 Functional Description

Bt868/Bt869

1.3 Circuit Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1-12

Conexant

100123B

NI_OUT

0

0

0

0

0

0

0

0

SYNC_AMP [7:0]

229

E5

240

F0

229

E5

240

F0

BST_AMP [7:0]

118

76

88

58

116

74

87

57

MCR [7:0]

121

79

129

81

119

77

128

80

MCB [7:0]

68

44

73

49

67

43

72

48

MY [7:0]

133

85

140

8C

133

85

140

8C

MSC [31:0]

545259520

20800000

645499916

26798C0C

396552378

17A2E8BA

528951320

1F872818

NOTE(S):

(1)

Assumes 13.5 MHz CLK-D frequency.

Table 1-5. Auto-Configuration Modes 0≠3--RGB Input (2 of 2)

Register Name

Mode 0

NTSC 640x480

(1)

CLKO=28.195793 MHz

Mode 1

PAL 640x480

CLKO=29.500008 MHz

Mode 2

NTSC 800x600

CLKO=38.769241 MHz

Mode 3

PAL 800x600

CLKO=36.000000 MHz

DEC

HEX

DEC

HEX

DEC

HEX

DEC

HEX

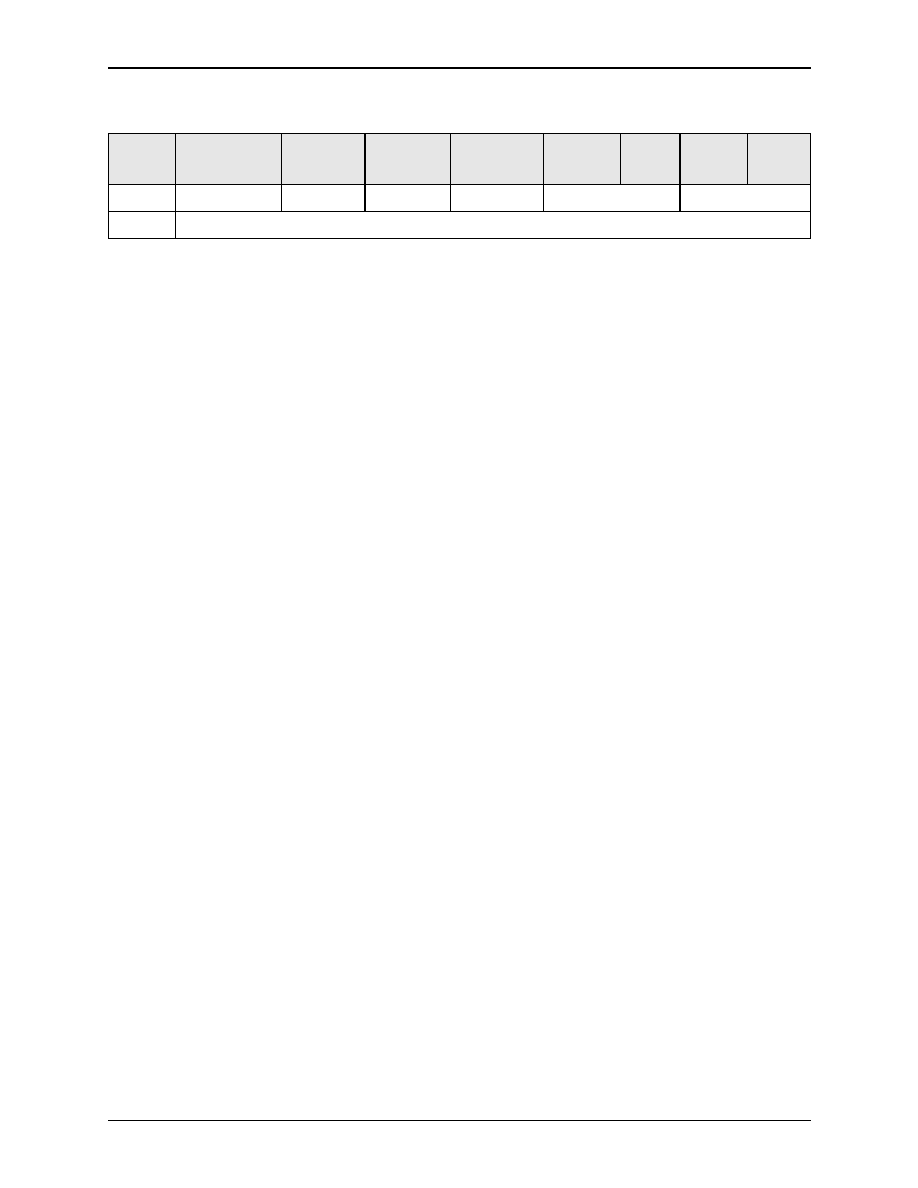

Table 1-6. Auto-Configuration Modes 4≠7--YCrCb Input (1 of 2)

Register Name

Mode 4

NTSC 640x480

CLKO=28.195793 MHz

Mode 5

PAL 640x480

CLKO=29.500008 MHz

Mode 6

NTSC 800x600

CLKO=38.769241 MHz

Mode 7

PAL 800x600

CLKO=36.000000 MHz

DEC

HEX

DEC

HEX

DEC

HEX

DEC

HEX

H_CLKO [11:0]

1792

700

1888

760

2464

9A0

2304

900

H_ACTIVE [9:0]

640

280

640

280

800

320

800

320

HSYNC_WIDTH [7:0]

132

84

138

8A

182

B6

170

AA

HBURST_BEGIN

[7:0]

150

96

166

A6

206

CE

202

CA

HBURST_END [7:0]

96

60

103

68

180

B4

154

9A

H_BLANKO [10:0]

381

17D

449

1C1

597

255

525

20D

V_BLANKO [9:0]

34

22

46

2E

32

20

41

29

V_ACTIVEO [8:0]

212

D4

242

F2

216

D8

252

FC

H_FRACT [7:0]

0

0

0

0

0

0

0

0

H_CLKI [10:0]

784

310

944

3B0

880

370

960

3C0

H_BLANKI [8:0]

126

7E

266

10A

66

42

140

8C

V_BLANK_DLY

0

0

0

0

0

0

0

0

V_LINESI [9:0]

600

258

625

271

735

2DF

750

2EE

V_BLANKI [7:0]

75

4B

90

5A

86

56

95

5F

V_ACTIVEI [9:0]

480

1E0

480

1E0

600

258

600

258

CLPF [1:0]

0

0

0

0

0

0

0

0

Bt868/Bt869

1.0 Functional Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1.3 Circuit Description

100123B

Conexant

1-13

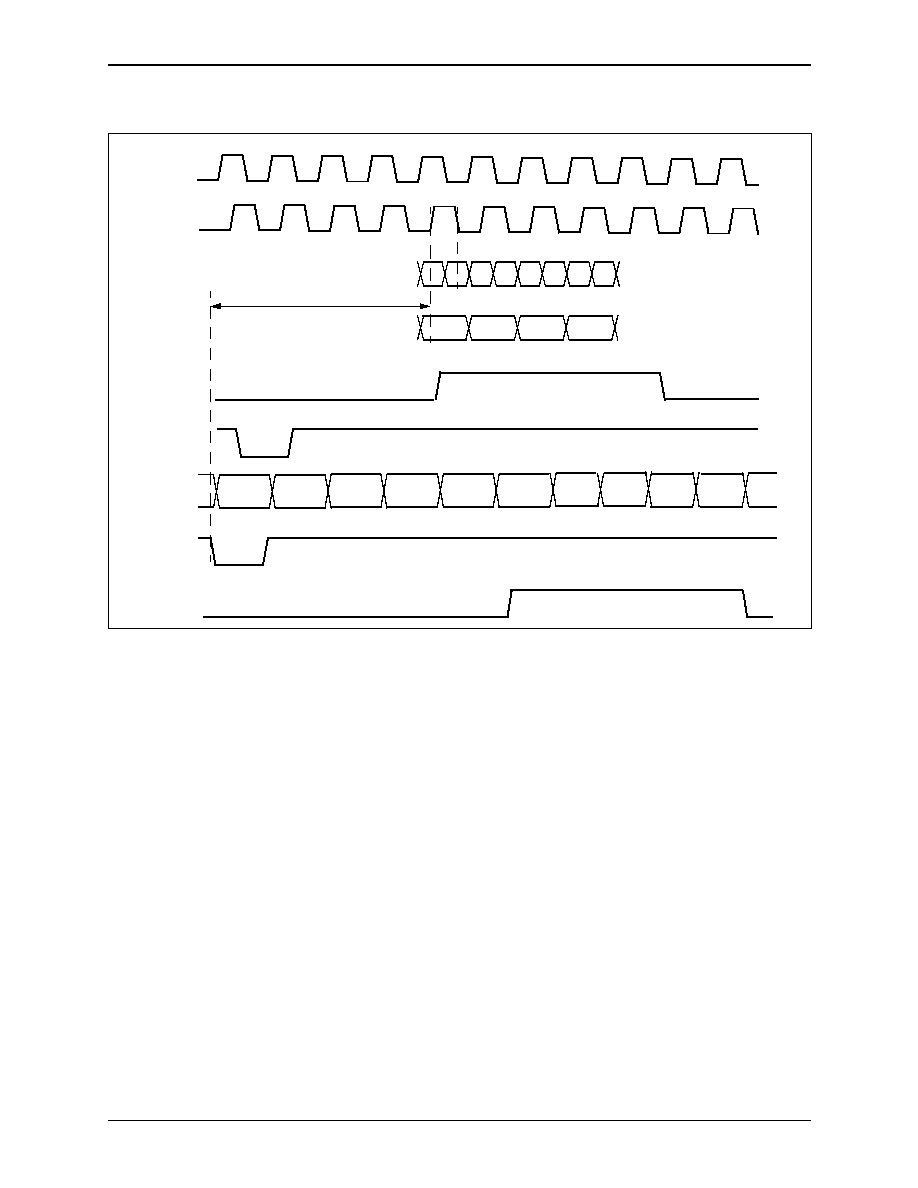

1.3.6 Clocking and Timing Generation

There are two timing generators that control the operation of the encoder. The

encoder timing block generates the signals for the proper encoding of the video

into NTSC or PAL, and extracts the processed input pixels from the internal

FIFO. The encoding timing generator can receive its clock from either an external

crystal oscillator and PLL, or from the CLKI pin. Normal operation requires that

the encoding clock be generated by the PLL. The clock source is selected by the

EN_XCLK register bit. If EN_XCLK is set to a logical 0, the internal clock

source is selected; and when the EN_OUT bit is set, the CLKO pin is enabled to

drive the derived clock.

A crystal must be present between XTALIN and XTALOUT pins if the

internal clock source is selected. The frequency of the CLK is synthesized by a

PLL such that the frequency is:

F

clk

= F

xtal

*

{PLL_INT(5:0) + [PLL_FRACT(15:0)/216]}/6

YLPF [1:0]

3

3

3

3

3

3

3

3

V_SCALE [13:0]

5266

1492

4096

1000

7373

1CCD

5734

1666

PLL_FRACT [15:0]

34830

880E

7282

1C72

15124

3B14

0

0

EN_XCLK

0

0

0

0

0

0

0

0

BY_PLL

0

0

0

0

0

0

0

0

PLL_INT [5:0]

12

C

13

D

17

11

16

10

EN_SCART

0

0

0

0

0

0

0

0

ECLIP

0

0

0

0

0

0

0

0

PAL

0

0

1

1

0

0

1

1

DIS_SCRESET

0

0

0

0

0

0

0

0

VSYNC_DUR

1

1

0

0

1

1

0

0

625LINE

0

0

1

1

0

0

1

1

SETUP

1

1

0

0

1

1

0

0

NI_OUT

0

0

0

0

0

0

0

0

SYNC_AMP [7:0]

229

E5

240

F0

229

E5

240

F0

BST_AMP [7:0]

118

76

88

58

116

74

87

57

MCR [7:0]

121

79

129

81

119

77

128

80

MCB [7:0]

68

44

73

49

67

43

72

48

MY [7:0]

133

85

140

8C

133

85

140

8C

MSC [31:0]

545259520 20800000 645499916

26798C0C

396552378

17A2E8BA

528951320

1F872818

Table 1-6. Auto-Configuration Modes 4≠7--YCrCb Input (2 of 2)

Register Name

Mode 4

NTSC 640x480

CLKO=28.195793 MHz

Mode 5

PAL 640x480

CLKO=29.500008 MHz

Mode 6

NTSC 800x600

CLKO=38.769241 MHz

Mode 7

PAL 800x600

CLKO=36.000000 MHz

DEC

HEX

DEC

HEX

DEC

HEX

DEC

HEX

1.0 Functional Description

Bt868/Bt869

1.3 Circuit Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1-14

Conexant

100123B

The crystal must be chosen so that the precise line rate for the video standards

required can be achieved. This is done to maintain the subcarrier relationship to

the line rate and thereby achieve the precise subcarrier frequency as required by

the standard. The crystal oscillator is designed to oscillate from 5-25 MHz. A

13.5 MHz crystal meets the requirements for both NTSC and PAL video

standards. The crystal must be within 50 ppm of the maximum desired clock rate

for NTSC operation, and 25 ppm for PAL operation, across temperature (0∞ to

70∞C). See Appendix B for list of recommended crystal vendors.

The crystal oscillator is disabled by the SLEEP pin. Sufficient time (greater

than approximately 1 second) must be allowed after coming out of sleep mode to

allow the oscillator to stabilize.

If the external clock source is selected (EN_XCLK=1), a clock signal of the

desired pixel clock rate must be present at the CLKI pin. The CLKO pin will be

three-state, and the crystal oscillator disabled. The clock must meet the same

requirements as above. It is highly recommended that the internal clock be used in

order to ensure that the output video remain within the specifications defined by

the relevant video standard. Any aberration in the source clock is reflected in the

output video and detracts from the quality of the image.

The BY_PLL bit will bypass the PLL, and the encoder clock will be at the

crystal frequency. This bit will take precedence over the EN_XCLK bit.

The second timing generator controls the generation of the HSYNC*,

VSYNC*, BLANK*, and pixel input clocking. This is normally the same clock as

the encoding clock. The EN_ASYNC register bit, if set, will allow this clock to be

driven directly by the CLKI pin. If the DIV2 register bit is set, this internal clock

is divided by two before driving the second timing generator. This is required for

interlaced input to interlaced output mode (i.e., CCIR601 applications).

The CLKI pin is the clock used for synchronizing the pixel inputs (P[23:0])

and any timing input signals (HSYNC*, VSYNC*, and BLANK*) and normally

must be a delayed version of the CLKO pin. It can be directly connected to CLKO

if desired. Data is registered with this input and re-synchronized to the internal

clock. Normally, in muxed input mode, both edges of the CLKI input are used. If

the MODE2X register bit is set, the internal clock is divided by two, allowing a 2x

external clock, and the data to be provided on the rising edge only.

1.3.7 Master and Slave Modes

The device can operate as either a timing master or a slave. In master mode, the

device will generate and output HSYNC*, VSYNC*, and BLANK*. In slave

mode, these must be provided externally. The desired mode is selected by the

SLAVE pin and SLAVER bit.

It is highly recommended that the device operate as a master, to ensure that

the input and output video streams remain synchronized. If the device supplying

the HSYNC* and VSYNC* inputs in slave mode is not correctly programmed, or

the timing varies from that which is required, the output image will lose lock with

the input. By running the device in master mode, any timing errors that occur can

be absorbed to some extent by the on-board FIFO.

Bt868/Bt869

1.0 Functional Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1.3 Circuit Description

100123B

Conexant

1-15

1.3.8 Input Formats

The device can convert a wide range of input formats to television video formats.

The input format can be either non-interlaced computer video in 640 x 480 or

800 x 600 formats, or interlaced formats such as CCIR601 formats as well as

most other formats which might be encountered. For detailed information on the

CCIR601 mode, please refer to the "DVD Movie Playback Architecture and

Solutions Application Note". This application note may be obtained from your

local Conexant Semiconductor sales office.

1.3.9 Pixel Input Timing

The device can accept the input in data either RGB or YCrCb color spaces. Data

can be input either a full pixel at a time, clocked in on the rising edge of CLKI, or

in various multiplexed modes, using both edges of CLKI.

In YCrCb mode, either 24-bit 4:4:4 data or 16-bit 4:2:2 data can be input. In

RGB mode, either 15 bit 5:5:5, 16 bit 5:6:5, or 24-bit RGB can be input. In 16-bit

4:2:2 YCrCb input mode, multiplexed Y, Cr, and Cb data is input through the

P[11:4] inputs. The Y data is input on the falling edge of CLK. The Cr/Cb data is

input on the rising edge of CLK. The Cb/Y/Cr/Y sequence begins at the first

active pixel. In 24-bit 4:4:4 YCrCb input mode, multiplexed Y, Cr, and Cb data is

input through the P[11:0] inputs. The input data is sampled on both the rising and

falling edge of CLK. In RGB input mode, input data is sampled as 12 bits in

24-bit RGB mode or 8 bits in 15/16 bit RGB mode on both the rising and falling

edge of CLK.

Table 1-2

shows the assignments of input P[11:0] data on rising

edge and falling edge of CLK.

In addition, all 24-bit modes can utilize a non-multiplexed mode. See

Table

1-3 on page 1-5

.

1.3.10 Output Modes

The encoder can generate the video as Composite/Y-C, as YUV component, or as

VGA-style RGB. These modes are selected by the OUT_MODE[1:0] register

bits.

When outputting RGB, the device will output VGA/SVGA analog RGB. In

this mode, the R, G, and B input data is fed to the DACs after the addition of sync

and, if the SETUP bit is set, setup. The output currents are scaled so that the

DACs output the proper 1 V full-scale levels for driving a monitor. The graphics

controller provides all the timing control for the monitor, and the device operates

as a slave. Only the P[23:0], BLANK*, HSYNC*, and VSYNC* input pins and

the RGB analog output pins are active. The BLANK*, HSYNC*, and VSYNC*

pins are automatically enabled as inputs in this mode.

Each of the three video signals generated by the OUT_MODE bits can be

multiplexed to any DAC using the OUT_MUXA[1:0], OUT_MUXB[1:0], and

OUT_MUXC[1:0] register bits.

1.0 Functional Description

Bt868/Bt869

1.3 Circuit Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1-16

Conexant

100123B

1.3.11 YCrCb Inputs

Y has a nominal range of 16≠235; Cb and Cr have a nominal range of 16≠240,

with 128 equal to zero. Values of 0 and 255 are interpreted as 1 and 254,

respectively. Y values of 1≠15 and 236≠254, and CrCb values of 1≠15 and

241≠254, are interpreted as valid linear values.

Figure 1-4

shows the frequency response of the sub-sampling process. If 4:4:4

data is input, it is sub-sampled to 4:2:2 prior to overscan compensation and flicker

filtering.

The resulting 4:2:2 output must then be converted to YUV values and then

scaled for the output range of the DACs. The MY, MCR, and MCB registers must

be programmed to perform this conversion. The scaling equations are as follows:

MY = (int) [V100/(219.0

*

VFS)

*

2

6

+ 0.5]

MCR = (int)[(128.0/127.0)

*

V100

*

0.877/(224.0

*

VFS

*

0.713

*

sinx)

*

2

6

+

0.5]

MCB = (int)[(128.0/127.0)

*

V100

*

0.493/(224.0

*

VFS

*

0.564

*

sinx)

*

2

6

+ 0.5]

where:V

100

= 100% white voltage (0.661 V for NTSC, 0.7 V for PAL)

V

FS

= Full scale output voltage (1.28 V)

SINX = SIN (2

F

SC

/F

CLK

)/(2

F

SC

/F

CLK

)

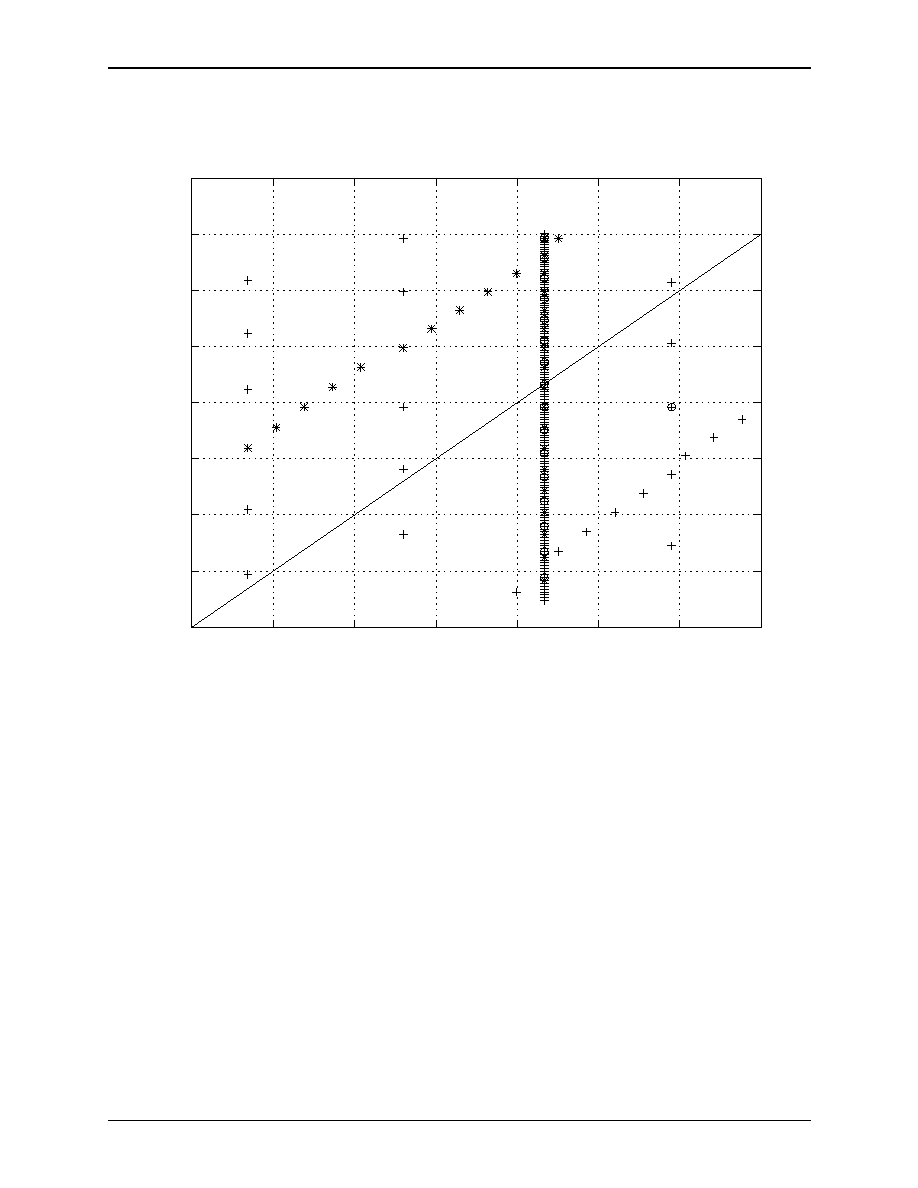

Figure 1-4. Decimation Filter at Fs=27 MHz

Freq (Fs=27MHz

De

c

i

be

l

s

(

d

B

)

Chroma Decimation Filter

Bt868/Bt869

1.0 Functional Description

Flicker-Free Video Encoder with Ultrascale

TM

Technology

1.3 Circuit Description

100123B

Conexant

1-17

1.3.12 RGB Inputs