| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ISD1016AP | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

1≠1

Information Storage Devices, Inc.

1

Æ

FEATURES

∑

Easy-to-use single-chip voice Record/Play-

back solution

∑

High-quality, natural voice/audio

reproduction

∑

Manual switch or microcontroller compatible

≠

Playback can be edge- or level-

activated

∑

Single-chip durations of 16 and 20 seconds

∑

Directly cascadable for longer durations

∑

Power-down mode

≠

1

µ

A standby current (typical)

∑

Zero-power message storage

≠

Eliminates battery backup circuits

∑

Fully addressable to handle multiple

messages

∑

100-year message retention (typical)

∑

100,000 record cycles (typical)

∑

On-chip clock source

∑

No algorithm development required

∑

Single +5 volt supply

∑

Available in die form, DIP, and SOIC

packaging

∑

Industrial temperature (-40

∞

C to +85

∞

C)

version available

ISD1000A Series

Single-Chip Voice Record/Playback Devices

16- and 20-Second Durations

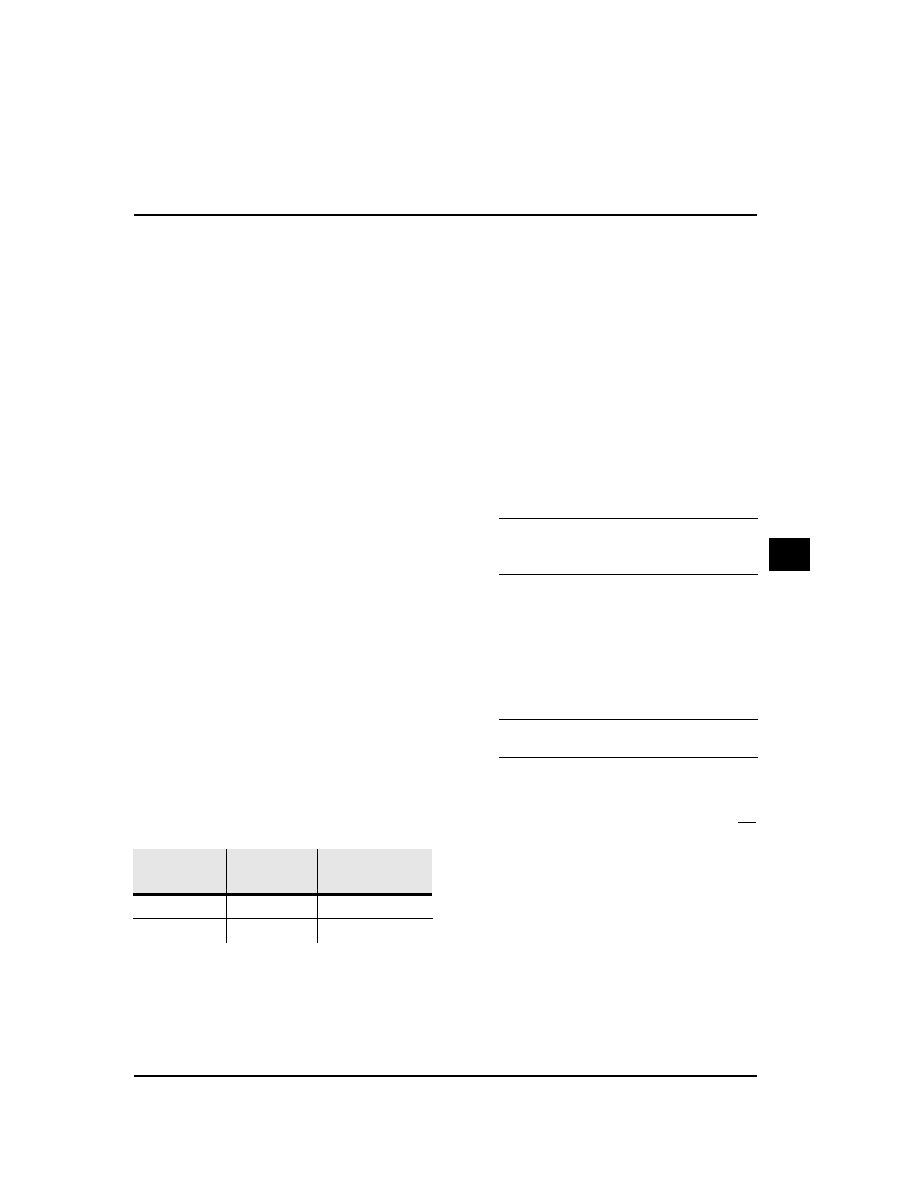

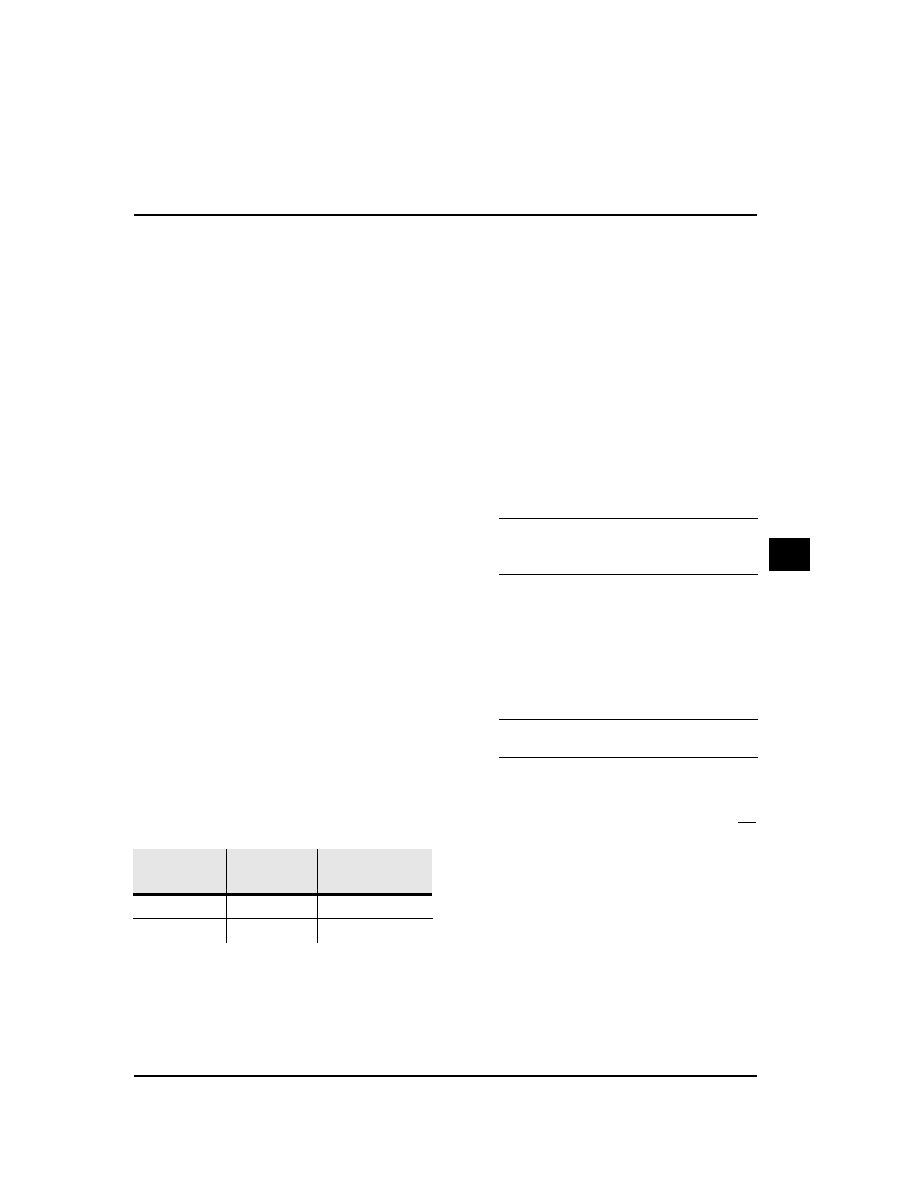

ISD1000A SERIES SUMMARY

Part

Number

Duration

(Seconds)

Input Sample

Rate (KHz)

Typical Filter

Pass Band

(KHz)

ISD1016A

16

8

3.4

ISD1020A

20

6.4

2.7

06.DataBook_1000A Dsht Page 1 Friday, September 27, 1996 10:44 AM

Product Data Sheets

ISD1000A Series

1≠2

-

1

GENERAL DESCRIPTION

Information Storage Devices' ISD1000A Chip-

Corder

Æ

Series provides high-quality, single-chip

record/playback solutions for 16- and 20-second

messaging applications. The CMOS devices

include an on-chip oscillator, microphone pream-

plifier, automatic gain control, antialiasing filter,

smoothing filter, and speaker amplifier. In addi-

tion, the ISD1000A Series is fully microprocessor-

compatible, allowing complex messaging and

addressing to be achieved.

Recordings are stored in on-chip nonvolatile

memory cells, providing zero-power message

storage. This unique, single-chip solution is made

possible through ISD's patented multilevel stor-

age technology. Voice and audio signals are

stored directly into memory in their natural form,

providing high-quality, solid-state voice reproduc-

tion.

DETAILED DESCRIPTION

The ISD1000A ChipCorder Series devices are

designed to Record and Play back audio and

voice information in a single chip with a minimum

of circuit complexity. This compact, easy-to-use,

nonvolatile, low-power solution has been made

possible by ISD's multilevel storage technology --

a breakthrough in storage technology in EEPROM.

ISD's multilevel storage technology results in stor-

age density that is eight times greater than digital

memory. The ISD1000A nonvolatile analog array

consists of 128K cells -- the equivalent of 1 Mbits

of digital storage.

The ISD1000A Series eliminates the need for dig-

ital conversion, digital compression, and voice

synthesis techniques which often compromise

voice quality and are more complicated to use.

The ISD1000A Series includes signal conditioning

circuits and control functions which enable a com-

plete, high-quality Recording and Playback sys-

tem in a single device. The ISD1000A is available

in two versions, which store voice in 16- or 20-sec-

ond arrays. Additional devices may be cascaded

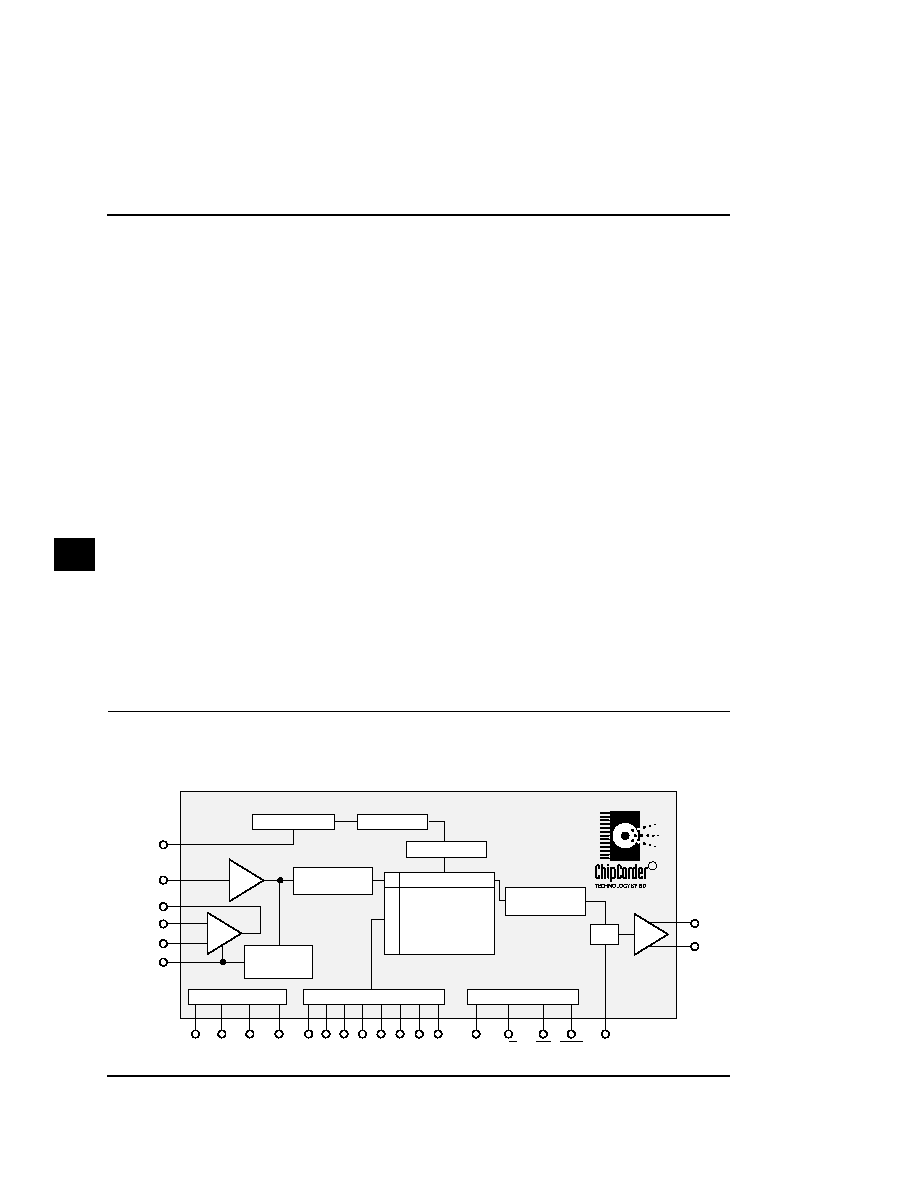

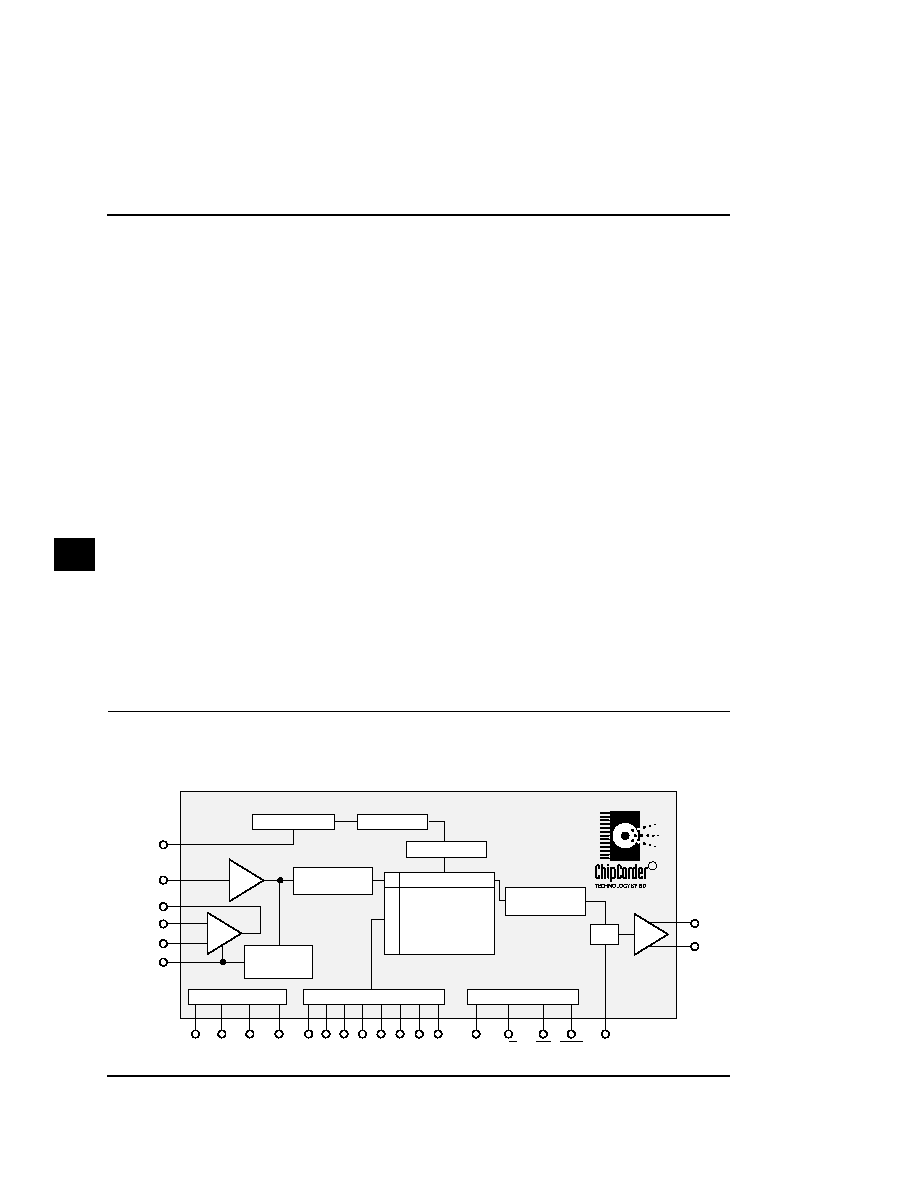

ISD1000A SERIES BLOCK DIAGRAM

Amp

Timing

Internal Clock

Pre-

Amp

V

CCA

V

CCD

Power Conditioning

A0

A2 A3 A4 A5

A7

A6

Address Buffers

ANA IN

ANA OUT

MIC

MIC REF

AGC

Analog Transceivers

Decoders

128 K Cell

Nonvolatile

Multilevel Storage

Array

Amp

Sampling Clock

PD

P/R

CE

EOM

Device Control

XCLK

AUX IN

SP+

SP≠

Mux

V

SSA

V

SSD

A1

Automatic

Gain Control

(AGC)

5-Pole Active

Antialiasing Filter

5-Pole Active

Smoothing Filter

R

06.DataBook_1000A Dsht Page 2 Friday, September 27, 1996 10:44 AM

Product Data Sheets

ISD1000A Series

1≠3

1

to achieve longer recording durations. The non-

volatile storage array is based on production-

proven, low-power CMOS EEPROM technology.

The highly integrated ISD1000A Series contains

all the basic functions required for high-quality

voice Recording and Playback. The noise-cancel-

ling Microphone Preamplifier and Automatic Gain

Control (AGC) record both low-volume and high-

volume sounds. The AGC attack and release

times are adjusted by an external resistor and

capacitor. Antialiasing is performed by a continu-

ous fifth-order Chebyshev filter, requiring no exter-

nal components or clocks to give toll-quality

reproduction. The low corner of the passband is

user-settable by two external capacitors. The

devices contain their own temperature-stabilized

timebase oscillator.

The ISD1000A devices drive a speaker directly

through differential outputs. This boosts power by

four times and eliminates the need for a series

capacitor or an output amplifier. The device will

operate from a single power supply or from batter-

ies. The device also includes a power down func-

tion for applications where minimum power

consumption is critical. The CMOS-based design,

combined with the nonvolatile storage array,

assures the lowest possible overall power con-

sumption.

On-chip control functions make the ISD1000A

Series very easy to use in a wide array of applica-

tions. Each device offers a variety of operating

modes and interface options. The devices may be

used in applications that require little more than a

few switches and a battery. The devices may also

be integrated into electronic systems where digital

addresses can be provided for more sophisti-

cated message addressing and control. The

ISD1000A array is organized into 160 segments.

Addresses A0 through A7 provide access to each

segment in the array for message addressing.

Addressing provides the capability of construct-

ing messages by combining stored phrases and

sounds.

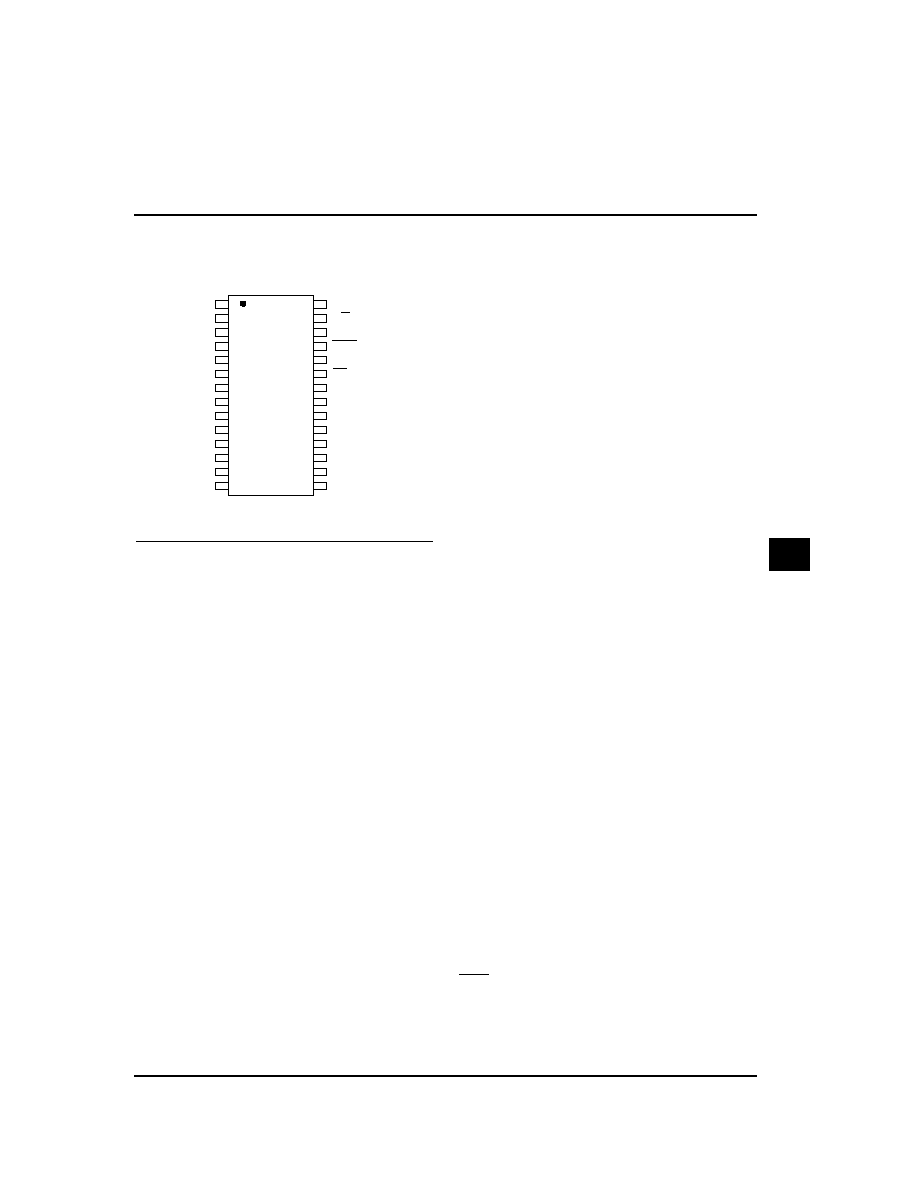

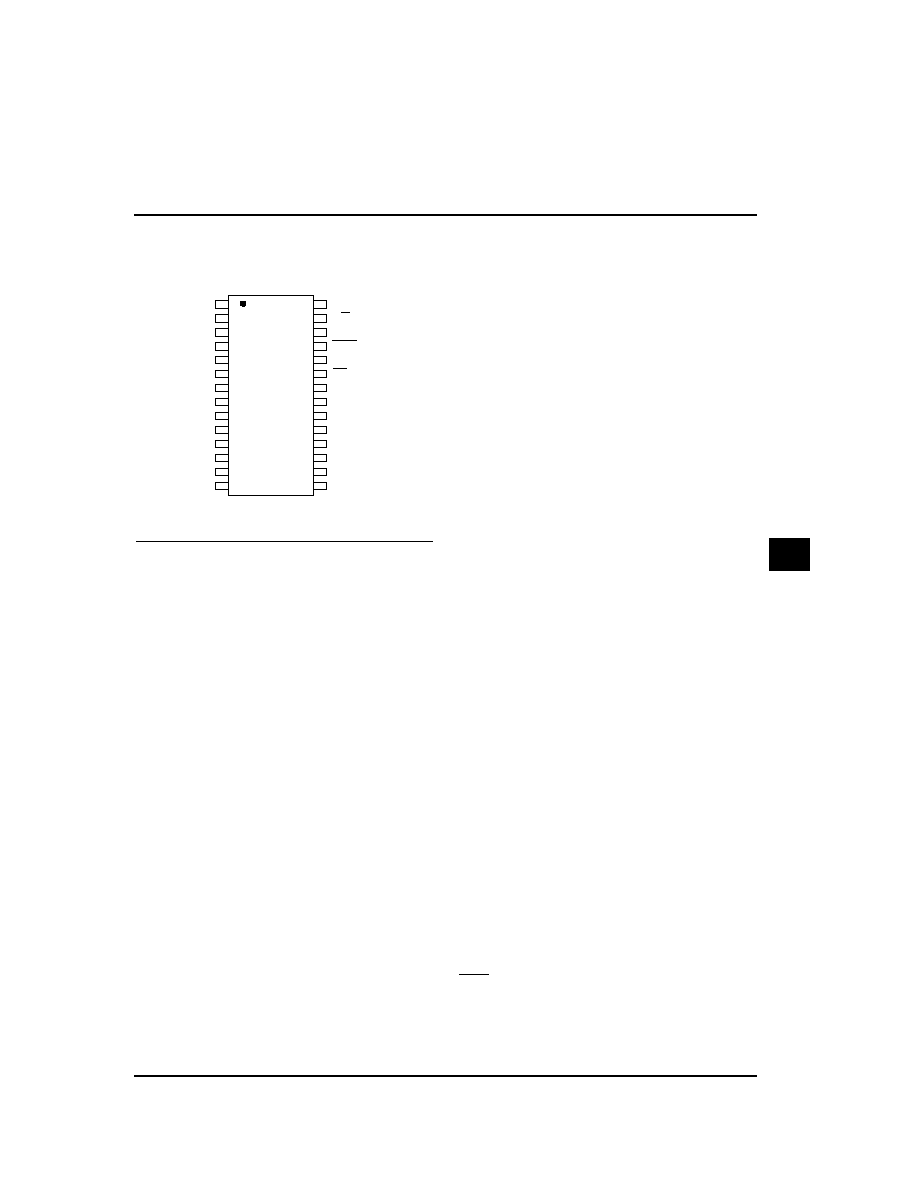

PIN DESCRIPTIONS

Voltage Inputs (V

CCA

, V

CCD

)

To minimize noise, the analog and digital circuits

in the ISD1000A Series devices use separate

power busses. These voltage busses are brought

out to separate pins and should be tied together

as close to the supply as possible. In addition,

these supplies should be decoupled as close to

the package as possible.

Ground Inputs (V

SSA

, V

SSD

)

The ISD1000A Series of devices utilizes separate

analog and digital ground busses. These pins

should be tied together as close to the package

as possible and connected through a low-imped-

ance path to power supply ground.

Power Down Input (PD)

When not recording or playing back, the PD pin

should be pulled HIGH to place the part in a very

low power mode (see I

SB

specification). When

EOM pulses LOW for an overflow condition, PD

should be brought HIGH to reset the address

pointer back to the beginning of the Record/Play-

back space.

SSD

SSA

M0/A0

M1/A1

M2/A2

M3/A3

M4/A4

M5/A5

NC

NC

A6

A7

AUX IN

V

V

SP+

V

P/R

XCLK

EOM

PD

CE

NC

ANA OUT

ANA IN

AGC

MIC REF

MIC

V

SP≠

CCD

CCA

DIP/SOIC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

ISD1000A SERIES PINOUTS

06.DataBook_1000A Dsht Page 3 Friday, September 27, 1996 10:44 AM

Product Data Sheets

ISD1000A Series

1≠4

-

1

Chip Enable Input (CE)

The CE pin is taken LOW to enable all Playback

and Record operations. The address inputs and

Playback/Record input (P/R) are latched by the

falling edge of CE. When CE is taken HIGH, the

ISD1000A is unselected, the P/R is HIGH, and the

auxiliary input is directed into the speaker ampli-

fier.

Playback/Record Input (P/R)

The P/R input is latched by the falling edge of the

CE pin. A HIGH level selects a Playback cycle

while a LOW level selects a Record cycle. For a

Record cycle, the address inputs provide the

starting address and recording continues until PD

or CE is pulled HIGH or an overflow is detected

(i.e. the chip is full). When a Record cycle is termi-

nated by pulling PD or CE HIGH, an End-Of-Mes-

sage (EOM) marker is stored at the current

address in memory. For a Playback cycle, the

address inputs provide the starting address and

the device will play until an EOM marker is

encountered. The device can continue past an

EOM marker in an operational mode, or if CE is

held LOW in address mode. (See page 1-6 for

more Operational Modes).

End-Of-Message Output (EOM)

A non-volatile marker is automatically inserted at

the end of each recorded message. It remains

there until the message is recorded over. During

Playback, the EOM output pulses LOW for a

period of T

EOM

at the end of each message, or in

the event of a message overflow (device full).

In addition, the ISD1000A Series has an internal

V

CC

detect circuit to maintain message integrity

should V

CC

fall below 3.5V. In this case, EOM

goes LOW and the device is fixed in Playback-

only mode. The EOM marker provides a conve-

nient handshake signal for a processor, and also

facilitates the cascading of devices.

Microphone Input (MIC)

The microphone input transfers its signal to the

on-chip preamplifier. An on-chip Automatic Gain

Control (AGC) circuit controls the gain of this

preamplifier from -15 to 24 dB. An external micro-

phone should be AC coupled to this pin via a

series capacitor. The capacitor value, together

with the internal 10 Kohm resistance on this pin,

determines the low-frequency cutoff for the

ISD1000A Series passband. See ISD's Applica-

tion Notes and Design Manual in this book for

additional information on low-frequency cutoff cal-

culation.

Microphone Reference Input (MIC REF)

The MIC REF input is the inverting input to the

microphone preamplifier. This provides a noise-

canceling or common-mode rejection input to the

device when connected to a differential micro-

phone.

IF

THIS

INPUT

IS

UNUSED

,

IT

MUST

BE

LEFT

DISCONNECTED

.

Automatic Gain Control Input (AGC)

The AGC dynamically adjusts the gain of the

preamplifier to compensate for the wide range of

microphone input levels. The AGC allows the full

range of whispers to loud sounds to be recorded

with minimal distortion. The "attack" time is deter-

mined by the time constant of a 5 K

internal

resistance and an external capacitor (C2) con-

nected from the AGC pin to V

SSA

analog ground.

The "release" time is determined by the time con-

stant of an external resistor (R2) and an external

capacitor (C2 on the schematic on page 1-17)

connected in parallel between the AGC Pin and

V

SSA

analog ground. Nominal values of 470 K

and 4.7

µ

F give satisfactory results, in most cases.

For AGC voltages of 1.5V and below, the pream-

plifier is at its maximum gain of 24 dB. Reduction

in preamplifier gain occurs for voltages of approx-

imately 1.8V.

06.DataBook_1000A Dsht Page 4 Friday, September 27, 1996 10:44 AM

Product Data Sheets

ISD1000A Series

1≠5

1

Analog Output (ANA OUT)

This pin provides the preamplifier output to the

user. The voltage gain of the preamplifier is deter-

mined by the voltage level at the AGC pin. It has a

maximum gain of about 24 dB for small input sig-

nal levels.

Analog Input (ANA IN)

The analog input pin transfers its signal to the chip

for recording. For microphone inputs, the ANA

OUT pin should be connected via an external

capacitor to the ANA IN pin. This capacitor value,

together with the 2.7 K

input impedance of ANA

IN, is selected to give additional cutoff at the low-

frequency end of the voice passband. If the

desired input is derived from a source other than

a microphone, the signal can be fed, capacitively

coupled, into the ANA IN pin directly.

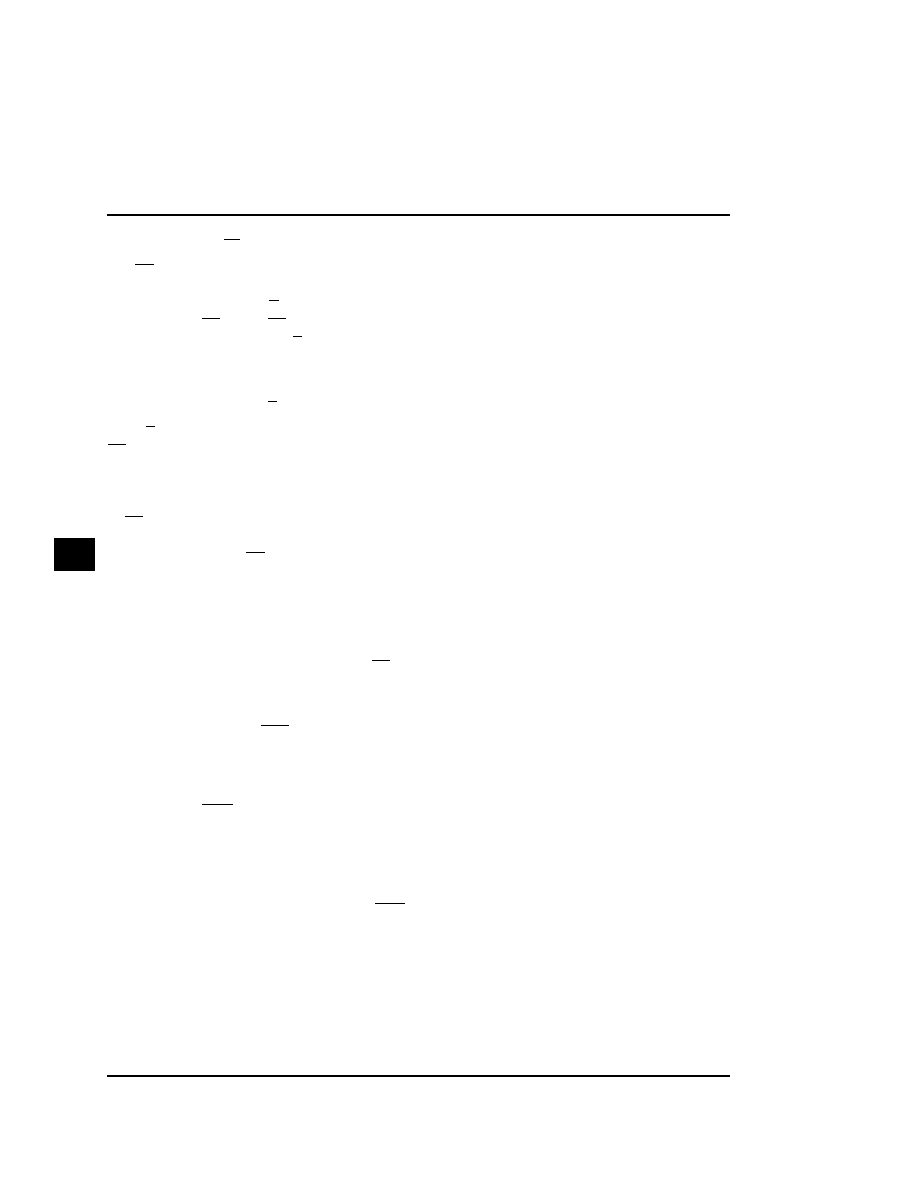

Optional External Clock Input (XCLK)

ISD1000A devices are configured at the factory

with an internal sampling clock frequency cen-

tered to

±

1% of specification. The frequency is

maintained to a total variation of

±

2.25% toler-

ance over the entire commercial temperature and

4.5 to 5.5 voltage ranges. The internal clock has a

±

5% tolerance over the industrial temperature

range and 4.5 to 5.5 voltage range. A regulated

power supply is recommended for industrial-tem-

perature-range parts. If greater precision is

required, the device can be clocked through the

XCLK pin as follows.

These recommended clock rates should not be

varied because the antialiasing and smoothing fil-

ters are fixed, and aliasing problems can occur if

the sample rate differs from the one recom-

mended. The duty cycle on the input clock is not

critical, as the clock is immediately divided by

two.

IF

THE

XCLK

IS

NOT

USED

,

THIS

INPUT

MUST

BE

CONNECTED

TO

GROUND

.

Speaker Outputs (SP+/SP-)

All devices in the ISD1000A Series include an on-

chip differential speaker driver, capable of driving

50 milliwatts into 16

from AUX IN (12.2 mW from

memory).

The speaker outputs are held at V

SSA

levels during

record and power down. It is therefore not possi-

ble to parallel speaker outputs of multiple

ISD1000A devices or the outputs of other speaker

drivers.

NOTE

Connection of speaker outputs in parallel

may cause damage to the device.

While a single output may be used alone (includ-

ing a coupling capacitor between the SP pin and

the speaker), these outputs may be used individ-

ually with the output signal taken from either pin.

Using the differential outputs results in a 4:1

improvement in output power.

NOTE

Never ground or drive an output.

Auxiliary Input (AUX IN)

The Auxiliary Input is multiplexed through to the

output amplifier and speaker output pins when CE

is HIGH and Playback has ended, or if the device

is in overflow. When cascading multiple ISD1000A

devices, the AUX IN pin is used to connect a Play-

back signal from a following device to the

previous output speaker drivers. For noise consid-

erations, it is suggested that the Auxiliary Input not

be driven when the storage array is active.

Address/Mode Inputs (Ax/Mx)

The Address/Mode Inputs provide two functions in

the ISD1000A Series: 1. Message address (either

Part

Number

Sample Rate

Required Clock

ISD1016A

8.0 KHz

1024 KHz

ISD1020A

6.4 KHz

819.2 KHz

06.DataBook_1000A Dsht Page 5 Friday, September 27, 1996 10:44 AM