| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: OV7620 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

OV7620 Product Specifications -Rev. 1.3 (5/13/00)

Preliminary

Company Confidential

OV7620 SINGLE-CHIP CMOS VGA COLOR DIGITAL CAMERA

Features

∑ 326,688 pixels, 1/3" lens, VGA / QVGA format

∑ Read out - progressive / Interlace

∑ Data format - YCrCb 4:2:2, GRB 4:2:2, RGB Raw Data

∑ 8/16 bit video data: CCIR601, CCIR656, ZV port

∑ Video Timing - 525 line, 30 fps

∑ Wide dynamic range, anti-blooming, zero smearing

∑ SCCB (Serial Camera Control Bus) interface

∑ Electronic exposure / Gain / white balance control

∑ Image enhancement - brightness, contrast, gamma, saturation,

sharpness, window, etc.

∑ Internal / external synchronization scheme

∑ Frame exposure / line exposure option

∑ 5 Volt operation, low power dissipation.

General Description

OV7620 is a highly integrated high resolution

(640x480) Interlaced / Progressive Scan CMOS digital

color / black&white video camera chip. The digital

video port supports 60Hz YCrCb 4:2:2 16Bit / 8 Bit for-

mat, ZV Port output format, RGB raw data 16Bit/8Bit

output format and CCIR601/CCIR656 format. The built-

in SCCB interface provides an easy way of controlling

the built-in camera functions.

∑ Video Conferencing

∑ Video Phone

∑ Video Mail

∑ Still Image

∑ PC Multimedia

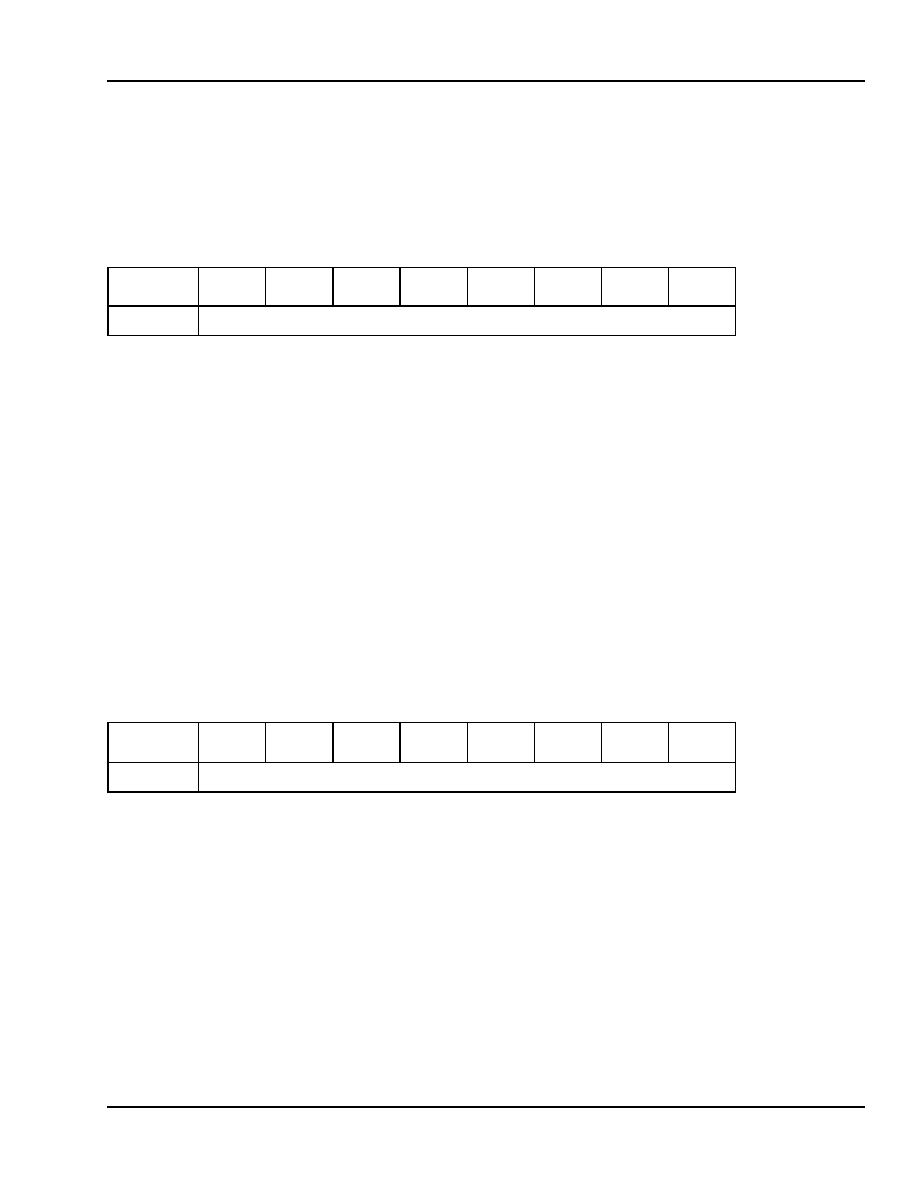

OV7001 48-Pin Out Diagram

U

V

7

/

B

8

U

V

6

/

B

P

C

L

R

U

V

5

/

M

I

R

U

V

4

/

S

L

A

E

N

U

V

3

/

E

C

L

K

O

U

V

2

/

Q

V

G

A

U

V

1

/

C

C

6

5

6

U

V

0

/

G

A

M

D

I

S

X

C

L

K

1

X

C

L

K

2

D

V

D

D

D

G

N

D

6

5

4

3

2

1

4

8

4

7

4

6

4

5

4

4

4

3

A

G

N

D

V

R

E

Q

F

R

E

X

A

G

C

E

N

/

R

A

M

I

N

T

R

E

S

E

T

S

V

D

D

S

G

N

D

M

I

D

S

I

O

-

0

S

I

O

-

1

A

V

D

D

A

G

N

D

7

8

9

10

11

12

13

14

15

16

17

18

AGND

AVDD

PWDN

VRS

VCCHG

SBB

VTO

AVDD

AGND

VSYNC/CSYS

FODD/SRAM

HREF/VSRAM

31

32

33

34

35

36

37

38

39

40

41

42

DOGND

DOVDD

PCLK/OUTX2

Y7/CS0

Y6/CS2

Y5/SHARP

Y4/CS1

Y3/RAW

Y2/G2X

Y1/PROG

Y0/CBAR

CHSYNC/BW

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

OV7620

Array Elements

664 x 492

Pixel Size

7.6 x 7.6 um

Image Area

4.86 x 3.64mm

Electronic

Exposure

500 : 1

Scan Mode

progressive

interlace

Gamma

Correction

128 Curve Settings

See specifics

Minimum

Illumination

2.5 lux @ f1.4

0.5 lux @ f1.4

(3000K)

S/N Ratio

> 48dB

Power Supply

5VDC, ±5%

Power

Requirements

<120mW Active

<10uW Standby

Package

48-pin LCC

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

2

Preliminary

Company Confidential

SECTION 1

PRODUCT OVERVIEW

OV7620 is a highly integrated high resolution (640x480) Interlaced / Progressive Scan CMOS

digital color / black&white video camera chip. The digital video port supports 60Hz YCrCb 4:2:2

16Bit / 8 Bit format, ZV Port output format, RGB raw data 16Bit/8Bit output format and CCIR601/

CCIR656 format. The built-in SCCB (Serial Camera Control Bus) interface provides an easy way

of controlling the built-in camera functions.

1.1 FEATURES

∑ Single chip digital color/black&white video camera chip.

∑ Scanning - Interlaced / Progressive Scan.

∑ Format - 1/3" lens compatible.

∑ Image area -4.86X 3.64mm.

∑ Total active pixel elements - (H)664 x (V)492 square pixel.

∑ Default active pixel element -(H)640 x (V)480.

∑ Pixel size: 7.6 x 7.6um.

∑ 10Bit two channel internal A/D Converter and 8/10 Bit Output.

∑ PCLK and HREF polarity programmable.

∑ Digital Output format -

YCrCb 16bit/8bit selectable

60Hz 16 Bit YCrCb 4:2:2 - 640x480

60Hz 8 Bit YCrCb 4:2:2 - 640x480

RGB Raw Data Digital Output 16Bit/8Bit selectable

∑ Two-line output:

∑ Y Channel: B G B G B G ...

∑ UV Channel: G R G R G R ...

Two-line alternate output:

Y Channel: G G G G G G ...

UV Channel: B R B R B R ...

One-line output, use Y Channel only, effective only in Progressive Scan Mode

1st line: B G B G B G B G...

2nd line: G R G R G R G R ...

∑ CCIR601 /CCIR656 standard.

∑ YCrCB or YUV output format to support TV or monitor display

∑ ZV Port YUV 16 Bit format.

∑ QVGA format(320x240).

∑ Y/UV or RGB output byte MSB and LSB swap.

∑ SCCB interface, support fast mode: 400 kBit/s.

∑ External Field Sync input.

∑ External Horizontal / Vertical Sync input format, OV7620 worked as slave chip.

∑ Support external micro-controller and RAM interface

∑ Progressive Scan mode: support whole-frame exposure.

∑ Programmable frame rate - 0.5 to 30fps.

∑ Electronic shutter setting (use 27Mhz crystal and default clock rate).

Interlaced: 1/60 to

1

/

15734

(s)

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

3

Preliminary

Company Confidential

Progressive Scan: 1/30 to 1/15734(s)

∑ AGC (+24dB) - auto / programmable.

∑ PreAmp Gain 6/12 db.

∑ Auto-Exposure-ratio programmable.

∑ White balance - auto/programmable.

∑ Auto-White-Balance-ratio programmable.

∑ Brightness & contrast adjustment.

∑ Color Saturation adjustment.

∑ Aperture correction.

∑ Multiple gamma correction curve selection.

∑ Multiple luminance gamma correction curve selection.

∑ S/N ratio > 48 dB.

∑ Software/Hardware Reset.

∑ Software/hardware power saving control

∑ Minimum illumination 2.5 lux at f1.4 (3000k).

∑ Optical fill factor is 40%.

∑ Supply: 5 volt for analog and Digital circuit;5volt or 3.3volt for digital interface.

∑ Power consumption < 120 mW.

∑ Power-save mode < 10 uA.

∑ Chip SCCB ID: 0 1 0 CS2 CS1 CS0 1 R/W (CS2 CS1 CS0 select by PIN when power-on, default 0).

∑ 48pin package.

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

4

Preliminary

Company Confidential

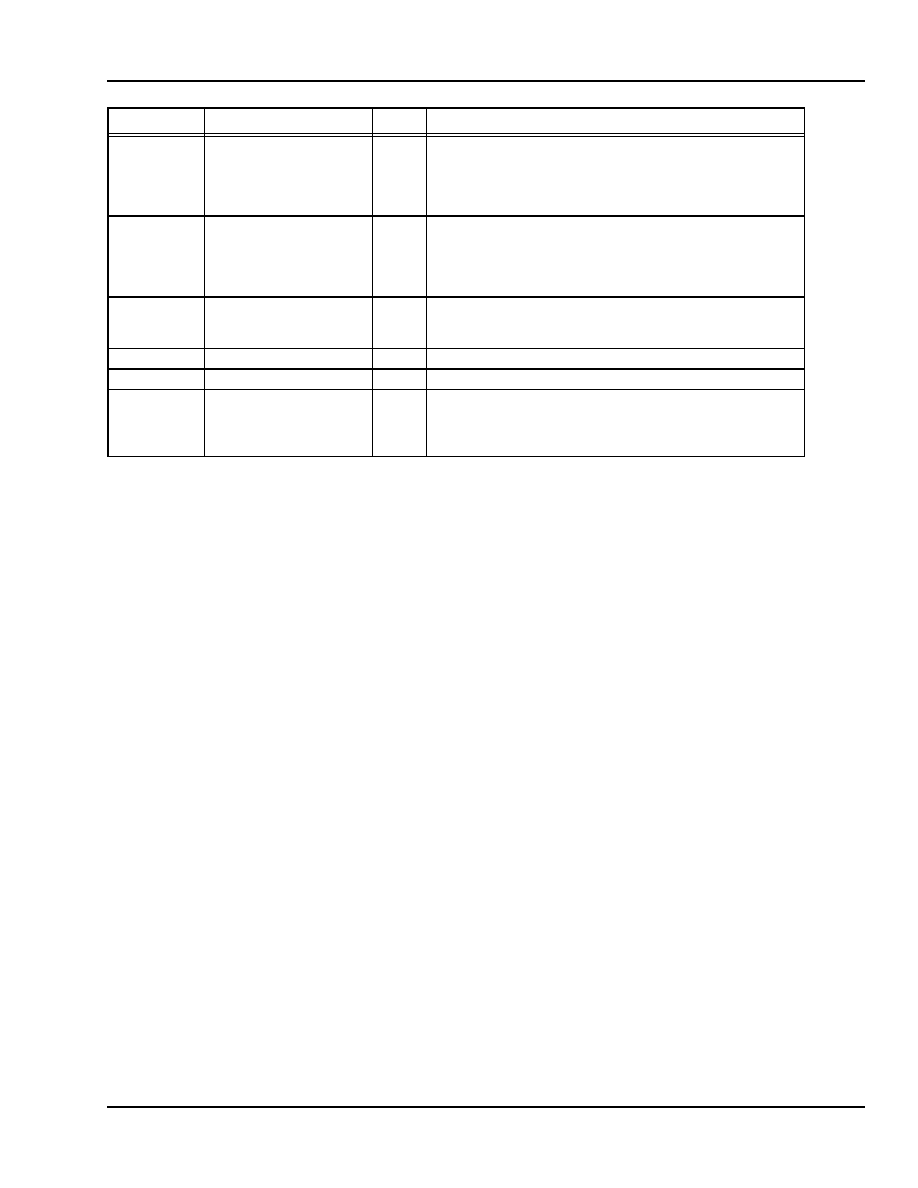

1.2 Pin Assignments

Table 1:Pin Descriptions

(Pin type and default level: I-1: digital input+10k pull up; I-0: digital input +10k pull

down, XI/XO; xtal IO; /Secondary functions are set during power up; O/I: digital CMOS level output Bias: power

supply bias.).

Pin #

Name

Class

Function

1

SVDD

Bias

Sensing Power (+5V) pins.

8, 14,44

AVDD

Bias

Analog Power (+5V) pins.

29

DVDD

Bias

Digital Power (+5V) pins.

32

DOVDD

Bias

Digital I/O Power (+5V / +3.3V) pins.

48

SGND

Bias

Sensing ground connections. Connect to supply common

6, 7, 15, 43

AGND

Bias

Analog ground connections. Connect to supply common

30

DGND

Bias

Digital ground connection. Connect to supply common

31

DOGND

Bias

Digital Output ground connection.

2

RESET

I

Chip reset, "high" active.

3

AGCEN/RAMINT

I-I

AGCEN =1 enables the Auto Gain Control. AGCEN = 0 disables it.

This pin setting is effective when pin SBB = 1.

RAMINT=1 initializes frame transfer.

4

FREX

I

Frame exposure control input, effective in progressive scan only.

The positive width of FREX defines the exposure time.

5

VrEQ

CAP

Internal voltage reference. Requires an 0.1uF decoupling capacitor

to ground.

9

PWDN

I-0

PWDN =1 puts chip in power down (sleep) mode.

10

VrS

CAP

Internal voltage reference. Requires an 0.1uF decoupling capacitor

to ground.

11

VcCHG

CAP

Internal voltage reference. Requires an 1.0uF decoupling capacitor

to ground.

12

SBB

I

SBB = 1 selects the power-up method of programming the internal

functions. SBB = 0 selects the SCCB pin programming method.

Results of the power-up method can only be changed by a new

power-up or reset sequence.

13

VTO

O

Video Test Output (NTSC)

16

VSYNC/CSYS

O/I

VSYNC: Vertical sync output. This pin is asserted high during sev-

eral scan lines in the vertical sync period.

CSYS: Composite Sync. When not using SCCB, a 10k pull up

changes pin 42(CHSYNC) to CSYS.

17

FODD/SRAM

O/I

FODD: Odd field flag. Asserted high during the odd field, low during

the even field.

SRAM: External SRAM

18

HREF/VSFRAM

O/I

HREF: Horizontal window reference output. HREF is high during the

active pixel window, otherwise low.

VSFRAM: Vertical Sync Frame.

19

UV7/B8

O/I

UV7: Digital output UV bus. UV7 used for 16-bit operation for out-

putting chrominance data.

B8: Switch for 8 bit mode luminance/Chroma tristate. Default is 16

bit mode.

20

UV6/BPCLR

O/I

UV6: Digital output UV bus. UV6 used for 16-bit operation for out-

putting chrominance data.

BPCLR: Bypass RGB color matrix.

21

UV5/MIR

O/I

UV5: Digital output UV bus. UV5 used for 16-bit operation for out-

putting chrominance data.

MIR: Mirror.

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

5

Preliminary

Company Confidential

22

UV4/SLAEN

O/I

UV4: Digital output UV bus. UV4 used for 16-bit operation for out-

putting chrominance data.

SLAEN: Slave Enable.

23

UV3/ECLKO

O/I

UV3: Digital output UV bus. UV3 used for 16-bit operation for out-

putting chrominance data.

ECKLO: Swap clock output - changes pin 17(FODD) to XCLK out.

24

UV2/QVGA

O/I

UV2: Digital output UV bus. UV2 used for 16-bit operation for out-

putting chrominance data.

QVGA: QVGA format (320x240)

25

UV1/CC656

O/I

UV1: Digital output UV bus. UV1 used for 16-bit operation for out-

putting chrominance data.

CC656: CCIR 656 mode.

26

UV0/GAMDIS

O/I

UV0: Digital output UV bus. UV0 used for 16-bit operation for out-

putting chrominance data.

GAMDIS: Disables Chroma Gamma (RGB).

27, 28

XCLK1, XCLK2

XO, XI

XCLK1 and XCLK2 are the input/output of the on-chip video oscilla-

tor. Nominal crystal clock frequency is 27MHz. If an external clock is

used, input to XCLK1, leave XCLK2 unconnected.

33

PCLK/OUTX2

O/I

PCLK: Pixel clock output. By default, data is updated at the falling

edge of PCLK and is stable at its rising edge. PCLK runs at the pixel

rate in 16-bit bus operations and twice the pixel rate in 8-bit bus

operations

OUTX2: Doubles current output.

34

Y7/CSO

O/I

Y7: Digital output Y bus. In a 16-bit operation, the luminance data is

clocked out of this bus at the rate of one byte per pixel. In 8-bit oper-

ation, the luminance data and the chrominance data is multiplexed

to this bus.

CSO: ID configuation bit for the SCCB slave ID.

35

Y6/CS2

O/I

Y6: Digital output Y bus. In a 16-bit operation, the luminance data is

clocked out of this bus at the rate of one byte per pixel. In 8-bit oper-

ation, the luminance data and the chrominance data is multiplexed

to this bus.

CS2: ID configuation bit for the SCCB slave ID.

36

Y5/SHARP

O/I

Y5: Digital output Y bus. In a 16-bit operation, the luminance data is

clocked out of this bus at the rate of one byte per pixel. In 8-bit oper-

ation, the luminance data and the chrominance data is multiplexed

to this bus.

SHARP: Enable Analog Sharpness.

37

Y4/CS1

O/I

Y4: Digital output Y bus. In a 16-bit operation, the luminance data is

clocked out of this bus at the rate of one byte per pixel. In 8-bit oper-

ation, the luminance data and the chrominance data is multiplexed

to this bus.

CS1: ID configuation bit for the SCCB slave ID.

38

Y3/RAW

O/I

Y3: Digital output Y bus. In a 16-bit operation, the luminance data is

clocked out of this bus at the rate of one byte per pixel. In 8-bit oper-

ation, the luminance data and the chrominance data is multiplexed

to this bus.

RAW: Raw Data.

39

Y2/G2X

O/I

Y2: Digital output Y bus. In a 16-bit operation, the luminance data is

clocked out of this bus at the rate of one byte per pixel. In 8-bit oper-

ation, the luminance data and the chrominance data is multiplexed

to this bus.

G2X: Gain 2X.

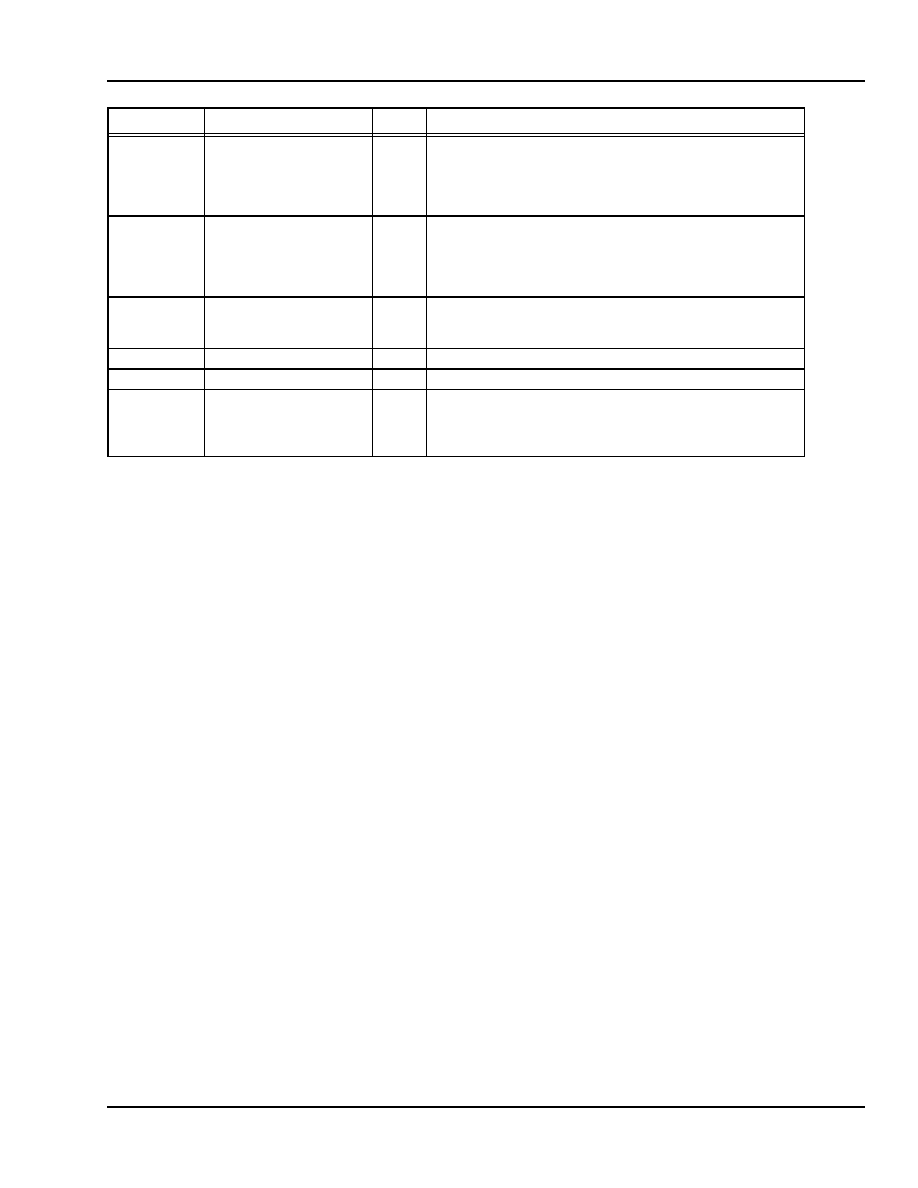

Pin #

Name

Class

Function

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

6

Preliminary

Company Confidential

40

Y1/PROG

O/I

Y1: Digital output Y bus. In a 16-bit operation, the luminance data is

clocked out of this bus at the rate of one byte per pixel. In 8-bit oper-

ation, the luminance data and the chrominance data is multiplexed

to this bus.

PROG: Progressive Scan Mode.

41

Y0/CBAR

O/I

Y0: Digital output Y bus. In a 16-bit operation, the luminance data is

clocked out of this bus at the rate of one byte per pixel. In 8-bit oper-

ation, the luminance data and the chrominance data is multiplexed

to this bus.

CBAR: Color Bar Test Pattern.

42

CHSYNC/BW

O/I

CHSYNC: Digital output for either composite sync or horizontal sync

signal.

BW: Enables Black & White.

45

SIO-1

I

SCCB Serial clock input with schmitt trigger.

46

SIO-0

IO

SCCB Serial data, input with schmitt trigger.

47

MID

I-0

Multiple SCCB slave ID enable.

MID = 1 SCCB slave ID is configurable through power up setting in

CS(2:0)

MID = 0 SCCB slave ID is preset to 42H/43H.

Pin #

Name

Class

Function

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

7

Preliminary

Company Confidential

1.3 CHIP OPERATION

Referring to FIG 1.1, OV7620 includes a 664x492 resolution image array, an analog signal pro-

cessor, dual 10bit A/D converters, analog video mux, digital data formatter and video port, SCCB

interface with its registers, the digital controls including timing block, exposure block and white

balance.

FIG 1.1 OV7620Block Diagram

OV7620is a 1/3 inch CMOS imaging device. The sensor contains approximately 326,688 pixels.

It is base on field integration read-out system with line-by-line transfer and an electronic shutter

with synchronous pixel read out scheme. The color filter of the sensor consists of primary color

RG/GB array arranged in line alternating fashion.

RVO

BUO

GYO

image

r

o

w

s

e

l

e

c

t

column sense amp

array

Cb

Cr

Y

VcSAT

GAMMA

white

exposure

detect

WB

control

balance

detect

AWB

AGCEN

XVCLK1

(664X492)

RGB

1/2

sys-clk

AWBTH/

VcCNT

r

g

b

mx

FODD

VSYNC

HREF

PCLK

video

timing

generator

FZEX

exposure

control

VrEQ

VcSHP

FREZ

CHSYNC

mx

ADC

f

o

r

m

a

t

t

e

r

Y(7:0)

UV(7:0)

SCCB

interface

SIO-1

SIO-0

registers

v

i

d

e

o

p

o

r

t

ADC

analog

processing

FSIN

MIR

DENB

mx

PROG

AWBTM

SBB

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

8

Preliminary

Company Confidential

The majority of signal processing is performed in the analog processing block, which does color

separation, matrixing, AGC, gamma correction, color correction, color balance, black level cali-

bration, knee smooth, aperture correction, controls for the luminance and chrominance picture

and anti-alias filtering. The analog video signals are based on the formula:

Y = 0.59G + 0.31R + 0.11B; where R,G,B is the equivalent color components in each pixel

U = R-Y;

V = B-Y;

Another output data format is YCrCb, its formula is as follows:

Y = 0.59G + 0.31R + 0.11B

Cr = 0.713 x (R - Y)

Cb = 0.564 X (B - Y)

The YCrCb /RGB Raw Data signal is fed to two 10 bit A/D converters, one for the Y/R&G chan-

nel, one is shared by Cr&Cb / B&G channels. The A/D converted data stream is further condi-

tioned in the digital formatter, finally the 16bit or 8 bit data muxing is done in the digital video port.

The on-chip 10 bit A/D can operate up to 13.5 MSPS, since it is fully synchronous to the pixel

rate, the conversion rate always follows the frame rate. An A/D black-level-calibration circuitry

ensures the black level of Y/RGB is translated to value 16, and the peak white level is limited to

240; CrCb black level is 128, Peak/Bottom is 240/16. RGB raw data output range is 16/240, 0 &

255 reserved for sync flag. Also OV7620 support non-CCIR standard output range, that is 1/254,

0 and 255 are reserved for sync flag.

The computation in the electronic exposure control is based on the brightness of the full image.

The exposure algorithm is optimized for normal scene which assuming the subject is well-lit rel-

ative to the background. In case of a different backlight condition, there is also a AEC White/

Black ratio selection register, which can be used as AEC algorithm adjustment to get special im-

age. Along with the AEC is the on chip AGC which can boost gain up to 24dB if needed. To

achieve proper color temperature, auto or manual white balance control is also available. There

is a separate saturation, brightness contrast and sharpness adjustment for further fine tuning of

the picture quality. OV7620 provide a set of register to control White Balance ratio register which

can be used as increase/decrease image field Red/Blue component ratio. In most case, the de-

fault setting may be sufficient.

The windowing feature allows the user to size the window according to their need. The window

is sizable from 4X2 to 664x492 and can be placed anywhere inside the 664X492 boundary. Not-

ed this function does not change the frame rate or data rate, it simply change the assertion of the

HREF

to match with the horizontal and vertical region that is programmed by the user. A typical

application for this is hardware zooming, and panning. Default output window is 640x480.

The digital video port offers 16 bit 4:2:2 format complying to the 60Hz CCIR601 timing standard.

OV7620 also supports 8 bit data format in Cb Y Cr Y order by using port Y only and running at

twice the pixel rate while the port UV is inactive. Other than the 16 bit data bus, OV7620 supplies

standard video timing signals such as

VSYNC

,

HREF

,

PCLK

,

FODD, CHSYNC.

OV7620 support standard ZV Port Interface Timing. It provides VSYNC, CHSYNC, PCLK and

16 Bit data bus: Y<7:0> and UV<7:0>. PCLK rising edge clock data bus into ZV port.

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

9

Preliminary

Company Confidential

To decrease data transfer rate while high resolution image unnecessary, OV7620 provide a so-

lution, that is it can output QVGA resolution image. This mode decrease pixel rate one half. The

resolution default value is 320x240 and can be programmable. Every line only output one half

data. For Interlaced Mode, all field line output (320), for Progressive Scan Mode, only one half

line data output.

The digital video port also offer RGB Raw Data 16 Bit/8 Bit format. The output sequence is

matched to OV7620 Color Filter Pattern, that is UV channel output sequence is G R G R ..., Y

Channel output sequence is B G B G,....To 8 Bit RGB Raw data output format, just use Y channel

and disable UV channel, output sequence is B G R G ....

OV7620 support CCIR656 YCrCb 4:2:2 digital output format. The SAV(Start of Active Video) and

EAV(End of Active Video) is just at the beginning and the end of HREF window. So the position

of SAV and EAV is changing with active pixel window. Also you can get 8 bit RGB raw data with

SAV and EAV information.

OV7620 support some flexible YUV output format. One is standard YUV 4:2:2. Another is U V

sequence swap format, that means UV channel output V U V U ...(16 Bit) and V Y U Y ...(8 Bit).

The 3rd format is Y/UV sequence swap in 8 Bit output, that is Y U Y V ....

OV7620 can be use as black&white camera. At this mode, it's vertical resolution will be higher

than color mode. All data will be output from Y port and UV port will be tri-state. Data (Y/RGB)

output rate is same as 16 Bit mode.

OV7620 can be programmable to swap Y/UV or RGB output byte MSB and LSB. Y7 - Y0 default

sequence is Y7 is MSB and Y0 is LSB. When swap, Y7 is LSB and Y0 is MSB, relative middle

bits are swapped.

An important factor about digital camera is how convenient the interface is, OV7620 has made

the frame rate programmable and the A/D synchronous to the actual pixel rate. Essentially, it is

a whole image capture system in a single chip. Since the internal AEC has a range of 1:260, and

AGC have 24dB, for the most of applications, the camera can adjust itself to meet the lighting

condition without user intervention.

OV7620 support hardware/software RESET function: when RESET pin tie to high, whole chip

will be reset including all register. Hardware sleeping mode: when PWDN tie to high, chip clock

will be stop and internal circuit reset except all SCCB register. Also there is a SCCB control soft-

ware reset control register 12 bit 7, which is same as hardware RESET pin function.

OV7620 hardware reset time minimum is 1 ms.

OV7620 support hardware/software power saving mode. When the PWDN pin tie to high, whole

chip will be set to power down status without any current consumption. For software power down

control, all current set to zero except crystal circuit. In power down mode, all SCCB register value

will be kept.

Two control mechanism have been built into OV7620: A. one time read-in of pin states at power

up or RESET status, including hardware and software reset; B. SCCB interface. Two methods

are mutually exclusive, only one is used at a time, selected by pin

SBB

. Method A has limited

access to full chip features.

The power up reset method is a one time setting, the setting can not be altered later. The pins

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

10

Preliminary

Company Confidential

used in the control are shared with the digital video port data bus. At power up, the video port is

initially tri-stated, allowing the external pull-up/pull-down resistor to set the default operating con-

ditions, 2048 clocks later the video port resumes normal function. The detail of the power up pin

control method is explained in the individual pin out section.

SCCB interface provides full access to all the features. The detail is in the SCCB register set.

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

11

Preliminary

Company Confidential

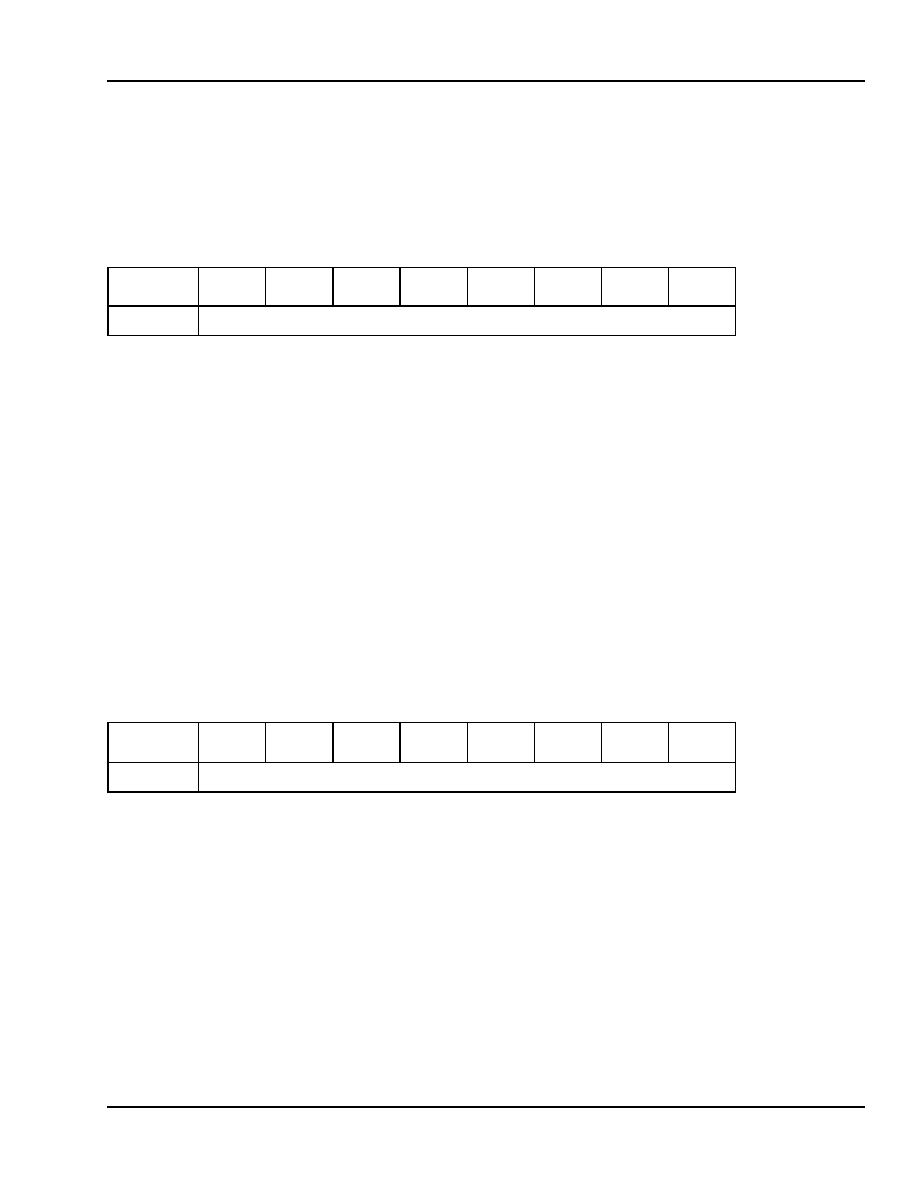

1.4 VIDEO FORMAT

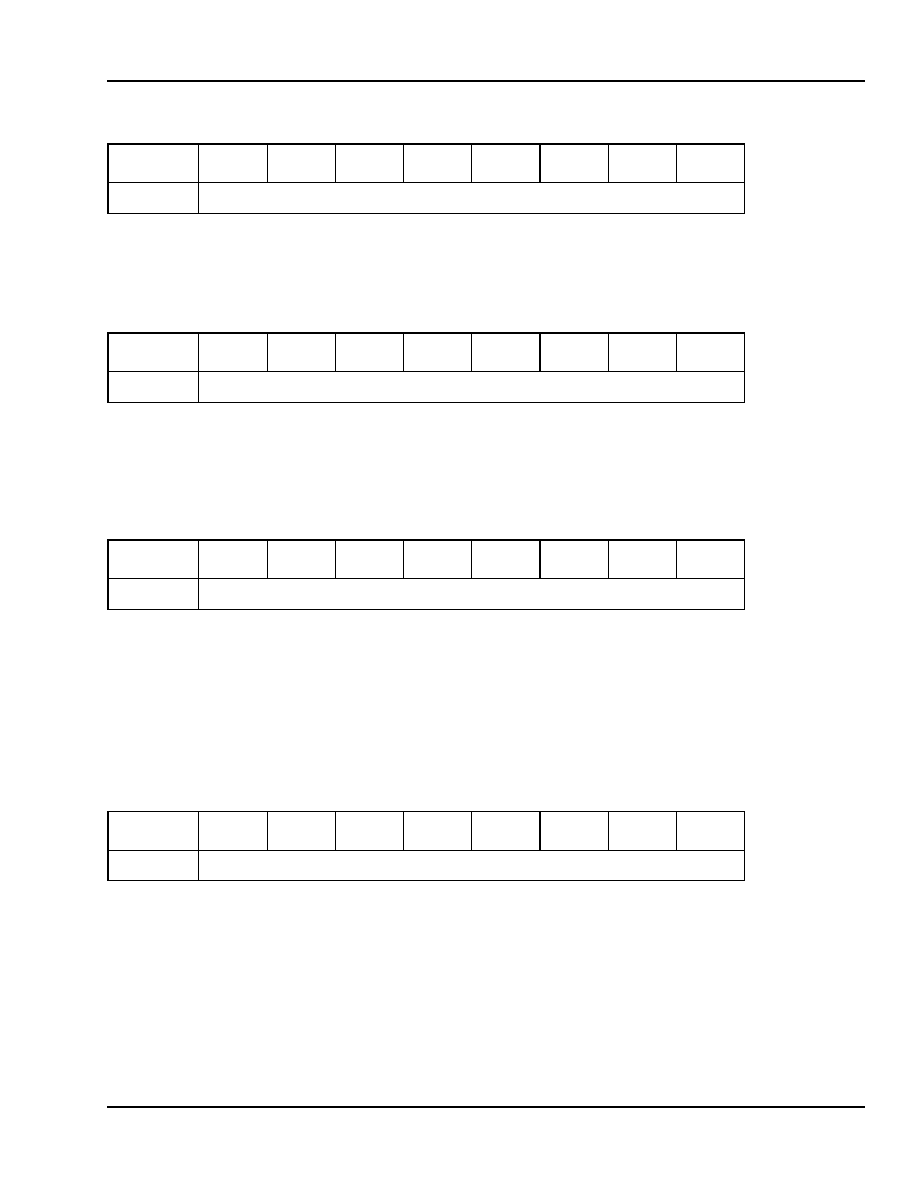

Table 1.1: 4:2:2 16 bit Format

Data Bus

Pixel Byte Sequence

Y7

Y7

Y7

Y7

Y7

Y7

Y7

Y6

Y6

Y6

Y6

Y6

Y6

Y6

Y5

Y5

Y5

Y5

Y5

Y5

Y5

Y4

Y4

Y4

Y4

Y4

Y4

Y4

Y3

Y3

Y3

Y3

Y3

Y3

Y3

Y2

Y2

Y2

Y2

Y2

Y2

Y2

Y1

Y1

Y1

Y1

Y1

Y1

Y1

Y0

Y0

Y0

Y0

Y0

Y0

Y0

UV7

U7

V7

U7

V7

U7

V7

UV6

U6

V6

U6

V6

U6

V6

UV5

U5

V5

U5

V5

U5

V5

UV4

U4

V4

U4

V4

U4

V4

UV3

U3

V3

U3

V3

U3

V3

UV2

U2

V2

U2

V2

U2

V2

UV1

U1

V1

U1

V1

U1

V1

UV0

U0

V0

U0

V0

U0

V0

Y FRAME

0

1

2

3

4

5

UV FRAME

0

2

4

Table 1.2: 4:2:2 8 bit Format

Data Bus

Pixel Byte Sequence

Y7

U7

Y7

V7

Y7

U7

Y7

V7

Y7

Y6

U6

Y6

V6

Y6

U6

Y6

V6

Y6

Y5

U5

Y5

V5

Y5

U5

Y5

V5

Y5

Y4

U4

Y4

V4

Y4

U4

Y4

V4

Y4

Y3

U3

Y3

V3

Y3

U3

Y3

V3

Y3

Y2

U2

Y2

V2

Y2

U2

Y2

V2

Y2

Y1

U1

Y1

V1

Y1

U1

Y1

V1

Y1

Y0

U0

Y0

V0

Y0

U0

Y0

V0

Y0

Y FRAME

0

1

2

3

UV FRAME

0 1

2 3

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

12

Preliminary

Company Confidential

FIG 1.2 Pixel Data Bus (YUV Output)

Note: Tclk is pixel clock period. When OV7620 system clock is 27MHz, Tclk=74ns for 16 Bit out-

put; Tclk=37ns for 8 Bit output. Tsu is HREF set-up time, maximum is 15 ns; Thd is HREF hold

time, maximum is 15 ns.

Y<7:0>

PCLK

HREF

UV<7:0>

10

10

Y

Y

80

80

U

V

repeat for all data bytes

Pixel Data 16 bit Timing

Y<7:0>

PCLK

HREF

repeat for all data bytes

Pixel Data 8 bit Timing

U

Y

V

Y

80

10

10

80

Use PCLK rising edge latch data bus

Use PCLK rising edge latch data bus

Tsu

Thd

Thd

Tclk

Tclk

10

Tsu

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

13

Preliminary

Company Confidential

1.5 RGB Raw Data Format

RGB Raw data output from Y and UV port.

UV port output data sequence: G R G R G R ... or B R B R ...(refer to register 28 bit 2)

Y port output data sequence: B G B G B G ... or G G G G ...(refer to register 28 bit 2)

Array Color Filter Patter is Bayer-Pattern

1.5.1 Interlaced Mode 16 Bit Format (HREF total 242)

1.5.1.1 Default mode: In ODD FIELD, 1st HREF output UV channel is 2nd line: G

21

R

22

G

23

R

24

... and Y channel

is Row 1: B

11

G

12

B

13

G

14

... . 2nd HREF output UV channel output 4th line: G

41

R

42

G

43

R

44

... and Y port output

3rd line: B

31

G

32

B

33

G

34

... , so on. Data bus should be latched by PCLK rising edge and related to the exact phys-

ical position In Even FIELD, 1st HREF Y channel output B

31

G

32

B

33

G

34

... and UV channel output G

21

R

22

G

23

R

24

...2nd HREF Y channel output B

51

G

52

B

53

G

54

... and UV output G

41

R

42

G

43

R

44

....

1.5.1.2 YG mode: In ODD FIELD, 1st HREF Y channel output G

21

G

12

G

23

G

14

... and UV channel is B

11

R

22

B

13

R

24

.... 2nd HREF Y channel output G

41

G

32

G

43

G

34

... and UV channel output B

31

R

42

B

33

R

44

.... In EVEN

FIELD, 1st HREF Y channel output G

21

G

32

G

23

G

34

... and UV channel output B

31

R

22

B

33

R

24

... 2nd HREF

channel output G

41

G

52

G

43

G

54

... and UV channel output B

51

R

42

B

53

R

44

...

Table 1.3:

R\C

1

2

3

4

.

641

642

643

644

1

B

11

G

12

B

13

G

14

B

G

B

G

2

G

21

R

22

G

23

R

24

G

R

G

R

3

B

31

G

32

B

33

G

34

B

G

B

G

4

G

41

R

42

G

43

R

44

G

R

G

R

5

B

51

G

52

B

53

G

54

B

G

B

G

.

481

B

G

B

G

B

G

B

G

482

G

R

G

R

G

R

G

R

483

B

G

B

G

B

G

B

G

484

G

R

G

R

G

R

G

R

485

B

G

B

G

B

G

B

G

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

14

Preliminary

Company Confidential

1.5.2 Progressive Scan Mode 16 Bit Format (HREF total 484)

1.5.2.3 Default mode: 1st HREF UV channel output unstable data, Y output B

11

G

12

B

13

G

14

.... 2nd HREF UV

channel output G

21

R

22

G

23

R

24

..., Y output B

11

G

12

B

13

G

14

... 3rd HREF UV channel output G

21

R

22

G

23

R

24

...,

Y output B

31

G

23

B

33

G

34

.... Every line data output twice.

1.5.2.4 YG mode: 1st HREF Y and UV output unstable data. 2nd HREF Y channel output G

21

G

12

G

23

G

14

..., UV

output B

11

R

22

B

13

R

24

... 3rd HREF Y is G

21

G

32

G

23

G

34

..., UV channel is B

31

R

22

B

33

R

24

... Every line data out-

put twice.

1.5.2.5 One line mode: 1st HREF Y channel output B

11

G

12

B

13

G

14

..., 2nd HREF Y channel output G

21

R

22

G

23

R

24

..., so on. UV channel tri-state.

1.5.3 Interlaced Mode 8 Bit (242 HREF)

1.5.3.6 ODD FIELD: 1st HREF Y channel output B11 G21 R22 G12 ... 2nd HREF Y channel output B31 G41 R42

G32..., so on. PCLK timing is double and use PCLK rising edge latch data bus. UV channel tri-state.

1.5.3.7 EVEN FIELD: 1st HREF Y channel output B31 G21 R22 G32 ... 2nd HREF Y channel output B51 G41 R42

G52 ..., so on. PCLK timing is double and data bus should be latched by its rising edge. UV channel tri-state.

1.5.4 Progressive Scan Mode 8 Bit (484 HREF)

1.5.4.8 1st HREF Y channel output unstable data. 2nd HREF Y channel output B11 G21 R22 G12 ... 2nd HREF Y

channel output B31 G21 R22 G32 ..., so on. PCLK timing is double and PCLK rising edge latch data bus. UV chan-

nel tri-state. Every line data output twice.

RGB raw data timing chart is as follows:

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

15

Preliminary

Company Confidential

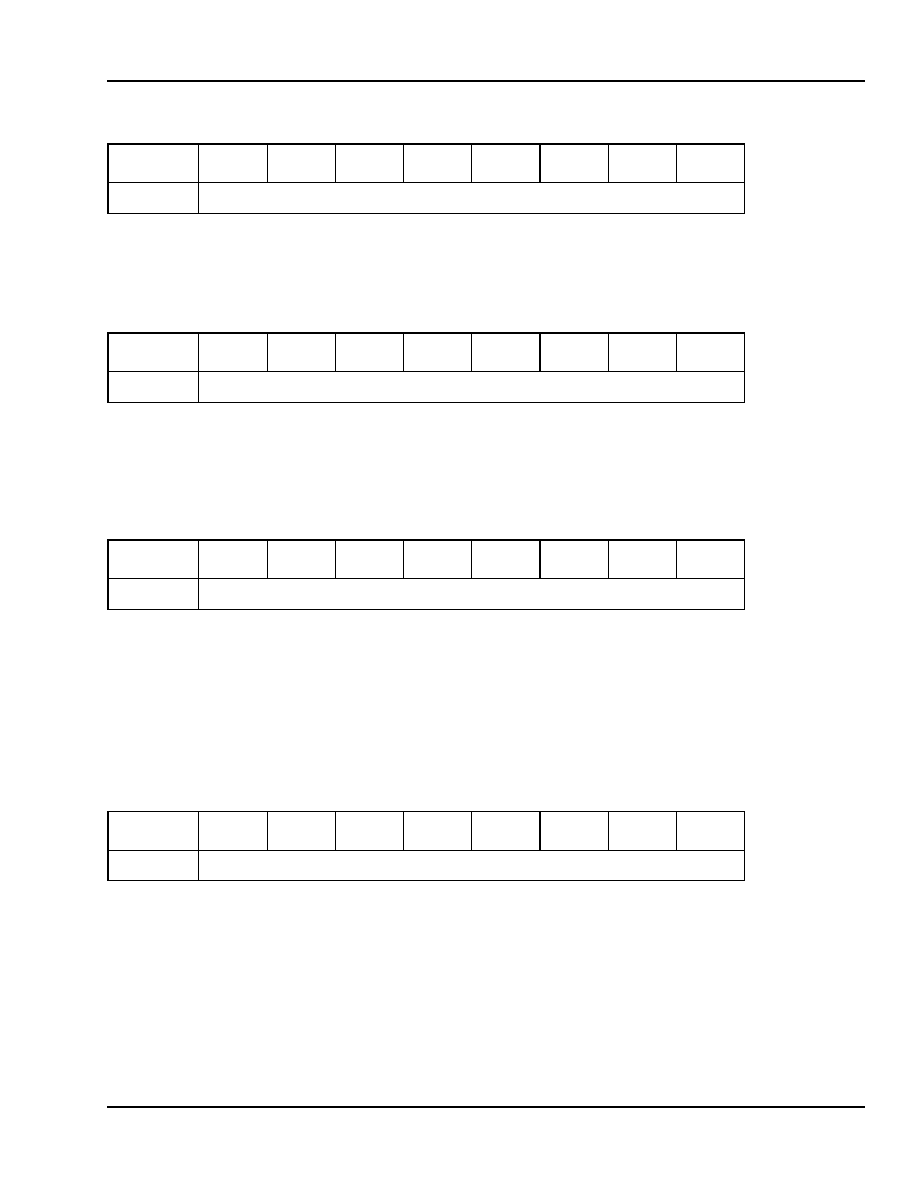

FIG 1.3 Pixel Data Bus (RGB Output)

Note: Tclk is pixel clock period. When OV7620 system clock is 27MHz, Tclk=74ns for 16 Bit out-

put; Tclk=37ns for 8 Bit output. Tsu is HREF set-up time, maximum is 15 ns; Thd is HREF hold

time, maximum is 15 ns.

UV<7:0>

PCLK

HREF

Y<7:0>

10

10

G

R

10

10

B

G

repeat for all data bytes

Pixel Data 16 bit Timing

Y<7:0>

PCLK

HREF

10

10

B

B

repeat for all data bytes

Pixel Data 8 bit Timing

10

G

G

10

PCLK rising edge latch data bus

PCLK rising edge latch data bus

Tclk

Tclk

Thd

Thd

Tsu

Tsu

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

16

Preliminary

Company Confidential

1.6 ZV Port Interlace Timing

The ZV Port is a single-source uni-directional video bus between a PC Card socket and a VGA

controller. The ZV Port complies with CCIR601 timing to allow NTSC decoders to deliver real-

time digital video straight into the VGA frame buffer from a PC Card. OV7620 support ZV Port

Timing, which output signal can be output to a PC Card directly, then to VGA controller. The tim-

ing is as below:

FIG 1.4 ZV Port Timing

Notes: ZV Port format output signal include:

VSYNC: Vertical sync pulse.

HREF: Horizontal valid data output window.

PCLK: Pixel clock used to clock valid data and CHSYNC into ZV Port. Default frequency is 13.5MHz when

use 27MHz as system clock. Rising edge of PCLK is used to clock the 16 Bit data.

Y<7:0>: 8 Bit luminance data bus..

UV<7:0>: 8 Bit chrominance data bus.

All Timing Parameters is list in following table.`

VSYNC

PCLK

Y<7:0>

UV<7:0>

/

HREF

639 640

t8

t8

Even Field 1(FODD=0)

Odd Field(FODD=1)

t6

t7

t1

t2

t3

t4

Horizontal Timing

VSYNC

Y<7:0>/

UV<7:0>

Valid Data

1 Line

Tvs

Tve

t5

Tline

1

2

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

17

Preliminary

Company Confidential

Note: In Interlaced Mode, there are Even/Odd field different (t8). When In Progressive Scan Mode, only

frame timing same as Even field(t8).

After VSYNC falling edge, OV7620 will output black reference level, the line number is Tvs,

which is the line number between the 1st HREF rising edge after VSYNC falling edge and 1st

valid data CHSYNC rising edge. Then valid data, then black reference, line number is Tve, which

is the line number between last valid data CHSYNC rising edge and 1st CHSYNC rising edge

after VSYNC rising edge. The black reference output line number is dependent on vertical win-

dow setting.

When in default setting, Tvs = 14*Tline, which is changed with register register 19<7:0>. If in

Interlaced Mode, register 19<7:0> change 1 step, Tvs increase 1 line. If in Progressive Scan

Mode, register 19<7:0> step equal to 2 line.

When in default setting, Tve = 4*Tline for Odd Field, Tve = 3*Tline for Even Field, which is

changed with register register 1A<7:0>. If in Interlaced Mode, register 1A<7:0> change 1 step,

Tve increase 1 line. If in Progressive Scan Mode, register 1A<7:0> step equal to 2 line.

In Progressive Scan Mode, Tve = 3*Tline and Tvs = 35*Tline.

Table 1.4: ZV Port AC Parameter

Symbol

Parameter

Min.

Max.

t1

PCLK fall timing

4 ns

8 ns

t2

PCLK low time

30 ns

t3

PCLK rise time

4 ns

8 ns

t4

PCLK high time

30 ns

t5

PCLK period

74 ns

t6

Y/UV/HREF setup time

10 ns

t7

Y/UV/HREF hold time

20 ns

t8

VSYNC setup/hold time to HREF

1 us

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

18

Preliminary

Company Confidential

1.7 Interface for External RAM Controller and Micro-controller

OV7620 can be programmed to output single frame data to external RAM. The structure block

diagram is as follows:

The timing diagram is as follows:

OV7620

FPGA

u-CPU

DRAM / SRAM

Data

Add

ACK

SCCB and Initial

SRAM

DATA

HREF

VS

AGCEN

Tri-State

Tri-State

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

19

Preliminary

Company Confidential

SRAM is internal control bit which is high means the OV7620 enter external RAM status. This is

programmed by SCCB (register 27) or power-on read-in. When SRAM=1, OV7620 all data bus

will be tri-stated and ready to send the data. Micro-controller will send a initial signal to FPGA to

reset all RAM Address block, after that, there are two method to get one frame data frame

OV7620:

1. Micro-controller send a initial pulse to OV7620 AGCEN input pin

2. Micro-controller send a SCCB command to program OV7620 send Single frame data

The OV7620 output signal VS is the ACK signal from sensor, when VS is high means OV7620

is in ready status, when VS is low, means OV7620 will send one frame data.

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

20

Preliminary

Company Confidential

1.8 Digital Output Format Table

Note: "Y" in the table means this combination is supported by OV7620.

1. RGB CCIR656 format means 4-byte SAV and EAV is inserted at the beginning and ending of

HREF, which are used to grab Vsync and Hsync information. So only use 8-bit data bus line and

don't need VSYNC and CHSYNC signal line.

2. Y/UV swap is valid only in 8 bit output. Y channel output sequence is Y U Y V ... rather U Y V

Y ....

3. To YUV format, U/V swap means UV channel output sequence swap. V U V U ... rather U V

U V ... for 16 bit; V Y U Y ... rather U Y V Y ... for 8-bit.

4. To RGB format, U/V swap means neighbor row B R output sequence swap. So refer to preview

RGB raw data output format, different format change accordingly.

5. MSB/LSB swap means: Default Y/UV channel output port relationship is:

Table 1.5: Digital Output Format Type

Interlaced

Progressive Scan

Resolution

640x480

320x240

640x480

320x240

YUV 4:2:2

16Bit

Y

Y

Y

Y

8Bit

Y

Y

Y

Y

CCIR656

Y

Y

Y

Y

RGB

16Bit

Y

Y

Y

Y

8Bit

Y

Y

Y

Y

CCIR656

1

Y

Y

Y

Y

Y/UV swap

2

16Bit

-

-

-

-

8Bit

Y

Y

Y

Y

U/V swap

YUV

3

Y

Y

Y

Y

RGB

4

Y

Y

Y

Y

YG

16Bit

Y

Y

Y

Y

8Bit

-

-

-

-

One Line

16Bit

-

-

Y

-

8Bit

-

-

-

-

MSB/LSB swap

5

Y

Y

Y

Y

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

21

Preliminary

Company Confidential

If swap, sequence is change to:

6. RGB mode selected by COMA3=1; COMA3=0 select YUV mode.

7. 8 Bit mode selected by COMB5=1.

8. CCIR656 mode selected by COMB4=1.

9.Y/UV swap selected by COMA4=1.

10. YG mode selected by COMH2=1.

11. One line mode selected by COMH7=1.

12. U/V swap mode selected by COMD0=1.

13. MSB/LSB swap mode selected by COMF2=1.

Table 1.6: Default Output Sequence

MSB

LSB

Output Port

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

Internal Output data

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

Table 1.7: Swap MSB/LSB output sequence

MSB

LSB

Output Port

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

Internal Output data

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

22

Preliminary

Company Confidential

1.9 QVGA Resolution Digital Output Format

1.9.5 Interlaced Mode:

Y channel output Y2 Y3 Y6 Y7 Y10 Y11 ... UV channel output U2 V3 U6 V7 U10 V11 ... Every line output

data number is half(320 pixels) and all line data(240 line) in one field will be output.

1.9.6 Progressive Scan Mode:

Y channel output Y2 Y3 Y6 Y7 Y10 Y11 ... UV channel output U2 V3 U6 V7 U10 V11 ... Every line output

data number is half(320 pixels) and only one half line data (every other line, total 240 line) in

one frame will be output.

1.9.7 QVGA 60 Frame/s Mode:

In Interlace Mode, QVGA mode output frame rate is 30 Frame/s and 60 Field/s. When in 60 Frame/s

mode, only Odd field data output and frame rate is 60 Frame/s.

1.9.8 Interlaced Mode (Default RGB two line output mode):

UV channel output G0 R1 G4 R5 G8 R9 ... Y channel output B0 G1 B4 G5 B8 G9 ...Every line output half

data(320 pixels) and all line data(240 line) in one field will be output.

1.9.9 Interlaced Mode (YG two line output mode):

Y channel output G0 G1 G4 G5 G8 G9 ... UV channel output B0 R1 B4 R5 B8 R9 ... Every line output half

data(320 pixels) and all line data(240 line) in one field will be output.

1.9.10 Progressive Scan Mode (Default RGB two line output mode):

UV channel output G0 R1 G4 R5 G8 R9 ... Y channel output B0 G1 B4 G5 B8 G9 ...Every line output half

data(320 pixels) and all line(480 line) data in one frame will be output.

1.9.11 Progressive Scan Mode (YG two line output mode):

UV channel output G0 R1 G4 R5 G8 R9 ... Y channel output B0 G1 B4 G5 B8 G9 ...Every line output half

data(320 pixels) and all line(480 line) data in one frame will be output.

Table 1.8: QVGA Digital Output Format(YUV, beginning of line)

Pixel #

1

2

3

4

5

6

7

8

Y

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

UV

U0,V0

U1,V1

U2,V2

U3,V3

U4,V4

U5,V5

U6,V6

U7,V7

Table 1.9: QVGA Digital Output Format (RGB Raw data, beginning of line)

Pixel #

1

2

3

4

5

6

7

8

Line 1

B0

G1

B2

G3

B4

G5

B6

G7

Line 2

G0

R1

G2

R3

G4

R5

G6

R7

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

23

Preliminary

Company Confidential

1.10 Slave Mode Operation

OV7620 can be programmable to be slave device. Default OV7620 is a master device, it provide

Hsync, Vsync output. If used as slave device, (register 29 bit 6=1), external master device must

provide:

System clock CLK to XCLK1 pin;

Horizontal sync Hsync to CHSYNC pin, positive acted.

Vertical frame sync Vsync to VSYNC pin, positive acted.

When in slave mode, OV7620 tri-state CHSYNC and VSYNC output pin and use as input pin. To

synchronize the chip, OV7620 use external system clock CLK synchronize external horizontal

sync Hsync, then use synchronized horizontal sync to synchronize external vertical frame sync

Vsync. But to match internal counter, these three must keep exact relation as below:

Hsync period is 2*858 * CLK

Vsync period is 525* 2*858 * CLK

FIG 1.5 Slave Mode External Sync Timing

OV7620 will be stable after 1 frame. (2nd Vsync).

1.11 Frame Exposure Mode

OV7620 support frame exposure mode when in Progressive Scan Mode. When the FREX pin is

used as an external master device sets the exposure time. When FREX =1, the whole array is

precharged. The exposure time is then determined by the external master device which controls

FREX. When FREX=0, the OV7620 begins to output data line by line. While data is output, the

OV7620 must be blocked from light by using a mechanical shutter, so that the whole array is ex-

posed at the same time and has the same exposure period. In default line exposure mode, the

array precharge and read mode is first charge 1st line, after one line read out, precharge 2nd

line, so on. the width of FREX=1 must large the a fixed timing to make sure whole array has been

precharged.

Frame exposure mode timing is as below:

CLK

Hsync

Vsync

1 frame = 525*2*858*Tclk

1 line=2*858*Tclk

Tclk

Tvs

Note: (1) Ths > 6*Tclk (2) Ths < Tvs < 2*858*Tclk

Ths

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

24

Preliminary

Company Confidential

FIG 1.6 Frame Exposure Timing

Note: Tpr = 492 * 4 * Pclk, Pclk is internal pixel clock. For default 27MHz, Tclk=74 ns. If CLK<5:0> set to

divided number, Tclk will increase accordingly.

Tex is array exposure time which is decided by external master device.

Tin is undetermined due to the use of HSYNC rising edge to synchronize FREX, Tin < Ths

When FREX=0, there are 8 lines of data output before valid data output. Thd = 4 * Ths. Valid data is output

when HREF=1.

Tset = Tin + Tpr + Tex. Tset > Tpr + Tin. Because Tin is uncertain, so exposure time setting resolution is

Ths (one line).

FREX

DATA

HSYNC

OUTPUT

VSYNC

ARRAY

PRECHARGE

Black Data

Invalid Data

Valid Data

1 Frame (484 line)

Prechage begin at rising edge of HSYNC

Array Exposure Period Tex

Array Precharge

period Tpr

Tset

Next Frame

Mechanical shutter closed

Head of Valid data

Tin

Ths

Thd

HREF

(8 line)

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

25

Preliminary

Company Confidential

1.12 SCCB BUS

SCCB access is enabled only if pin

SBB

=0. OV7620 is a slave device that supports 400kbit/s 7bit

address data transfer protocol. Within each byte, MSB is always transferred first, read/write con-

trol bit is the LSB of the first byte

The protocol requires

SIO-0

must be stable during the HIGH period of the

SIO-1

. Each data bit can

only change state when is

SIO-1

LOW.

OV7620 reserves

CS(2:0)

for the slave ID, which makes eight slave camera combinations.

OV7620 SCCB supports multi-byte write and multi-byte read. In a write cycle, the master must

supply the subaddress, however, the master does not supply the subaddress in the read cycle,

therefore, OV7620 takes the read subaddress from the previous write cycle. In multi-byte write

or multi-byte read cycles, the subaddress is auto increment after the first data byte so that con-

tinuous locations can be accessed in one bus cycle. Since a multi-byte cycle overwrites its orig-

inal subaddress, if a read cycle follows immediately to a multi-byte cycle, it is necessary to insert

a single byte write cycle that provides a new subaddress.

If OV7620 support 400 kBit/s fast SCCB mode, system clock (CLK) must be at least 10 Mhz.

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

26

Preliminary

Company Confidential

1.13 SCCB REGISTER SETS

OV7620 can be configured, by setting pin CS<2:0> high or low at reset/power up, to one of eight

slave IDs as listed below, the ID can not be altered once the chip is out of reset or power up state.

OV7620 support two option: single chip and multiple chip decided by PIN MID. If MID set to

LOW (Default value), chip slave ID is 42(for write) and 43(for read). If MID set to HIGH, OV7620

can support 8 slave ID selection. Default MID is LOW by internal setting.

In write cycle, the second byte in SCCB bus is the subaddress for selecting the individual on chip

registers, the third byte is the data associated with this register. Writing to unimplemented sub-

address and reserved subaddress is ignored.

In read cycle, the second byte is the data associated with the previous stored subaddress. read-

ing of unimplemented subaddress returns unknown.

Registers [00] ~ [02] contains image effect parameters that also can be modified by internal con-

trols in auto adjust mode. This provides a simple way to read out those parameters computed by

chip internal controls. To do this, first set the chip in auto adjust mode (Register 13 bit 0=1, reg-

ister 12 bit 2 = 1, register 12 bit 5=1), wait for the image is stable, the register [00],[01] and [02]

will be updated by internal control circuit. Then returns it to manual adjust mode(register 13 bit

0=0), all the registers retain the last adjusted values and can be read or overwritten by external

host. When the chip is operated in auto adjust mode(register 13 bit 0=1), register [00] ~ [02] will

be update by internal algorithm and if write data to them, there will be no effect on chip parame-

ters. The register data can be read out.

The detailed definitions of each register are described below.

AGC<5:0> - gain setting for the entire image channel.

The formula is:

Gain = (AGC<3:0>/16+1)*(AGC<4>+1)*(AGC<5>+1); range (1x ~ 7.75x), AGC<5> and

AGC<4> control SA2.

Table 1.10: Slave ID

CS<2:0>

000

001

010

011

100

101

110

111

WRITE ID (hex)

42

46

4a

4e

52

56

5a

5e

READ ID (hex)

43

47

4b

4f

53

57

5b

5f

Register 00 - rw: AGC gain control

Bits

Null

AGC6

AGC5

AGC4

AGC3

AGC2

AGC1

AGC0

Default

-

-

0

0

0

0

0

0

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

27

Preliminary

Company Confidential

Register 01 - rw: Blue gain control

BLU<6:0> - white balance value for the blue channel.

The formula is:

Blue_gain=1+(BLU<7:0> - [80])/[100]; range (0.5x ~ 1.5x).

BLU<7> - Sign bit. If "1", Blue gain increase; "0" gain decrease.

Register 02 - rw: Red gain control

RED<6:0> - white balance value for the red channel.

The formula is:

Red_gain=1+(RED<7:0> - [80])/[100]; range (0.5x ~ 1.5x).

RED<7> - Sign bit. If "1", Red channel gain increase; "0" gain decrease.

SAT<7:0> - saturation adjustment for the UV channel based on the default setting;

range (-4dB ~ +6dB). If SAT<7:0> > [80], increase; if SAT<7:0> < [80], decrease.

Register 04 & 05 - w: Reserved Register

This register is reserved for internal test use. Write data to this register will be no function.

BRT<7:0> - brightness adjustment for the Y/RGB channel based on the default setting;

range (-200mv ~ +200mv). If BRT<7:0> > [80], brightness increase; If BRT<7:0> < [80], bright-

ness decrease. This register is auto/manual controllable. If register 2D bit 4=1, this register is

controlled by chip automatically, if write value to this register, this value will be updated by

internal circuit. Only when register 2D bit 4=0, this register can be set to any value

Bits

BLU7

BLU6

BLU5

BLU4

BLU3

BLU2

BLU1

BLU0

Default

1

0

0

0

0

0

0

0

Bits

RED7

RED6

RED5

RED4

RED3

RED2

RED1

RED0

Default

1

0

0

0

0

0

0

0

Register 03 - rw: Saturation control

Bits

SAT7

SAT6

SAT5

SAT4

SAT3

SAT2

SAT1

SAT0

Default

1

0

-0

0

0

0

0

0

Register 06 - rw: Brightness control

Bits

BRT7

BRT6

BRT5

BRT4

BRT3

BRT2

BRT1

BRT0

Default

1

0

0

0

0

0

0

0

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

28

Preliminary

Company Confidential

SHP<7:4> - Sharpness Threshold.

SHP<3:0> - Sharpness Magnitude.

Register [08] ~ [0B] - w: Reserved.

These four registers are reserved for internal use. Write data to these registers will not function.

Register 0C - rw: White Balance background control -- Blue channel

Changes AWB Hue Control

ABLU<4:0> - White Balance background blue color component ratio adjustment. Adjust resolution is

0.625% and total range is (+20% - -20%) This register is used to offset image background blue

component ratio.

ABLU<5> - Sign bit. If "1", decrease background blue component ratio; "0" increase blue component ratio.

Register 0D - rw: White Balance background control -- Red channel

Changes AWB Hue Control

ARED<4:0> - White Balance background red color component ratio adjustment. Adjust resolution is 1.5%

and total range is (+20% - -20%) This register is used to offset image background red compo-

nent ratio.

ARED<5> - Sign bit. If "1", decrease background red component ratio; "0" increase red component ratio.

Register 0E ~ 0F- rw: Reserved

These two registers are reserved for internal use. Write data to these registers will not function.

Register 07 - rw: Angalog Sharpness control

Bits

SHP7

SHP6

SHP5

SHP4

SHP3

SHP2

SHP1

SHP0

Default

1

1

0

0

0

0

1

1

Bits

Null

Null

ABLU5

ABLU4

ABLU3

ABLU2

ABLU1

ABLU0

Default

-

-

1

0

0

0

0

0

Bits

Null

Null

ARED5

ARED4

ARED3

ARED2

ARED1

ARED0

Default

-

-

1

0

0

0

0

0

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

29

Preliminary

Company Confidential

Register 10 - rw: Auto-Exposure-Control Register

AEC<7:0> - exposure time setting; the formula is

Interlaced: T

EXPOSURE

= T

LINE

x AEC(7:0);

Progressive: T

EXPOSURE

= T

LINE

x AEC(7:0)x2;

where T

LINE

= Frame Time / 525

if use 27MHz, T

LINE

= 63.5 uS

Range is: [00] - [7F] for Interlaced; [00] - [FF] for Progressive Scan.

* This register setting is only effective when operated in manual adjust mode (register 13 bit 0=0). Never-

theless, this register is always accessible through the SCCB bus. If register 13 bit 0=1, this

register will be updated by internal circuit according AEC algorithm, and if write special value

to this register will be useless. The register value can be read out at any time and latest AEC

value will be return. If register 13 bit 0=0, or register 29 bit 7=1, the register will hold last value

unchanged (either input from SCCB or AEC algorithm result).

* It generally takes no more than two fields for the image to reach the intended exposure after changing the

setting.

Register 11 - rw: Clock rate control

CLK<5:0> - system clock prescaler; this register defines the chip pixel clock rate, clock rate is defined by

following fulmar:

(16 Bit mode) PCLK = (CLK_input / (( CLK<5:0> + 1) * 2))

(8 Bit mode) PCLK = (CLK_input / ( CLK<5:0> + 1))

SYN<7:6> - Three sync output polarity selection:

SYN7 = 0, SYN6 = 0: HSYNC negative, CHSYNC negative, VSYNC positive edge;

SYN7 = 0, SYN6 = 1:.HSYNC negative, CHSYNC negative, VSYNC negative;

SYN7 = 1, SYN6 = 0: HSYNC positive, CHSYNC negative, VSYNC positive.

SYN7 = 1, SYN6 = 1: HSYNC negative, CHSYNC positive, VSYNC positive.

* The effect of the change is immediate, however, it generally takes about two fields for the image to reach

the stable state

Bits

AEC7

AEC6

AEC5

AEC4

AEC3

AEC2

AEC1

AEC0

Interlace

0

1

1

1

1

1

1

1

Progres-

sive Scan

1

1

1

1

1

1

1

1

Bits

SYN7

SYN6

CLK5

CLK4

CLK3

CLK2

CLK1

CLK0

Default

0

0

0

0

0

0

0

0

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

30

Preliminary

Company Confidential

.

COMA7 - "1" initiates the chip soft reset, the reset takes place after the acknowledge bit is issued, the

effect is the same as power up the chip, the chip is initialized to a default state, all registers

including SCCB's contents are set to default, this bit is self cleared after the reset.

COMA6 - "1" selects mirror image

COMA5 - "1" enables AGC. "0" - stop AGC and set register [00] to default value. Only effective in auto

adjust mode.

COMA4 - "1" select 8 Bit Digital output format is Y U Y V Y U Y V ...

COMA3 - "1" selects raw data signal as video data output, "0" selects YCrCb as video data output. The

selection applies to both analog video and digital video.

COMA2 - "1" enable auto white balance, "0" AWB stop and AWB register [01] and [02] value is held at last

updated value. Can used as one-shot AWB mode. Valid only in auto mode.

COMA1 - "1" selects Color Bar Test pattern output.

COMA0 - "1" select precise A/D Black Level Compensation (BLC) line method. "0" use standard black level

compensation to do A/D BLC field method which is more stable but less precise.

COMB7 - Reserved.

COMB6 - Reserved.

COMB5 - "1" selects 8 bit data format, Y/CrCb and RGB video data is multiplexed to the eight bit Y bus, tri-

state UV bus; "0" selects 16 bit format, data go to both Y<7:0> bus and UV<7:0> bus.

COMB4 - "0" enables digital output in CCIR601 format. "1" enables CCIR656 format.

COMB3 - "0" selects horizontal sync for output to pin CHSYNC, "1" selects composite sync for output.

COMB2 - "1" tri-states bus Y<7:0> and UV<7:0>, "0" enables both buses.

COMB1 - "1" initiates the single frame transfer, for this function to work, field drop mode (FD<1:0> in regis-

ter [16]) must set to "OFF". See figure below. After this bit is set, for Interlaced mode, HREF is

only asserted for consecutive two fields beginning at Odd field. This bit is cleared automati-

cally at the end of this frame. For Progressive Scan mode, HREF is only asserted for one

frame. Clearing this bit in the middle of active frame has no effect to the assertion of current

HREF.

COMB0 - "1" enables auto adjust mode, in this mode, internal exposure circuitry overwrites those parame-

ters in registers [00]~[02], the chip adjusts the image based on a preset algorithm. "0" manual

adjust mode.

Register 12 - rw: Common control A

Bits

COMA7

COMA6

COMA5

COMA4

COMA3

COMA2

COMA1

COMA0

Default

0

0

1

0

0

1

0

0

Register 13 - rw: Common control B

Bits

COMB7

COMB6

COMB5

COMB4

COMB3

COMB2

COMB1

COMB0

Default

-

-

0

0

0

0

0

1

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

31

Preliminary

Company Confidential

.

VSYNC

COMB1

HREF

SCCB BIT SET

SCCB BIT SET

END OF FRAME

SCCB BIT CLEAR

BIT CLEAR

FODD

FD<1:0>

SCCB BIT CLEAR

1 FRAME

FIG 1.7 Single Frame Transfer Example (Interlaced Mode)

VSYNC

COMB1

HREF

SCCB BIT SET

SCCB BIT SET

END OF FRAME

SCCB BIT CLEAR

BIT CLEAR

FD<1:0>

SCCB BIT CLEAR

1 FRAME

FIG 1.8 Single Frame Transfer Example (Progressive Scan Mode)

SCCB BIT CLEAR

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

32

Preliminary

Company Confidential

Register 14- rw: Common control C

COMC7 - AWB activation threshold selection: 1- high; 0-low.

COMC6 - Reserved.

COMC5 - QVGA digital output format selection. 1 - 320x240; 0 - 640x480.

COMC4 - Field/Frame vertical sync output in VSYNC port selection: 1 - frame sync, only inserted in ODD

field vertical sync; 0 - field vertical sync, effect in Interlaced mode

COMC3 - HREF polarity selection: 0 - HREF positive effective, 1 - HREF negative.

COMC2 - RGB gamma selection: 1 - Gamma on, value defined by register [62] value; 0 - gamma is 1 (lin-

ear).

COMC1 - Reserved.

COMC0 - Reserved.

COMD7 - Reserved.

COMD6 - PCLK polarity selection. "0" OV7620 output data at PCLK falling edge and data bus will be stable

at PCLK rising edge; "1" rising edge output data and stable at PCLK falling edge. When

OV7620 work as CCIR656 format, COMB4=1, this bit is disable and should use PCLK rising

edge latch data bus.

COMD<5:1> - Reserved.

COMD0 - U V digital output sequence exchange control. 0 - V U V U ... for 16Bit, V Y U Y ... for 8 Bit; 1- U

V U V ... for 16Bit and U Y V Y ... for 8 Bit.

FD<7:2>- Frame drop selection, it operates in ODD and EVEN mode as defined by FD<1:0>, it is ignored

in OFF & FRAME mode. Its purpose is to divide the video signal into programmed number of

time slots in unit of field/frame, and to allow HREF to be active only one field/frame during the

period. This function does not affect the video data or pixel rate.

000000 - 000001: disable digital data output, only output black reference level.

000010 - 111111: Output 1 of (2 ~ 63) frame. If set register 33 bit 1= 1, that means

only drop 1 frame from (2 ~ 63) frame.

Bits

COMC7

COMC6

COMC5

COMC4

COMC3

COMC2

COMC1

COMC0

Default

0

-

0

0

0

1

-

-

Register 15- rw: Common control D

Bits

COMD7

COMD6

COMD5

COMD4

COMD3

COMD2

COMD1

COMD0

Default

-

0

-

-

-

-

-

1

Register 16 - rw: Frame Drop

Bits

FD7

FD6

FD5

FD4

FD3

FD2

FD1

FD0

Default

0

0

0

0

0

0

1

1

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

33

Preliminary

Company Confidential

Interlaced:

FD<1:0>- field mode selection. Each frame consists of two fields: Odd & Even, these bits defines the

assertion of HREF in relation to the two fields.

00 - OFF mode; HREF is not asserted in both fields, one exception is the single frame transfer

operation (see the description for the register [13])

01 - ODD mode; HREF is asserted in odd field only.

10 - EVEN mode; HREF is asserted in even field only.

11 - FRAME mode; HREF is asserted in both odd field and even field. FD<7:2> useless (default).

Progressive Scan:

FD<1:0> - frame mode selection.

00 - OFF mode; HREF is not asserted in both fields, one exception is the single frame transfer

operation (see the description for the register [13])

01,10 - SLOT mode; HREF is asserted in frame according FD<7:2>.

11 - FRAME mode; HREF is asserted in every frame. FD<7:2> useless

FODD

HREF

slot 1

slot 2

slot 3

slot 4

slot 1

slot 2

slot 3

slot 4

HREF

slot 2

slot 1

slot 2

slot 1

slot 2

slot 1

slot 2

slot 1

EVEN MODE

FD<7:2>=000010

E

V

E

N

M

O

D

E

O

D

D

M

O

D

E

ODD MODE

FD<7:2>=000001

FIG 1.9 Field Division Examples (Interlaced Mode)

FD<1:0>=10

FD<1:0>=01

1 field

HREF

slot 2

slot 1

slot 2

slot 1

slot 2

slot 1

slot 2

slot 1

S

L

O

T

M

O

D

E

FD<7:2>=000001

FIG 1.10 Frame Division Examples (Progressive Scan Mode)

FD<1:0>=01

VSYNC

1 frame

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

34

Preliminary

Company Confidential

Register 17 - rw: Horizontal Window start

HS<7:0> - selects the starting point of HREF window, each LSB represents four pixels for Inter-

laced/Progressive full resolution mode, two pixels for QVGA resolution mode, this value is set

based on an internal column counter, the default value corresponds to 640 horizontal window.

Maximum window size is 664. see window description below. HS<7:0> programmable range

is [2C]- [D2], and should less than HE<7:0>. HS<7:0> should be programmable to value larger

than or equal to [2C]. Value larger than [D2] is invalid. See Figure 1.14.

Register 18 - rw: Horizontal Window end

HE<7:0> - selects the ending point of HREF window, each LSB represents four pixels for full resolution

and two pixels for QVGA resolution, this value is set based on an internal column counter, the

default value corresponds to the last available pixel. The HE<7:0> programmable range is

[2D] - [D2]. HE<7:0> should be larger than HS<7:0> and less than or equal to [D2]. Value

larger than [D2] is invalid. See Figure 1.14.

Register 19- rw: Vertical Window start

VS<7:0> - selects the starting row of vertical window, in full resolution mode, each LSB represents 1scan

line in one field for Interlaced Mode, 2 scan line in one frame for Progressive Scan Mode. In

QVGA resolution (set by register 14 bit 5), each LSB represents 1 scan line in one field for

Interlaced Mode, 1scan line in one frame for Progressive Scan Mode. See Figure 1.14. Min. is

[05], max. is [F6] and should less than VE<7:0>.

VE<7:0>- selects the ending row of vertical window, in full resolution mode, each LSB represents 1scan

line in one field for Interlaced Mode, 2 scan line in one frame for Progressive Scan Mode. In

QVGA resolution, each LSB represents 1 scan line in one field for Interlaced Mode, 1scan line

in one frame for Progressive Scan Mode. See Figure 1.14. Min. is [05], max. is [F6] and should

larger than VS<7:0>.

Bits

HS7

HS6

HS5

HS4

HS3

HS2

HS1

HS0

Default

0

0

1

0

1

1

1

1

Bits

HE7

HE6

HE5

HE4

HE3

HE2

HE1

HE0

Default

1

1

0

0

1

1

1

1

Bits

VS7

VS6

VS5

VS4

VS3

VS2

VS1

VS0

Default

0

0

0

0

0

1

1

0

Register 1A- rw: Vertical Window end

Bits

VE7

VE6

VE5

VE4

VE3

VE2

VE1

VE0

Default

1

1

1

1

0

1

0

1

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

35

Preliminary

Company Confidential

As shown above, HS<7:0> defines the starting pixel within a scan line, HE<7:0> defines the ending pixel

within a scan line. VS<7:0> defines the starting row within a field, VE<7:0> defines the ending

row within a field. VS/VE automatically defines the window height of a image frame. The rect-

angular window defined by HS/HE/VS/VE is the active image window. Only pixels insides this

window is valid, along with the HREF timing signals, black level substitutes the pixel data

when outside the active window.

Identical value for HS/HE or VS/VE is not permitted since it causes undefined window size.

If end point is lower than the starting point, the window begins from the starting point and ends at the far

end of the available image boundary.

The window size calculate formula is as below:

1. Horizontal size: VGA mode: Horizontal window size = (Register [18] - Register [17])*4.

QVGA mode: Horizontal window size = (Register [18] - Register [17])*2.

2. Vertical size: VGA mode: Vertical window size = (Register [1A]- Register [19]+1);

QVGA mode: Horizontal window size = (Register [1A] - Register [19]+ 1).

VS

VE

HS

HE

FULL image boundary

Active Window

FIG 1.11 Window Sizing

HREF

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

36

Preliminary

Company Confidential

PS<7:0> - to provide a way to fine tune the output timing of the pixel data relative to that of HREF, it phys-

ically shifts the video data output time early or late in unit of pixel clock as shown in the figure

below. This function is different from changing the size of the window as is defined by

HS<7:0> & HE<7:0> in register [17] and [18].

Register 1B- rw: Pixel shift

Bits

PS7

PS6

PS5

PS4

PS3

PS2

PS1

PS0

Default

0

0

0

0

0

0

0

0

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

37

Preliminary

Company Confidential

The number of pixels that can only be shifted late. Maximum shift pixel number is 255.

MIDH<7:0> - read only, always returns "7F".

Register 1C- r: Manufacture ID high byte

Bits

MIDH7

MIDH6

MIDH5

MIDH4

MIDH3

MIDH2

MIDH1

MIDH0

Default

0

1

1

1

1

1

1

1

Register 1D- r: Manufacture ID low byte

Bits

MIDL7

MIDL6

MIDL5

MIDL4

MIDL3

MIDL2

MIDL1

MIDL0

Default

1

0

1

0

0

0

1

0

HREF

Y<7:0>

- DEFAULT

Y<7:0>

- LATE

define by

HS<7:0>

define by

HE<7:0>

Full= 664

physical image boundary

ACTIVE WINDOW

BLACK LEVEL

FIG 1.12 Pixel Shift Examples

LEFT SIDE

PIXEL ADDED

RIGHT SIDE

PIXEL LOST

right

shift

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

38

Preliminary

Company Confidential

MIDL<7:0>- read only, always returns "A2"

Register 1E ~ 1F- rw: Reserved

These two registers are reserved for internal use. Write data to these registers will not function.

Register 20- rw: Common control E

COME7 - Modified CCIR656 format vertical sizing enabled. "1" will enable vertical windowing function. "0"

will limit vertical size to 480 lines - unchanged by [19] and [1B ].

COME6 - Field luminance average signal generation enable.Value is stored in register [7C]

COME5 - "1" First stage aperture correction enable. Correction strength will be decided by register [07]. "0"

disable first stage aperture correction.

COME4 - "1" Second stage aperture correction enable. Correction strength and threshold value will be

decided by register 26 bit 7 ~ register 26 bit 4.

COME3 - AWB smart mode enable. 1 - Drop out pixel when compare pixel red, blue and green component

level to change register [01] and [02], which luminance level is higher than presetting level and

lower than presetting level, this two level is set by register [0F]. 0 - calculate all pixels to get

AWB result. Valid only when register 13 bit 0=1 and register 12 bit 2=1

COME2 - Reserved.

COME1 - AWB fast/slow mode selection. "1" - AWB is always fast mode, that is register [01] and [02] is

changed every field/frame. "0" AWB is slow mode, [01] and [02] change every 16/64 field/

frame decided by register 70 bit 1. When AWB enable, register 12 bit 2=1, AWB is working as

fast mode at first 1024 field/frame, than as slow mode later.

COME0 - Digital output driver capability increase selection: "1" Double digital output driver current; "0" low

output driver current status.

Y

6-Y0: Y channel digital output offset adjustment. Range: +127mV ~ -127mV. If COMG2=0, this register

will be updated by internal auto A/D BLC circuit, and write a value to this register with SCCB

has no effect. If COMG2=1, Y channel offset adjustment will use the register stored value

which can be changed by SCCB. If COMF1=0, this register has no adjustment effect to A/D

output data. If output RGB raw data, this register will adjust R/G/B data.

Y7: Offset adjustment direction 0 - Add Y[6:0]; 1 - Subtract Y[6:0].

Bits

COME7

COME6

COME5

COME4

COME3

COME2

COME1

COME0

Default

0

0

0

0

0

-

0

0

Register 21- rw: Y Channel Offset Adjustment

Bits

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

Default

1

0

0

0

0

0

0

0

OV7620 Product Specifications - Rev. 1.2 (5/13/00)

OMNIVISION TECHNOLOGIES INC.

39

Preliminary

Company Confidential

U

6-U0: U channel digital output offset adjustment. Range: +128mV ~ -128mV. If register 27 bit 2=0, this

register will be updated by internal auto A/D BLC circuit, and write a value to this register with