www.fairchildsemi.com

1

REV. 0.9.1 11/24/99

Features

∑ 8-bit resolution

∑ 80, 50, and 30 megapixels per second

∑ ±0.5 LSB linearity error

∑ Sync, blank, and white controls

∑ Independent sync current output

∑ 1.0V p-p video into 37.5

or 75

load

∑ Enhancement of the ADV7120

≠ Internal bandgap voltage reference

≠ Double-buffered data for low distortion

≠ Power-down sleep mode

∑ Double-buffered data for low distortion

∑ TTL-compatible inputs

∑ Low glitch energy

∑ Single +3.3V±5% Volt power supply

Applications

∑ Video and graphics displays

∑ Image processing systems

∑ Video signal conversion

∑ Broadcast television equipment

∑ Digital synthesis

Description

The TMC3533 is a high-speed triple 8-bit D/A converter

especially suited for video and graphics applications.

It offers 8-bit resolution, TTL-compatible inputs, low power

consumption, a power-down sleep mode, and requires only a

single +3.3V±5% Volt power supply. It has single-ended

current outputs, SYNC and BLANK control inputs, and a

separate current source for adding sync pulses to any D/A

converter output. WHITE and SLEEP control inputs are

available on PLCC parts. It is ideal for generating analog

RGB from digital RGB and driving computer display and

video monitors. Three speed grades are available: 30, 50, and

80 Msps.

The TMC3533 triple D/A converter is available in a 44-lead

plastic J-leaded PLCC. It is also available in a 48-lead plastic

LQFP package. It is fabricated on a sub-micron CMOS pro-

cess with performance guaranteed from 0∞C to 70∞C.

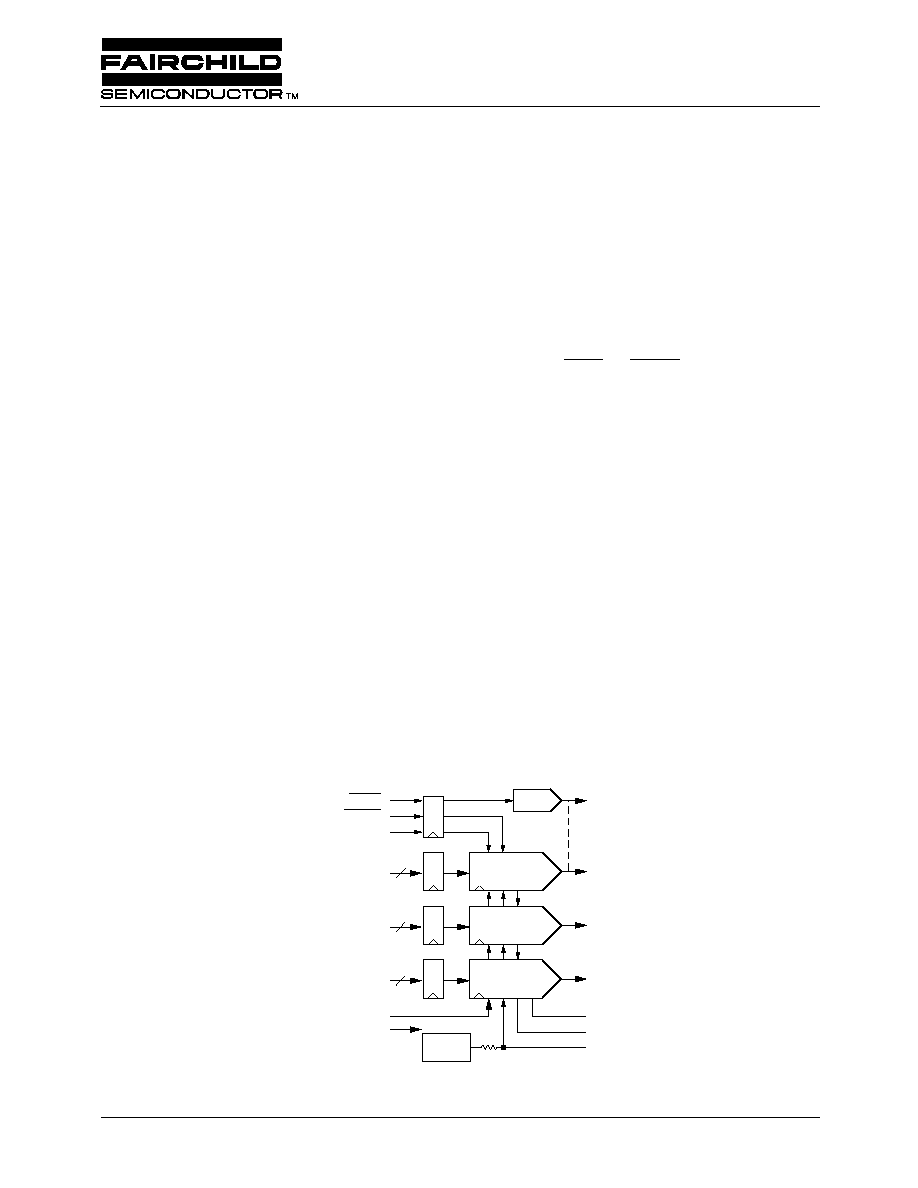

Block Diagram

8 bit D/A

Converter

SYNC

8

SYNC

CLOCK

SLEEP [PLCC only]

IO

S

G

7-0

COMP

65-3533-01

+1.235V

Ref

IO

G

BLANK

8 bit D/A

Converter

8

B

7-0

IO

B

8 bit D/A

Converter

8

R

7-0

IO

R

R

REF

V

REF

WHITE [PLCC only]

[LQFP only]

TMC3533

Triple Video D/A Converter

8 bit, 80 Msps, 3.3V

TMC3533

PRODUCT SPECIFICATION

2

REV. 0.9.1 11/24/99

Functional Description

The TMC3533 is a low-cost triple 8-bit CMOS D/A con-

verter designed to directly drive computer CRT displays at

pixel rates up to 80 Msps. It comprises three identical 8-bit

D/A converters with registered data inputs, common clock,

and internal voltage reference. An independent current

source allows sync to be added to any D/A converter output.

Digital Inputs

All digital inputs are TTL-compatible. Data are registered on

the rising edge of the CLK signal. The analog output

changes t

DO

after the rising edge of CLK. There is one stage

of pipeline delay on the chip. The guaranteed clock rates of

the TMC3533 are 80, 50, and 30 MHz.

SYNC and BLANK

SYNC and BLANK inputs control the output level

(Figure 1 and Table 1) of the D/A converters during CRT

retrace intervals. BLANK forces the D/A outputs to the

blanking level while SYNC turns off a separate current

source which is brought off the chip through the IO

S

pin.

Figure 1. Nominal Output Levels

IO

S

may be connected to any one D/A output, or used inde-

pendently. It is commonly tied to the green D/A converter for

"Sync on Green" operation. This connection adds a 40 IRE

sync pulse to the D/A output and brings that D/A output to

0.0 Volts during the sync tip. SYNC and BLANK are regis-

tered on the rising edge of CLK.

BLANK gates the D/A inputs and sets the pedestal voltage.

If BLANK = HIGH, the D/A inputs are added to a pedestal

which offsets the current output. If BLANK = LOW, data

inputs and the pedestal are disabled.

WHITE

The WHITE control drives all three D/As to full-scale, over-

riding the data inputs. It is overridden by the BLANK input,

and is independent of SYNC.

data: 660 mV max.

65-3503-02

pedestal: 54 mV

sync: 286 mV

SLEEP

The SLEEP control, when HIGH, places the TMC3533 in a

power-down state. This function operates asynchronously.

D/A Outputs

Each D/A output is a current source. To obtain a voltage out-

put, a resistor must be connected to ground. Output voltage

depends upon this external resistor, the reference voltage,

and the value of the gain-setting resistor connected between

R

REF

and GND.

Normally, a source termination resistor of 75 Ohms is con-

nected between the D/A current output pin and GND near

the D/A converter. A 75 Ohm coaxial cable may then be con-

nected with another 75 Ohm termination resistor at the far

end of the cable. This "double termination" presents the D/A

converter with a net resistive load of 37.5 Ohms.

The TMC3533 may also be operated with a single 75 Ohm

terminating resistor. To lower the output voltage swing to the

desired range, the value of the resistor on R

REF

should be

increased.

Voltage Reference

The TMC3533 has an internal bandgap voltage reference of

+1.235 Volts. An external voltage reference may be con-

nected to the V

REF

pin, overriding the internal voltage refer-

ence. All three D/A converters are driven from the same

reference.

A 0.1µF capacitor must be connected between the COMP

pin and V

DD

to stabilize internal bias circuitry and ensure

low-noise operation.

Power and Ground

The TMC3533 D/A converter requires a single +3.3 Volt

power supply. The analog (V

DD

) power supply voltage

should be decoupled to GND to reduce power supply

induced noise. 0.1µF decoupling capacitors should be placed

as close as possible to the power pins.

The high slew-rate of digital data makes capacitive coupling

to the outputs of any D/A converter a potential problem.

Since the digital signals contain high-frequency components

of the CLK signal, as well as the video output signal, the

resulting data feedthrough often looks like harmonic distor-

tion or reduced signal-to-noise performance. All ground pins

should be connected to a common solid ground plane for

best performance.

PRODUCT SPECIFICATION

TMC3533

REV. 0.9.1 11/24/99

3

Table 1. Output Voltage versus Input Code, SYNC, BLANK, and WHITE

V

REF

= 1.235 V, R

REF

= 572

, R

L

= 37.5

Pin Assignments

Notes (LQFP Package Only):

1. Pin functions White and Sleep are not available.

2. IO

S

function is internally tied to IO

G

pin.

RGB7-0

(MSB...LSB)

All D/As

D/A with IOS Connected

SYNC

BLANK

WHITE

V

OUT

SYNC

BLANK

WHITE

V

OUT

XXXX XXXX

X

1

1

0.714

1

1

1

1.000

1111 1111

X

1

0

0.714

1

1

0

1.000

1111 1110

X

1

0

0.711

1

1

0

0.997

1111 1101

X

1

0

0.709

1

1

0

0.995

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

0000 0000

X

1

0

0.385

1

1

0

0.671

1111 1111

X

1

0

0.383

1

1

0

0.669

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

∑

0000 0010

X

1

0

0.059

1

1

0

0.345

0000 0001

X

1

0

0.057

1

1

0

0.343

0000 0000

X

1

0

0.054

1

1

0

0.340

XXXX XXXX

X

0

X

0.000

1

0

X

0.286

XXXX XXXX

X

0

X

0.000

0

0

X

0.000

65-3533-03

G

0

G

1

G

2

G

3

G

4

G

5

G

6

G

7

BLANK

SYNC

V

DD

R

REF

V

REF

COMP

IO

R

IO

G

IO

S

V

DD

V

DD

V

DD

IO

B

GND

GND

GND

GND

R

7

R

6

R

5

R

4

R

3

R

2

R

1

R

0

B

0

B

1

B

2

B

3

B

4

B

5

B

6

B

7

CLK

WHITE

SLEEP

7

8

9

10

11

12

13

14

15

16

17

39

38

37

36

35

34

33

32

31

30

29

18

19

20

21

22

23

24

25

26

27

28

6

5

4

3

2

1

44

43

42

41

40

TMC3533

PLCC Package

65-3533-06

GND

G

0

G

1

G

2

G

3

G

4

G

5

G

6

G

7

BLANK

V

DD

R

0

GND

NC

R

REF

V

REF

COMP

IO

G

IO

R

OV

DD

V

DD

IO

B

GND

GND

NC

GND R

7

R

6

R

5

R

4

R

3

R

2

R

1

NC

GND

GND

B

0

B

1

B

2

B

3

B

4

B

6

B

5

NC

1

2

3

4

5

6

7

8

9

10

SYNC

11

12

36

35

34

33

32

31

30

29

28

27

CLOCK

26

25

13

14

15

16

17

18

19

20

21

22

B

7

23

24

48

47

46

45

44

43

42

41

40

39

GND

38

37

TMC3533

LQFP Package

TMC3533

PRODUCT SPECIFICATION

4

REV. 0.9.1 11/24/99

Pin Descriptions

Pin

Name

Pin Number

Value

Pin Function Description

LQFP

PLCC

Clock and Pixel I/O

CLK

26

27

TTL

Clock Input. The clock input is TTL-compatible and all pixel

data is registered on the rising edge of CLK. It is recommended

that CLK be driven by a dedicated TTL buffer to avoid reflection

induced jitter, overshoot, and undershoot.

R

7-0

G

7-0

B

7-0

47-40

9-2

23-16

6-1, 44-43

14-7

25-18

TTL

Red, Green, and Blue Pixel Inputs. The R, G, and B digital

inputs are TTL-compatible and registered on the rising edge of

CLK.

Controls

SYNC

11

16

TTL

Sync Pulse Input. Bringing SYNC LOW, turns off a 40 IRE

(7.62 mA) current source which forms a sync pulse on any D/A

converter output connected to IO

S

. SYNC is registered on the

rising edge of CLK along with pixel data and has the same

pipeline latency as BLANK and pixel data. SYNC does not

override any other data and should be used only during the

blanking interval. If the system does not require sync pulses,

SYNC and IO

S

should be connected to GND.

BLANK

10

15

TTL

Blanking Input. When BLANK is LOW, pixel inputs are ignored

and the D/A converter outputs are driven to the blanking level.

BLANK is registered on the rising edge of CLK and has the

same two-pipe latency as SYNC and Data.

WHITE

--

26

TTL

Force Full Scale Input. When WHITE is HIGH, pixel inputs are

ignored and the D/A converter outputs are driven to their full-

scale output level. A BLANK input overwrites a WHITE input.

WHITE is register on the rising edge of CLK and has the same

two-pipe latency as SYNC and Data.

SLEEP

--

28

TTL

Power-down Control Input. When HIGH, SLEEP places the D/

A converter in a low-power-dissipation mode. The D/A current

sources and the digital processing are disabled. The last data

loaded into the input and D/A registers is retained. This control is

asynchronous.

Video Outputs

IO

R

IO

G

IO

B

33

32

29

39

38

33

0.714 V

p-p

Red, Green, and Blue Data Outputs. The current source

outputs of the D/A converters are capable of driving RS-343A/

SMPTE-170M compatible levels into doubly-terminated 75 Ohm

lines. Sync pulses may be added to any D/A output.

IO

S

32

(connected

to IO

G

)

37

0.714 V

p-p

SYNC Current Output. When this pin is connected to any of the

D/A converter outputs, a 40 IRE offset can be added to the video

level. When the SYNC input is LOW, the current is turned off,

bring the sync tip voltage to 0.0V. If no sync pulse is required,

IO

S

should be grounded. When SYNC is HIGH, the current

flowing out of IO

S

is:

IO

S

= 3.64 (V

REF

/ R

REF

)

Voltage Reference

V

REF

35

41

+1.235 V

Voltage Reference Input/Output. An internal voltage source of

+1.235 Volts is output on this pin. An external +1.235 Volt

reference may be applied here which overrides the internal

reference. Decoupling V

REF

to GND with a 0.1µF ceramic

capacitor is required.

PRODUCT SPECIFICATION

TMC3533

REV. 0.9.1 11/24/99

5

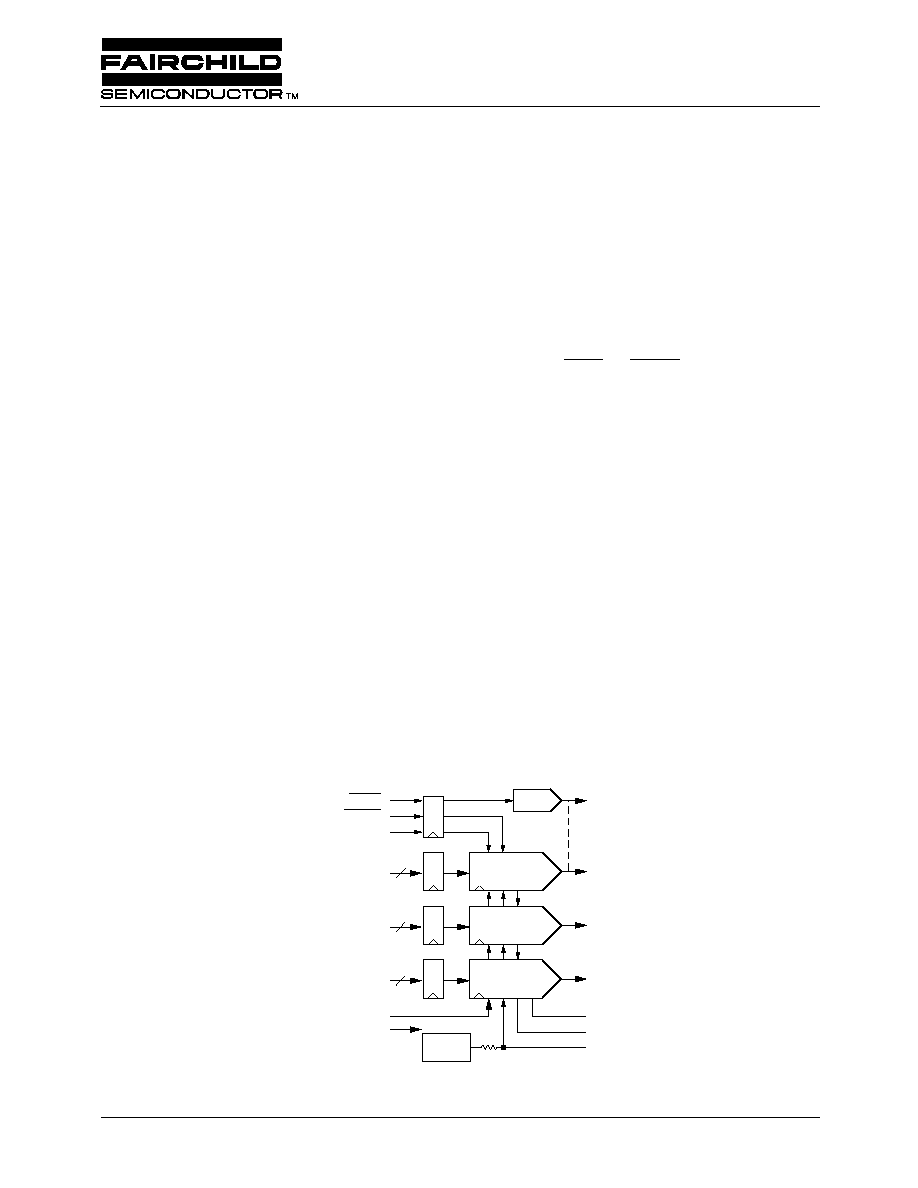

Equivalent Circuits

Figure 2. Equivalent Digital Input Circuit Figure 3. Equivalent Analog Output Circuit

R

REF

36

42

572

Current-setting Resistor. The full-scale output current of each

D/A converter is determined by the value of the resistor

connected between R

REF

and GND. The nominal value for

R

REF

is found from:

R

REF

= 9.1 (V

REF

/I

FS

),

but is optimized to be 572

. I

FS

is the full-scale (white) output

current (amps) from an output without sync. Sync current is 0.4

I

FS

.

D/A full-scale (white) current may also be calculated from:

I

FS

= V

FS

/R

L

Where V

FS

is the white voltage level and R

L

is the total resistive

load (ohms) on each D/A converter. V

FS

is the blank to full-scale

voltage.

COMP

34

40

0.1 µF

Compensation Capacitor. A 0.1 µF ceramic capacitor must be

connected between COMP and V

DD

to stabilize internal bias

circuitry.

Power, Ground

V

DD

12, 30, 31 17, 34≠36

+3.3 V

Power Supply.

GND

1, 14, 15,

27, 28, 38,

39, 48

29≠32

0.0V

Ground.

NC

13, 24, 25,

37

--

--

No Connect

Pin

Name

Pin Number

Value

Pin Function Description

LQFP

PLCC

n

p

OUT

GND

27013B

V

DD

V

DD

Digital

Input

V

DD

p

n

27014D

GND

Pin Descriptions

(continued)