| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: SP8720BDG | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

ABSOLUTE MAXIMUM RATINGS

Supply voltage

Output current

Storage temperature range

Max. junction temperature

Max. clock input voltage

SP8720

300MHz4

4

4

4

4

3/4

DS3650-1∑2

The SP8720 is an ECL two-modulus divider, with ECL10K

compatible outputs. It divides by 3 when either of the ECL control

inputs, PE1 or PE2, is in the high state and by 4 when both are low

(or open circuit). An AC coupled input of 600mVp-p is required.

FEATURES

s

ECL Compatible Outputs

s

AC-Coupled Input (Internal Bias)

s

Control Inputs ECL III/10K Compatible

QUICK REFERENCE DATA

s

Supply Voltage: 25∑2V

s

Power Consumption: 240mW

s

Temperature Range:

2

55

∞

C to 1125

∞

C (A Grade)

2

30

∞

C to 170

∞

C (B Grade)

Fig. 1 Pin connections - top view

DG16

2

8V

20mA

2

65

∞

C to 1150

∞

C

1

175

∞

C

2∑5V p-p

ORDERING INFORMATION

SP8720 A DG

SP8720 B DG

5962-90577 (SMD)

Fig. 2 Functional diagram

CLOCK INPUT

PE1

PE2

NC

V

CC

NC

NC

OUTPUT

INTERNAL BIAS DECOUPLING

NC

NC

NC

V

EE

DO NOT CONNECT

NC

OUTPUT

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

CONTROL

INPUTS

SP8720

V

CC

(0V)

D1

CK

Q1

D2

CK

Q2

PE1

PE2

CLOCK INPUT

OUTPUT

OUTPUT

V

EE

2

3

1

5

12

8

9

INTERNAL BIAS

DECOUPLING

16

Q2

ADVANCE INFORMATION

2

SP8720

ELECTRICAL CHARACTERISTICS

Unless otherwise stated, the Electrical Characteristics are guaranteed over specified supply, frequency and temperature range

Supply voltage, V

CC

= 0V, V

EE

= 25∑2V 6 0∑25V

Temperature, T

AMB

= 255

∞

C to 1125

∞

C (A Grade), 230

∞

C to 170

∞

C (B Grade)

Characteristic

Maximum frequency (sinewave input)

Minimum frequency (sinewave input)

Power supply current

Output high voltage

Output low voltage

PE input high voltage

PE input low voltage

Clock to output delay

Set-up time

Release time

Symbol

f

MAX

f

MIN

I

EE

V

OH

V

OL

V

INH

V

INL

t

p

t

s

t

r

300

2

0∑85

2

1∑8

2

0∑93

2∑5

3

Min.

Max.

40

65

2

0∑7

2

1∑5

2

1∑62

6

Value

Units

Input = 400-800mV p-p

Input = 400-800mV p-p

V

EE

= 25∑2V

V

EE

= 25∑2V (25

∞

C)

V

EE

= 25∑2V (25

∞

C)

V

EE

= 25∑2V (25

∞

C)

V

EE

= 25∑2V (25

∞

C)

Conditions

Notes

MHz

MHz

mA

V

V

V

V

ns

ns

ns

5

5

5

6

3, 6

4, 6

NOTES

1. The temperature coefficients of V

OH

= 11∑63mV/

∞

C, V

OL

= 10∑94mV/

∞

C and of V

IN

= 11∑22mV/

∞

C.

2. The test configuration for dynamic testing is shown in Fig.6.

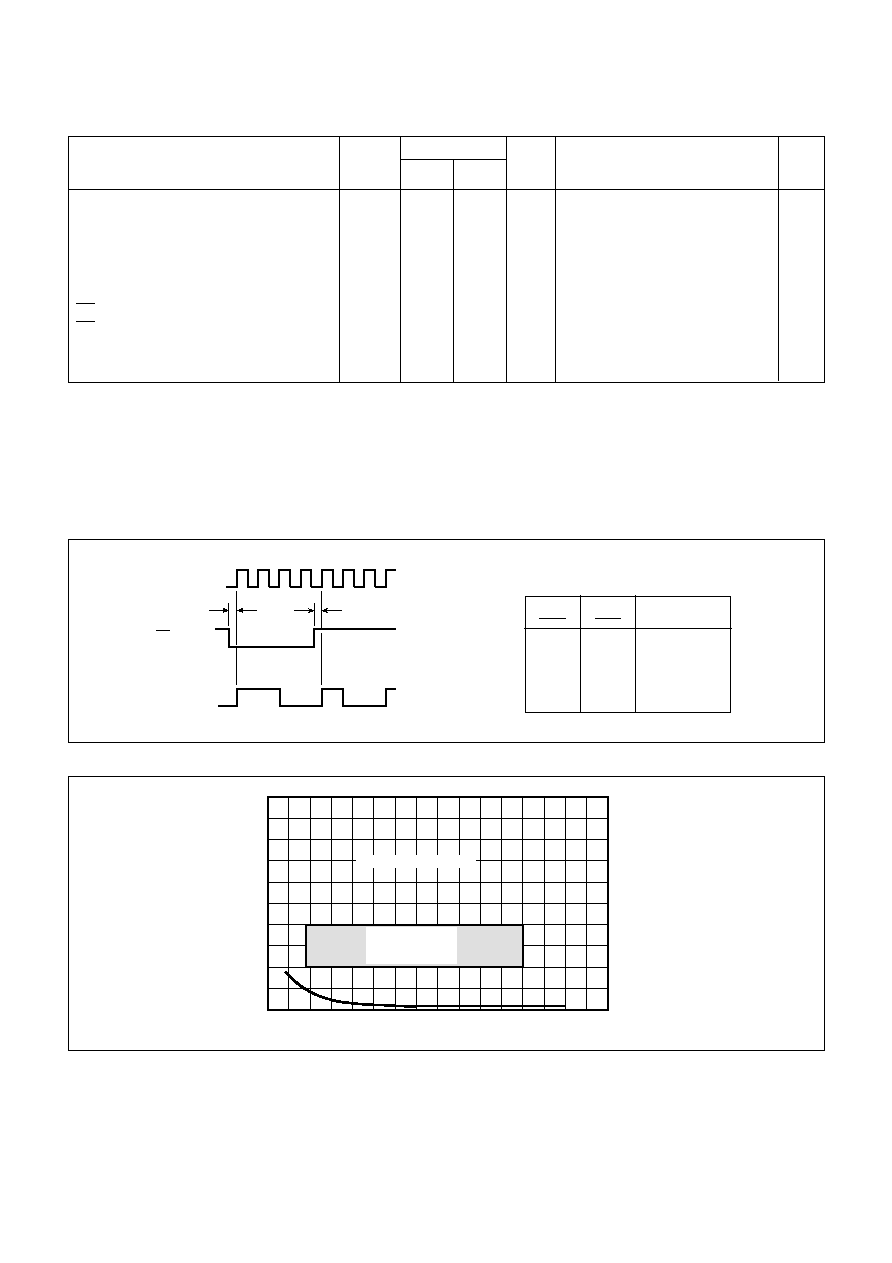

3. The set-up time t

s

is defined as the minimum time that can elapse between L

H transition of control input and the next L

H clock pulse transition

to ensure that the 43 mode is obtained.

4. The release time t

r

is defined as the minimum time that can elapse between H

L transition of control input and the next L

H clock pulse transition

to ensure that the 44 mode is obtained.

5. SP8720B tested at 25

∞

C only.

6. Guaranteed but not tested.

L

H

L

H

PE1

L

L

H

H

TRUTH TABLE FOR

CONTROL INPUTS

4

3

3

3

PE2

Division ratio

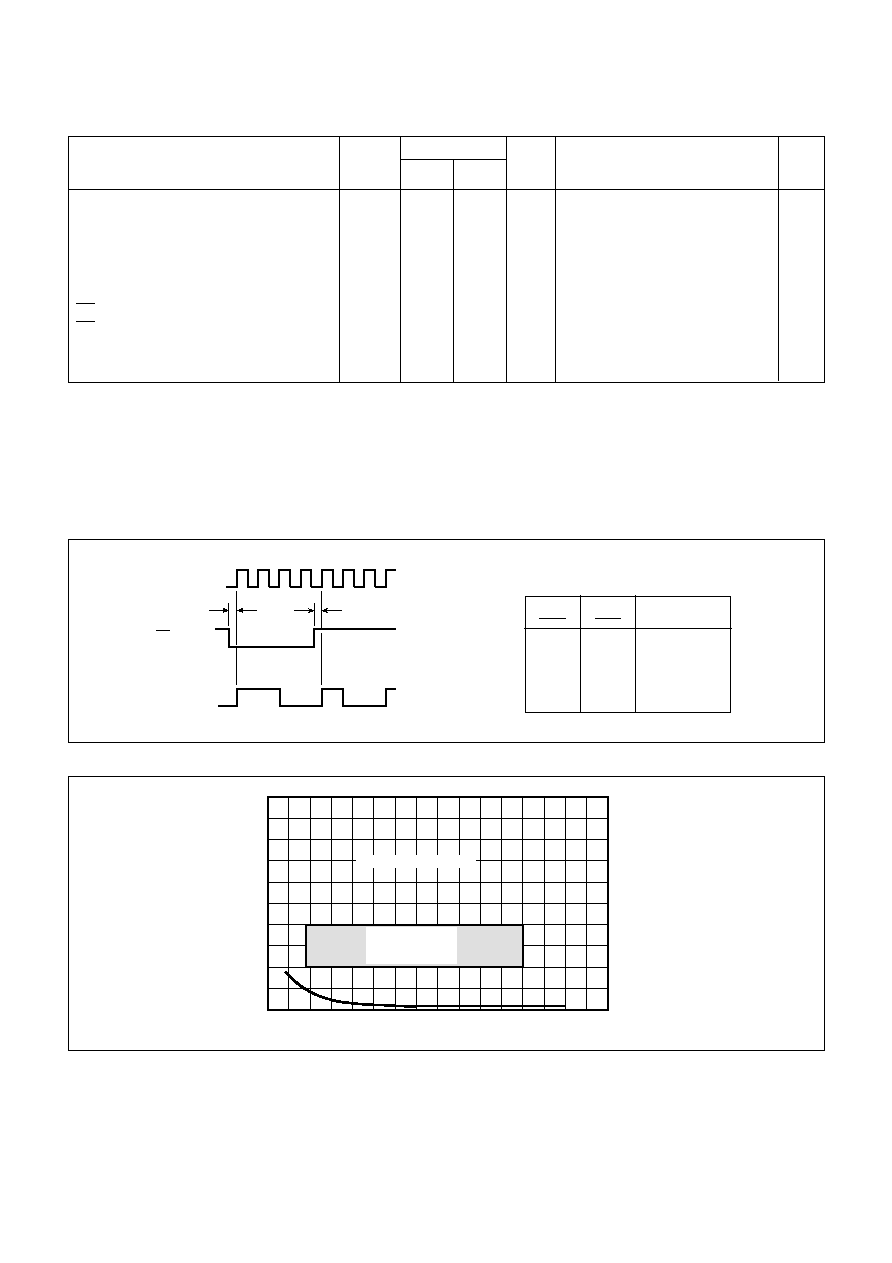

2000

1600

1200

800

400

0

0 100 200 300 400

INPUT FREQUENCY (MHz)

INPUT AMPLITUDE

(mV p-p)

*

Tested as specified

in table of Electrical

Characteristics

GUARANTEED

*

OPERATING

WINDOW

T

AMB

= 255

∞

C TO 1125

∞

C

Fig. 4 Typical input characteristic of SP8720A

Fig. 3 Timing diagram

2

t

r

t

s

1

CLOCK INPUT

PE INPUT

OUTPUT

2

2

3

SP8720

OPERATING NOTES

1. The clock input is biased internally and is coupled to the signal

source with a suitable capacitor. The input signal path is completed

by an input reference decoupling capacitor which is connected

from pin 16 to ground.

2. If no signal is present the device will self-oscillate. If this is

undesirable, it may be prevented by connecting a 15k

resistor

from the clock input (pin 1) to V

EE

. This will reduce the input

sensitivity by approximately 100mV.

3. The circuit will operate down to DC but slew rate must be better

than 100V/

µ

s.

4. The Q and Q outputs are compatible with ECLII but can be

interfaced to ECL10K as shown in Fig. 7. There is an internal

circuit equivalent to a load of 2k

at each output.

5. The PE inputs are ECLIII/10K compatible and include 4∑3k

pulldown resistors. Unused inputs can therefore be left open.

6. The input impedance of the SP8720 varies as a function of

frequency, see Fig. 5.

7. All components should be suitable for the frequency in use.

Fig. 5 Typical input impedance. Test conditions: Supply Voltage = 25∑2V,

Ambient Temperature = 25

∞

C. Frequencies in MHz, impedances normalised to 50

.

Fig. 6 Test circuit

DUT

450

450

100n

100n

OUTPUTS TO

SAMPLING

SCOPE

V

EE

= 25∑2V

5

8

9

12

16

1

1n

1n

1n

33

33

20

INPUT FROM

GENERATOR

TO SAMPLING

SCOPE

150

j 2

j 1

j 0.5

j 0.2

0

2

j 0.2

2

j 0.5

2

j 1

2

j 2

1

0.5

0.2

j 5

2

j 5

2

5

100

200

300

250

50

4

SP8720

Fig. 7 Typical application circuit showing interfacing

DIVIDE BY

3/4

ECL CONTROL INPUTS

0 = 4

1 = 3

9

8

2k

2k

4∑3k

4∑3k

2

3

12

400

1

16

5

BIAS

ECL10K

OUTPUT

15k

1n

1n

1n

1∑5k

47

V

EE

PE1

PE2

CLOCK

INPUT

5

SP8720

NOTES