1

GLT41016-10E

64k x 16 Embedded EDO DRAM

F

EATURES

x

Logical organization: 64k x 16 bits

x

Physical organization: 256 x 256 x 16

x

Single 3.3V

±

0.3V power supply

x

256 cycle refresh in 4 ms

x

Refresh modes: RAS only, CBR, and Hidden

x

Dual CAS for Byte Write and Byte Read control

x

Separate I/O operation

x

100 MHz page mode EDO cycle

x

30 ns row access time

x

Redundancy: 2 WL/256K, 2 CS/1M

G

ENERAL

D

ESCRIPTION

The 1 Mbit Embedded DRAM (EmDRAM) is an asynchro-

nous design with non-multiplexed row and column

addressing scheme. The memory operations are con-

trolled by RAS, CASH/CASL, and WE. Byte access is

controlled by CASH (upper byte) and CASL (lower byte).

The EmDRAM has been designed to support 200Mbyte

data rate with a 30 ns latency when operated in the page

mode with extended data output (EDO). this maximum

rate can be sustained for one page of 12 bytes.

Performance Data

Parameter

-30

Max. RAS access time, t

RAC

30 ns

Max. column address access time, t

AA

12 ns

Max. CAS access time, t

CAC

8 ns

Min. extended data out page mode cycle time, t

PC

10 ns

Min. read/write cycle time, t

RC

60 ns

May 1997 (Rev. 1)

2

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

F

UNCTIONAL

B

LOCK

D

IAGRAM

1. On-chip power supply to the EmDRAM should be separated from the Logic portion.

RAS

Timing

Generator

LCAS

Column

Address

Buffers

Internal

Address

Counter

Row

Address

Buffers

Refresh

Control

Clock

Column Decoders

Sense Amps

Memory Cells

Word Drivers

Row Decoders

A[8:0]

I/O Selector

Output

Buffer

Input

Buffer

DQ[15:8]

V

SS

V

CC

Output

Buffer

Input

Buffer

DQ[7:0]

UCAS

I/O Controller

I/O Controller

WE

OE

Figure 1. GLT44016 - 256K X 16

Y[8:0]

X[8:0]

Signal Descriptions

[1]

Symbol

Type

Description

DI[15:0]

Input

Data in.

DO[15:0]

Output

Data out.

XRA[7:0]

Input

Row address.

XCA[7:0]

Input

Column address.

RAS

Input

Row address strobe (active low).

CASH

Input

Column address strobe, access DI/DO[15:8] (active low)

CASL

Input

Column address strobe, access DI/DO[7:0] (active low)

WE

Input

Write enable (active low).

OE

Input

Output enable (active low).

V

DD

Supply

3.3v voltage supply, 2 pairs double bond minimum

V

SS

Supply

Ground (voltage return), 2 pairs double bond minimum

3

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

Function Table

Input Pin

DQ Pin

Functional Mode

RAS

LCAS

UCAS

WE

OE

DQ[7:0]

DQ[15:8]

H

≠

≠

≠

≠

High-Z

High-Z Standby

L

H

H

≠

≠

High-Z

High-Z Refresh

L

L

H

H

L

D

OUT

High-Z

Lower Byte Read

L

H

L

H

L

High-Z

Dout

Upper Byte Read

L

L

L

H

L

Dout

Dout

Word Read

L

L

H

L

H

Din

Don't Care

Lower Byte Write

L

H

L

L

H

Don't Care

Din

Upper Byte Write

L

L

L

L

H

Din

Din

Word Write

L

L

L

H

H

High-Z

High Z

≠

Truth Table

Function

RAS

CAS

WE

OE

Address

DQM0

DQM1

DQM2

DQM3

DI[31:0]

DO[31:0]

Standby

H

H

X

X

X

X

X

X

X

X

High-Z

Read

L

L

H

L

Row/Col

X

X

X

X

X

Data Out

Write (Early)

L

L

L

X

Row/Col

H

H

H

H

Data In

High-Z

Write DI[7:0]

L

L

L

X

Row/Col

L

H

H

H

Data In

High-Z

Write DI[15:8]

L

L

L

X

Row/Col

H

L

H

H

Data In

High-Z

Write DI[23:16]

L

L

L

X

Row/Col

H

H

L

H

Data In

High-Z

Write DI[31:24]

L

L

L

X

Row/Col

H

H

H

L

Data In

High-Z

Read-Write

L

L

H

L

L

H

Row/Col

H

H

H

H

Data In

Data Out

Page-Mode Read (First Cycle)

L

H

L

H

L

Row/Col

X

X

X

X

X

Data Out

Page-Mode Read (Subsequent Cycles)

H

L

H

L

Col

X

X

X

X

X

Data Out

Page-Mode Write (First Cycle)

L

H

L

L

X

Row/Col

H

H

H

H

Data In

High-Z

Page-Mode Write (Subsequent Cycle)

L

H

L

L

X

Col

H

H

H

H

Data In

High-Z

Page-Mode R-W (First Cycle)

L

H

L

H

L

L

H

Row/Col

H

H

H

H

Data In

Data Out

Page-Mode R-W (Subsequent Cycle)

L

H

L

H

L

L

H

Col

H

H

H

H

Data In

Data Out

CBR Refresh

H

L

L

X

X

X

X

X

X

X

X

High-Z

RAS-only Refresh

L

H

X

X

Row

X

X

X

X

X

High-Z

4

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

E

LECTRICAL

S

PECIFICATIONS

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the

operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

1. I

CC

Max. is specified for I

CC

for the output open condition.

2. Address can be changed once or less while RAS = V

IL

.

3. Address can be changed once or less while CAS = V

IH

.

Absolute Maximum Ratings

[1]

Symbol

Parameter

Conditions

Value

Unit

V

T

Voltage on any pin relative to V

SS

T

A

= 25 ∞C

-0.5 to +4.6

V

I

OS

Short circuit output current

T

A

= 25 ∞C

50

mA

P

D

Power dissipation

T

A

= 25 ∞C

1

W

T

OPR

Operating temperature

≠

0 to +70

∞

C

T

STG

Storage temperature

≠

-55 to +150

∞

C

Recommended Operating Conditions (T

A

= 0

∞

C to +70

∞

C)

Symbol

Parameter

Min

Typ

Max

Unit

V

CC

Power supply voltage

3.0

3.3

3.6

V

V

SS

0

0

0

V

V

IH

Input high voltage

2.4

≠

V

CC

+1

V

V

IL

Input low voltage

-1.0

≠

0.8

V

Capacitance (V

CC

= 5V

±

10%, T

A

= 25

∞

C, f = 1 MHz)

Symbol

Parameter

Min

Typ

Max

Unit

C

IN1

Input capacitance (A[8:0])

≠

1

pF

C

IN2

Input capacitance (RAS, LCAS, UCAS, WE, OE)

≠

1

pF

C

I/O

Input/Output capacitance (DQ[15:0])

≠

1

pF

DC Characteristics (V

CC

= 5V

±

10%, T

A

= 0

∞

C to +70

∞

C)

Symbol

Parameter

Condition

-30

Units

Note

Min

Max

V

OH

Output High Voltage

I

OH

= -2 mA

2.4

V

CC

V

V

OL

Output Low Voltage

I

OL

= -1.0mA

0

0.4

V

I

LI

Input Leakage Current

0V

V

IN

V

CC

-2

-2

µ

A

I

LO

Output Leakage Current

DQi Disable 0V

V

O

3.6V

-10

-10

µ

A

I

CC1

Average Power Supply Current

(Operating)

RAS, CAS Cycling, t

RC

=Min.

200

mA

[1] [2]

I

CC2

Power Supply Current (Standby)

RAS, CAS = V

IH

mA

[1]

I

CC3

Average Power Supply Current

(RAS-only Refresh)

RAS -Cycling, CAS = V

IH,

t

RC

= Min.

200

mA

[1] [2]

I

CC4

Average Power Supply Current

(Fast Page Mode)

RAS = V

IL,

CAS Cycling, t

HCP

= Min.

140

mA

[1] [3]

I

CC5

Average Power Supply Current

(CAS-before-RAS Refresh)

RAS Cycling, CAS-before-RAS

200

mA

5

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

1. Maximum CASH to CASL skew is 1 ns.

2. Last CASx LOW.

3. Last CASx HIGH.

4. First CASx LOW.

5. First CASx HIGH.

6. Last CASx LOW to first CASx HIGH.

7. Last CASx HIGH to first CASx LOW.

AC Characteristics (V

CC

= 3.3 V

±

10%, T

A

= 0

∞

C - 70

∞

C, C

L

= 1 pF)

Symbol

Description

Min

Max

Units

Notes

t

RC

Random Read/Write cycle time

60

≠

ns

t

PC

Page Mode Read/Write cycle

10

≠

ns

[1]

[2]

t

OFF

Read Data valid from RAS high

0

≠

ns

[3]

t

DOH

Read Data valid from next CAS low

3

≠

ns

[4]

t

AA

Access time from Column Address

≠

12

ns

t

RAC

Access time from RAS low

≠

30

ns

t

CAC

Access time from CAS low

≠

8

ns

[2]

t

CPA

Access time from CAS precharge

≠

14

ns

[3]

t

RAS

RAS pulse width

30

≠

ns

t

RCD

RAS to CAS delay time

15

35

ns

t

CSH

CAS hold time for RAS

30

[5]

t

CAS

CAS pulse width

4

≠

ns

[6]

t

ASR

Row Address setup time

3

≠

ns

t

RAH

Row Address hold time

3

≠

ns

t

ASC

Column Address setup time

3

≠

ns

[4]

t

CAH

Column Address hold time

3

≠

ns

[2]

t

CP

CAS precharge time

4

≠

ns

[7]

t

DS

Write Data setup time

3

≠

ns

[4]

t

DH

Write Data hold time

3

≠

ns

[2]

t

RP

RAS precharge time

20

≠

ns

t

CRP

CAS to RAS precharge time

15

≠

ns

[3]

t

RSH

CAS low to RAS high hold time

10

≠

ns

[2]

t

RCS

Read command setup time

0

≠

ns

[4]

t

RCH

Read command hold time from CAS high

0

≠

ns

[3]

t

RRH

Read command hold time from RAS high

0

≠

ns

t

WCS

Write command setup time

5

≠

ns

t

WCH

Write command hold time

5

≠

ns

t

WP

WE pulse width

8

≠

ns

t

T

Transition time (rise and fall)

≠

1.5

ns

t

RWL

Write command to RAS high

8

≠

ns

t

CWL

Write command to CAS high

8

≠

ns

[5]

6

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

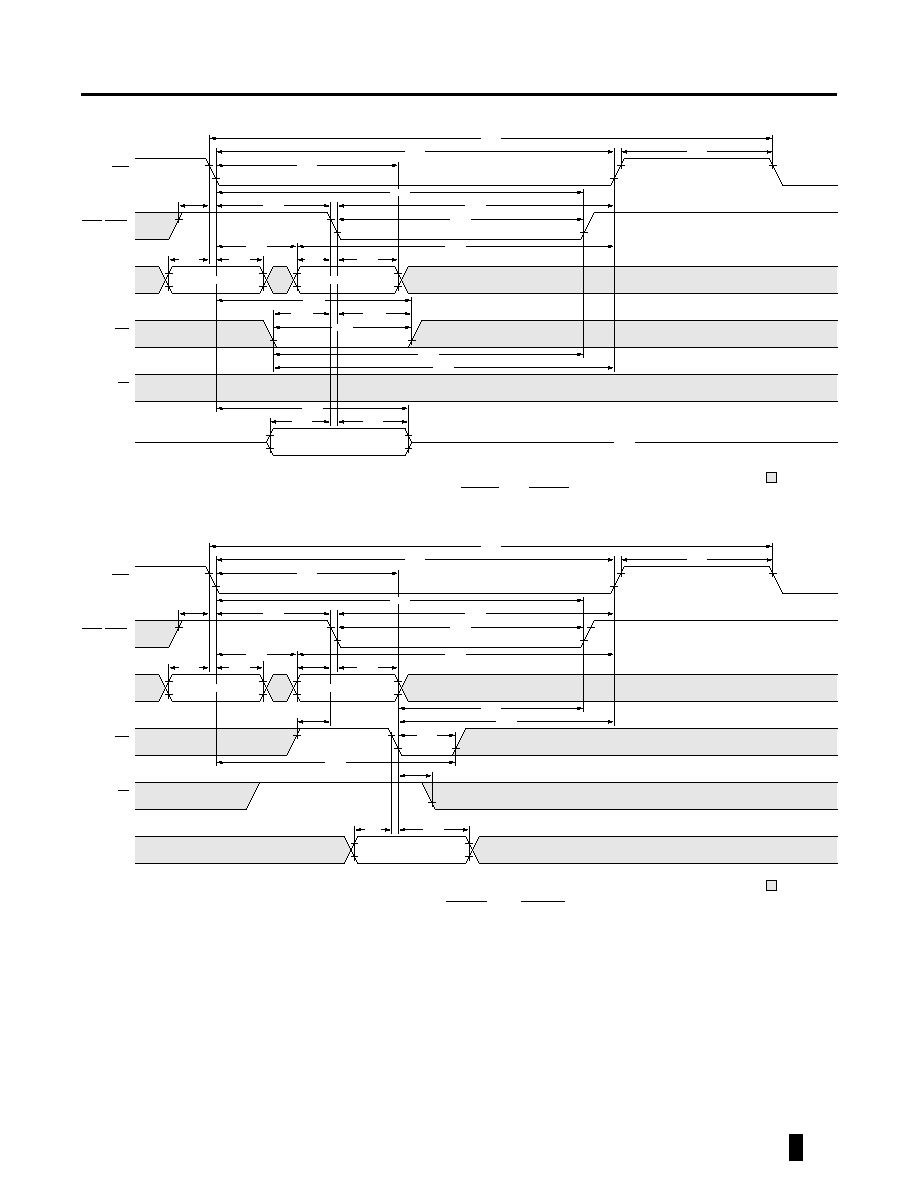

Figure 2. Read Cycle (RAS Output Control)

Don't Care

RAS

t

RC

t

RAS

t

RP

t

RSH

t

CAS

t

RCD

t

CRP

LCAS, UCAS

t

AR

t

RAL

t

RAD

t

CAH

t

RAH

t

ASR

t

ASC

A[8:0]

WE

OE

DQ

t

CSH

t

RCS

t

AA

t

RRH

t

RCH

t

OEA

t

ROH

t

CAC

t

OEZ

t

OFF

t

RAC

Hi-Z

ROW

COLUMN

VALID DATA

Figure 3. Read Cycle (CAS Output Control)

Don't Care

RAS

t

RC

t

RAS

t

RP

t

RSH

t

CAS

t

RCD

t

CRP

LCAS, UCAS

t

AR

t

RAL

t

RAD

t

CAH

t

RAH

t

ASR

t

ASC

A[8:0]

WE

OE

DQ

t

CSH

t

RCS

t

AA

t

RRH

t

OEA

t

ROH

t

CAC

t

OEZ

t

OFF

t

RAC

Hi-Z

VALID DATA

ROW

COLUMN

7

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

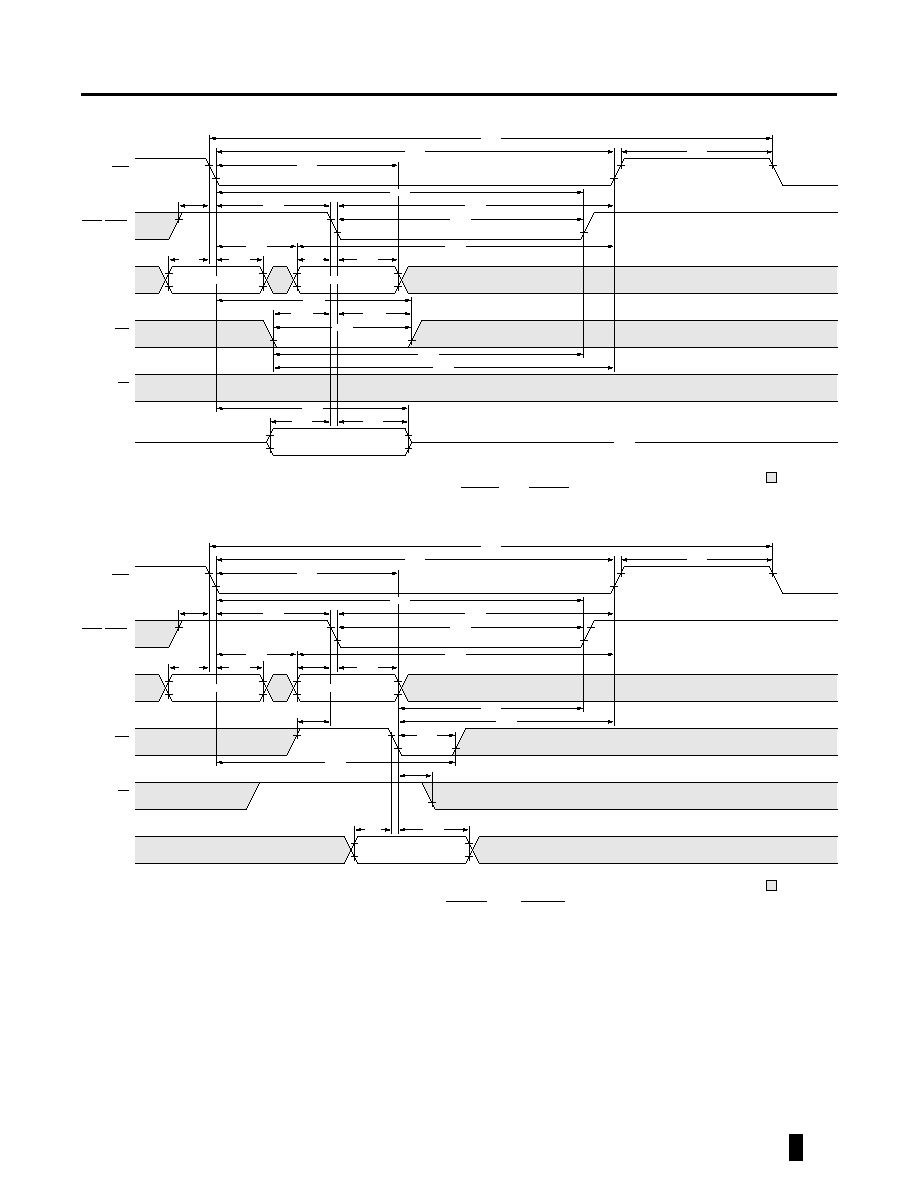

Figure 4. Early Write (LCAS and UCAS Active)

Don't Care

RAS

t

RC

t

RAS

t

RP

t

RSH

t

CAS

t

RCD

t

CRP

LCAS, UCAS

t

AR

t

RAL

t

RAD

t

CAH

t

RAH

t

ASR

t

ASC

A[8:0]

WE

OE

DQ

t

CSH

t

WP

t

WSC

t

WCH

t

WCR

t

CWL

t

RWL

t

DS

t

DH

t

DHR

Hi-Z

VALID DATA

COLUMN

ROW

RAS

Figure 5. Late Write (LCAS and UCAS Active)

t

RC

t

RAS

t

RP

t

RSH

t

CAS

t

RCD

t

CRP

LCAS, UCAS

t

AR

t

RAL

t

RAD

t

CAH

t

RAH

t

ASR

t

ASC

t

CWL

t

RWL

t

WP

t

RCS

t

WCR

t

OEH

t

DH

t

DS

A[8:0]

WE

OE

DQ

t

CSH

Don't Care

ROW

COLUMN

VALID DATA

8

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

RAS

Figure 6. Read Modify Write Cycle (LCAS and UCAS Active)

t

RMW

t

RAS

t

RP

t

CSH

t

RSH

t

CAS

t

RCD

t

CRP

LCAS, UCAS

t

AR

t

RAL

t

RAD

t

CAH

t

RAH

t

ASR

t

ASC

t

RCS

A[8:0]

WE

t

AWD

t

CWL

t

RWL

t

WP

t

OEH

t

RWD

t

CWD

t

DZO

t

OEA

t

OEZ

t

DS

t

DH

t

DZC

t

CAC

t

OED

t

RAC

DQ

OE

Don't Care

ROW

COLUMN

OUT

IN

Figure 7. Fast Page Mode Read Cycle with Extended Data Out

RAS

t

RC

t

RASP

t

CRP

t

RCD

t

CAS

t

CP

t

CAS

t

CP

t

CAS

t

CSH

t

PC

t

RSH

t

RP

t

ASR

t

RAH

t

ASC

t

CAH

t

ASC

t

CAH

t

ASC

t

CAH

t

RAD

t

RAL

t

AR

t

RCS

t

RCH

t

RRH

t

OEA

t

CAC

t

AA

HZ

t

CAC

t

COH

t

CAC

t

COH

t

OEZ

t

REZ

t

RAC

t

CPA

t

AA

t

AA

LCAS, UCAS

A[8:0]

WE

OE

DQ

t

CPA

Don't Care

ROW

COLUMN

COLUMN

COLUMN

VALID DATA

VALID DATA

VALID DATA

9

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

VALID

DATA

t

OEA

t

OEZ

t

RCH

t

RCS

t

CP

t

ASC

RAS

Figure 8. Fast Page Mode Read Hi-Z Operation

LCAS, UCAS

t

CRP

t

RASP

t

RC

t

RP

t

CSH

t

AR

t

RCD

t

CAS

t

HPC

t

CAS

t

CP

t

CAS

t

CP

t

CAS

t

RSH

t

CRP

t

RAD

t

CAH

t

CAH

t

CAH

t

CAH

t

RAL

t

RAH

t

ASR

t

ASC

t

ASC

t

ASC

t

RCS

t

RCH

t

RRH

t

WEP

t

RAC

t

CHO

t

OCH

t

OEP

t

OEP

t

CAC

t

CAC

t

AA

t

CAC

t

CPA

t

AA

t

CAC

t

AA

t

COH

t

OEZ

t

OEA

t

OEA

t

WEZ

t

AA

t

REZ

WE

OE

DQ

A[8:0]

Don't Care

ROW

COLUMN

VALID DATA

COLUMN

COLUMN

COLUMN

VALID DATA

VALID

DATA

VALID DATA

Figure 9. Fast Page Mode Early Write Cycle

RAS

t

RC

t

RASP

t

CRP

t

RCD

t

CAS

t

CP

t

CAS

t

CP

t

CAS

t

CSH

t

PC

t

RSH

t

RP

t

ASR

t

RAH

t

ASC

t

CAH

t

ASC

t

CAH

t

ASC

t

CAH

t

RAD

t

RAL

t

AR

LCAS, UCAS

A[8:0]

WE

OE

DQ

t

CWL

t

WCS

t

WCH

t

CWL

t

WCS

t

WP

t

WCH

t

WCS

t

WP

t

WCH

t

CWL

t

DS

t

DH

t

DS

t

DH

t

DS

t

DH

t

WP

Don't Care

ROW

COLUMN

COLUMN

COLUMN

INPUT DATA

INPUT DATA

INPUT DATA

10

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

t

ASC

t

CWL

t

CWL

Figure 10. Fast Page Mode Read Modify Write Cycle

RAS

t

RC

t

RASP

t

CRP

t

RCD

t

CAS

t

CP

t

RP

t

ASR

t

RAL

t

AR

A[8:0]

WE

OE

DQ

t

CP

t

CSH

t

RSH

t

CAS

t

CAS

t

PRMW

t

RAH

t

ASC

t

ASC

t

CAH

t

CAH

t

RAD

t

CAH

t

AWD

t

WP

t

CWD

t

RCS

t

WP

t

AWD

t

CWD

t

WP

t

CWL

t

AWD

t

CWD

t

OEA

t

OEZ

t

OEA

t

OEZ

t

OEA

t

OEZ

t

AA

t

DS

t

CAC

t

DH

t

AA

t

CAC

t

DS

t

DH

t

CAC

t

AA

t

DS

t

DH

Don't Care

LCAS, UCAS

ROW

COLUMN

COLUMN

COLUMN

OUT

OUT

OUT

IN

IN

IN

Figure 11. CAS-before-RAS Refresh Cycle

RAS

A[8:0]

WE

OE

DQ

t

RC

t

RAS

t

RP

t

RP

t

RPC

t

CSR

t

CHR

t

RPC

t

OFF

HZ

INHIBIT FALLING TRANSITION

Don't Care

LCAS, UCAS

11

G-LINK Technology

GLT41016-10E

May 1997 (Rev. 1)

Figure 12. Hidden Refresh Cycle

RAS

t

RC

t

RP

t

AR

A[8:0]

WE

OE

DQ

t

RAS

t

RAS

t

CRP

t

RCD

t

CHR

t

ASR

t

RAH

t

ASC

t

CAH

t

RAD

t

RAL

t

RSH

t

RRH

t

OEA

t

ROH

t

OEZ

t

AA

t

CAC

t

RAC

HZ

t

OFF

t

RCS

LCAS, UCAS

Don't Care

ROW

COLUMN

VALID DATA

Figure 13. RAS-Only Refresh Cycle

Don't Care

RAS

t

RC

t

RAS

t

RP

t

CRP

LCAS, UCAS

t

RAH

t

ASR

A[8:0]

DQ

Hi-Z

t

RPC

WE, OE

ROW

© 2001 G-LINK Technology

All rights reserved. No part of this document may be copied or reproduced in any form or by any means or transferred to any third party without the prior written consent of

G-LINK Technology.

Circuit diagrams utilizing G-LINK products are included as a means of illustrating typical semiconductor applications. Complete information sufficient for design purposes is

not necessarily given.

G-LINK Technology reserves the right to change products or specifications without notice.

The information contained in this document does not convey any license under copyrights, patent rights or trademarks claimed and owned by G-LINK or its subsidiaries.

G-LINK assumes no liability for G-LINK applications assistance, customer's product design, or infringement of patents arising from use of semiconductor devices in such

systems' designs. Nor does G-LINK warrant or represent that any patent right, copyright, or other intellectual property right of G-LINK covering or relating to any combination,

machine, or process in which such semiconductor devices might be or are used.

G-LINK Technology's products are not authorized for use in life support devices or systems. Life support devices or systems are device or systems which are: a) intended for

surgical implant into the human body and b) designed to support or sustain life; and when properly used according to label instructions, can reasonably be expected to cause

significant injury to the user in the event of failure.

The information contained in this document is believed to be entirely accurate. However, G-LINK Technology assumes no responsibility for inaccuracies.

GLT41016-10E

www.glinktech.com

G-LINK Technology

1753 South Main Street

Milpitas, California, 95035, USA

TEL: 408-240-1380 ∑ FAX: 408-240-1385

G-LINK Technology Corporation, Taiwan

6F, No. 24-2, Industry E. Rd. IV

Science-Based Industrial Park

Hsin Chu, Taiwan, R.O.C.

TEL: 03-578-2833 ∑ FAX: 03-578-5820

Printed in USA