G -LINK

GLT6200L16

Ultra Low Power 128k x 16 CMOS SRAM

Aug 2001(Rev. 2.6)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 1 -

Features :

Description :

Low-power consumption.

-active: 30mA Icc at 55ns.

-stand by :

10

µ

A (CMOS input / output , LL)

2

µ

A (CMOS input / output, SL)

Single +2.7V to 3.6V power supply.

Equal access and cycle time.

55\70\85 ns access time.

Tri-state output.

Automatic power-down when

deselected.

Multiple center power and ground pins

for improved noise immunity.

Individual byte controls for both read

and write cycles.

Industrial grade (-40

∞

C ~ 85

∞

C)

available.

Available in 48-fpBGA/44L TSOPII.

The GLT6200L16 is a low power CMOS Static

RAM organized as 131,072 words by 16 bits. Easy

memory expansion is provided by an active LOW

CE1

and

OE

pin.

This device has an automatic power ≠ down

mode feature when deselected. Separate Byte

Enable controls (

BLE

and

BHE

) allow individual

bytes to be accessed.

BLE

controls the lower bits

I/O0 ≠ I/O7.

BHE

controls the upper bits I/O8 ≠

I/O15.

Writing to these devices is performed by taking

Chip Enable

CE1

with Write Enable

WE

and byte

Enable (

BLE

/

BHE )

Low

Reading from the device is performed by taking

Chip Enable

CE1

with Output enable

OE

and byte

Enable (

BLE

/

BHE

) Low while Write Enable

WE

are held HIGH.

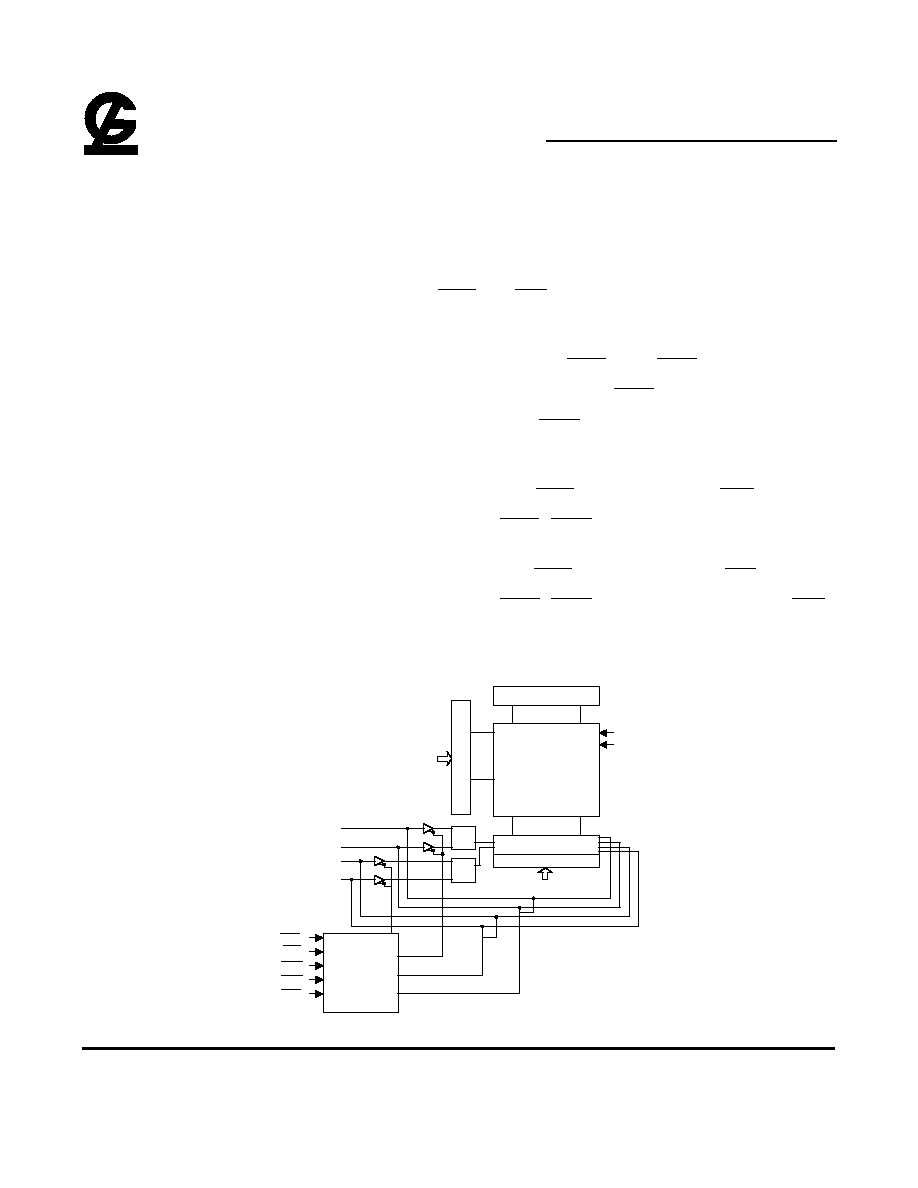

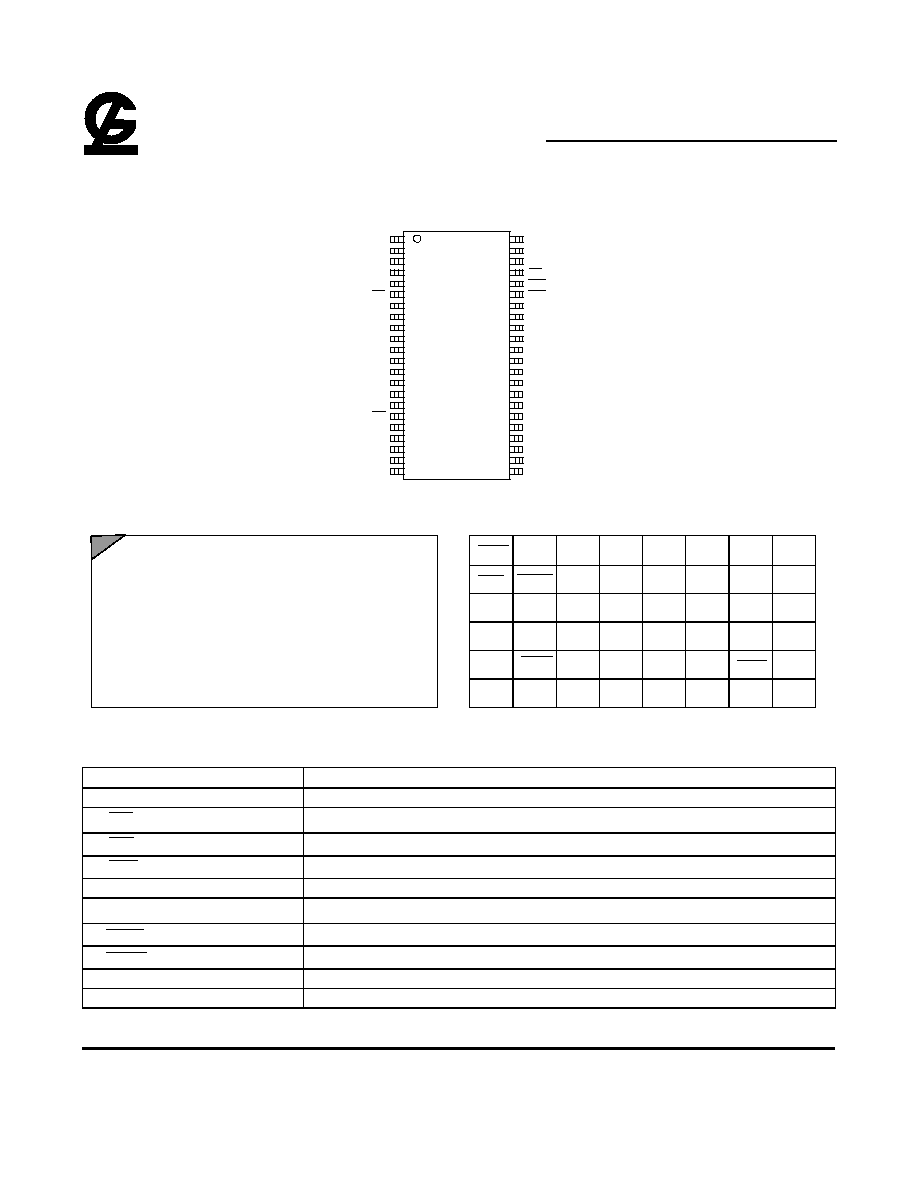

Function Block Diagram :

Row Select

Memory Array

1024 x 2048

Pre-Charge Circuit

I/O Circuit

Column Select

Data

Circuit

Data

Circuit

Vcc

Vss

WE

OE

BLE

BHE

CE1

I/O

8

- I/O

15

I/O

0

- I/O

7

Control

Logic

Column Address

Row Address

G -LINK

GLT6200L16

Ultra Low Power 128k x 16 CMOS SRAM

Aug 2001(Rev. 2.6)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 2 -

BHE

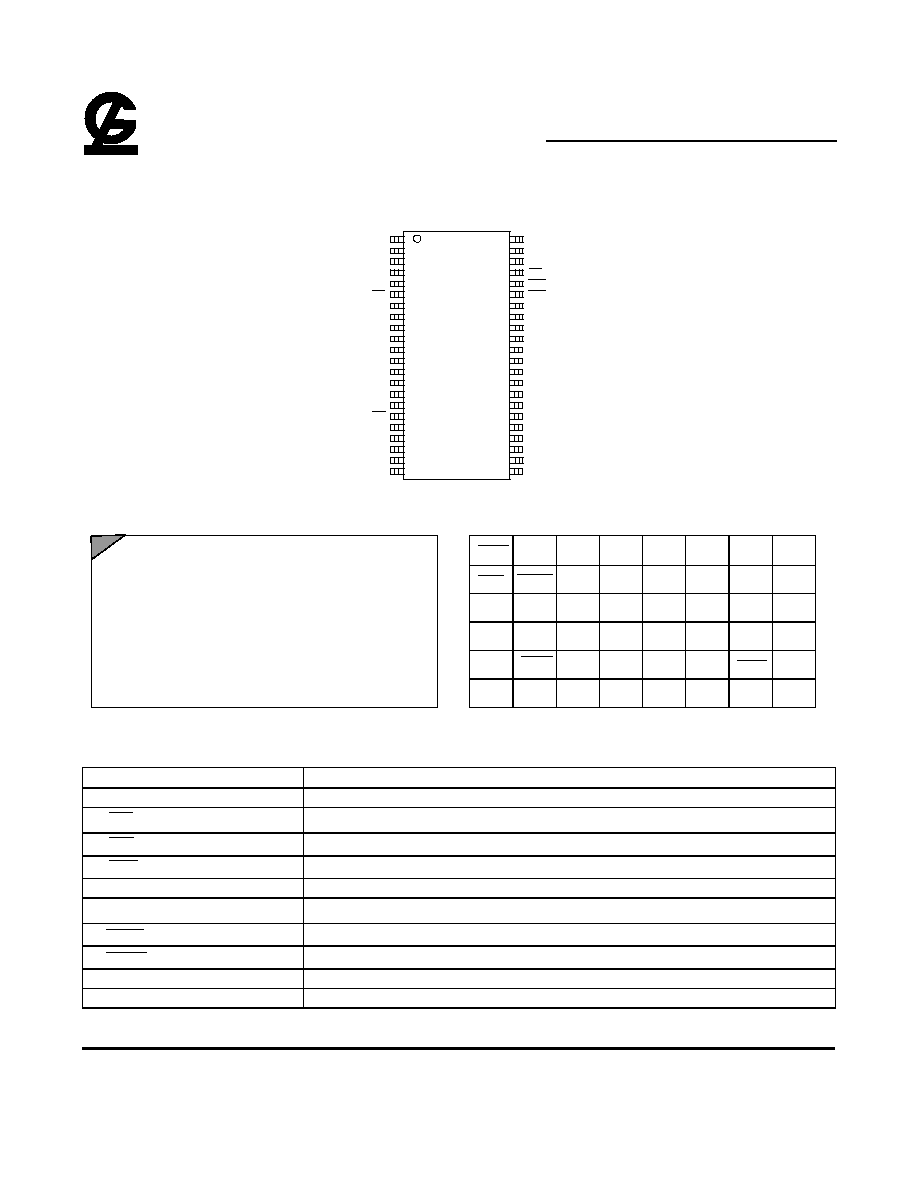

Pin Configurations :

GLT6200L16

A

4

1

2

3

4

5

6

7

9

10

12

13

14

Vcc

8

15

16

17

18

19

20

21

24

25

26

27

28

29

30

31

32

33

35

36

37

38

39

40

41

42

43

44

CE1

I/O

0

OE

BLE

22

23

34

11

Vcc

WE

A

3

A

2

A

1

A

0

I/O

1

I/O

2

I/O

3

Vss

I/O

4

I/O

5

I/O

6

I/O

7

A

16

A

15

A

14

A

13

A

11

A

10

A

9

A

8

NC

I/O

8

I/O

9

I/O

10

I/O

11

Vss

I/O

12

I/O

13

I/O

14

I/O

15

BHE

A

7

A6

A

5

A

12

NC

48 Ball fpBGA :

A

B

C

D

E

F

G

H

A

B

C

D

E

F

G

H

° °

°

°

°

°

°

°

1

BLE

I/O8

I/O9

Vss

Vcc

I/O14

I/O15

NC

° °

°

°

°

°

°

°

2

OE

I/O10

I/O11

I/O12

I/O13

NC

A8

°

°

° °

° °

°

°

3

A0

A3

A5

NC

NC

A14

A12

A9

°

°

° °

° °

°

°

4

A1

A4

A6

A7

A16

A15

A13

A10

°

°

° °

° °

°

°

5

A2

CE1 I/O1

I/O3

I/O4

I/O5

WE

A11

°

°

° °

° °

°

°

6

NC

I/O0

I/O2

Vcc

Vss

I/O6

I/O7

NC

Bottom View

Bottom View

Note

:

NC means no Ball.

Pin Descriptions:

Name

Function

A

0

≠ A

16

Address Inputs

CE

1

Chip Enable Input

OE

Output Enable Input

WE

Write Enable Input

I/O

0

≠ I/O

15

Data Input and Data Output

V

CC

2.7V~3.6V Power Supply

BLE

Lower Byte Enable Input ( I/O

0

to I/O

7

)

BHE

Higher Byte Enable Input ( I/O

8

to I/O

15

)

GND

Ground

NC

No Connection

G -LINK

GLT6200L16

Ultra Low Power 128k x 16 CMOS SRAM

Aug 2001(Rev. 2.6)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 3 -

Truth Table:

CE1

OE

WE

BLE BHE

I/O0-I/O7

I/O8-I/O15

Power

Mode

H

X

X

X

X

High-Z

High-Z

Standby

Deselected

X

X

X

H

H

High-Z

High-Z

Standby

Deselected

L

H

H

L

X

High-Z

High-Z

Active

Output Disabled

L

H

H

X

L

High-Z

High-Z

Active

Output Disabled

L

L

H

L

H

Data Out

High-Z

Active

Lower Byte Read

L

L

H

H

L

High-Z

Data Out

Active

Upper Byte Read

L

L

H

L

L

Data Out

Data Out

Active

Word Read

L

X

L

L

H

Data In

High-Z

Active

Lower Byte Write

L

X

L

H

L

High-Z

Data In

Active

Upper Byte Write

L

X

L

L

L

Data In

Data In

Active

Word Write

Note ; X means don care. (Must be low or high state).

Absolute Maximum Ratings*

Parameter

Symbol

Minimum

Maximum

Unit

Voltage on Any Pin Relative to Gnd

Vt

-0.5

Vcc + 0.3

V

Power Dissipation

P

T

-

1.0

W

Storage Temperature (Plastic)

Tstg

-55

+150

∞

C

Temperature Under Bias

Tbias

-25

+85

∞

C

*Note : Stresses greater than those listed above Absolute Maximum Ratings may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at these or any conditions outside those indicated

in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect reliability.

Recommended Operating Conditions ( TA = -25

∞

C to 85

∞

C )

Parameter

Symbol

Min

Typ

Max

Unit

V

CC

2.7

3

3.6

V

Supply Voltage

Gnd

0.0

0.0

0.0

V

V

IH

2.2

-

V

CC

+0.2

V

Input Voltage

V

IL

-0.5*

-

0.6

V

* V

IL

min = -2.0V for pulse width less than t

RC

/2.

G -LINK

GLT6200L16

Ultra Low Power 128k x 16 CMOS SRAM

Aug 2001(Rev. 2.6)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 4 -

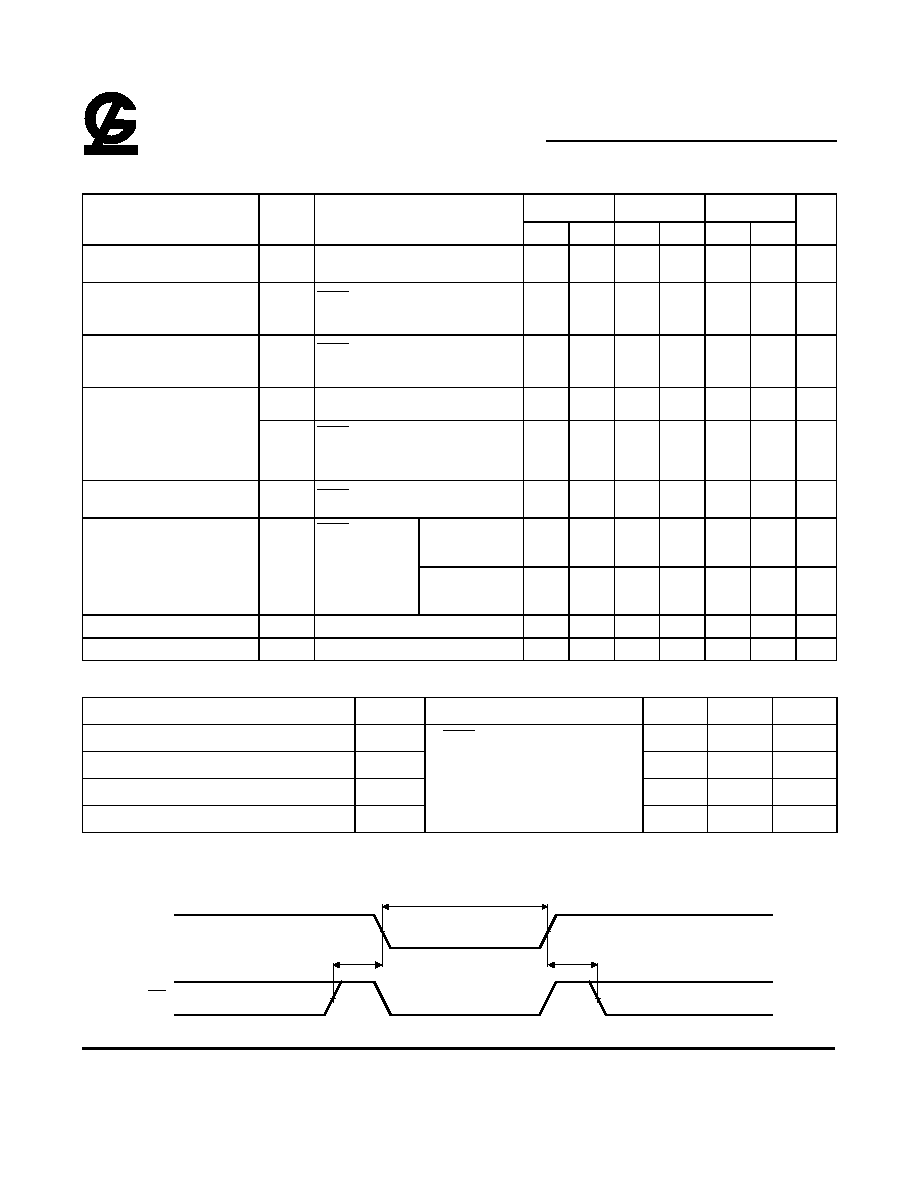

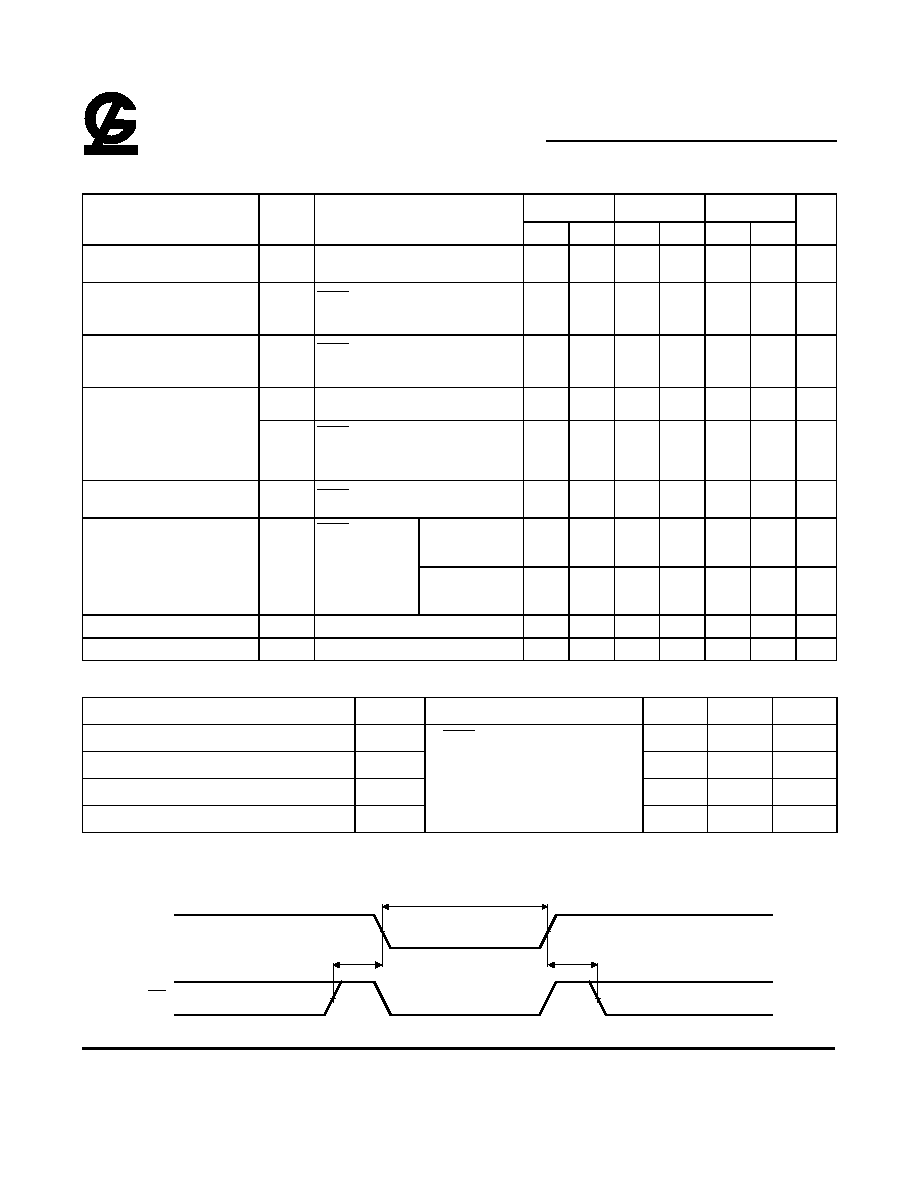

DC Operating Characteristics

( Vcc=2.7 to 3.6V, T

A

= -25

∞

C to 85

∞

C )

55

70

85

Unit

Parameter

Sym.

Test Conditions

Min

Max

Min

Max

Min

Max

Input Leakage Current

I

LI

V

CC

= Max,

Vin = Gnd to V

CC

1

1

1

µ

A

Output Leakage

Current

I

LO

CE1

=V

IH

or V

CC

= Max,

V

OUT

= Gnd to V

CC

1

1

1

µ

A

Operating Power

Supply Current

I

CC

CE1

=V

IL

,V

IN

=V

IH

or V

IL

, I

OUT

=0

5

5

5

mA

I

CC1

I

OUT

= 0mA,

Min Cycle, 100% Duty

30

30

25

mA

Average Operating

Current

I

CC2

CE1

0.2V

I

OUT

= 0mA,

Cycle Time=1

µ

s, 100% = Duty

3

3

3

mA

Standby Power Supply

Current(TTL Level)

I

SB

CE1

=V

IH

0.5

0.5

0.5

mA

GLT6200L16LL

10

10

10

µ

A

Standby Power Supply

Current (CMOS Level)

I

SB1

CE1

V

CC

-

0.2V

V

IN

0.2V or

V

IN

V

CC

-0.2V

GLT6200L16SL

2

2

2

µ

A

Output Low Voltage

V

OL

I

OL

= 2.1 mA

0.4

0.4

0.4

V

Output High Voltage

V

OH

I

OH

= -1 mA

2.4

2.4

2.4

V

Data Retention

Parameter

Sym.

Test Conditions

Min.

Max.

Unit

V

CC

for Data retention

V

DR

1.0

-

V

Data Retention Current

I

CCDR

-

2

µ

A

Chip Deselect to Data Retention Time

t

CDR

0

-

ns

Operating Recovery Time

(2)

t

R

CE1

V

CC

-0.2V

V

IN

V

CC

-0.2V or

V

IN

0.2V

t

RC

-

ns

Data Retention Waveform

(TA = -25

∞

C to +85

∞

C)

Data Retention Mode

Vcc

CE1

V

DR

V

DR >= 1.0V

t

R

t

CDR

2.7V

2.7V

V

IH

V

IH

G -LINK

GLT6200L16

Ultra Low Power 128k x 16 CMOS SRAM

Aug 2001(Rev. 2.6)

G-Link Technology Corporation

2701 Northwestern Parkway

Santa Clara, CA 95051, U.S.A.

G-Link Technology Corporation, Taiwan

6F No. 24-2, Industry E. RD. IV, Science Based

Industrial Park, Hsin Chu, Taiwan.

- 5 -

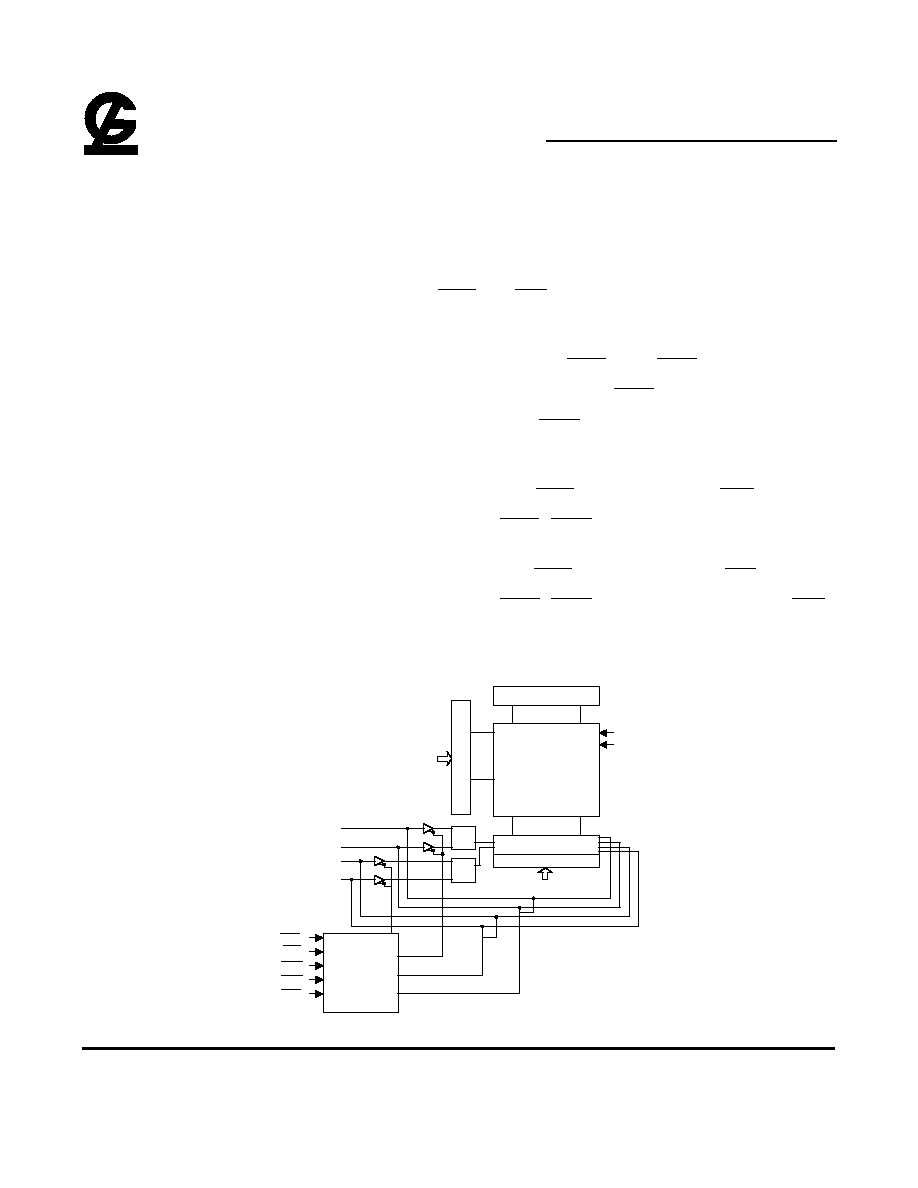

AC Test Conditions

AC Test Loads and Waveforms

C

L

*

TTL

Output Load Condition

*Including Scope and Jig Capacitance

C

L

= 30pf + 1TTL Load

Read Cycle

(9)

( Vcc=2.7V to 3.6V, T

A

= -25

∞

C to 85

∞

C )

55

70

85

Parameter

Symbol

Min

Max

Min

Max

Min

Max

Unit

Note

Read Cycle Time

t

RC

55

70

85

ns

Address Access Time

t

AA

55

70

85

ns

Chip Enable Access Time

t

ACE

55

70

85

ns

Output Enable Access Time

t

OE

35

40

40

ns

Output Hold from address Change

t

OH

10

10

10

ns

Chip Enable to Output in Low-Z

t

LZ

10

10

10

ns

4,5

Chip Disable to Output in High-Z

t

HZ

25

30

35

ns

3,4,5

Output Enable to Output in Low-Z

t

OLZ

5

5

5

ns

Output Disable to Output in High-Z

t

OHZ

25

25

30

ns

BLE , BHE Enable to Output in Low-Z

t

BLZ

5

5

5

ns

4,5

BLE , BHE Disable to Output in High-Z

t

BHZ

25

25

30

ns

3,4,5

BLE , BHE Access Time

t

BA

35

40

85

ns

Timing Waveform of Read Cycle 1 (Address Controlled)

D

OUT

t

RC

Address

t

OH

t

AA

Previous Data Valid

Data Valid

Input Pulse Levels

0.4V to 2.4V

Input Rise and Fall Time

Input and Output Timing

Reference Level

5 ns

1.4V