SiRF Chips and Software

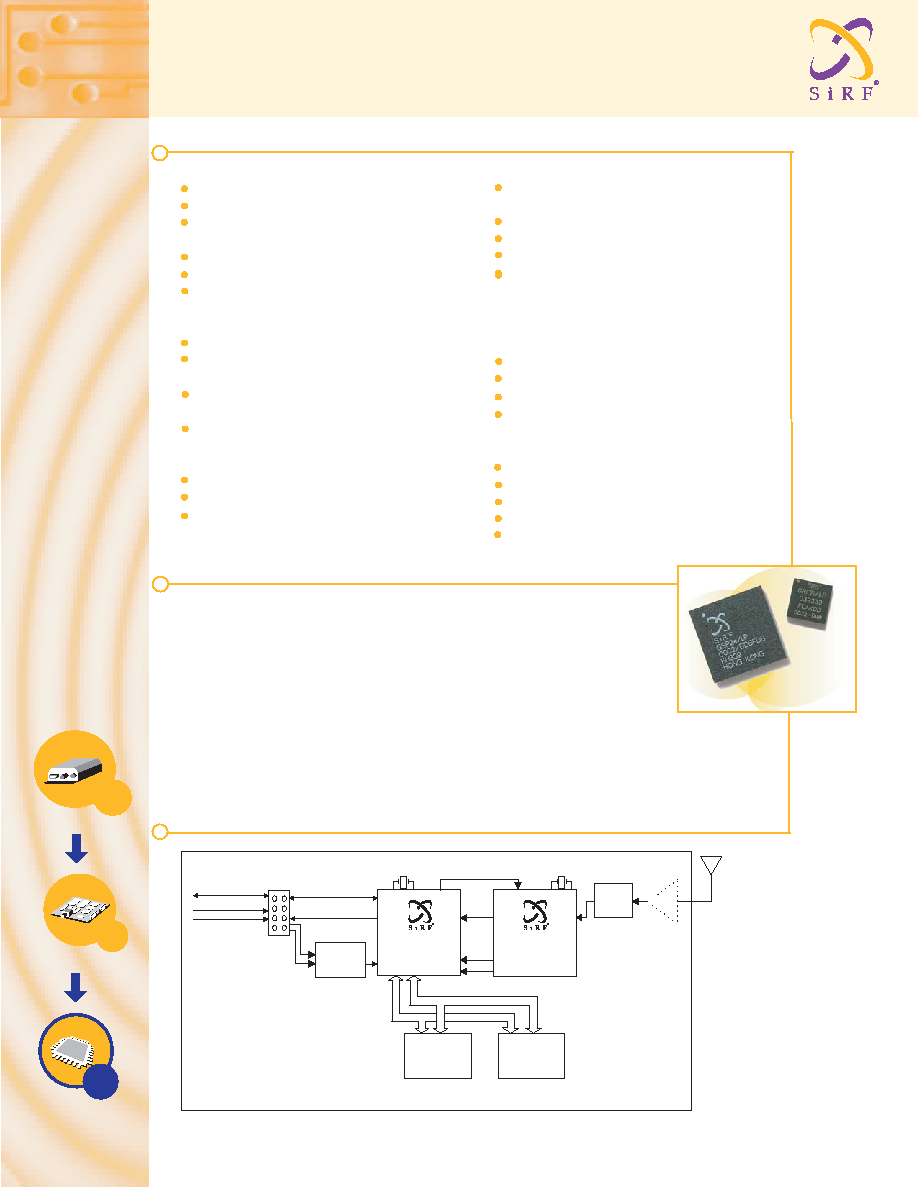

SiRFstar

IIe/LP BLOCK DIAGRAM

SiRFstar

IIe/LP Chip Set

A Low Power GPS Chip Set for Consumer Products

SiRFstar

II ARCHITECTURE

SiRFstarIIe/LP architecture sets the standard for high volume GPS performance. The

SiRFstarIIe/LP still uses 1,920 corrolators and 12 channels to provide fast acquisition and re-

aquisition times, while keeping peak current to under 65 mA. TricklePower extends battery

life even further by reducing average current to under 20mA. Now superior performance

features like SingleSat, SnapLock, and FoliageLock are available using less power.

The chipset consists of the GSP2e/LP, a highly integrated digital chip with 40 MIPS of

processing power and the GRF2i/LP, a lower power version of the GRF2i integrated front end.

The GSW2 software completes the package providing flexible system architechture for stand-

alone GPS based products. The SiRFstarIIe/LP also supports SiRF's high sensitivity stand

alone software, SiRFXtrac and mult-mode software,SiRFLoc. When low power, low cost, and

high performance matter SiRFstarIIe/LP is the best solution.

ARCHITECTURE HIGHLIGHTS

Industry Leading GPS Performance

Builds on high performance SiRFstar

IIe

Architecture supports user task integration

Signal acquisition using 1920 time/frequency

search channels

SBAS (WAAS and EGNOS), and DGPS support

Multipath-mitigation hardware

Cold Start under 45 seconds

Low Power

Under 175 mW at full power

TricklePower

TM

mode reduces power to under

60 mW

Adaptive TricklePower intelligently switches between

full and TricklePower.

Push to fix reduces power by as much as 98%

Maximizes GPS Position Availability

SingleSat

TM

updates in reduced visibility

Superior urban canyon performance

FoliageLock

TM

for weak signal tracking

FAMILY HIGHLIGHTS

GSP2e/LP - Flexible Digital IC

Microprocessor throughput measured at

up to 40 MIPS

8k of cache for improved throughput

On-chip 1Mb SRAM for GPS navigation

Integrated high-precision Real-Time Clock

Extensive GPS receiver peripherals

2 UARTS, high speed serial bus,

battery backed SRAM, >40 GPIO,

GRF2i/LP - Low Power RFIC

On-chip VCO and reference oscillator

Integrated LNA

Uses less than 30 mA's of current

Simplified digital interface

GSW2 Modular Software

Easily integrated into existing systems

95% CPU throughput available for user tasks

Tunable performance in all applications

Robust development environment

Compatible with SiRFloc and SiRFXtrac

1

3

Evaluate

2

Develop

Build

2-Bit

DATA BUS

(Optional)

RTC XTAL

AGC

GPS

Antenna

Input

RAM

(Optional)

ROM

GPS

CLKS

RF

Filter

LNA

GSP2e/LP

GRF2i/LP

Reset

Controller

REF XTAL

ADDRESS BUS

Serial Data

Timemark

Serial Data

Power

Battery

SiRF's technology is protected by U.S. and foreign patents pending and issued. SiRF and the SiRF logo are registered trademarks of SiRF Technology, Inc. SiRFstar, SiRF Powered, SnapLock, Foliage Lock,

TricklePower, SingleSat, SiRFLoc, SiRFDRive, SnapStart, Push-to-Fix, SiRFNav, and SiRFXtrac are trademarks of SiRF Technology, Inc. Other trademarks are property of respective companies.

February 2003

Rev. 1.1

APPLICATIONS

The SiRFstar

IIe/LP is a flexible low-power GPS chip set that integrates

into a postage-stamp sized receiver. It works well where GPS is the

main function such as handheld GPS, marine GPS, or personal locators

or where the design calls for stand-alone GPS functionality such as GPS

integrated into the batteryback of a cell phone or in an add on compact

flash card. The excess processing power can be used for user tasks

such as running an LCD or controlling an Automatic Vehicle Location

module.

For more information, contact your SiRF representative, call our sales force on

+1 (408) 467-0410, or visit us at www.sirf.com.

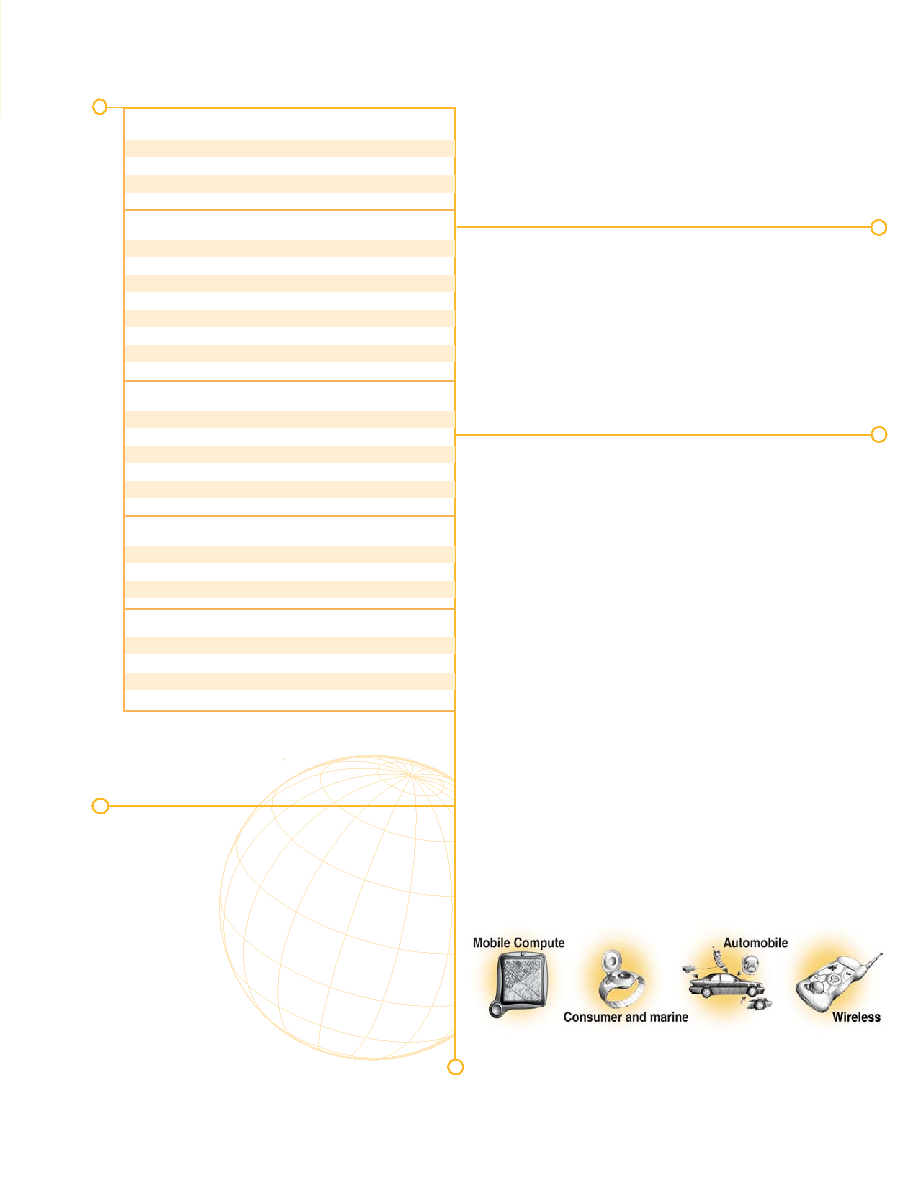

CHIP ORDERING CONFIGURATION

RF CHIP PACKAGES

DIGITAL CHIP PACKAGES

ADDITIONAL SOFTWARE OPTIONS

Chip Name

SiRFstar

II GRF2i/LP

SiRFstar

II GRF2i/LP (QFN)

Chip PN

GRF2I/LP-0210

GRF2I/LP-0214

Package

LQFP, 48 pin

(LPCC), 32 pin

Chip Name

SiRFstar

II GSP2e/LP

SiRFstar

II GSP2e/LP

SiRFstar

II GSP2e/LP

Chip PN

GSP2E/LP-7450

GSP2E/LP-7451

GSP2E/LP-7460

Package

TQFP, 16-bit, 100 pin

BGA, 16-bit, 144 pin

LQFP, 32-bit, 144 pin

SiRF California

+1 (408) 467-0410

sales@sirf.com

SiRF Texas

Central U.S.

+1 (972) 239-6988

jdaniels@sirf.com

SiRF United Kingdom

+44 1344 668390

aellis@sirf.com

SiRF France

+33 3 82 86 04 15

rocky@sirf.com

SiRF Europe

+49 81 529932-90

peterz@sirf.com

SiRF Taiwan

+886 2 2723 7853

tomlin@sirf.com

WORLDWIDE SALES OFFICES

SiRFXtrac (High Sensitivity stand alone software)

SiRFLoc (High Sensitivity multimode software)

Position Accuracy

Autonomous

WAAS

Beacon DGPS

Receiver

Tracking

Channels

Max. Update Rate

Sensitivity

Max. Altitude

Max. Velocity

Protocol Support

<10m

<5m

<2.5m

L1, CA code

12

10Hz

-172dBW

<60,000

ft

<1,000 knots

NMEA, SiRF Binary

Acquisition

Reacquisition Time

SnapStart

Hot Start

Warm Start

Cold Start

Power

Full Power (S2AM Module)

TricklePower (1Hz)

Voltage

100msec

<3sec

<8sec

<38sec

<45sec

<175mW

<60mW

2.7-3.3V (5V I/O capable)

Processor

Processor Type

ARM7/TDMI

Processor Speeds

6MHz, 12.5MHz, 25MHz, 49MHZ

Data

Bus

16 Bit or 32 Bit

Ports

>40 GPIO

Specifications above are for GSW2

TECHNICAL SPECIFICATIONS