HD74HC75

Quad. Bistable Latches

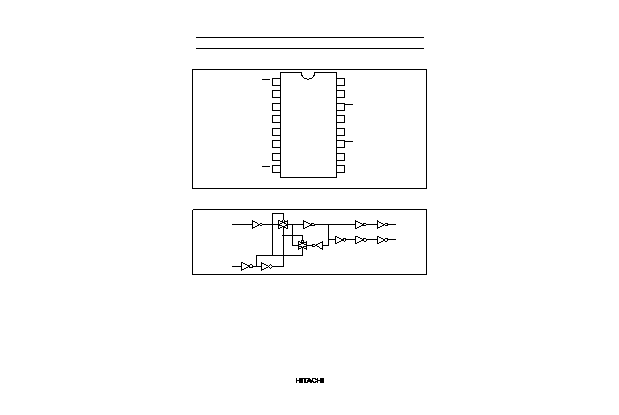

Description

This latch is ideally suited for use as temporary storage for binary information processing, input/output, and

indicator units. Information present at the data (D) input is transferred to the Q output when the latch

enable (LE) is high. The Q output will follow the data input as long as the enable remains high. when the

enable goes low, the information that was present at the data input at the time the transition occurred is

retained at thte Q output unit the enable is permitted to go high again.

Features

·

High Speed Operation: t

pd

(D to Q) = 12.5 ns typ (C

L

= 50 pF)

·

High Output Current: Fanout of 10 LSTTL Loads

·

Wide Operating Voltage: V

CC

= 2 to 6 V

·

Low Input Current: 1 µA max

·

Low Quiescent Supply Current: I

CC

(static) = 2 µA max (Ta = 25°C)

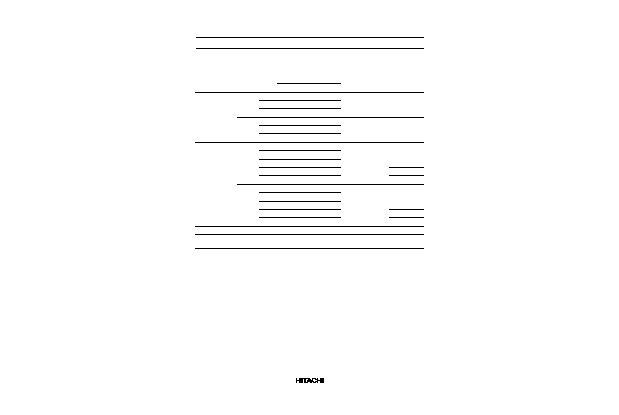

Function Table

Inputs

Outputs

D

Latch Enable

Q

Q

L

H

L

H

H

H

H

L

X

L

Q

0

Q

0