IBM Packet Routing Switch PRS28.4G

Version 1.7

Datasheet

�

Copyright and Disclaimer

Copyright International Business Machines Corporation 1999, 2000, 2001.

All Rights Reserved

Printed in the United States of America February 2001

The following are trademarks of

International Business Machines Corporation in the United States, or other coun-

tries, or both.

IBM

IBM logo

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this docu-

ment are NOT intended for use in implantation or other life support applications where malfunction may result in injury

or death to persons. The information contained in this document does not affect or change IBM's product specifications

or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellec-

tual property rights of IBM or third parties. All information contained in this document was obtained in specific environ-

ments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS.

In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this

document.

IBM Microelectronics Division

1580 Route 52, Bldg. 504

Hopewell Junction, NY 12533-6351

The IBM home page can be found at http://www.ibm.com

The IBM Microelectronics Division home page can be found at http://www.chips.ibm.com

prs28_title.04.fm

February 6, 2001

�

PRS28.4G

IBM Packet Routing Switch

prs28.04TOC.fm

February 6, 2001

Page 3 of 131

Contents

List of Figures ................................................................................................................ 7

List of Tables .................................................................................................................. 9

1. General Information .................................................................................................. 11

1.1 Features ......................................................................................................................................... 11

1.2 Description .................................................................................................................................... 11

1.3 Ordering Information .................................................................................................................... 12

1.4 Conventions .................................................................................................................................. 12

2. Architecture ............................................................................................................... 15

2.1 Functional Island ........................................................................................................................... 16

2.1.1 Sizing ..................................................................................................................................... 16

2.1.2 Output Queuing and Priorities ............................................................................................... 16

2.1.3 Flow Control .......................................................................................................................... 17

2.1.4 Multicast ................................................................................................................................ 17

2.1.5 Control Packets ..................................................................................................................... 17

2.1.6 Incoming Flow Process ......................................................................................................... 17

2.1.7 Incoming Flow Control ........................................................................................................... 17

2.1.8 Outgoing Flow Process ......................................................................................................... 18

2.1.9 Outgoing Flow Control ........................................................................................................... 18

2.1.10 Signaling .............................................................................................................................. 19

2.1.11 Internal Features ................................................................................................................. 19

2.1.12 Miscellaneous ...................................................................................................................... 20

2.2 Expansion Modes .......................................................................................................................... 22

2.2.1 Speed Expansion .................................................................................................................. 22

2.2.2 Port Expansion ...................................................................................................................... 23

3. Functional Description ............................................................................................. 25

3.1 Logical Interface ............................................................................................................................ 25

3.1.1 Physical Interface .................................................................................................................. 26

3.1.2 Packet Type ........................................................................................................................... 27

3.2 Header Format ............................................................................................................................... 30

3.2.1 Header Byte H0 - Packet Qualifier ........................................................................................ 30

3.2.2 Header Byte H1 and H2 ........................................................................................................ 32

3.2.3 Idle Packet Trailer Byte T ...................................................................................................... 33

3.3 Packet Reception .......................................................................................................................... 33

3.3.1 Master Input Port Operation .................................................................................................. 33

3.3.2 Slave Input Port Operation .................................................................................................... 34

3.3.3 Parity and CRC Errors ........................................................................................................... 34

3.3.4 Address Insertion ................................................................................................................... 35

3.4 Input Flow Control ........................................................................................................................ 35

3.4.1 Memory Threshold Exceeded Condition ............................................................................... 35

3.4.2 Programming the Memory Full Thresholds ........................................................................... 35

3.4.3 Output Queue Threshold Exceeded Condition ...................................................................... 36

3.4.4 Packet Reception Fairness .................................................................................................... 36

PRS28.4G

IBM Packet Routing Switch

Page 4 of 131

prs28.04TOC.fm

February 6, 2001

3.5 Output Queue Grant Signaling ..................................................................................................... 37

3.5.1 Adapter Transmission Rules .................................................................................................. 38

3.5.2 Flow Control Error .................................................................................................................. 38

3.6 Output Queues and Output Queue Priorities ............................................................................. 39

3.7 Shared Memory ............................................................................................................................. 39

3.7.1 Organization ........................................................................................................................... 39

3.7.2 Shared Memory Access by Local Processor ......................................................................... 39

3.8 Packet Transmission .................................................................................................................... 40

3.8.1 Output Port Servicing ............................................................................................................. 40

3.8.2 Idle Packet Transmission ....................................................................................................... 41

3.9 Send Grant ..................................................................................................................................... 42

3.10 Receive Filter ............................................................................................................................... 42

3.11 Port Disabling .............................................................................................................................. 43

3.12 Address Manager and Address Corruption .............................................................................. 43

3.13 Control Packets ........................................................................................................................... 43

3.13.1 Control Packet Reception .................................................................................................... 43

3.13.2 Control Packet Transmission ............................................................................................... 44

3.14 Speed Expansion ........................................................................................................................ 44

3.14.1 External Speed Expansion ................................................................................................... 44

3.14.2 Internal Speed Expansion .................................................................................................... 44

3.14.3 Packet Reception Window for Speed Expansion ................................................................. 45

3.14.4 Synchronization of Slave Device with Master Device .......................................................... 45

3.14.5 Master Slave Address Communication ................................................................................ 45

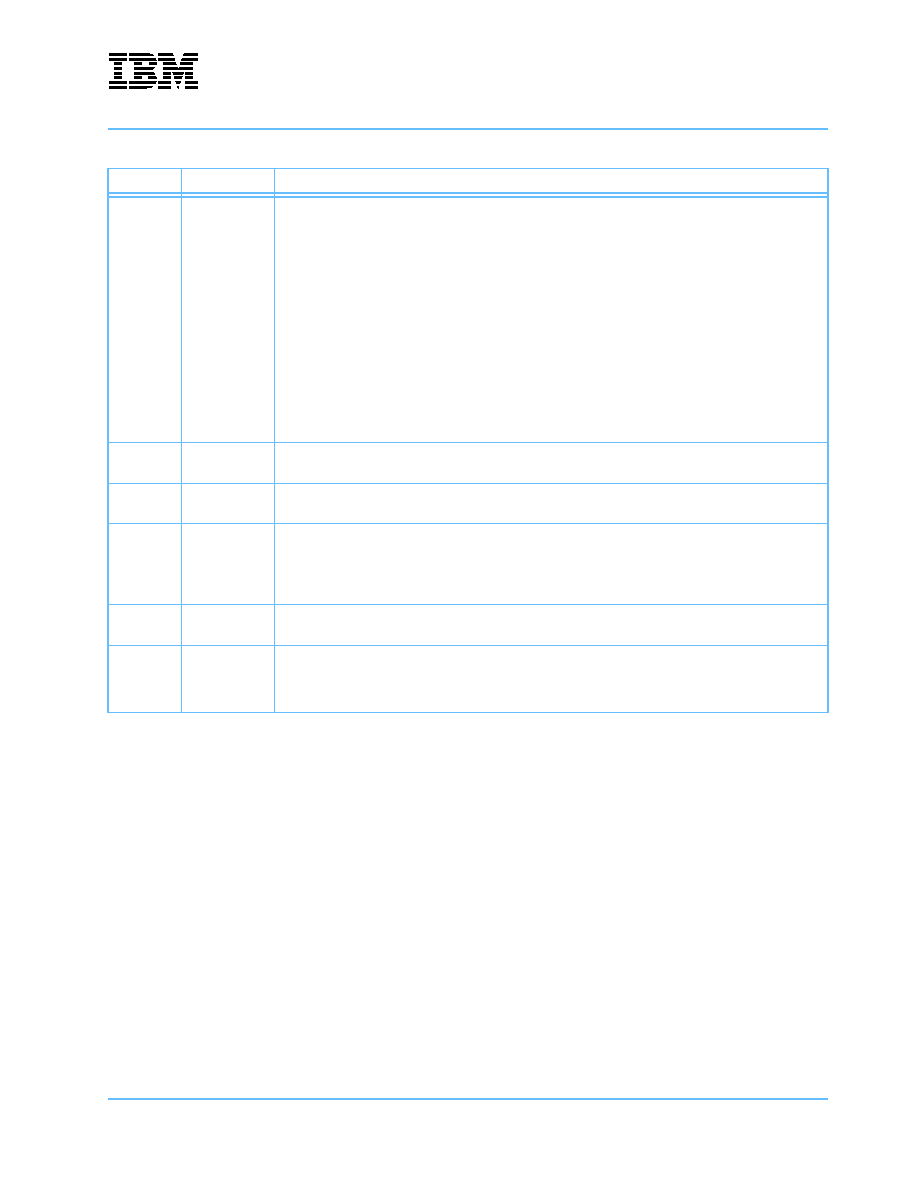

4. Programming Interface and Internal Registers ...................................................... 47

4.1 OCM Instruction/Status Mode ...................................................................................................... 47

4.1.1 OCM Instruction Register ....................................................................................................... 47

4.1.2 OCM Instruction Set ............................................................................................................... 47

4.1.3 OCM Response Register ....................................................................................................... 49

4.1.4 OCM Error Checking .............................................................................................................. 49

4.1.5 Operational Protocol .............................................................................................................. 50

4.2 OCM Scan Mode ............................................................................................................................ 50

4.2.1 Operational Protocol .............................................................................................................. 50

4.2.2 Scan String Access from OCM .............................................................................................. 51

4.3 Built In Self Test (BIST) ................................................................................................................. 51

4.3.1 Pseudo-Random Pattern Generator (PRPG) ......................................................................... 51

4.3.2 Multiple Input Signature Register (MISR) .............................................................................. 51

4.3.3 BIST Execution ...................................................................................................................... 52

5. Internal Registers ...................................................................................................... 54

5.1 Status Register .............................................................................................................................. 54

5.2 Application Register Definitions .................................................................................................. 56

5.2.1 Indirect Access of Memory Data and Look-Up Table ............................................................ 57

5.2.2 Register Formats ................................................................................................................... 57

5.2.3 Mode Register ........................................................................................................................ 58

5.2.4 Configuration Register 0 ........................................................................................................ 59

5.2.5 Configuration Register 1 ........................................................................................................ 61

5.2.6 Port Enable Register .............................................................................................................. 62

5.2.7 Output Queue Threshold Register ......................................................................................... 63

PRS28.4G

IBM Packet Routing Switch

prs28.04TOC.fm

February 6, 2001

Page 5 of 131

5.2.8 Shared Memory Threshold Register 0 ................................................................................... 64

5.2.9 Shared Memory Threshold Register 1 ................................................................................... 65

5.2.10 Mask Register ...................................................................................................................... 66

5.2.11 Synchronization Status and Hunt Register .......................................................................... 67

5.2.12 Sync Packet Transmit Register ........................................................................................... 68

5.2.13 CRC Port ID Register .......................................................................................................... 69

5.2.14 CRC Error Counter .............................................................................................................. 70

5.2.15 NoSignal Register ................................................................................................................ 71

5.2.16 Flow Control Violation Port ID Register ............................................................................... 72

5.2.17 Miscellaneous Status Register ............................................................................................ 73

5.2.18 Output Queue Status Registers 0-3 .................................................................................... 74

5.2.19 Look-Up Tables and Memory Row ...................................................................................... 75

5.2.20 Table Pointer Register ......................................................................................................... 76

5.2.21 Table Data Register ............................................................................................................. 77

5.2.22 Memory Row Address Register ........................................................................................... 78

5.2.23 Command Register .............................................................................................................. 79

5.2.24 Control Packet Destination Register .................................................................................... 80

5.2.25 Bit Map Filter Register ......................................................................................................... 81

5.2.26 Yellow Packet Received Register ........................................................................................ 82

5.2.27 PLL Configuration Register ................................................................................................. 83

5.2.28 Processor Access Registers ................................................................................................ 84

5.2.29 Processor Address Register ................................................................................................ 84

5.2.30 Processor Data Register ..................................................................................................... 85

5.2.31 BIST Data Register .............................................................................................................. 86

5.2.32 BIST Control Register .......................................................................................................... 87

6. Reset, Initialization, and Operation ......................................................................... 88

6.1 Clock and PLL ............................................................................................................................... 88

6.1.1 Internal PLL ........................................................................................................................... 88

6.1.2 External PLL .......................................................................................................................... 88

6.2 Reset .............................................................................................................................................. 88

6.2.1 Power-On-Reset Sequence and Clock Start OCM Event ..................................................... 88

6.2.2 Flush Reset and OCM_RESET Command ........................................................................... 89

6.2.3 nTRST Primary Input Reset .................................................................................................. 89

6.3 Initialization ................................................................................................................................... 89

6.4 DASL Initialization and Operation ............................................................................................... 90

6.5 Control Packet Reception and Transmission ............................................................................. 92

6.5.1 Control Packet Reception ...................................................................................................... 92

6.5.2 Control Packet Transmission ................................................................................................. 93

7. I/O Definitions and Timing ....................................................................................... 94

7.1 I/O Timing ..................................................................................................................................... 105

7.1.1 DASL Signals ...................................................................................................................... 105

7.1.2 OCM Interface Signals ........................................................................................................ 105

7.1.3 Master-Slave Speed Expansion Signals ............................................................................. 108

8. Packaging and Pin Information ............................................................................. 109

9. DASL Specification and Pico-Processor .............................................................. 124

PRS28.4G

IBM Packet Routing Switch

Page 6 of 131

prs28.04TOC.fm

February 6, 2001

10. Electrical Characteristics ...................................................................................... 125

11. Line Termination .................................................................................................... 128

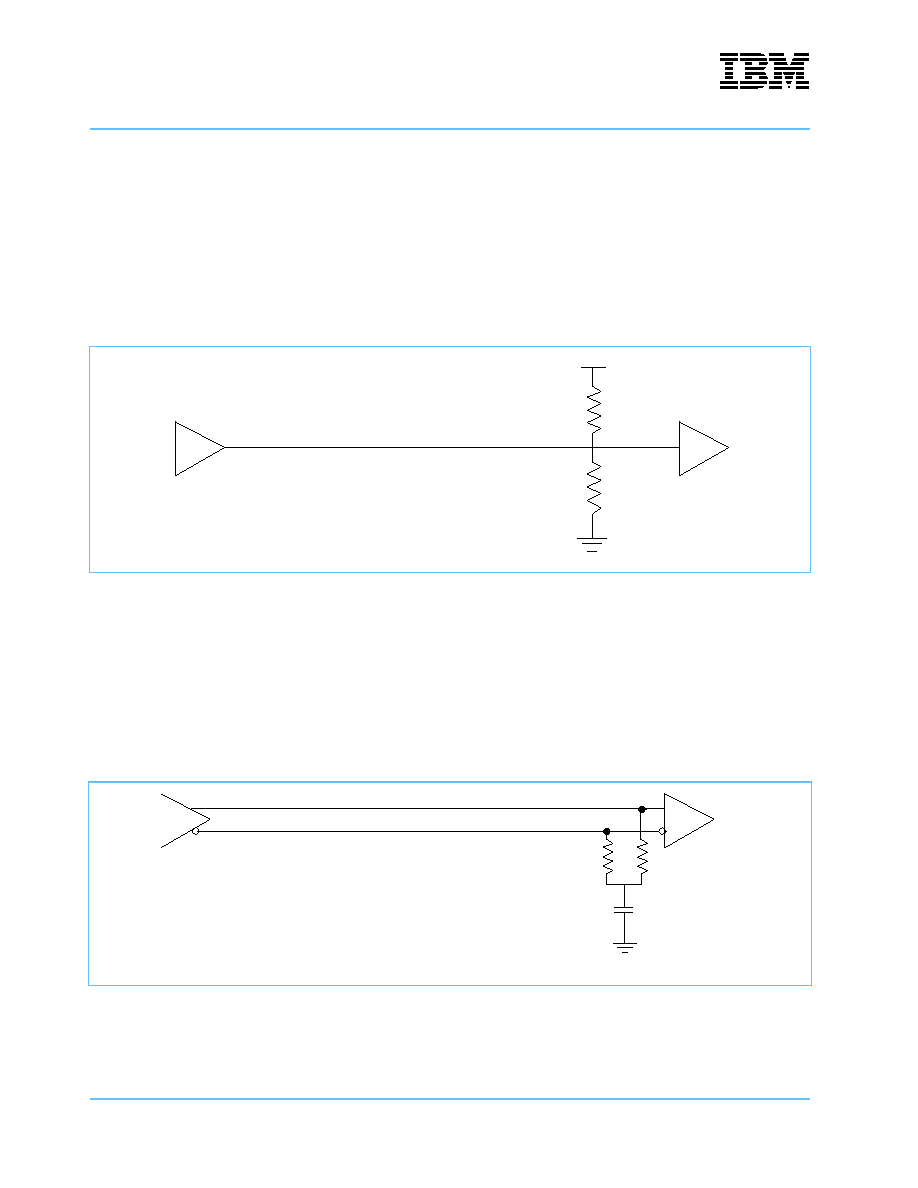

11.1 HSTL ........................................................................................................................................... 128

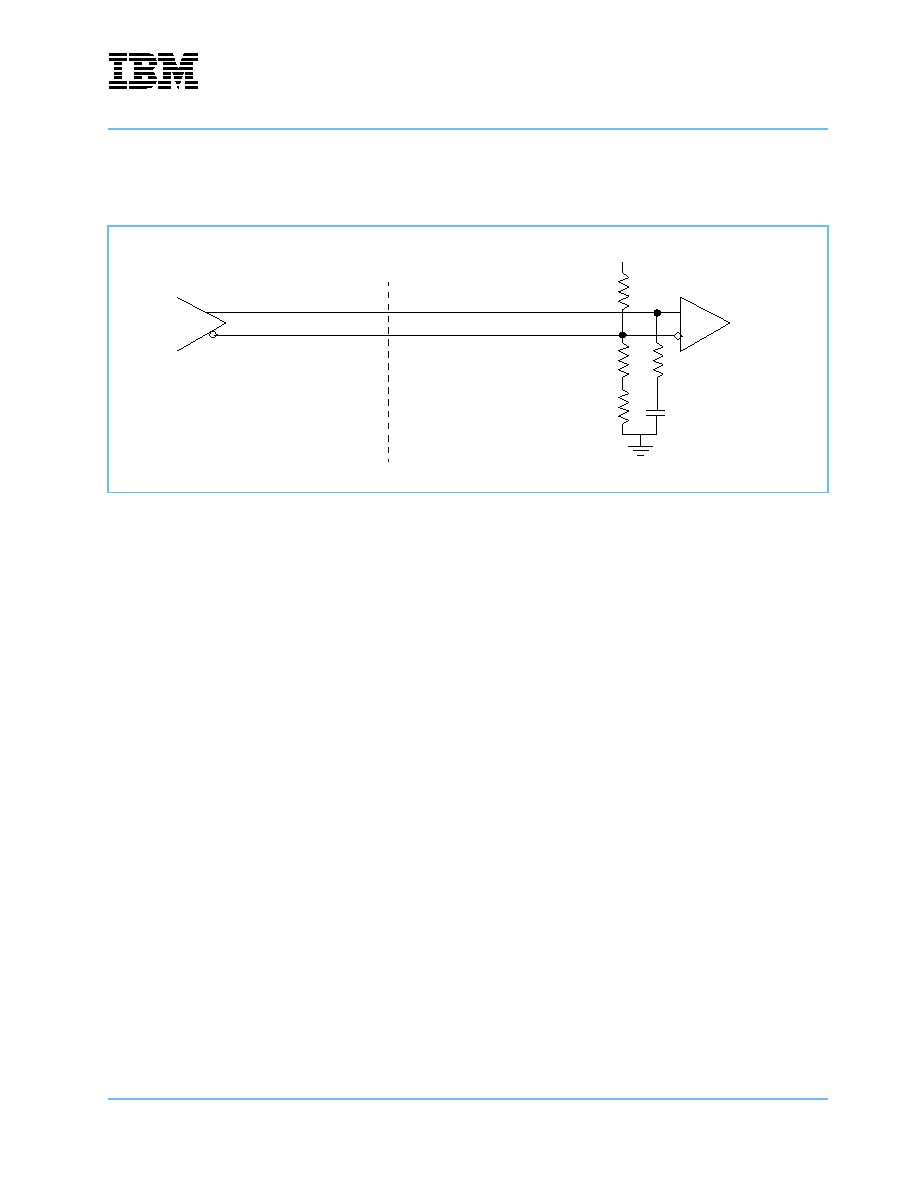

11.2 DASL and SYS_CLK .................................................................................................................. 128

12. Internal RAM ABIST ............................................................................................... 130

13. References ............................................................................................................. 131

3. Revision Log ............................................................................................................ 131

PRS28.4G

IBM Packet Routing Switch

prs28.04LOF.fm

February 6, 2001

List of Figures

Page 7 of 131

List of Figures

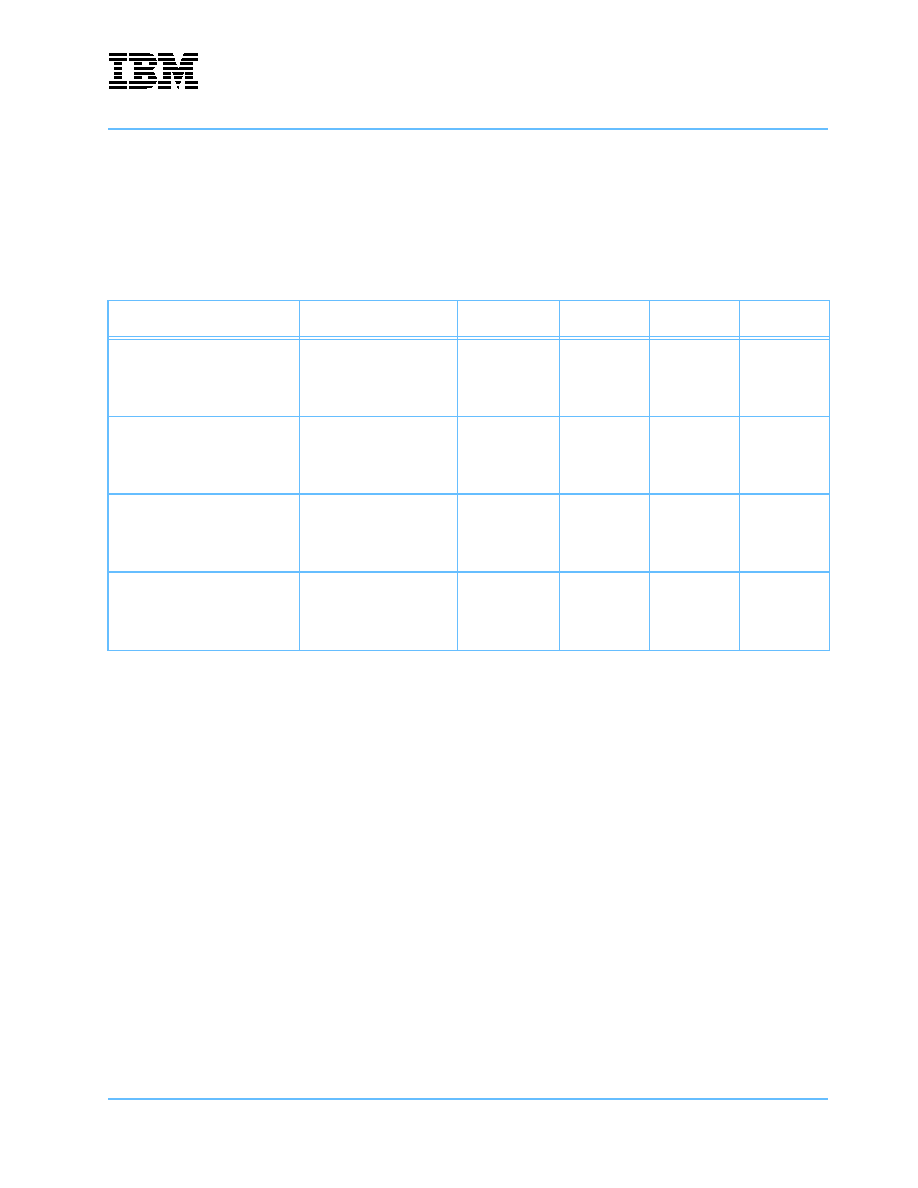

Figure 1: Pinout ........................................................................................................................................... 13

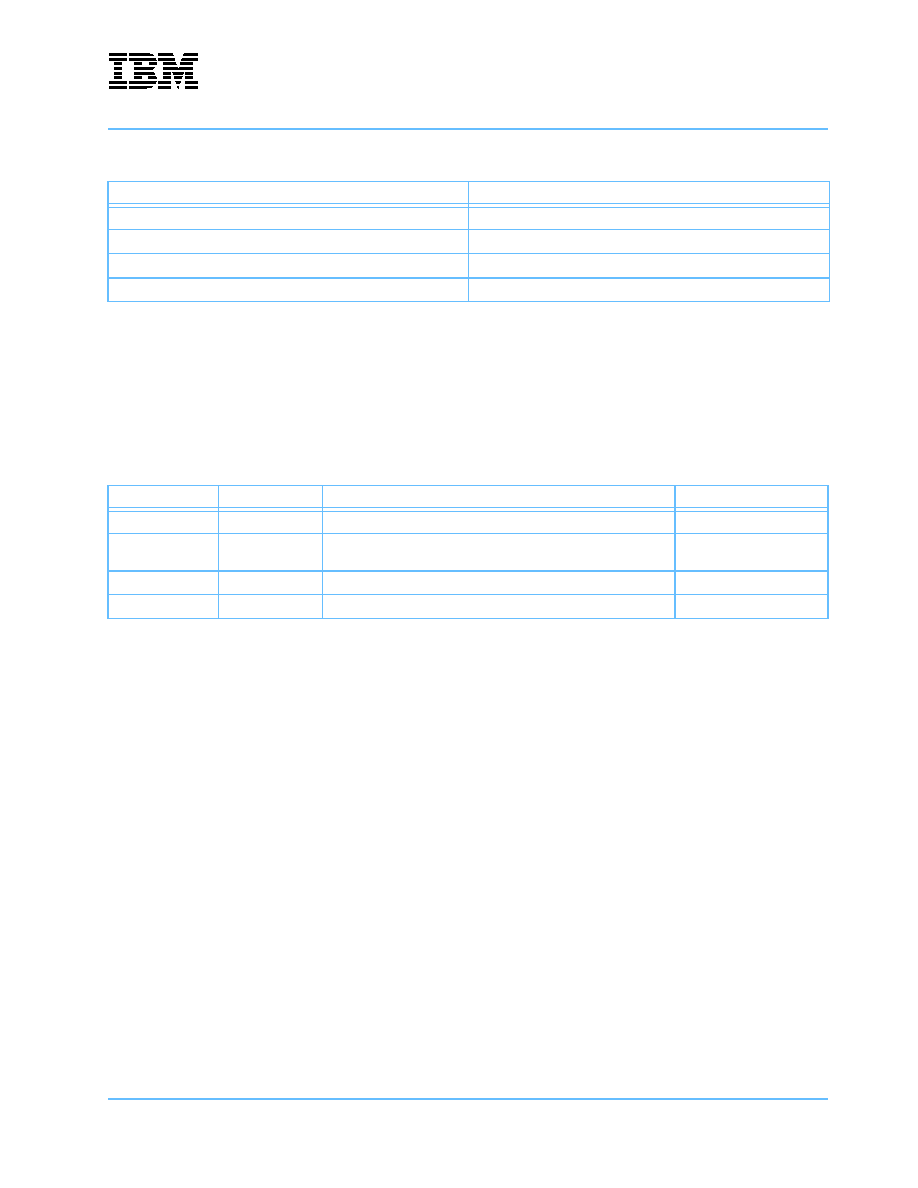

Figure 2: Block Diagram .............................................................................................................................. 14

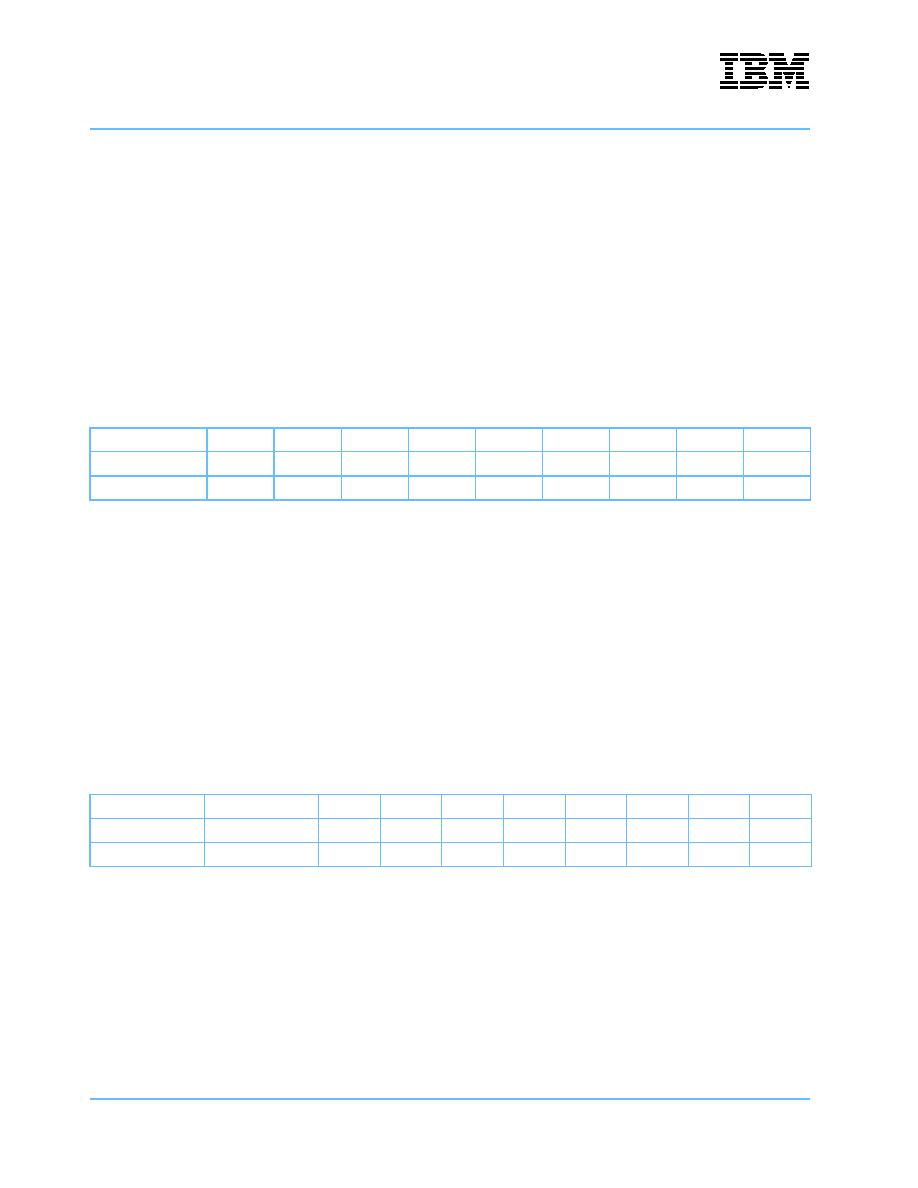

Figure 3: Speed Expansion Block Diagram ................................................................................................. 22

Figure 4: Single Stage Port Expansion Block Diagram ............................................................................... 24

Figure 5: Packet Format 1.77 Gb/s Port ...................................................................................................... 25

Figure 6: Packet Format for 3.54 Gb/s Port ................................................................................................ 25

Figure 7: Idle Packet Format ....................................................................................................................... 28

Figure 8: Input-side Grant Operation ........................................................................................................... 38

Figure 9: OCM Interface Signals Timing Diagram ..................................................................................... 105

Figure 10: OCM Signal Timing Diagram .................................................................................................... 106

Figure 11: SND_GRANT(n) ....................................................................................................................... 107

Figure 12: RCV_GRANT(n) ....................................................................................................................... 107

Figure 13: Q_FULL, Q_EMPTY, Q_SYNC Timing Diagram ..................................................................... 108

Figure 14: Package Physical Dimensions ................................................................................................. 109

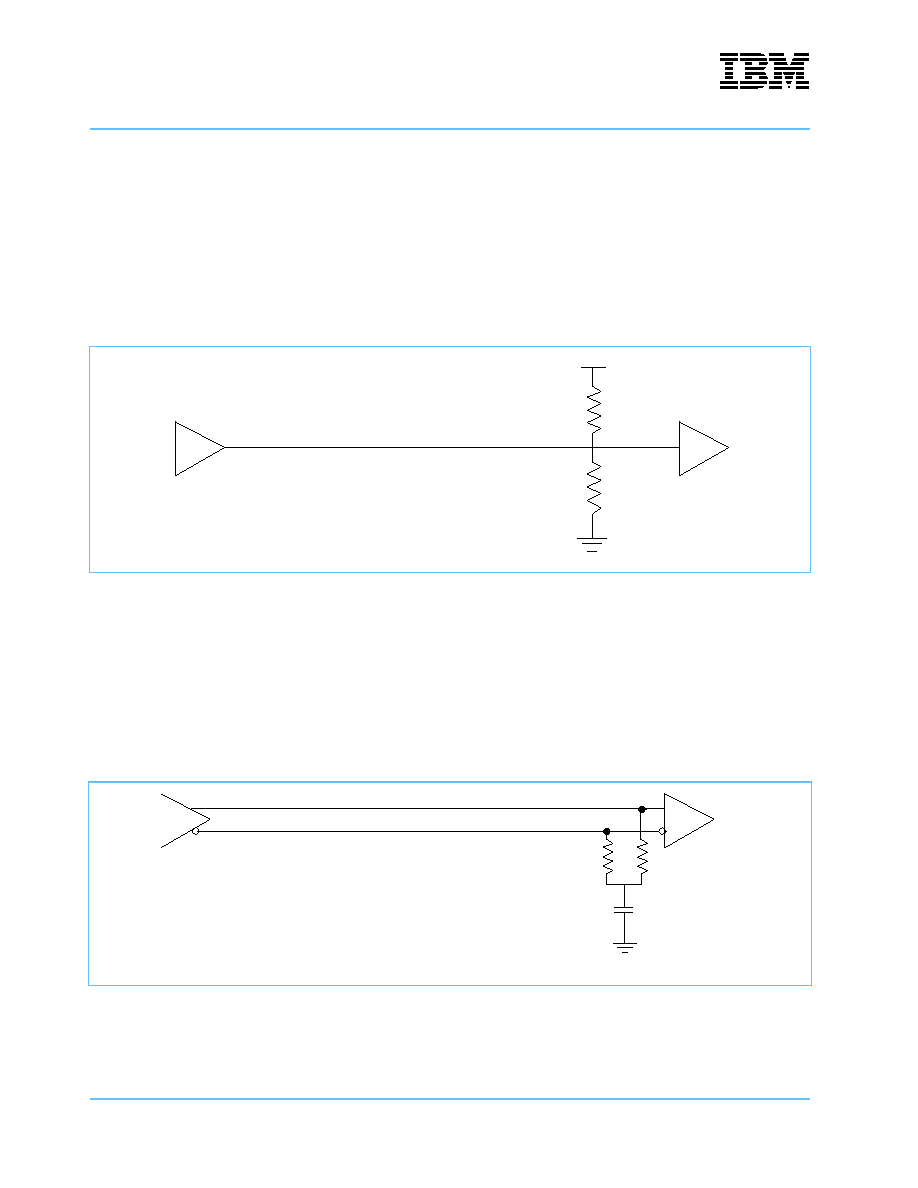

Figure 15: HSTL Termination .................................................................................................................... 128

Figure 16: DASL Termination for Slave LUs ............................................................................................. 128

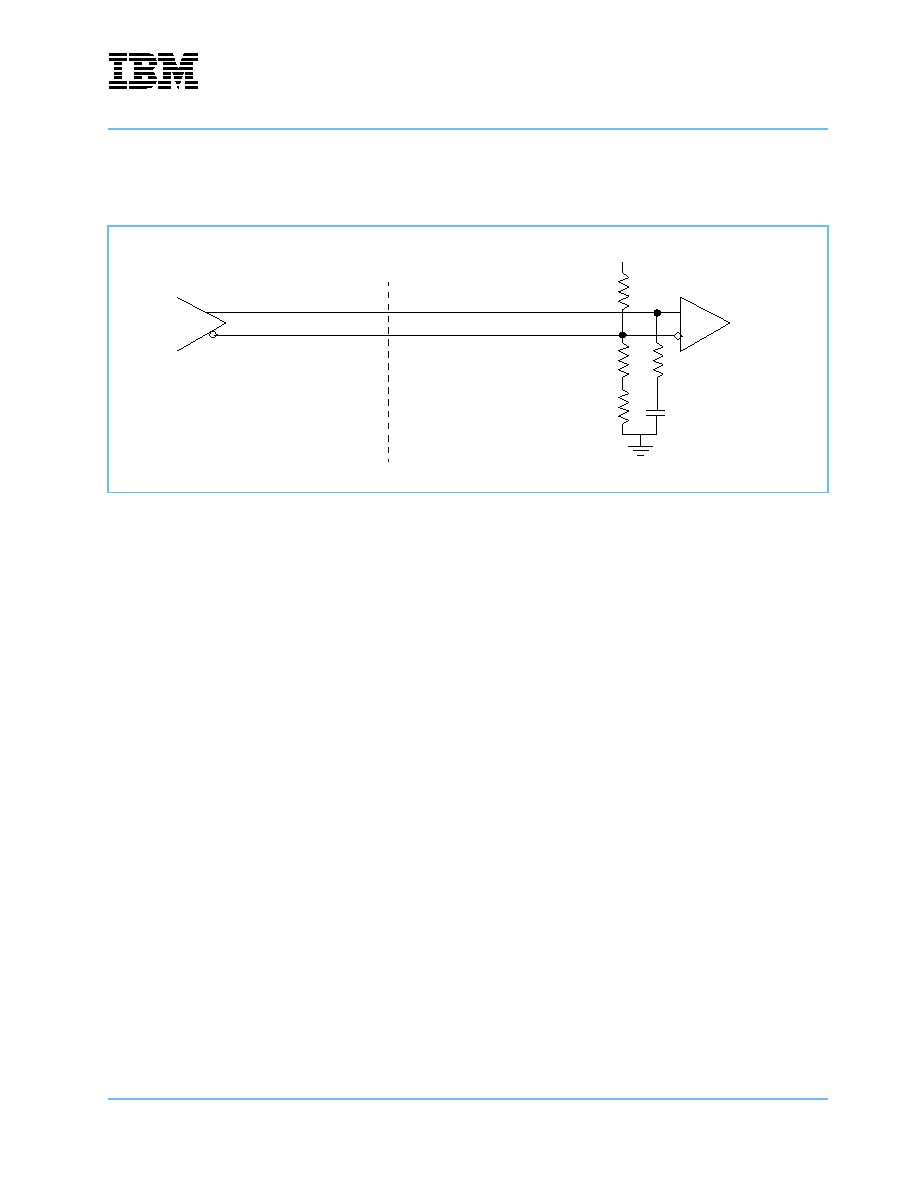

Figure 17: DASL Termination for Master LUs, Bits 2 and 3 ...................................................................... 129

PRS28.4G

IBM Packet Routing Switch

List of Figures

Page 8 of 131

prs28.04LOF.fm

February 6, 2001

PRS28.4G

IBM Packet Routing Switch

prs28.04LOT.fm

February 6, 2001

List of Tables

Page 9 of 131

List of Tables

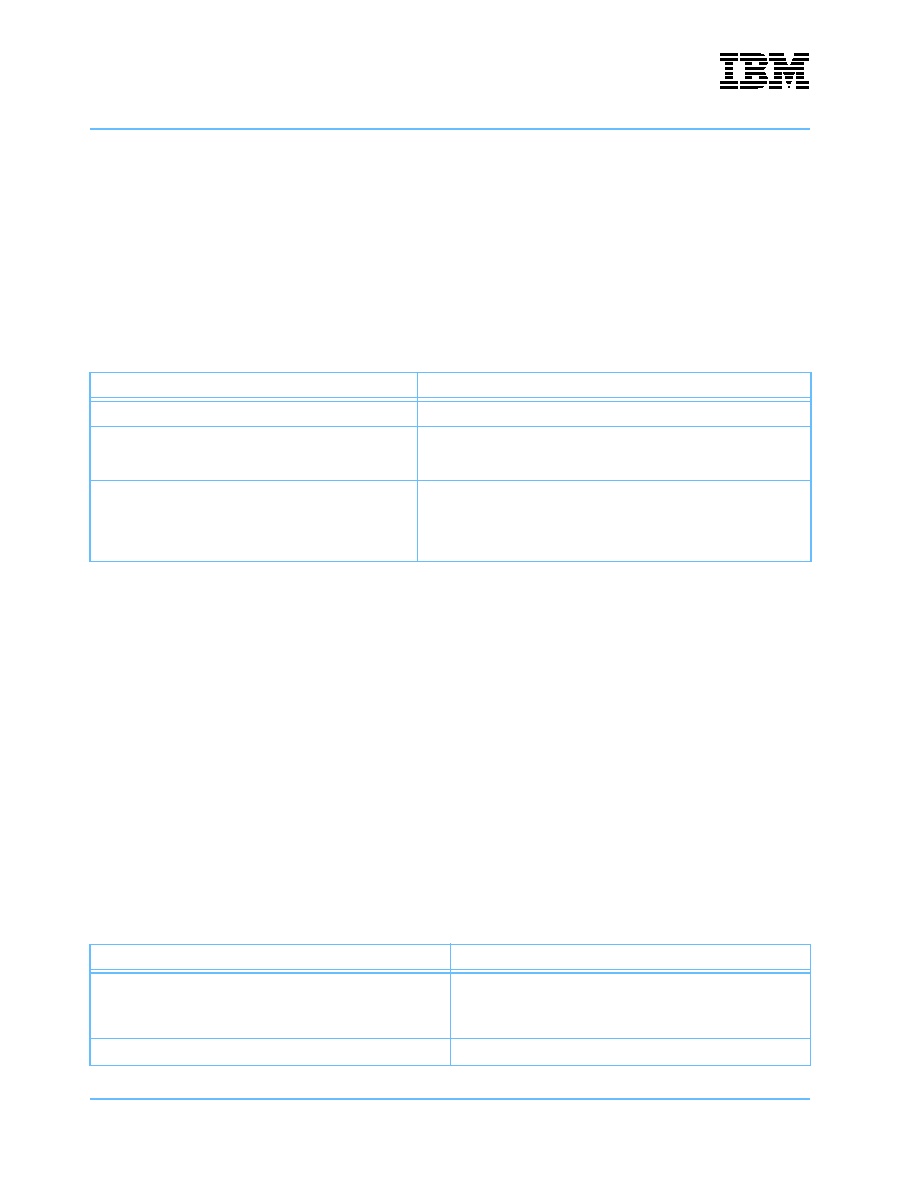

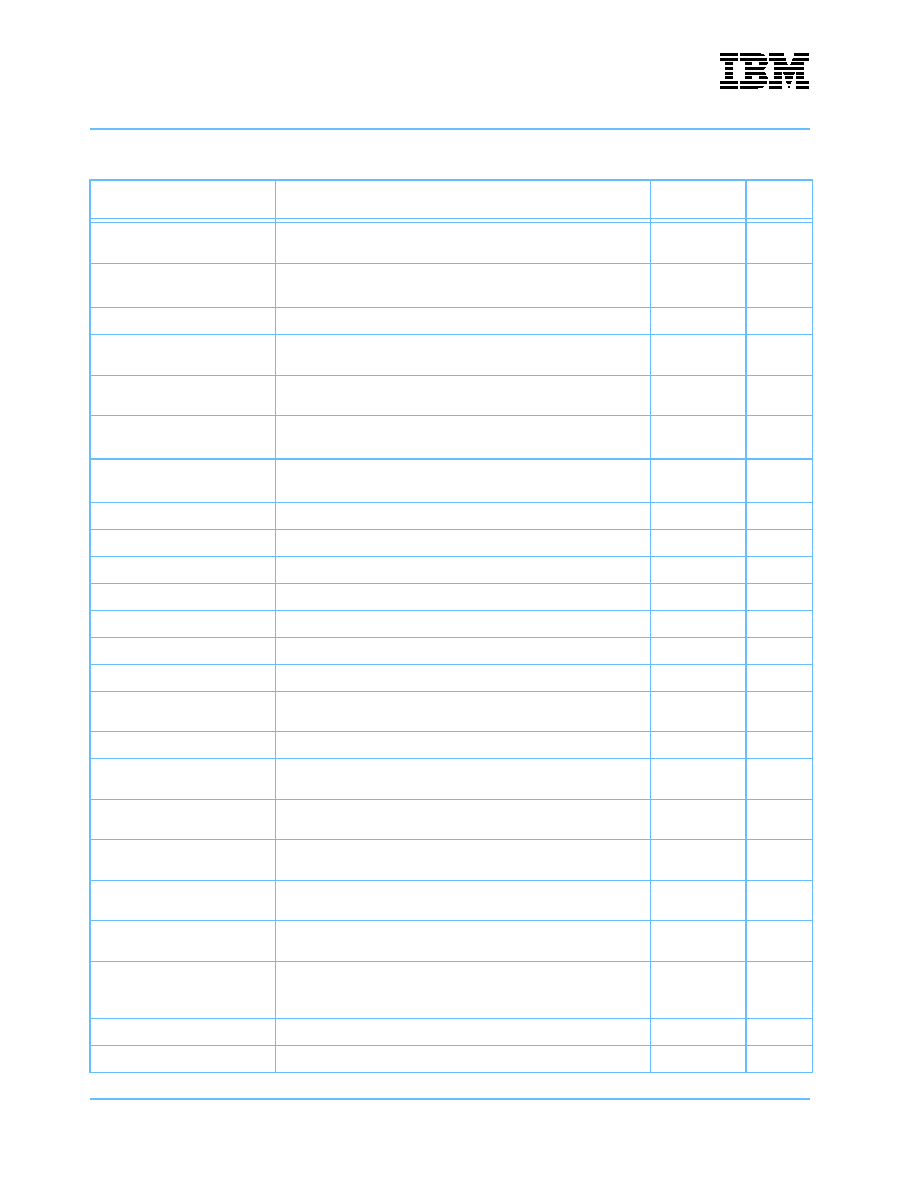

Table 1: Speed Expansion Shared Memory Buffering Capacities ................................................................ 22

Table 2: Physical Bit Organization of a Port ................................................................................................. 27

Table 3: Packet Length and Logical Unit Length .......................................................................................... 29

Table 4: Header Byte H0 for Idle Packets .................................................................................................... 30

Table 5: Header Byte H0 for Data Packet (Bits 2 and/or 3

0), and Control Packet ................................... 30

Table 6: Data Packet Priority ........................................................................................................................ 31

Table 7: Bit Map Filter .................................................................................................................................. 31

Table 8: Header Byte 1 and 2 and Incoming Packet Bitmap ........................................................................ 32

Table 9: Header Byte 0 and 1 and Output queue grant ................................................................................ 32

Table 10: Byte Reordering via the Look-Up Table ....................................................................................... 41

Table 11: Shared Memory Reserved Address for Control Packets .............................................................. 44

Table 12: Port Combination in Internal Port Expansion ................................................................................ 45

Table 13: OCM Instruction Set Definitions ................................................................................................... 47

Table 14: Number of Instruction Bits Protected by Parity Bit ........................................................................ 49

Table 15: OCM Instruction Mode Sequence ................................................................................................ 50

Table 16: OCM Scan Mode Sequence ......................................................................................................... 50

Table 17: Simulated BIST Signatures .......................................................................................................... 53

Table 18: Status Register Bit Definitions ...................................................................................................... 54

Table 19: Application Register List ............................................................................................................... 56

Table 20: Master and Slave Memory Bank Addressing ............................................................................... 92

Table 21: Signal Definitions .......................................................................................................................... 94

Table 22: DBG_DATA Bus Definitions ....................................................................................................... 100

Table 23: I/O Summary .............................................................................................................................. 102

Table 24: DASL Interface Skew ................................................................................................................. 105

Table 25: OCM Signal Timing Values ........................................................................................................ 106

Table 26: SND_Grant Sampling Window Timing ....................................................................................... 107

Table 27: RCV_Grant Sampling Window Timing ....................................................................................... 107

Table 28: Q_FULL, Q_EMPTY, Q_SYNC Timing Values .......................................................................... 108

Table 29: Pin List, Sorted by Pin Name ...................................................................................................... 110

Table 30: Pin List, Sorted by Pin Number .................................................................................................. 117

Table 31: DASL Temperature Range ......................................................................................................... 124

Table 32: Instruction Memory in Processor Address Space ....................................................................... 124

Table 33: Absolute Maximum Ratings ........................................................................................................ 125

Table 34: Recommended Operating Conditions ........................................................................................ 126

Table 35: Electrical Characteristics for DASL I/Os ..................................................................................... 127

Table 36: Clocks ......................................................................................................................................... 127

PRS28.4G

IBM Packet Routing Switch

List of Tables

Page 10 of 131

prs28.04LOT.fm

February 6, 2001

prs28.04.fm

February 6, 2001

PRS28.4G

IBM Packet Routing Switch

General Information

Page 11 of 131

1. General Information

1.1 Features

� Non-blocking, self-routing, single-stage switch

� High Performance:

- 100 MHz to 111.1 MHz frequency operation

- 1.77 Gb/s throughput per port (16x16 config.)

- Up to 3.54 Gb/s throughput per port (8x8 con-

fig.)

- Up to 28.4 Gb/s single device aggregate

throughput

- Up to 56.8 Gb/s aggregate throughput with

speed expansion

� Serial data communication at 444 Mb/s, compli-

ant with the EIA/JEDEC JESD8-6 standard.

� Multicast support without packet duplication in

shared memory

� Dynamically shared output buffer (256 packets

of 64 to 80 bytes)

� Configurable number of traffic priorities (1 to 4)

with programmable output queue thresholds

and shared memory thresholds

� Configurable packet lengths of:

- 64 to 80 bytes (increment of four)

- 128 to 160 (increment of eight) with external

speed expansion only

� Serial processor interface (on-chip monitor)

� Packet header of three bytes, containing desti-

nation bit map, packet priority, switch redun-

dancy support information, all protected by a

parity bit

� Shared output buffer with total capacity of:

- 256 packets for a single chip

- 512 packets with external speed expansion

� Packet lossless switchover (scheduled

switchover) facility

� Reception on any input port of Control Packets

destined to the local processor

� Transmission of control packets from the local

processor to any output port

� Detection of link liveness by reception of specific

packets

� Programmable byte shuffling in outgoing

packets

� CMOS5S6 (0.35

�

m) technology: 3.3V compliant

TTL compatible I/O for low speed signals

� IEEE 1149.1 standard boundary scan to facili-

tate circuit board testing

1.2 Description

The IBM Packet Routing Switch PRS28.4G is the

first in a family of second generation switching

devices designed for high performance, non-

blocking fixed length packet switching. Its modularity

enables development of scalable switch fabrics of

aggregate bandwidth from 28.4Gb/s to 227.2 Gb/s.

The PRS28.4G receives packets on 16 input ports

and routes them to one or more of 16 output ports

based on bit map information carried in the packet

header. Each port operates at 1.77 Gb/s, resulting in

a single device throughput of 28.4 Gb/s. This data

speed is achieved by implementing, in one device,

two 16 by 16 sub-switch elements, running at 888

Mb/s per port and organized internally in speed

expansion mode. In addition, 444 Mb/s serial data

communication provides, over two differential pairs,

the necessary bit rate per island.

Quality of service support is provided through four

levels of packet priority. The architecture supports

flow control, based on a grant mechanism, and

provides programmable thresholds, one per priority.

Scalability of speed is achieved by external speed

expansion. Two devices operate in parallel (one as

master, the other as slave) to form a 16 by 16 switch

element at 3.54 Gb/s per port. Scalability of ports is

provided by single stage port expansion, which

allows the number of ports on the switch fabric to be

increased.

No synchronization is required between input ports.

However, packets on a given port are always

received or transmitted at fixed periodicity equal to

the packet length.

PRS28.4G

IBM Packet Routing Switch

General Information

Page 12 of 131

prs28.04.fm

February 6, 2001

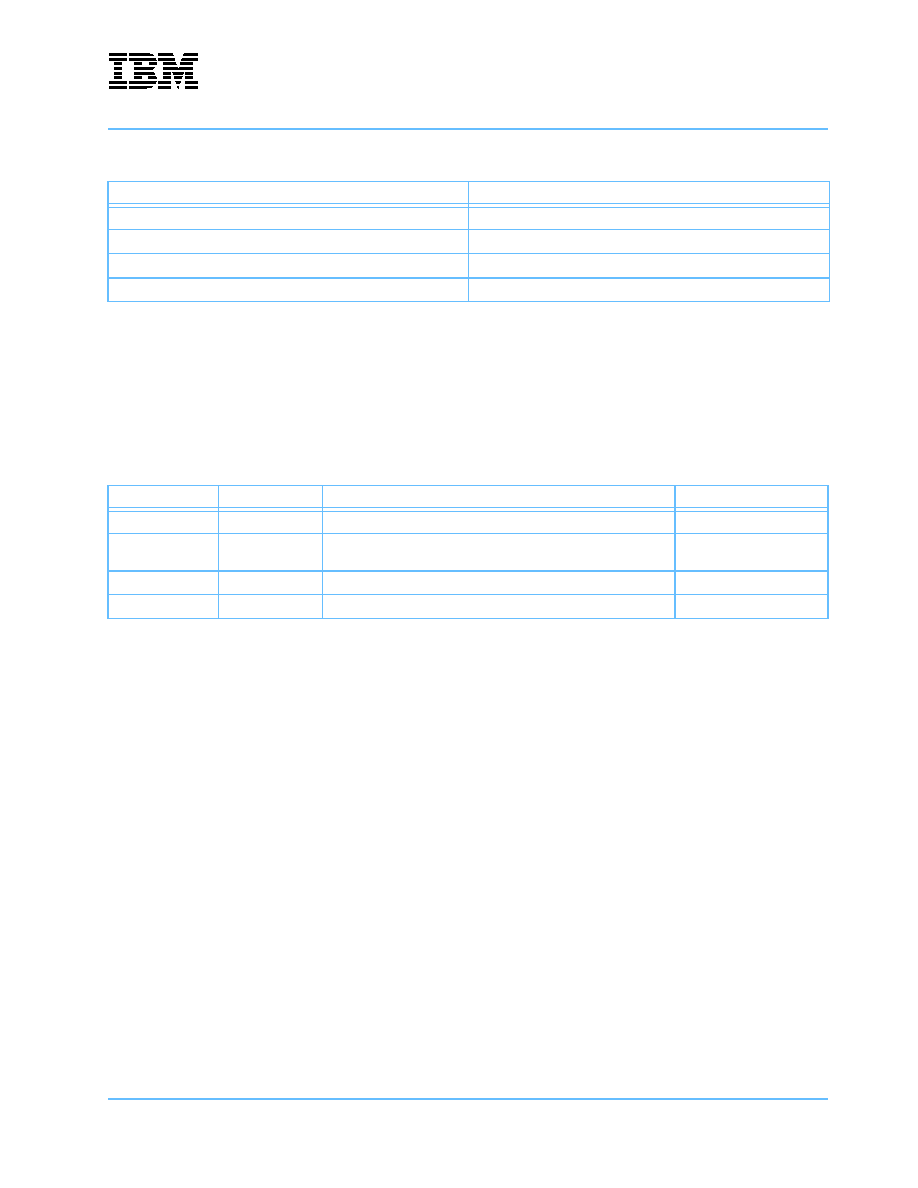

1.3 Ordering Information

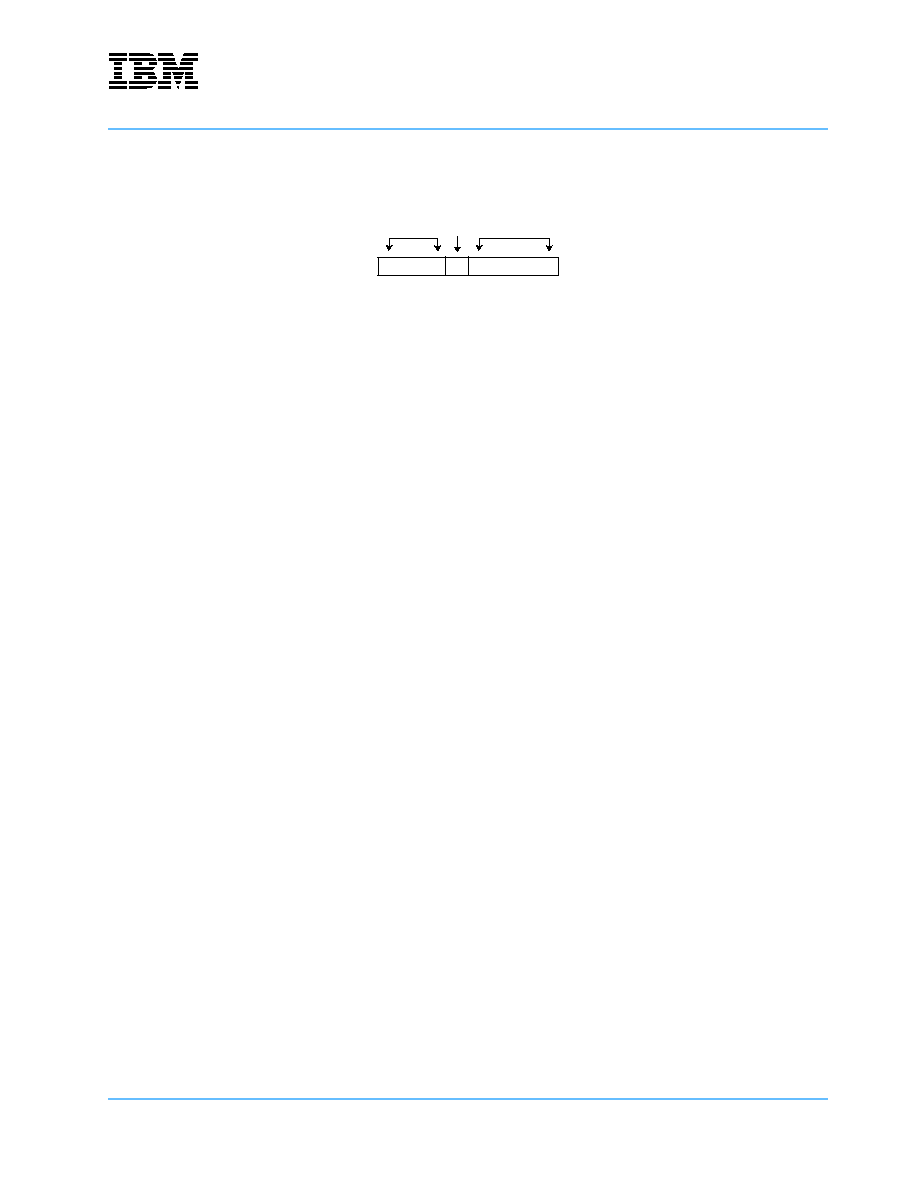

1.4 Conventions

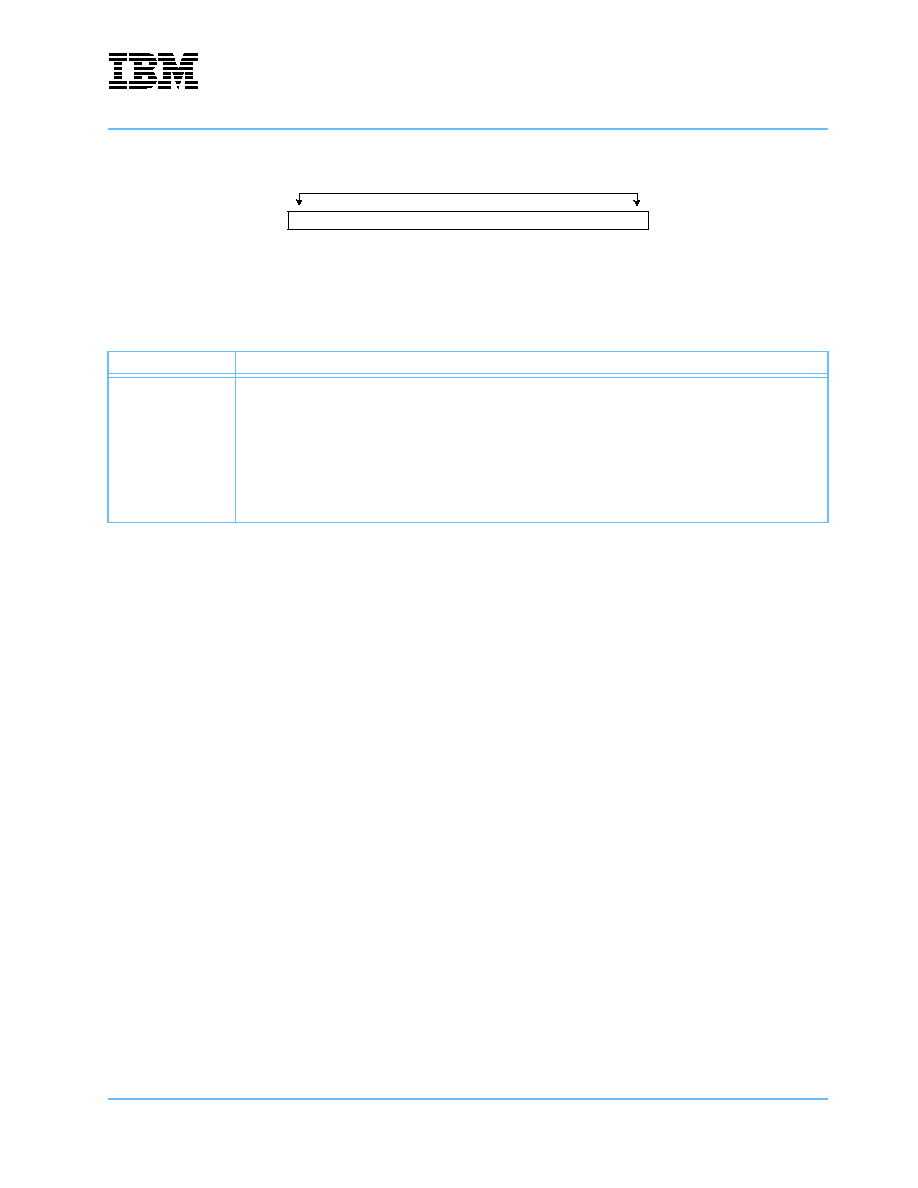

Throughout this document, standard IBM notation is used: bits and bytes are numbered in ascending order

from left to right. Thus the Most Significant Bit (MSB) has the lowest number and the Least Significant Bit

(LSB) has the highest number:

The use of overbars, for example RESET, designates signals that are active low.

Decimal, hexadecimal, and binary numbers are used in this document and represented as follows:

Decimal:

12345.67

Hexadecimal:

0x"ABCD" or ABCD'x'

Binary:

`000'b

Part Number

Description

IBM3221L0572

IBM Packet Routing Switch

MS

B

LS

B

0

1

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

General Information

Page 13 of 131

Figure 1: Pinout

(Refer to

Pin List, Sorted by Pin Number

on page 117 for names of all pins).

AE

AD

AC

AB

AA

0Y

0W

0V

0U

0T

0R

0P

0N

0M

0L

0K

0J

0H

0G

0F

0E

0D

0C

0B

0A

01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

VDD

GND

No Connect

Signal Pin

PRS28.4G

IBM Packet Routing Switch

General Information

Page 14 of 131

prs28.04.fm

February 6, 2001

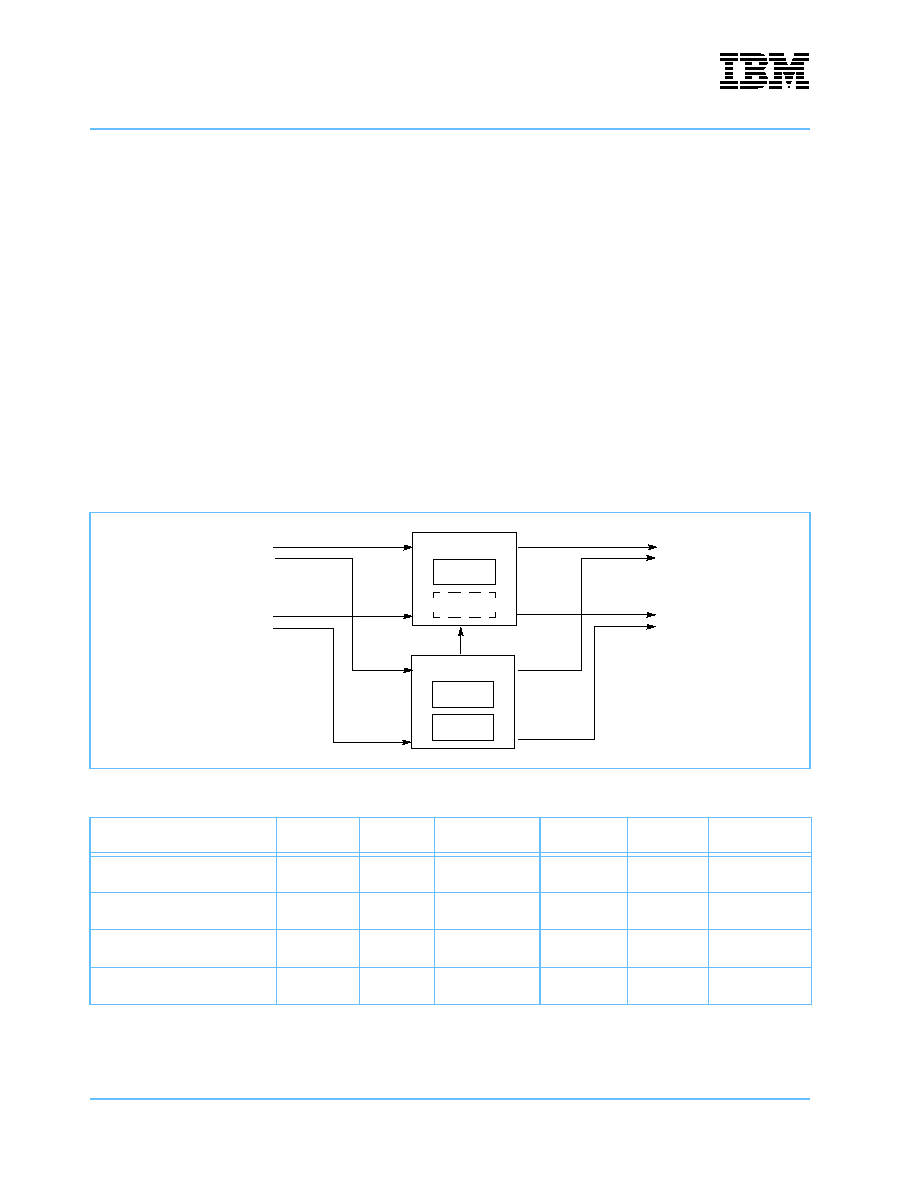

Figure 2: Block Diagram

Input

Controller

0

Input

Controller

15

Shared Memory

512 Rows

Slave

Shared Memory

512 Rows

Master

Address Manager

Output Queue 0

Output Queue 15

Output

Controller

0

Output

Controller

15

Ou

t

p

u

t

Qu

e

u

e

R

e

ad

M

a

na

ge

r

Ou

t

p

u

t

Qu

e

u

e

A

c

ce

ss

Ma

na

ge

r

of 512 positions

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Architecture

Page 15 of 131

2. Architecture

The PRS28.4G incorporates two 888 Mb/s, per-port, self-routing sub-switch elements and a control section

that is common to both.

Each 1.77 Gb/s port therefore carries two data streams, one master and one slave, each at 888 Mb/s. The

master stream carries the data packet header bytes, followed by some packet payload bytes. The slave

stream carries only payload bytes.

The input controllers examine the headers of incoming Data Packets and check the data integrity, using a

parity bit on the header bytes. Valid Data Packets are then stored in the shared memory, and their storage

addresses, along with the packet priority and bit map, are further processed by a centralized output queue

access manager. These addresses are enqueued into FIFO queues, one per output port and per priority,

according to the packet priority and bit-map field. Data Packets are then transmitted, one at a time according

to their place in the output queues, with the restriction that high priority packets always overtake lower priority

packets.

Multicast packets are processed the same way. A multicast packet is stored only once in the shared buffer,

while its address is enqueued in all output queues indicated by its bit map field. A multicast packet is trans-

mitted on the indicated outputs according to its position in each output queue, not necessarily at the same

time on all outputs.

A central address manager maintains a pool of free shared-buffer addresses and provides new store

addresses to the input controllers. Once a packet is transmitted, its address is returned to the address

manager. The address manager also keeps track of the number of outputs still holding each address, since

one address can be copied multiple times for multicast packets. Once this reaches zero, the address is

returned to the free address pool.

The shared memory is organized as two banks, one master and one slave, each consisting of 512 rows of 20

bytes, with one write port and one read port. Access to the shared memory is performed one input and output

port at a time. 16 to 20 bytes are transferred at each access, depending on the packet length. A central

sequencer grants shared memory access to the input and output ports, in round robin. This sequencer cycle

is equal, in byte cycles, to the number of data bytes stored at every access in one memory row. It is defined

as an integer between 16 and 20, such that packet length is a multiple of this integer. All cycles have equal

length. Without speed expansion or with speed expansion and packet length greater than 128 bytes, an LU is

received in two cycles of equal length. In speed expansion and packet length smaller than 128 bytes, it takes

only one cycle to receive an LU.

Data flow is controlled using a grant mechanism. Grants are given to the input interface of the attached

device to allow packets to be transmitted. Similarly, the output interface of the attached device provides

grants to each output port to enable packet transmission. On the input side of the switch, output queue

grants, which reflect the status of the output queues, and memory grants, for the status of the shared

memory, are provided. One output queue grant is provided per output and per priority. The output queue

manager maintains a counter for each output queue, which indicates the total number of packets enqueued

for that output, regardless of priority. Four programmable output queue thresholds are also provided, one for

each priority. All output counters are compared to those four thresholds once per sequencer cycle. If an

output counter value is less than the threshold, the corresponding grant is set. Otherwise, it is cleared. Simi-

larly, a counter keeps track of the total number of packets in the shared memory. Four programmable shared

memory thresholds are also provided, one for each priority. This counter is compared once per sequencer

cycle to those four thresholds to generate the memory grants. An input interface island is only allowed to

PRS28.4G

IBM Packet Routing Switch

Architecture

Page 16 of 131

prs28.04.fm

February 6, 2001

transmit a packet when it has received the output queue grants for the packet's destination, in addition to the

memory grant for the packet priority. On the output side, a send grant is provided to each output port, regard-

less of priority.

Control Packets can be received on any input ports and are passed one at a time to the local processor. A

control packet address queue allows buffering of up to 16 control addresses. Also, control packets can be

transmitted by the local processor on any set of output ports. Control Packets do not carry a priority and are

always transmitted on one output before any other enqueued Data Packets. Due to the slow nature of the

local processor access compared to the packet data traffic rate, Control Packet transmission is infrequent

and does not impact the performance of high priority traffic.

An On-Chip Monitor (OCM) provides a serial interface to a local processor for programming application regis-

ters and accessing control packets.

A high speed serial interface is used to minimize the number of pins and to provide direct access over an

extended distance. Two pairs of differential lines running at 444 Mb/s are provided for each master and slave

byte stream. Therefore, each port is composed of four differential lines. On the input side, the serial interface

provides deserialization of one 2.25 ns bit stream into a 9ns nibble stream of four bits. On the output side, a

9ns nibble stream is serialized into a 2.25 bit stream. For each stream, two nibbles are grouped to form a

byte. Data is transmitted with a known clock, such that only bit-phase alignment and packet alignment have to

be performed. There is a picocode mechanism that compensates for a skew between nimble of

�

1 clock

cycle between serial links belonging to the same port within the same device. The hardware scheduler

compensates for up to

�

2 clock cycles of skew between two devices in external speed expansion.

The following sections describe the architecture and features of the PRS28.4G from a black box perspective.

The internal structure of the device is not described. The first part describes the functional island of the

PRS28.4G architecture, its elementary building block. The second section describes the PRS28.4G speed

expansion mode.

2.1 Functional Island

2.1.1 Sizing

The PRS28.4G basic functional island is 16 input ports by 16 output ports. Each port runs at 0.8 Gb/s. The

PRS28.4G is a self-routing switch element with fixed packet length shared memory. Its shared memory has a

buffering capacity of 512 rows of 20 bytes.

The internal controller is managed by a sequencer, with a cycle value of 16 to 20 byte clocks (boundaries

included). The lower bound is given by the number of supported ports, and the upper bound by the maximum

row length of the shared memory. The island controller allows the handling of logical units (LU) of 16 to 20

bytes (in steps of 1 byte), or 32 to 40 bytes (in steps of 2 bytes). An LU is the part of a packet that one island

processes. The shared memory organization allows storage of 512 LUs of 16 to 20 bytes, or 256 LUs of 32 to

40 bytes.

2.1.2 Output Queuing and Priorities

Queuing is provided for each output port. Packets from each output are organized into four logical queues of

different priority. For each logical queue, packets are organized into a First In First Out (FIFO) queuing struc-

ture.

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Architecture

Page 17 of 131

Incoming packets are sorted by priority when stored, according to a priority flag they carry. The highest

priority is represented by 0 and the lowest by 3. Packets are transmitted on a given output with the highest

available priority, always overtaking the lower priorities.

2.1.3 Flow Control

Flow control is provided by the output queue, as well as for the entire shared memory.

One threshold value is associated with all logical queues (of each output). Each output queue has one unique

counter. The total number of packets in all four logical queues of one output is compared to the threshold

value of a given priority, in order to provide flow control for that output priority.

In addition, one counter keeps track of the total number of packets in shared memory. The shared memory

also has four thresholds, one per priority. The total number of packets in shared memory is compared to

these threshold values for each priority, regardless of the output destination of the packets.

2.1.4 Multicast

The internal architecture of the island allows for packets, physically stored once in shared memory, to be

multicasted to multiple outputs. A multicast packet is transmitted on the output ports according to the FIFO

structure of each destination output queue (not necessarily at the same time on all ports). Multicast packets

can only have one priority for all of its destinations.

2.1.5 Control Packets

Support is provided for receiving packets destined to a local processor, and for transmitting packets

constructed by a local processor. These packets are known as Control Packets.

A 16-position FIFO queue is provided for incoming control packets (no priority is involved).

2.1.6 Incoming Flow Process

Each incoming packet carries information about the physical output addresses (output port) of its destina-

tions, the logical address (priority) per output, or all zero (identification as a control packet).

The island controller allows one packet, corresponding to one input, to be processed and stored at a time.

Inputs are visited once per sequencer cycle. When the input on which a packet arrives is visited by the island

controller, the packet data is stored once in the shared memory. The address of this location is placed in the

logical queues (specified by its priority) of all of its destination outputs according to its priority. At the same

time, the shared memory counter and the output queue counters of its destination are incremented.

If an incoming packet is marked as a control packet, it is also stored in shared memory. Its address is then

placed in a control packet queue, and an interrupt is sent to the local processor. An incoming control packet

can only be received if fewer than 16 control packets are present in the control packet queue. Otherwise, the

packet is discarded and a flag is raised.

2.1.7 Incoming Flow Control

Flow control of incoming packets is provided by grants which are authorizations for the attached adapter to

transmit a packet. Grants are provided separately for each output port and for each priority of a port. An

output queue grant for a priority is provided whenever the total packet count for an output (regardless of

PRS28.4G

IBM Packet Routing Switch

Architecture

Page 18 of 131

prs28.04.fm

February 6, 2001

priority) is below the output priority threshold. It is removed whenever this count exceeds the threshold value

(no hysteresis). Grants are also provided for the shared memory for each priority. The shared memory grant

(memory grant) for a given priority is provided whenever the total packet count in shared memory is below the

shared memory priority threshold. It is removed whenever this count exceeds the threshold value (no hyster-

esis).

An adapter is only allowed to transmit a packet when it has the memory grant for the packet priority as well as

the output queue grants for the destination logical outputs. For multicast packets, the adapter is allowed to

transmit a packet if it has the memory grant for the packet priority, regardless of output queue grants.

Incoming packets also carry a drop flag. This flag allows packet discard at the input of the island whenever

the memory grant and/or output queue grants are removed before the packet is received from the attached

adapter (due to the latency in grant update). The grant information used by the input controllers to decide to

drop a packet is updated once every sequencer cycle, providing fairness among all inputs.

Finally, an anti-streaming function is provided at the input controllers to detect badly behaving adapters.

When an adapter sends a packet to an output priority for which the output queue grant or memory grant have

not been given in the past eight packet cycles, the packet is discarded and an interrupt is raised. For multicast

packets, the same mechanism is applied, but it takes only the memory grants into consideration.

2.1.8 Outgoing Flow Process

In each of the four logical output queues, control packets and Data Packets are transmitted in the following

order:

1. Control Packets

2. Priority 0 packets

3. Priority 1 packets

4. Priority 2 packets

5. Priority 3 packets

This order cannot be changed. Packets of higher priority overtake packets of lower priority.

Control Packets are constructed by the local processor and can be transmitted one at a time to multiple

outputs The control packets take precedence over any other packet present in the shared memory.

2.1.9 Outgoing Flow Control

Flow control at the output is also provided by send grants (one per output), regardless of priority. A packet on

a given output can only be transmitted if the send grant is provided for that output.

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Architecture

Page 19 of 131

2.1.10 Signaling

LU data is passed in and out of the island, one byte per clock cycle, for each input and output port, at a rate of

0.88 Gb/s.

The first byte of a packet, either incoming or outgoing, is called the Qualifier byte and carries information

about:

� Packet priority

� Packet identification

� Packet filtering support

� Drop flag

� Parity bit over the three byte header

2.1.10.1 Idle Packets

When no Data Packets are available on a port, fill-up (empty) packets, called Idle Packets, are transmitted.

The inputs recognize these packets by their packet identification, and they are not stored. Outputs automati-

cally generate Idle Packets also, when no Control Packets or Data Packets of any priority are available.

2.1.10.2 Input

For incoming Data Packets, the second and third bytes provide the address of the packet destination, in the

form of a bit map. Each bit of these two bytes is associated with an output port. A bit set to 1 in the bit map

indicates that the packet is to be routed to the corresponding port. This bit map field can point to multiple

outputs.

An incoming packet is interpreted as a Control Packet when the entire bit map field is set to 0.

2.1.10.3 Output

The second and third bytes of outgoing packets carry the grant status of all output ports. This grant status is

used by the receiver of the other adapter to make a decision on Data Packet transmission, according to the

incoming flow control scheme presented above. This grant status is referred to as an output queue grant.

On a given packet, the output queue grant field carries the status of all logical queues of the same priority.

Consecutive packets carry the grant status for the different priorities, in a cyclic order. The synchronization of

this cycle is provided by the packet numbering field contained in the outgoing Idle Packets.

2.1.11 Internal Features

2.1.11.1 Packet Filtering

A packet filtering function is provided on the switch island inputs in order to decide whether or not to receive

packets for certain destinations. According to the packet filtering field in the qualifier byte, the incoming

packet bit map is either logically ORed with a specified mask (its complement value) or not masked at all.

There is one mask for all 16 inputs.

PRS28.4G

IBM Packet Routing Switch

Architecture

Page 20 of 131

prs28.04.fm

February 6, 2001

2.1.11.2 Line Interface and Synchronization

Data are transmitted on the physical lines two bits at a time, at a rate four times that of the internal byte clock.

Each bit is carried by a differential pair at a speed of 444 Mb/s. Both the transmitting and receiving devices

run with the same byte clock.

Link synchronization is provided by a training sequence of special Idle Packets, called Sync Packets. When

sync packets are transmitted on a port, the receiving port can perform bit phase alignment of the incoming

data, as well as packet alignment. The format of these sync packets is such that they are recognized by the

receiving end as valid packets, and provide bit transitions on the physical line to allow for phase recovery. A

sync packet LU is entirely composed of `CC' bytes, except for the last byte which is `33'.

One data byte is carried over two differential pairs. One pair carries all even numbered bits, and the other one

all odd numbered bits. This converts the `CC' sync packet bytes into 0 and 1 bit transitions on the physical

lines.

2.1.11.3 Link Integrity

Link integrity is provided by a CRC field, placed in the last byte of all Idle Packet LUs. The 8-bit CRC is the

checksum of all bits carried over a port since the previous Idle Packet ended. Thus, when multiple Data

Packets are transmitted, followed at some time by an Idle Packet, the CRC of this Idle Packet covers all

previous Data Packets. This provides a measure of the link quality for fault isolation.

2.1.11.4 Packet Numbering

In order to extract the output queue grant information that is multiplexed in the second and third bytes of

outgoing packets, Idle Packets carry a packet numbering field. This field is equal to the value of the priority of

the grant status being carried by the current Idle Packets.

The number of packet cycles required to carry the output queue grant for all priorities is equal to the number

of priorities. This output queue grant cycle repeats itself as long as non-sync packets are transmitted. The

output queue grant cycle always starts with the lowest priority number and ends with the highest.

2.1.12 Miscellaneous

2.1.12.1 Receive Grants

A receive grant function is provided on device pins as a means to block packet reception for specific outputs.

This function allows the implementation of packet lossless switchover for simple switch systems. It cannot be

combined with the packet lossless switchover mechanism provided by colored packets. When a receive grant

is asserted, reception of Data Packets in the corresponding output queue is enabled. When a receive grant is

disasserted no incoming packets are stored in the corresponding output queue, regardless of their bit map.

2.1.12.2 Send Grants

Send grant pins are provided to control the outgoing flow. They indicate to the output controllers when

packets are allowed to be transmitted.

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Architecture

Page 21 of 131

2.1.12.3 Colored Packet

Idle Packets and Data Packets also carry a color, either blue or red. Color packets are used to provide

support for packet lossless switchover.

Some Idle Packets carry a yellow color. The reception of a yellow Idle Packet on a given input is logged into a

register accessible by the local processor. Yellow packets can only be transmitted by the local processor.

Yellow packets are used as link liveness messages.

2.1.12.4 Control Packets

Data Packets for which the bit map field is 0 are detected as control packets and are passed to the local

processor via a dedicated queue. The first bit map byte of an incoming packet is overwritten by the input port

number on which the packet is received.

2.1.12.5 Queue Full

Queue-full information is also provided directly by the island. Sixteen bits carry all logical port full statuses, by

multiplexing the information of all priorities of a given port over one bit. At a given time, all 16 bits carry the full

status for the same priority, for all output queues. All priorities rotate, from the lowest number to the highest,

in a cyclic manner, while the change from one priority to the next only occurs after four byte cycles. An extra

bit indicates when all 16 queue-full bits carry priority 0, and is used to synchronize to this cycle.

2.1.12.6 Queue Empty

Queue-empty information is also provided by a 16-bit bus, for all logical output queues. The information multi-

plexing and timing is identical to the queue-full bits.

2.1.12.7 Look-Up Table

The lookup table is a facility that allows permutation of the bytes of outgoing packets. Only the first 16 bytes

can be permuted among each other or overwritten by one of the 16 bytes. One table is provided for all output

ports.

PRS28.4G

IBM Packet Routing Switch

Architecture

Page 22 of 131

prs28.04.fm

February 6, 2001

2.2 Expansion Modes

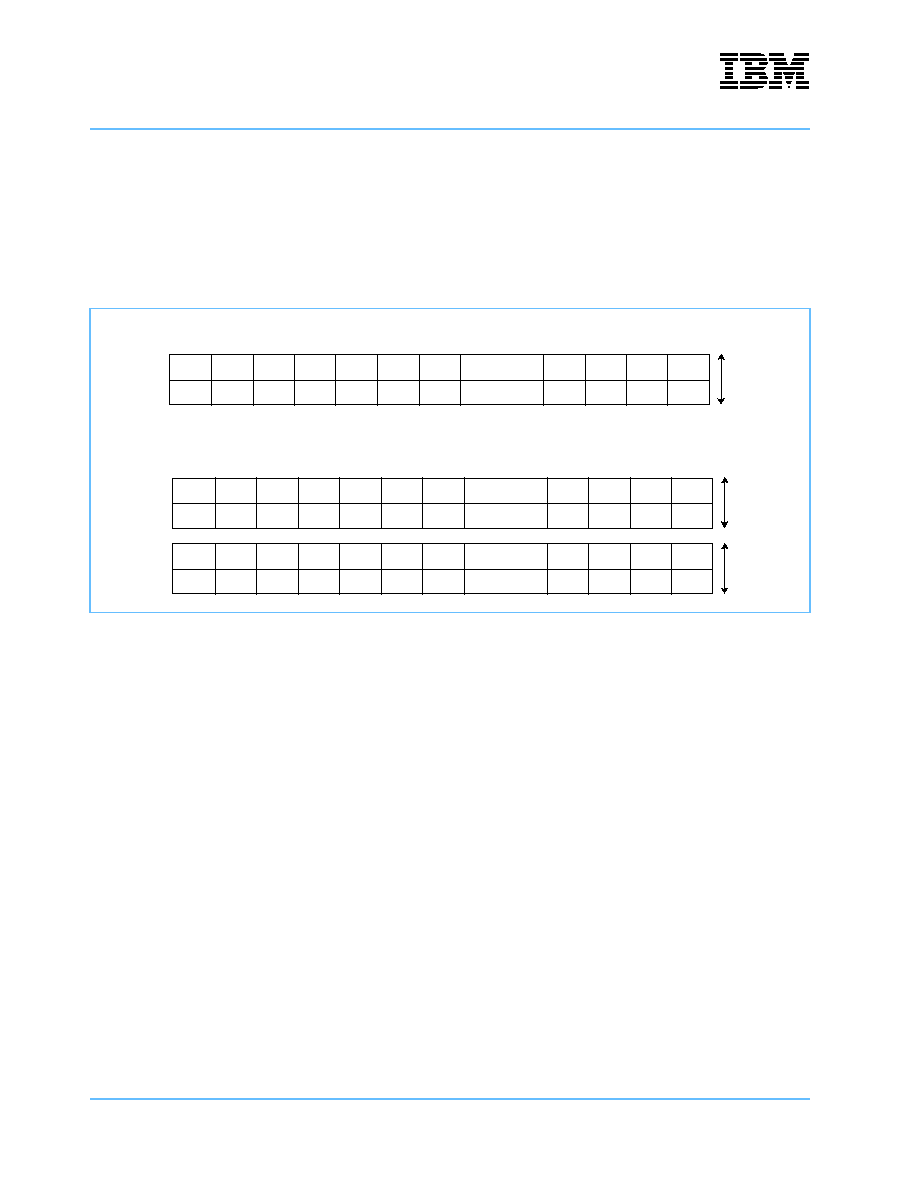

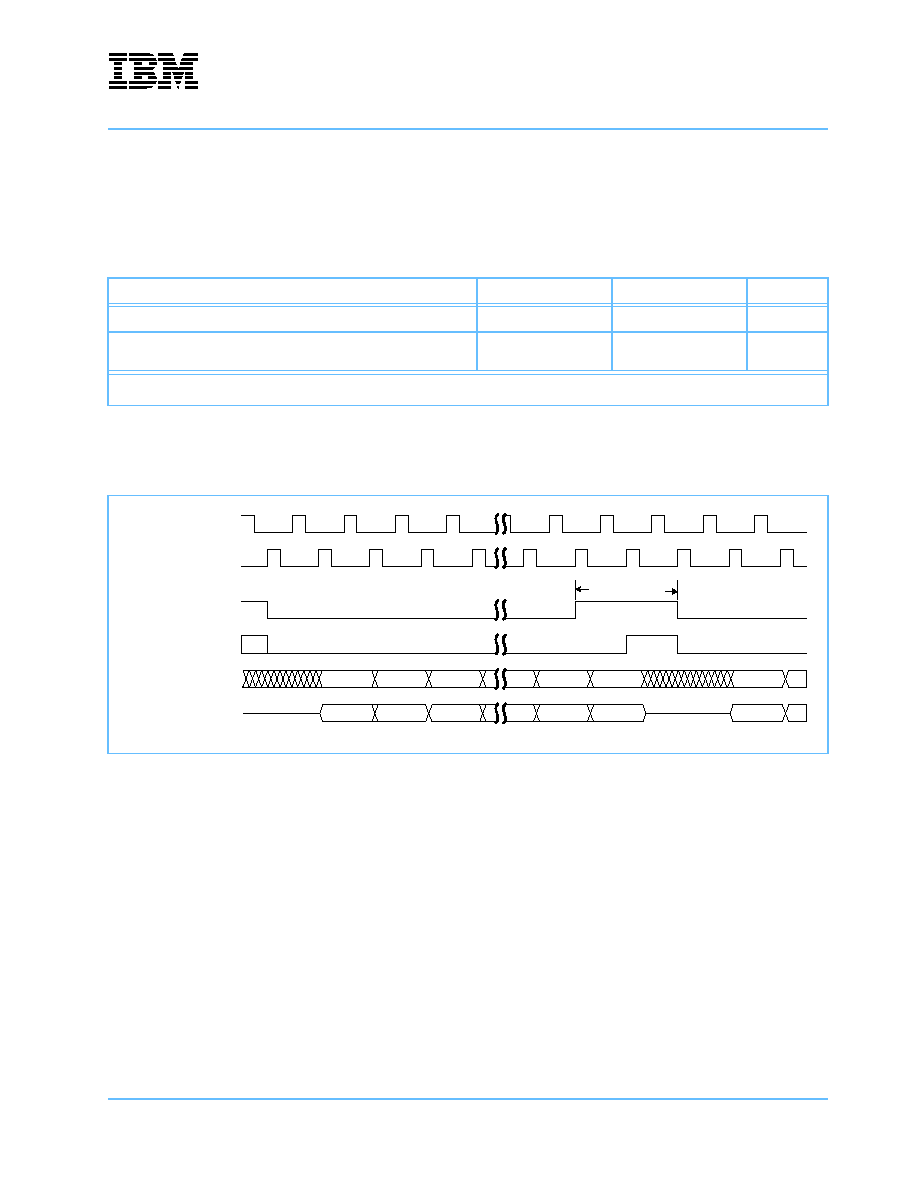

2.2.1 Speed Expansion

The PRS28.4G device is internally composed of two islands operating in speed expansion. It is a 16 x 16

shared-buffer device, with port speed of 1.77Gb/s. Each port is composed of two byte streams, one corre-

sponding to the master island, one to the slave island.

The device supports two-way speed expansion, that is, two devices can be combined to increase the port

speed to 3.2Gb/s. Supported packet lengths range from 64 to 80 bytes, in increments of four. However, when

two devices operate in speed expansion, packets of length 128 to 160, in increments of eight, are also

supported.

Note: The PRS28.4G implementation allows for only two (2) devices to be combined in external speed

expansion.

Speed expansion allows multiple devices to be connected in parallel to increase the port speed while keeping

the number of ports constant, as shown in the

Speed Expansion Block Diagram

.

In each case, the LU size seen by one island (either the master or the slave island of one device) is equal to

the packet length divided by the speed expansion factor (port speed divided by the island port speed of 0.88

Gb/s)

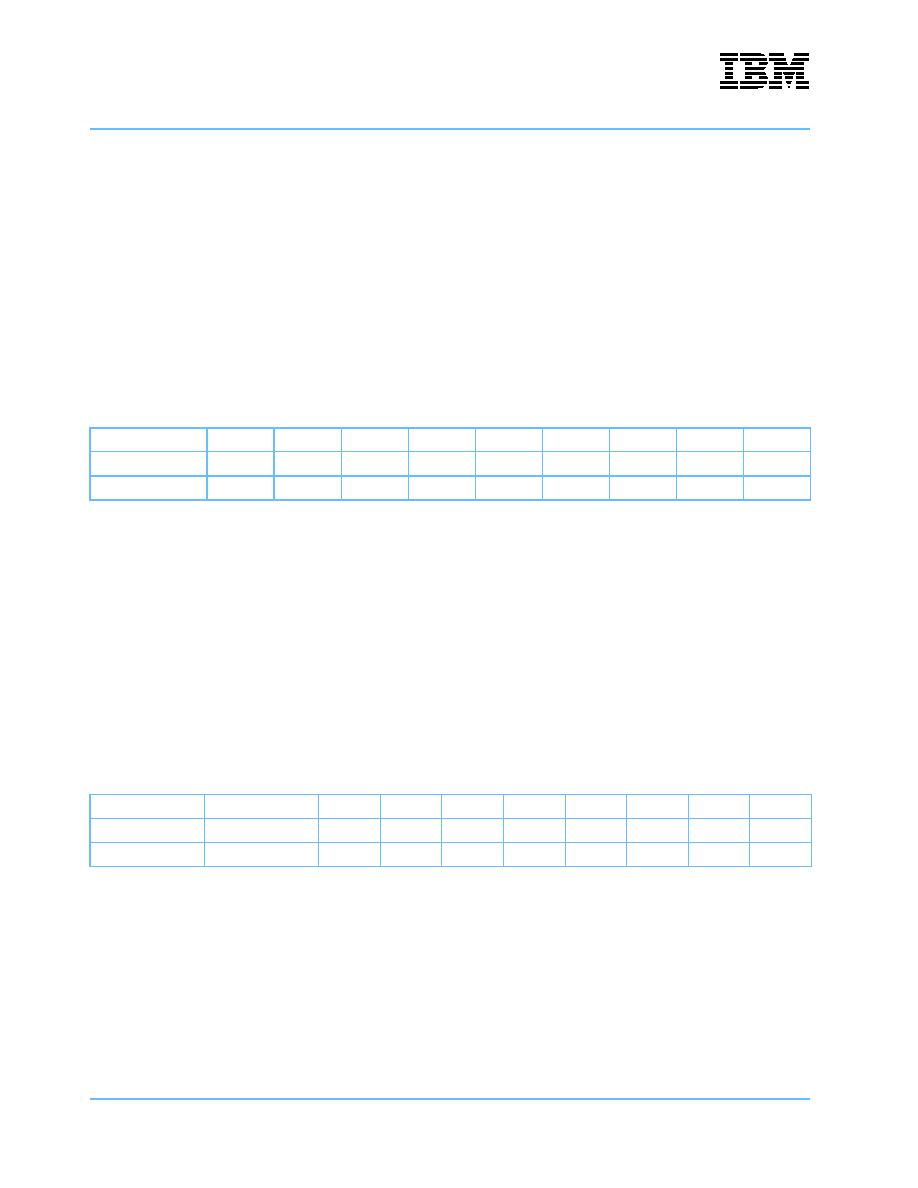

Figure 3: Speed Expansion Block Diagram

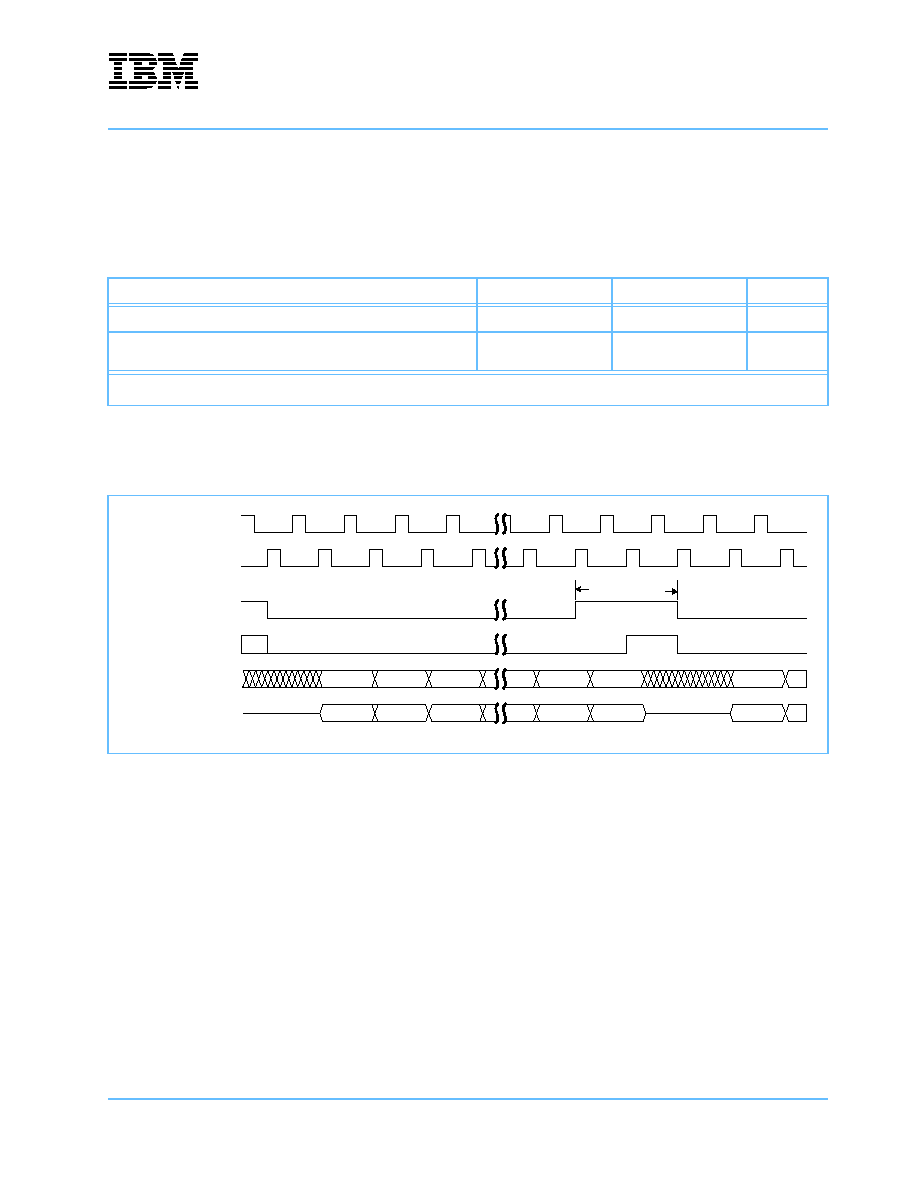

Table 1: Speed Expansion Shared Memory Buffering Capacities

Speed Expansion Mode

Switch

Configuration

Gb/s per

port

Packet Length

(bytes)

LU Size

(bytes)

Buffering

(packets)

Speed

Expansion Factor

Single device, no internal speed

expansion

16 x 16

1.77

64 - 80

32 - 40

256

2

Single device, with internal speed

expansion

8 x 8

3.54

64 - 80

16 - 20

256

4

Two devices speed expanded,

no internal speed expansion

16 x 16

3.54

64 - 80

16 - 20

512

4

Two devices speed expanded,

no internal speed expansion

16 x 16

3.54

128 - 160

32 - 40

256

4

Slave

Buffer

Control

16 Outputs

16 Inputs

Sync + Address

Master

Buffer

Control

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Architecture

Page 23 of 131

2.2.1.1 External Speed Expansion

When multiple islands are running in speed expansion, one is master and the others are slaves. The master

device is the one which receives the byte stream containing the qualifier byte, bit map, and output queue

grant. The master device also performs packet routing and queuing. The slave devices only receive data

bytes, and do not perform any packet routing and queuing. The address of packets in shared memory is

provided by the master, and is the same for all devices. Furthermore, the slave devices' internal sequencers

are all synchronized on the master sequencer in order to transmit the LUsat the same time on a given port.

LUs of a packet incoming on a port have to arrive at all devices within a two-byte interval.

2.2.1.2 Internal Speed Expansion

Ports of one island can also be paired to double the port speed while reducing the number of input and output

ports to eight. Each pair of ports is built of one master port and one slave port, which have exactly the same

functions as the ports of master or slave islands in external speed expansion.

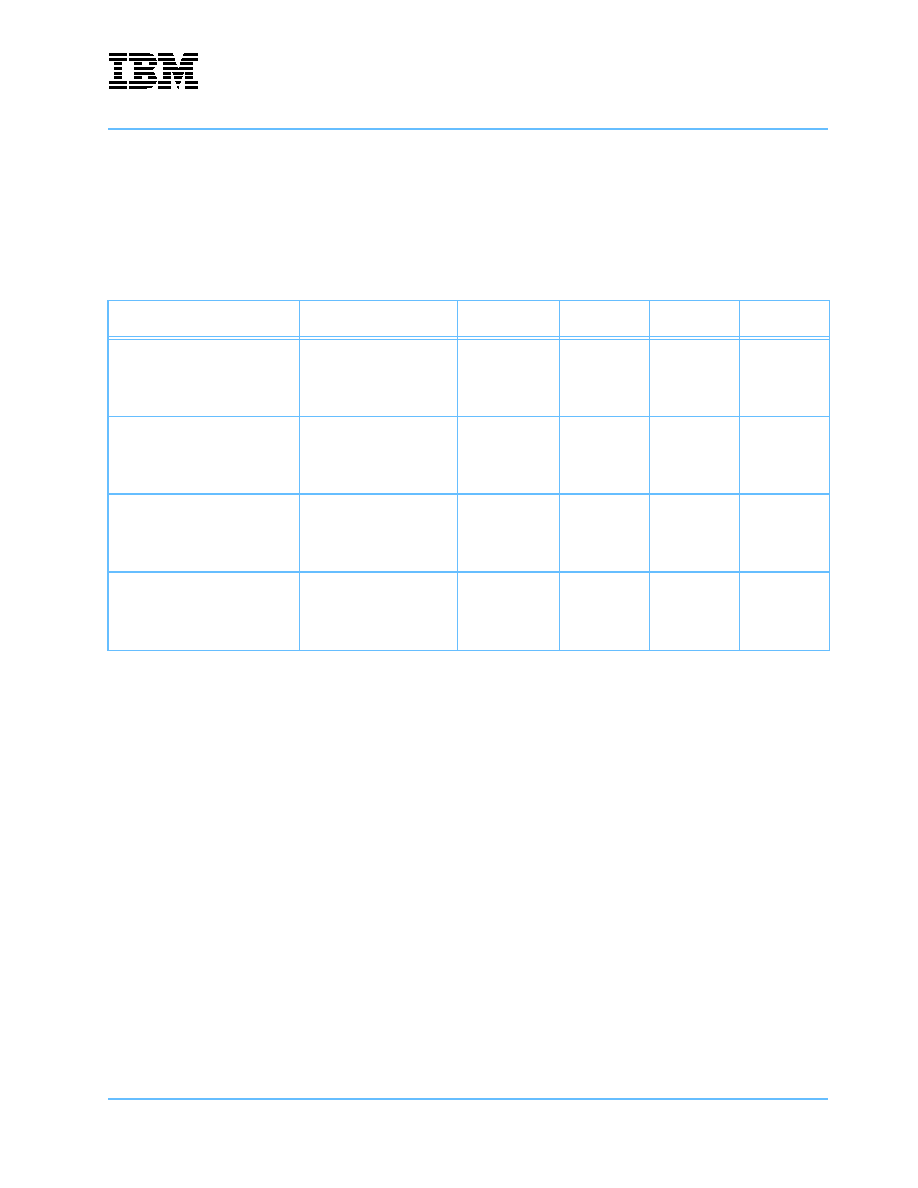

2.2.2 Port Expansion

Port expansion allows multiple islands to be interconnected in parallel, in a single stage, in order to increase

the number of physical ports, while keeping the port speed constant.

An external function must be provided to:

� Duplicate incoming packets and insert the correct bit map used by each island

� Merge traffic from different islands

The same external function can also instruct an island to transmit by controlling the send grants, according to

the queue-empty status, for instance.

Port expansion can be combined with speed expansion (internal and/or external) to increase port speed and

the number of ports at the same time.

PRS28.4G

IBM Packet Routing Switch

Architecture

Page 24 of 131

prs28.04.fm

February 6, 2001

.

Figure 4: Single Stage Port Expansion Block Diagram

Buffer

Control

Buffer

Control

Buffer

Control

Buffer

Control

32 Outputs

32 Inputs

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Functional Description

Page 25 of 131

3. Functional Description

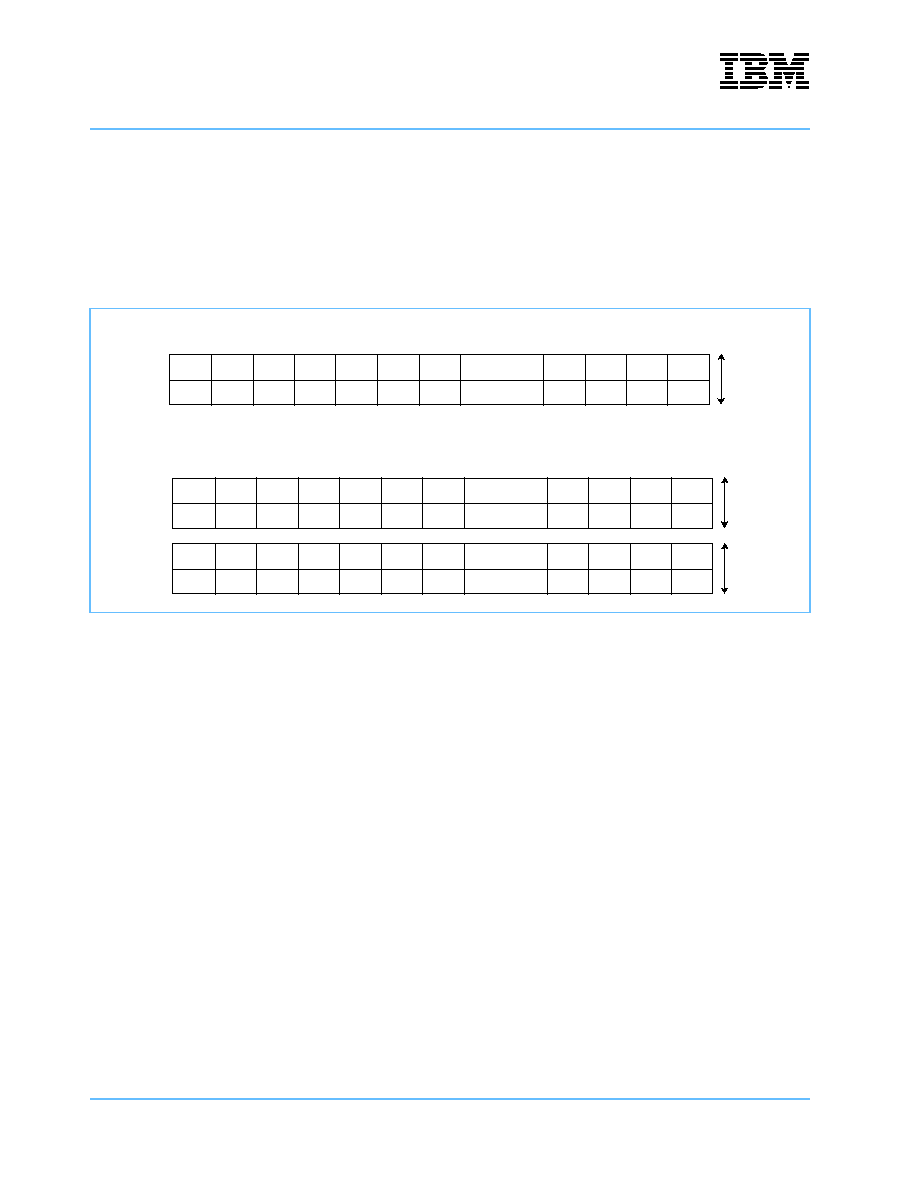

3.1 Logical Interface

As described in

Expansion Modes

on page 22, an PRS28.4G device consists of two switch islands running in

speed expansion. This leads to packet data being carried over an input or output port in two byte streams of

888 Mb/s, one related to the master island, and the other one to the slave island. Each byte stream carries

Logical Units (LU). An LU is a set of bytes belonging to the same packet and which are sent over one stream.

Depending on the expansion mode and packet length, an LU has a length L of 16 to 20 bytes or 32 to 40 (in

step of 2) bytes.

As represented in the figure below, the master LU always carries the packet routing information, or header

bytes, indicated by H0, H1 and H2.

When running in either internal or external speed expansion, two ports are grouped to form a 3.54Gb/s port.

Depending on the port and chip configuration, a 1.77Gb/s port can run either as a master port or a slave port:

� The master port is composed of two streams, one master, which carries the packet header information

and data bytes, and one slave, which carries data bytes only.

� The slave port is composed of two slave streams, which carry data bytes only.

The LUs of a packet are always transmitted or received at the same time on both streams of a port. Further-

more, the LUs of successive packets are transported one after the other, with no gap between packets.

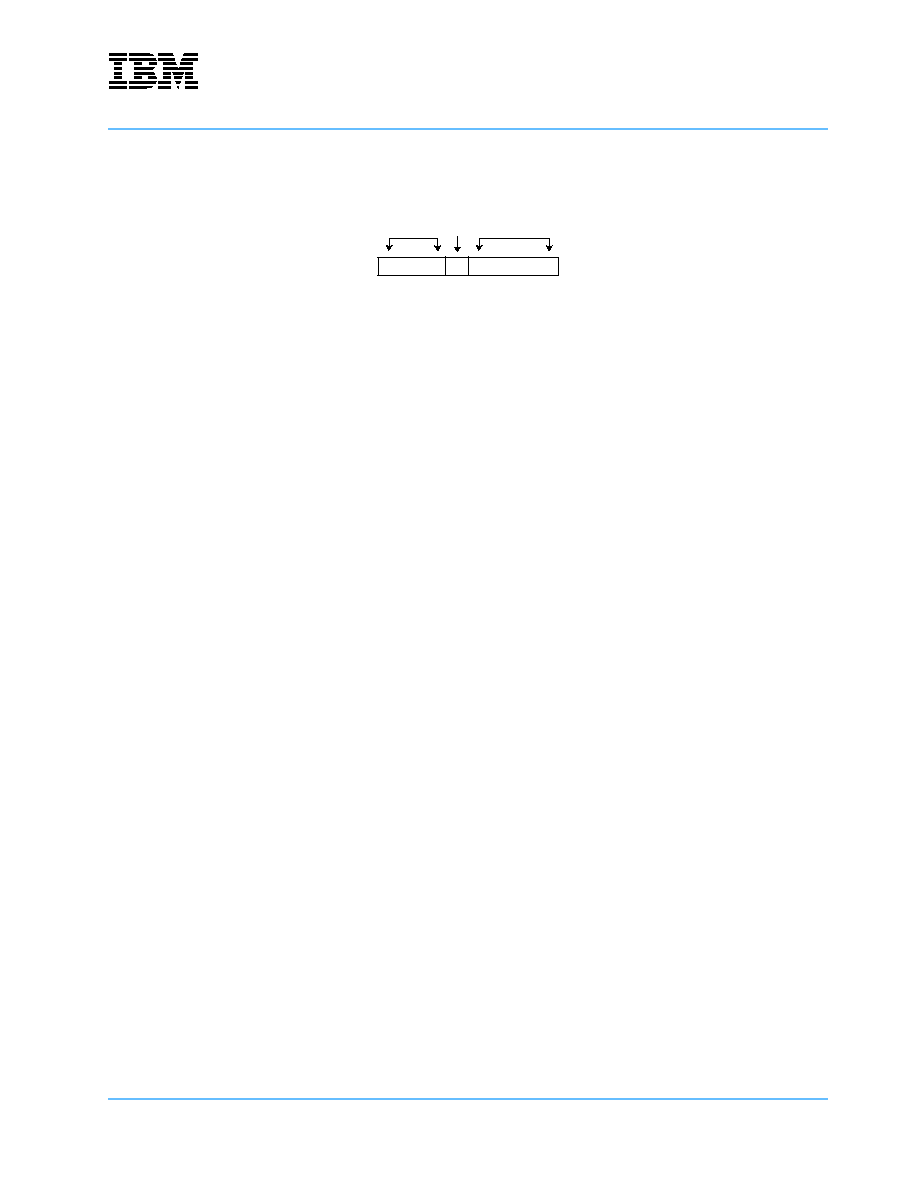

Figure 5: Packet Format 1.77 Gb/s Port

Figure 6: Packet Format for 3.54 Gb/s Port

H0

H1

H2

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

W0

W1

W2

W3

W4

W5

W6

W(L-1)

D

D

. . .

. . .

. . .

Master LU

Slave LU

16 Bits

H0

H1

H2

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

W0

W1

W2

W3

W4

W5

W6

W(L-1)

D

D

. . .

. . .

. . .

Master LU

Slave LU

16 Bits

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

. . .

. . .

Master LU

Slave LU

16 Bits

Master Port

Slave Port

D

D

D

PRS28.4G

IBM Packet Routing Switch

Functional Description

Page 26 of 131

prs28.04.fm

February 6, 2001

3.1.1 Physical Interface

Within the device, an LU is transported in a stream of bytes at 111.1 MB/s. Externally, it is transported over

two bit streams of 444 Mb/s each. At chip-pin level, each bit stream interface is differential and complies with

the JEDEC JESD8-6 standard (HSTL).

Data bits are transferred across devices at a known frequency, and no companion clock is required.

However, bit-phase alignment is performed during the link synchronization phase.

The interface between the 9 ns and the 2.25 ns domains is handled by a data line interface, the Data Aligned

Serial Link (DASL).

� On the input side, the DASL deserializes the two bit streams into one byte stream. It also performs the

link synchronization to allow bit phase alignment and packet alignment.

� On the output side, the DASL serializes the byte stream into two bit streams.

An internal pico-processor (M3) performs the synchronization of all lines on all ports. A synchronization algo-

rithm running on the pico-processor performs the bit-phase alignment and packet alignment of all ports during

the synchronization phase (see

DASL Specification and Pico-Processor

on page 124). The synchronization

algorithm is downloaded into an internal instruction memory and is delivered along with the module. See

DASL Specification and Pico-Processor

on page 124 for more information.

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Functional Description

Page 27 of 131

During serialization and deserialization, a one byte stream is split into two bit streams, one carrying the even

bits, and the other the odd bits. Thus, a port consists of four differential pairs. The information and bit order

that each pair carries is given in the table below.

Note: The MASTER stream is carried by bits 2 and 3, and the SLAVE stream by bits 0 and 1.

This bit grouping guarantees bit transitions to perform the phase alignment during synchronization on SYNC

packets.

3.1.2 Packet Type

A packet can be one of the following types:

� A Data Packet that contains user data to be switched from input to output.

� A Control Packet that is used to communicate with the local processor.

� An Idle Packet that does not contain user data. Idle Packets are sent on a link when no data packet are

available, or to perform link synchronization.

3.1.2.1 Data Packets and Control Packets

Data Packets carry user data and Control Packets carry information for local processor communication. The

figure

Packet Format 1.77 Gb/s Port

on page 25 shows the format of a data and control packet without speed

expansion. A packet consists of 16-bit words, divided into a master stream and a slave stream.

The figure

Packet Format for 3.54 Gb/s Port

on page 25 shows the Data and Control Packet format with

speed expansion, either internal or external. In those configurations, the packet is transported over two

different ports, either in the same device or in separate devices, in four LUs. The master port receives the

master LU and a slave LU, and the slave port receives two slave LUs.

Data Packets have a priority that ranges from 0 (highest) to 3 (lowest). In addition, they also carry filtering

(color) information used for switchover support.

Control Packets do not have priority, but they carry filtering (color) information.

Table 2: Physical Bit Organization of a Port

Differential Pair

Information Carried

Bit Order

Data_0_Q and Data_0_QN

even number bits of the slave byte stream

b0 b2 b4 b6 of slave byte

Data_1_Q and Data_1_QN

odd number bits of the slave byte stream

b1 b3 b5 b7 of slave byte

Data_2_Q and Data_2_QN

even number bits of the master byte stream

b0 b2 b4 b6 of master byte

Data_3_Q and Data_3_QN

odd number bits of the master byte stream

b1 b3 b5 b7 of master byte

PRS28.4G

IBM Packet Routing Switch

Functional Description

Page 28 of 131

prs28.04.fm

February 6, 2001

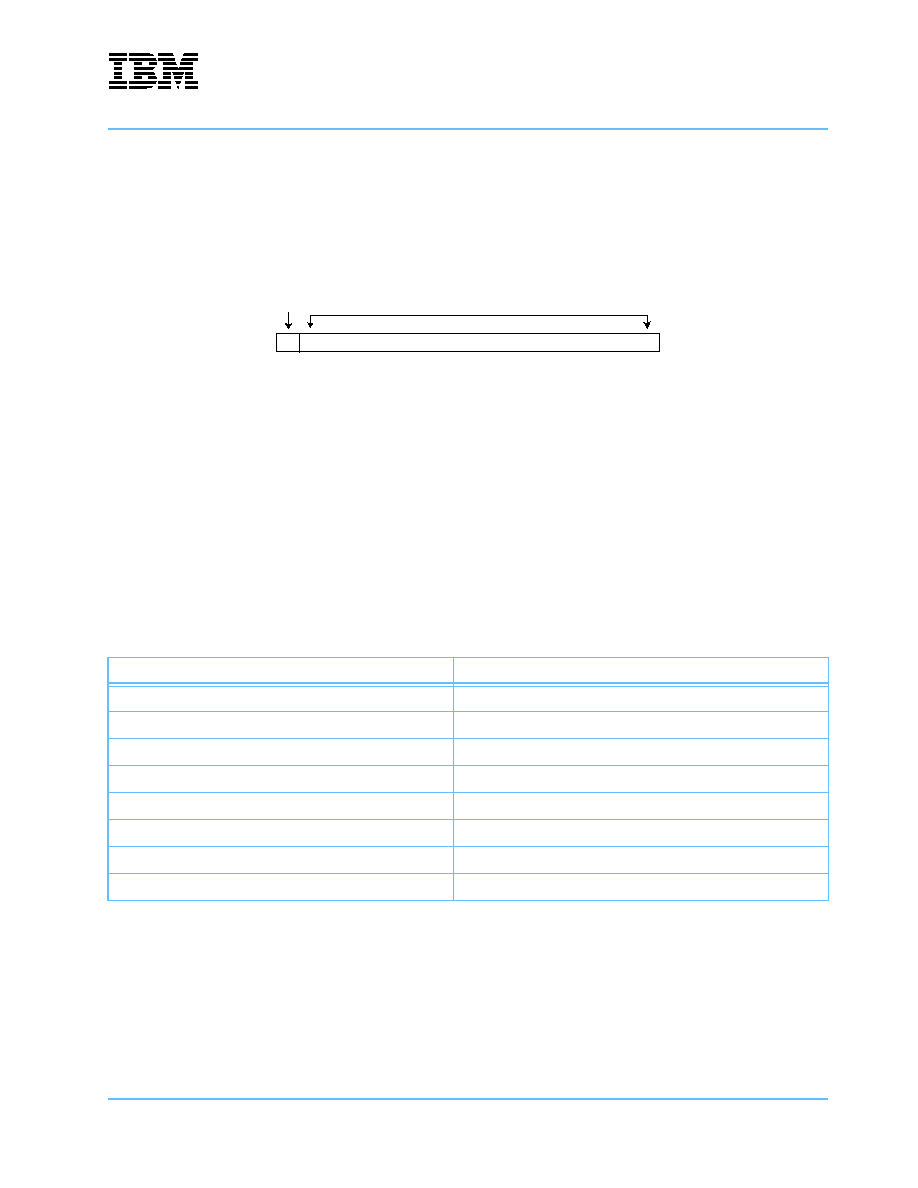

3.1.2.2 Idle Packets

The format of an Idle Packet without speed expansion (normal mode) is identical to data packet formats,

except that an Idle Packet contains two trailer-bytes in the last word of the packet.

Idle Packet format with speed expansion is similar to the data packet format for a 3.54 Gb/s port, except for

the trailer-bytes at the end of the packet.

Like Data Packets, Idle Packets also carry color information. However, in this case the color information is for

signaling (such as liveness messages, or to identify link synchronization packets, called Sync packets), in

addition to switchover support.

The payload bytes of nonsync Idle Packets - shown as `D' in the above two figures - are not processed and

are therefore irrelevant. However, in order to allow for dynamic phase alignment for the link interface receiver,

6 payload bytes are `CC'. All bytes of a non-sync Idle-packet LU transmitted by the PRS28.4G have the value

`00', with the following exceptions:

� Bytes 6 to 11 are all 0x`CC'.

� Byte 5 of a slave LU is 0x`07'.

� The last byte contains the trailer CRC.

� For a master LU, the header is defined according to the following sections.

3.1.2.3 Sync Packet

Sync packets are special types of Idle Packets, which allow link synchronization by providing bit transition

and packet delineation.

In accordance with the above definition of an Idle Packet, a Sync packet LU has all bytes equal to `CC',

except for the last byte, the trailer CRC byte, which is `33'.

The bit organization by the physical interface provides on a given differential pair, a sequence of `A', followed

by a `5'. This bit sequence provides the necessary bit transition while the `A to 5' transition allows for packet

delineation.

Figure 7: Idle Packet Format

H0

H1

H2

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

T

D

D

D

T

W0

W1

W2

W3

W4

W5

W6

W(L-1)

D

D

. . .

. . .

. . .

Master LU

Slave LU

16 Bits

Normal Mode

H0

H1

H2

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

T

D

D

D

T

W0

W1

W2

W3

W4

W5

W6

W(L-1)

D

D

. . .

. . .

. . .

Master LU

Slave LU

16 Bits

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

T

D

D

D

T

D

D

. . .

. . .

Slave LU

Slave LU

16 Bits

Master Port

Slave Port

D

D

D

Speed Expansion Mode

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Functional Description

Page 29 of 131

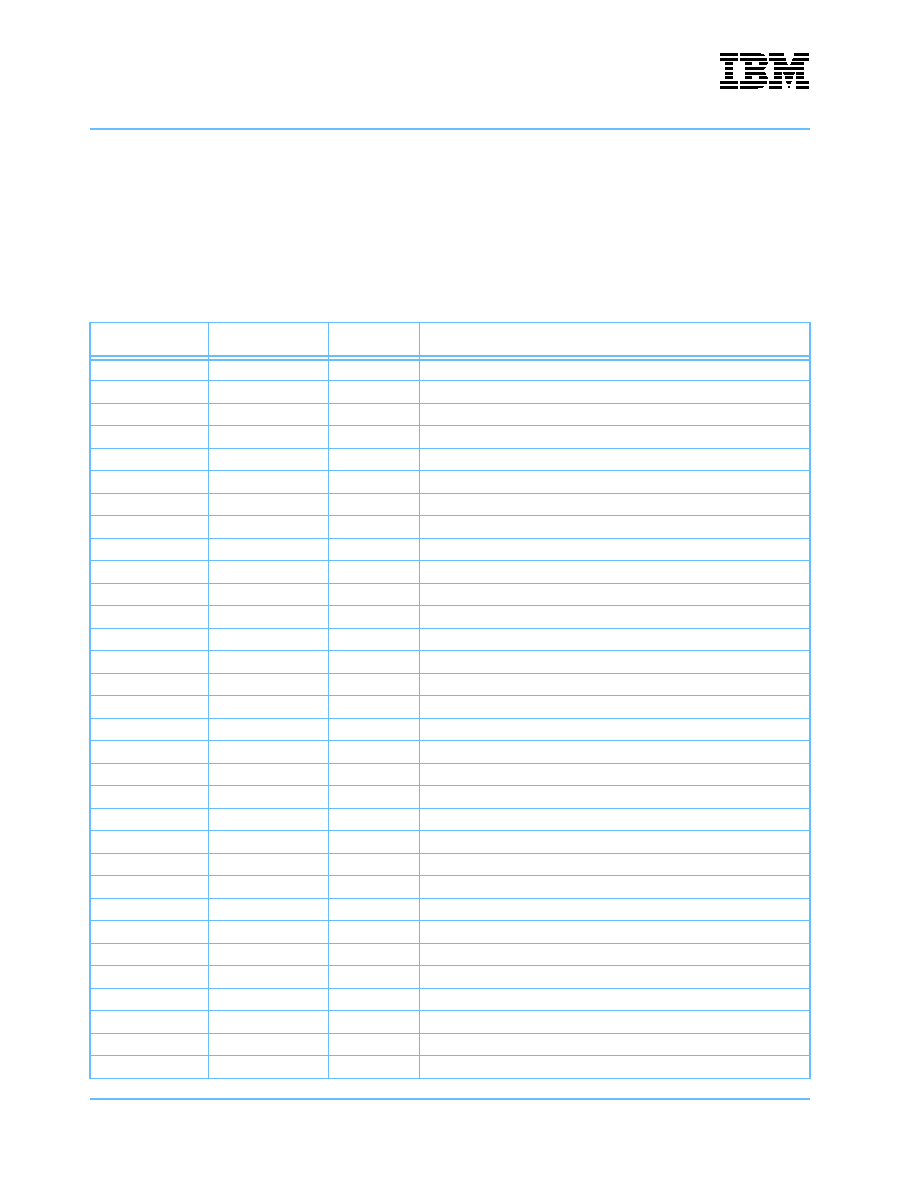

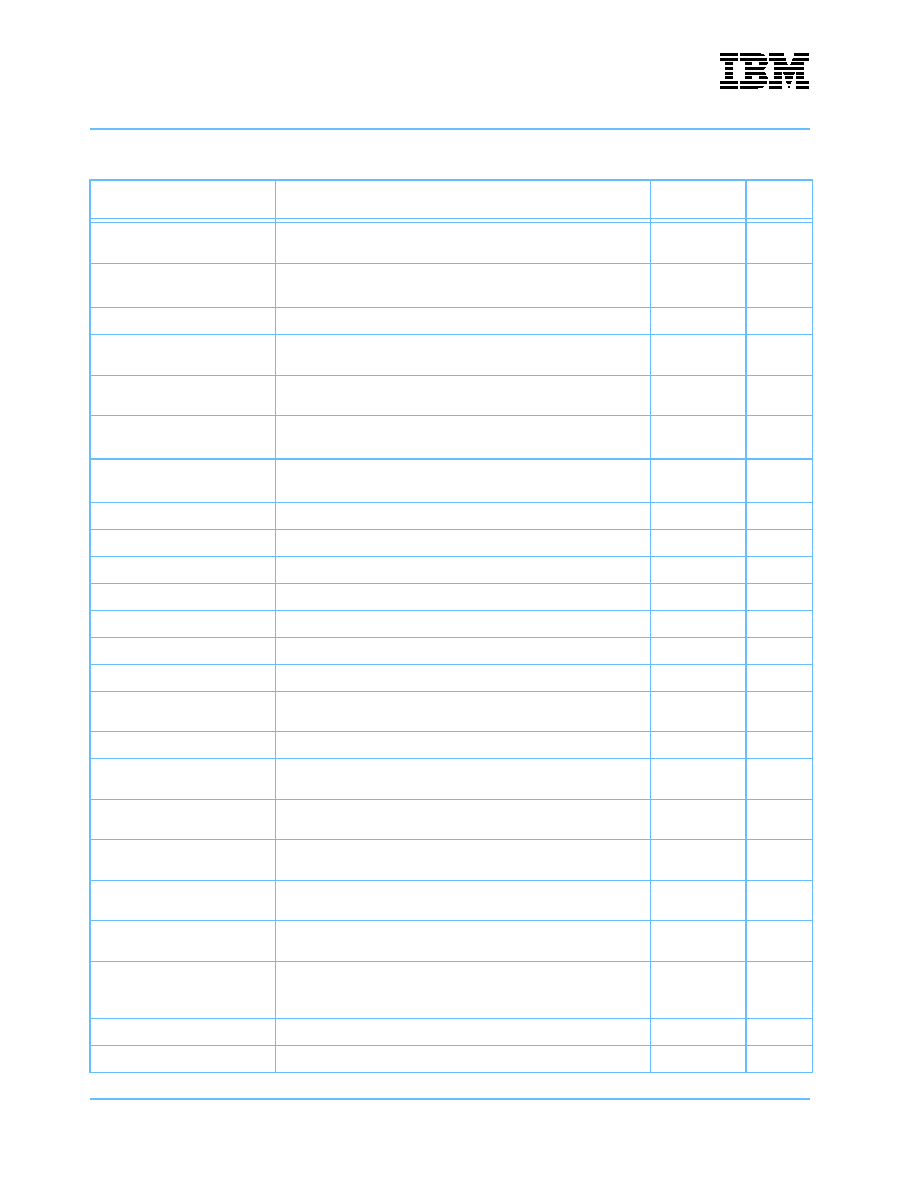

3.1.2.4 Logical Unit Lengths

As mentioned previously, an LU is the part of a packet transported over one 0.8Gb/s stream. The table below

lists, for all speed expansion modes, all possible LU lengths and their corresponding packet lengths, as well

as the total packet buffering provided.

All packets received and transmitted by the switch have the same length.

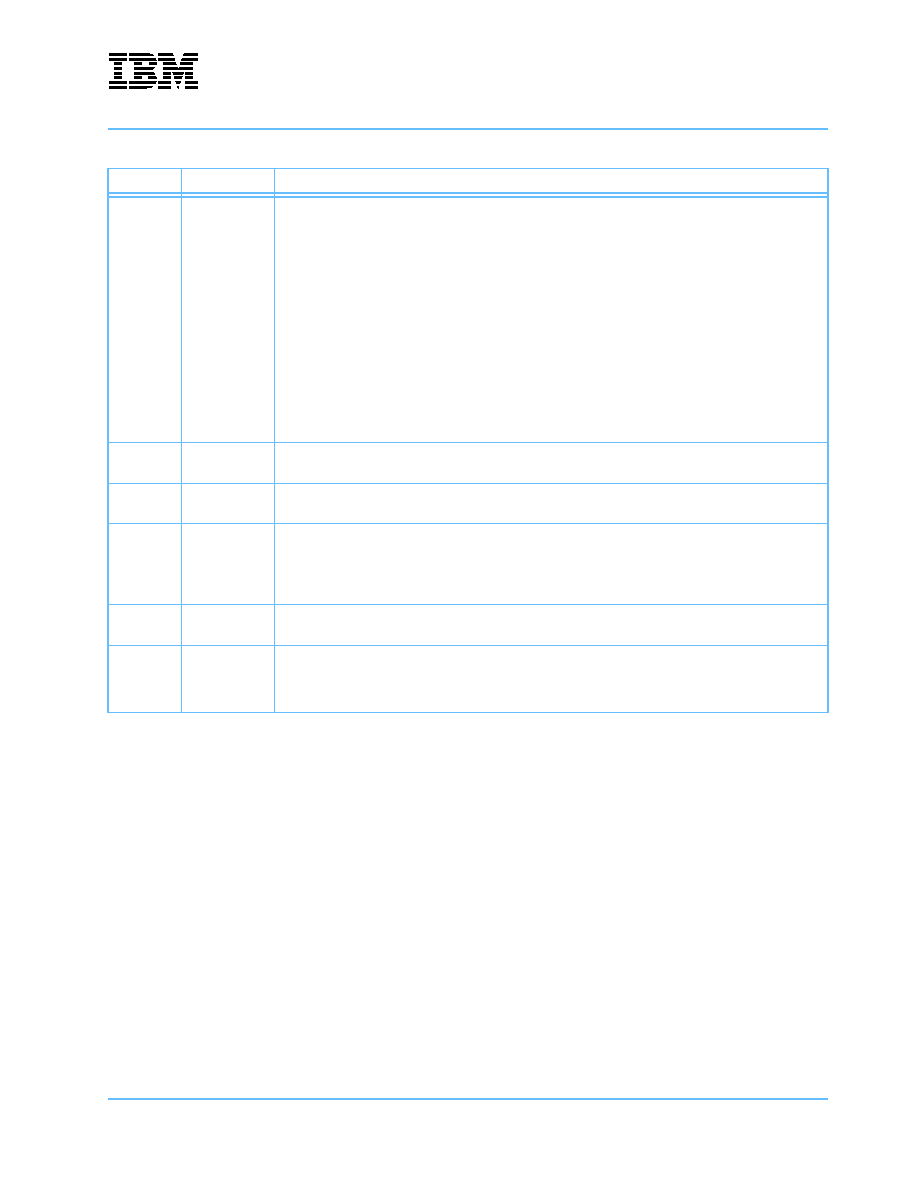

Table 3: Packet Length and Logical Unit Length

Speed Expansion Mode

Switch Configuration

Gb/s Per Port

Packet Length

(Bytes)

LU Size

(Bytes)

Total Buffering

(packets)

Single device, no internal speed

expansion

16 x 16

1.77

64

68

72

76

80

32

34

36

38

40

256

Single device, with internal speed

expansion

8 x 8

3.54

64

68

72

76

80

16

17

18

19

20

256

Two devices speed expanded, no

internal speed expansion

16 x 16

3.54

64

68

72

76

80

16

17

18

19

20

512

Two devices speed expanded, no

internal speed expansion

16 x 16

3.54

128

136

144

152

160

32

34

36

38

40

256

PRS28.4G

IBM Packet Routing Switch

Functional Description

Page 30 of 131

prs28.04.fm

February 6, 2001

3.2 Header Format

3.2.1 Header Byte H0 - Packet Qualifier

3.2.1.1 Parity Bit

The parity bit is an even parity calculated on the first three bytes of the header. Even parity assures that the

resulting number of `1' in the three byte header is even. This ensures that the SYNC cell has a valid header.

3.2.1.2 Reserved Bits

Reserved bits pass through the device unmodified.

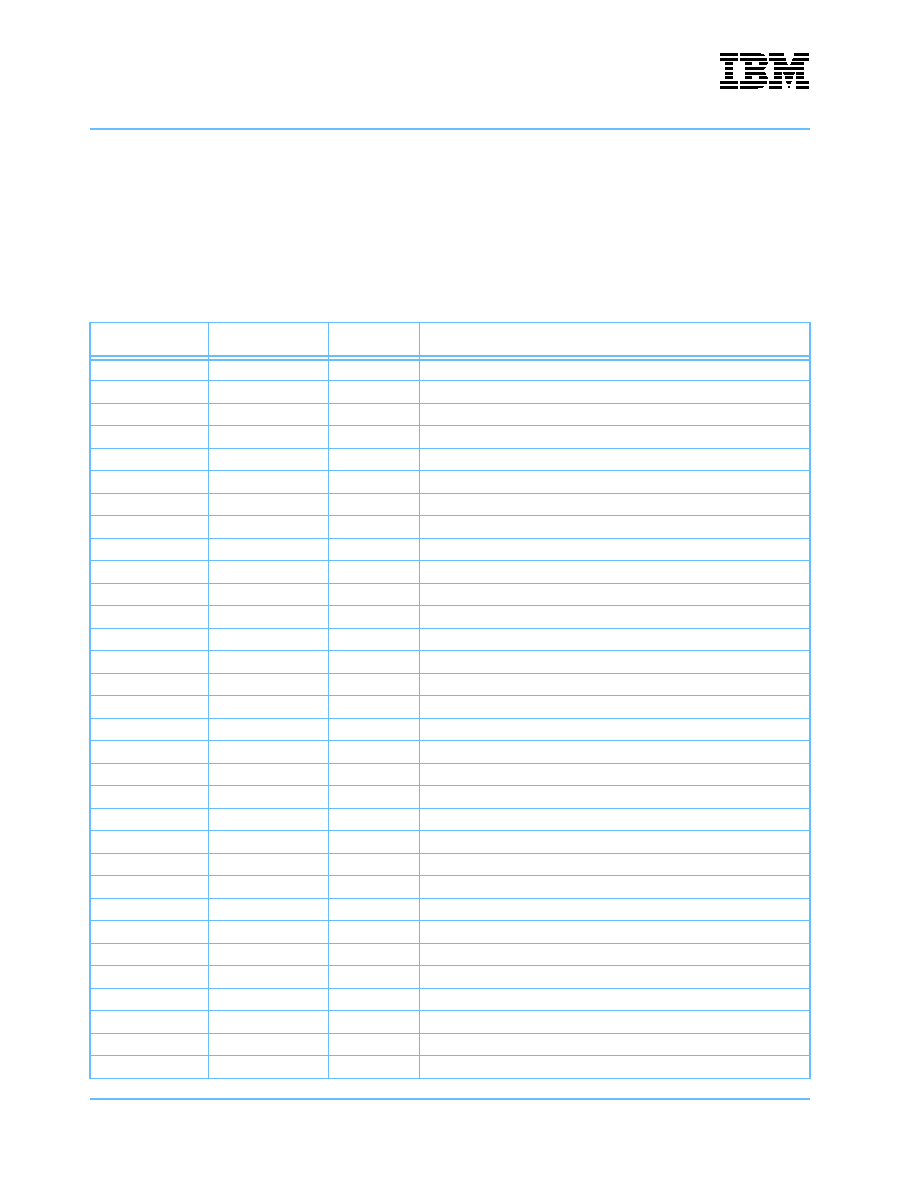

Table 4: Header Byte H0 for Idle Packets

(Bits 2 and 3

0)

Packet Type

Bit Position

0

1

2

3

4 and 5

6 and 7

Color bit

(1)

Parity

(1)

0

0

Color bits

(2)

Grant Priority

bits (2)

Blue Idle Packet

0

r

0

0

0 0

g g

Red Idle Packet

0

r

0

0

0 1

g g

Yellow Idle Packet

0

r

0

0

1 0

x x

Sync Packet

1

1

0

0

1 1

0 0

Reserved

1

1

1

0

r

r

r

r

0

0

0

0

0

0

0

0

0 0

0 1

1 0

1 1

x x

x x

x x

x x

Key:

x

value = 0 or 1

r

even parity bit on entire header (H0, H1, H2)

gg

value of grant sync bits (ignored for received packets - value = `00'

Table 5: Header Byte H0 for Data Packet

(Bits 2 and/or 3

0),

and Control Packet

(Bits 2 and/or 3

0; H1 and

H2

0)

Packet Type

Bit Position

0

1

2

3

4

5 and 6

7 and 8

Reserved

(1)

Parity

(1)

Active Bit

(1)

Backup Bit

(1)

Drop Bit

(1)

Reserved

(1)

Priority

(2)

Red Data/Control Packet

x

r

0

1

d

x

p p

Yellow Data/Control

Packet

x

r

1

0

d

x

p p

Blue Data/Control

Packet

x

r

1

1

d

x

p p

Key:

x

value = 0 or 1

r

even parity bit on entire header (H0, H1, H2)

gg

value of grant sync bits (ignored for received packets - value = `00'

PRS28.4G

IBM Packet Routing Switch

prs28.04.fm

February 6, 2001

Functional Description

Page 31 of 131

Data Packets will be transmitted in order of priority. A Control Packet is always transmitted before Data

Packets.

3.2.1.3 Active and Backup Bits

The Active and Backup bits are used to determine how the Bit Map Filter Mask is applied to the Bit Map Desti-

nation Address (header bytes H1 and H2) and to determine the traffic type (Red or Blue) of Data Packets.

The Bit Map Filter is a programmable register. The resulting masked destination bit map is used by the

PRS28.4G to route the packets to the appropriate destination(s), or to ignore the packet if the resulting bit

map is all zeros. Control Packet detection is performed before the Bit Map Filter is applied to the bit map

contained in the packet header.

3.2.1.4 Drop Bit

Incoming packets with the drop bit set will be dropped by the PRS28.4G when the number of packets in the

destination output queue and/or the shared memory has exceeded the programmable thresholds for the

corresponding priority. For multicast packets, the packet is dropped only if the shared memory threshold is

crossed. The output queue full information is updated once every sequencer cycle, so all input controllers see