8304AM-01

www.icst.com/products/hiperclocks.html

REV. D MAY 23, 2005

1

Integrated

Circuit

Systems, Inc.

ICS8304-01

L

OW

S

KEW

, 1-

TO

-4

LVCMOS / LVTTL I

NVERTING

F

ANOUT

B

UFFER

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

ICS8304-01

8-Lead SOIC

3.8mm x 4.8mm x 1.47mm package body

M Package

Top View

V

DDO

V

DD

CLK

GND

1

2

3

4

nQ0

nQ1

nQ2

nQ3

CLK

nQ3

nQ2

nQ1

nQ0

8

7

6

5

G

ENERAL

D

ESCRIPTION

The ICS8304-01 is a low skew, 1-to-4 Invert-

ing Fanout B u f fe r a n d a m e m b e r o f t h e

HiPerClock S TM

family of High Perfor mance

Clock Solutions from ICS. The ICS8304-01

is characterized at full 3.3V for input V

DD

, and

mixed 3.3V and 2.5V for output operating supply modes

(V

DDO

). Guaranteed output and par t-to-par t skew char-

acteristics make the ICS8304-01 ideal for those clock

distribution applications demanding well defined per-

for mance and repeatability.

F

EATURES

� 4 LVCMOS / LVTTL outputs

� LVCMOS/LVTTL clock input

� Maximum output frequency: 166MHz

� Output skew: 50ps (maximum)

� Part-to-part skew: 600ps (maximum)

� Small 8 lead SOIC package saves board space

� 3.3V input, outputs may be either 3.3V or 2.5V supply modes

� 0�C to 70�C ambient operating temperature

� Lead-Free package fully RoHS compliant

HiPerClockSTM

ICS

8304AM-01

www.icst.com/products/hiperclocks.html

REV. D MAY 23, 2005

3

Integrated

Circuit

Systems, Inc.

ICS8304-01

L

OW

S

KEW

, 1-

TO

-4

LVCMOS / LVTTL I

NVERTING

F

ANOUT

B

UFFER

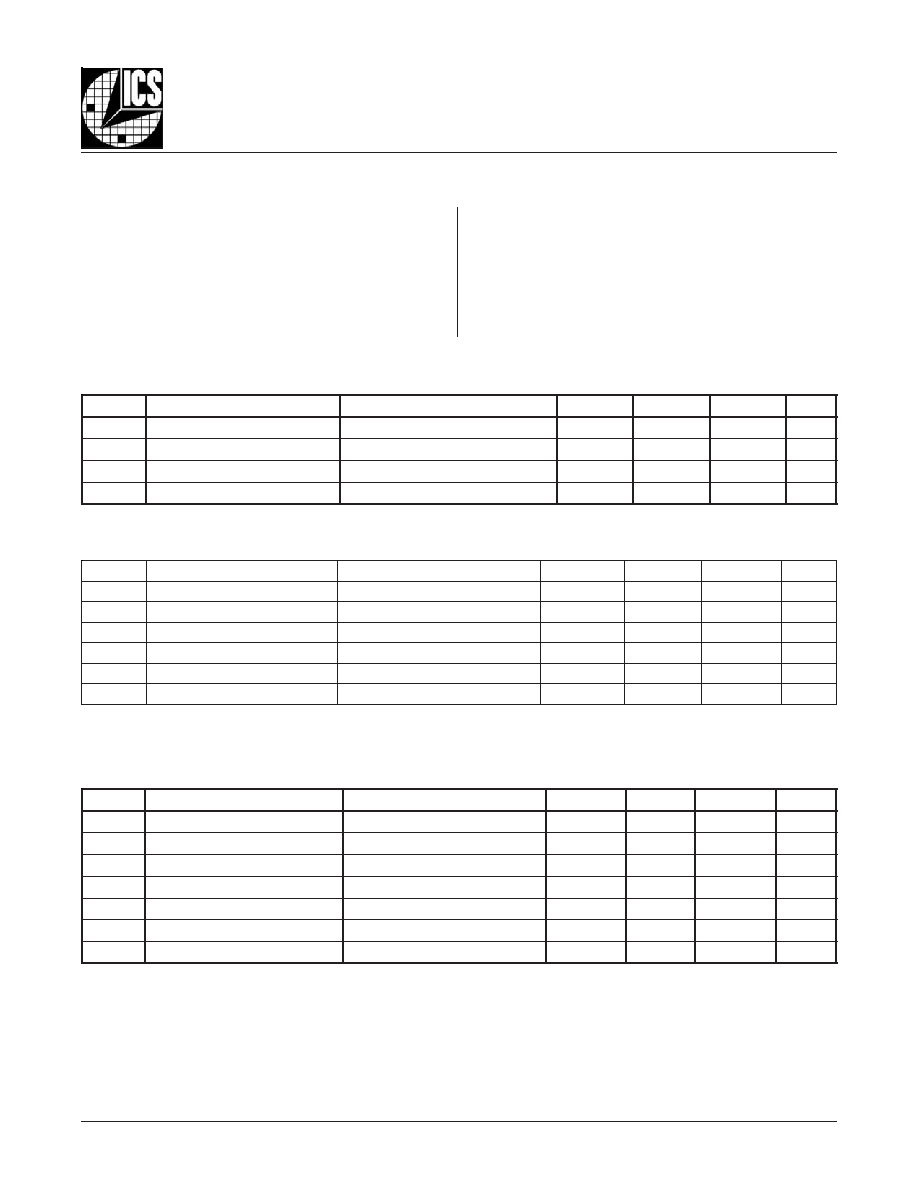

T

ABLE

3A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= V

DDO

= 3.3V�5%, T

A

= 0�C

TO

70�C

T

ABLE

3B. LVCMOS / LVTTL DC C

HARACTERISTICS

,

V

DD

= V

DDO

= 3.3V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

r

e

w

o

P

t

u

p

t

u

O

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

5

1

A

m

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

8

A

m

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

2

V

D

D

3

.

0

+

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

3

.

0

-

3

.

1

V

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

5

-

A

�

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

6

.

2

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

5

.

0

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

O

D

D

,

"

n

o

i

t

c

e

S

n

o

i

t

a

m

r

o

f

n

I

t

n

e

m

e

r

u

s

a

e

M

r

e

t

e

m

a

r

a

P

e

e

S

.

2

/

.

"

t

i

u

c

r

i

C

t

s

e

T

d

a

o

L

t

u

p

t

u

O

V

3

.

3

"

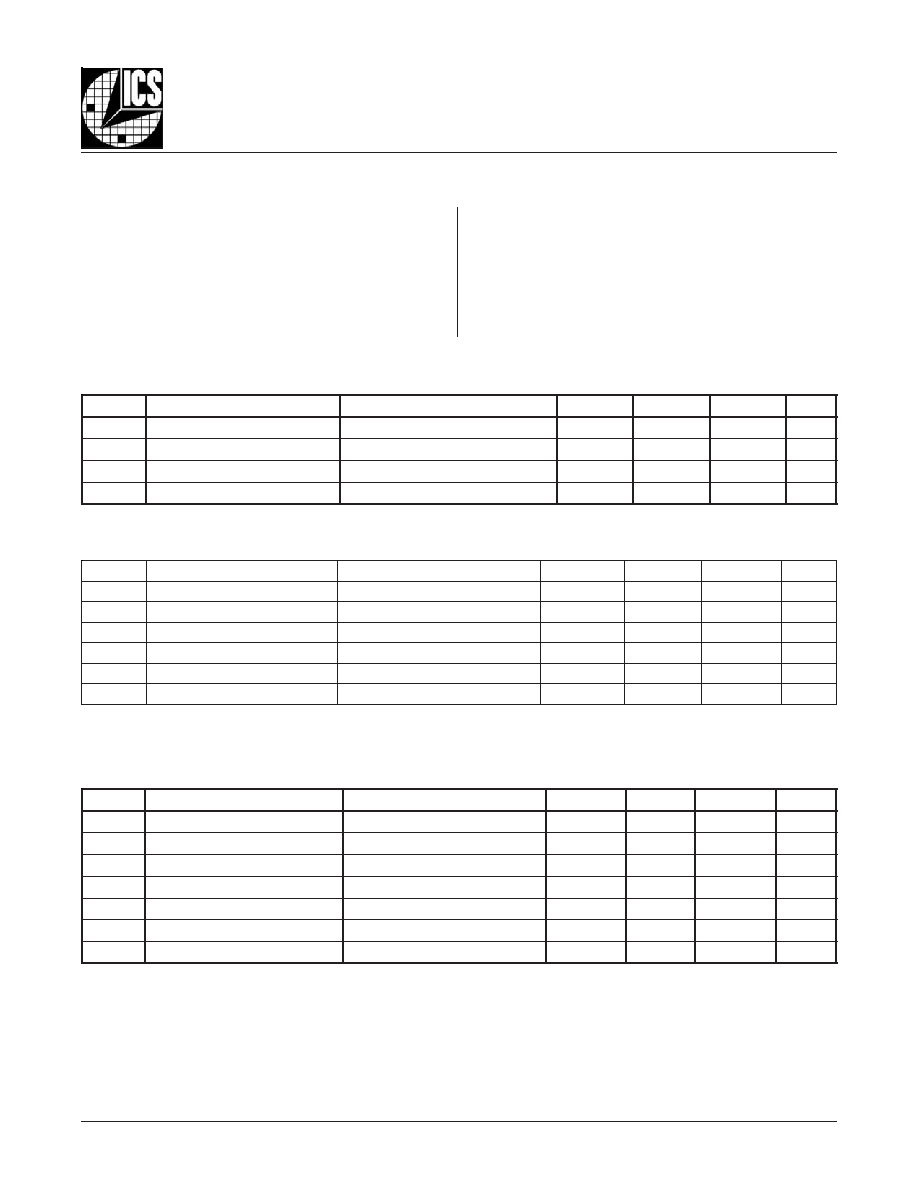

T

ABLE

4A. AC C

HARACTERISTICS

,

V

DD

= V

DDO

= 3.3V�5%, T

A

= 0�C

TO

70�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

f

X

A

M

y

c

n

e

u

q

e

r

F

t

u

p

t

u

O

6

6

1

z

H

M

t

D

P

1

E

T

O

N

;

y

a

l

e

D

n

o

i

t

a

g

a

p

o

r

P

z

H

M

6

6

1

3

.

2

5

.

3

s

n

t

)

o

(

k

s

4

,

2

E

T

O

N

;

w

e

k

S

t

u

p

t

u

O

0

5

s

p

t

)

p

p

(

k

s

4

,

3

E

T

O

N

;

w

e

k

S

t

r

a

P

-

o

t

-

t

r

a

P

0

0

6

s

p

t

R

e

m

i

T

e

s

i

R

t

u

p

t

u

O

%

0

7

o

t

%

0

3

0

5

2

0

0

5

s

p

t

F

e

m

i

T

ll

a

F

t

u

p

t

u

O

%

0

7

o

t

%

0

3

0

5

2

0

0

5

s

p

c

d

o

e

l

c

y

C

y

t

u

D

t

u

p

t

u

O

f

z

H

M

6

6

1

0

4

0

6

%

.

e

s

i

w

r

e

h

t

o

d

e

t

o

n

s

s

e

l

n

u

z

H

M

6

6

1

t

a

d

e

r

u

s

a

e

m

s

r

e

t

e

m

a

r

a

p

ll

A

V

m

o

r

f

d

e

r

u

s

a

e

M

:

1

E

T

O

N

D

D

V

o

t

t

u

p

n

i

e

h

t

f

o

2

/

O

D

D

f

o

e

g

d

e

g

n

i

s

i

r

e

h

t

m

o

r

f

d

e

r

u

s

a

e

M

.

t

u

p

t

u

o

e

h

t

f

o

2

/

.

t

u

p

t

u

o

e

h

t

f

o

e

g

d

e

g

n

il

l

a

f

e

h

t

o

t

t

u

p

n

i

e

h

t

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

2

E

T

O

N

V

t

a

d

e

r

u

s

a

e

M

O

D

D

.

2

/

s

e

g

a

t

l

o

v

y

l

p

p

u

s

e

m

a

s

e

h

t

t

a

g

n

i

t

a

r

e

p

o

s

e

c

i

v

e

d

t

n

e

r

e

f

f

i

d

n

o

s

t

u

p

t

u

o

n

e

e

w

t

e

b

w

e

k

s

s

a

d

e

n

i

f

e

D

:

3

E

T

O

N

d

e

r

u

s

a

e

m

e

r

a

s

t

u

p

t

u

o

e

h

t

,

e

c

i

v

e

d

h

c

a

e

n

o

s

t

u

p

n

i

f

o

e

p

y

t

e

m

a

s

e

h

t

g

n

i

s

U

.

s

n

o

i

t

i

d

n

o

c

d

a

o

l

l

a

u

q

e

h

t

i

w

d

n

a

V

t

a

O

D

D

.

2

/

.

5

6

d

r

a

d

n

a

t

S

C

E

D

E

J

h

t

i

w

e

c

n

a

d

r

o

c

c

a

n

i

d

e

n

i

f

e

d

s

i

r

e

t

e

m

a

r

a

p

s

i

h

T

:

4

E

T

O

N

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DD

X

4.6V

Inputs, V

DD

-0.5V to V

DD

+ 0.5 V

Outputs, V

DDO

-0.5V to V

DDO

+ 0.5V

Package Thermal Impedance,

JA

112.7�C/W (0 lfpm)

Storage Temperature, T

STG

-65�C to 150�C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.