854058AG

www.icst.com/products/hiperclocks.html

REV. A APRIL 8, 2004

1

Integrated

Circuit

Systems, Inc.

ICS854058

8:1

D

IFFERENTIAL

-

TO

-LVDS C

LOCK

M

ULTIPLEXER

PRELIMINARY

G

ENERAL

D

ESCRIPTION

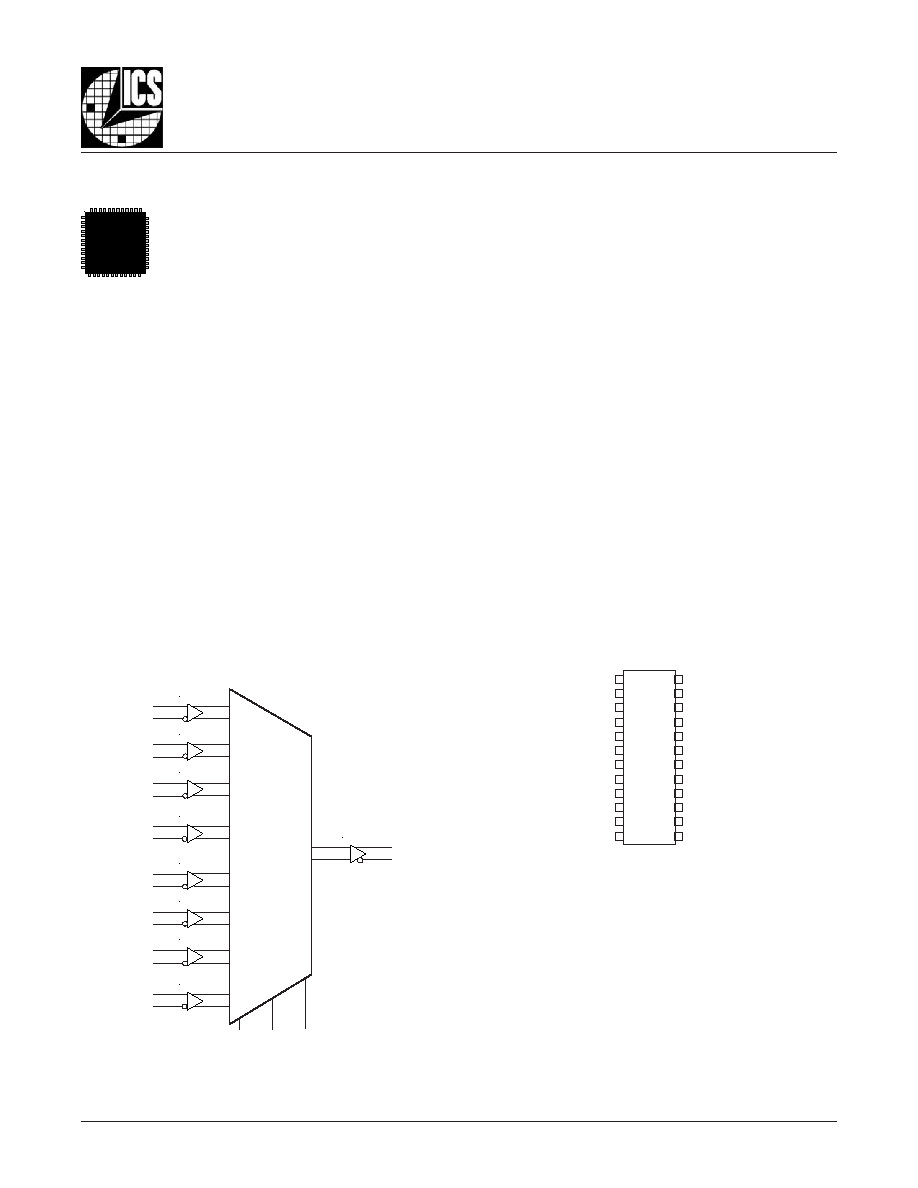

The ICS854058 is an 8:1 Differential-to-LVDS Clock

Multiplexer which can operate up to 2.5GHz and

is a member of the HiPerClockSTM family of High

Performance Clock Solutions from ICS. The

ICS854058 has 8 selectable differential clock in-

puts. The PCLK, nPCLK input pairs can accept LVPECL, LVDS,

CML or SSTL levels. The fully differential architecture and low

propagation delay make it ideal for use in clock distribution cir-

cuits. The select pins have internal pulldown resistors. The SEL2

pin is the most significant bit and the binary number applied to

the select pins will select the same numbered data input (i.e.,

000 selects PCLK0, nPCLK0).

F

EATURES

� High speed 8:1 differential multiplexer

� 1 differential LVDS output

� 8 selectable differential PCLK, nPCLK inputs

� PCLKx, nPCLKx pairs can accept the following

differential input levels: LVPECL, LVDS, CML, SSTL

� Maximum output frequency: 2.5GHz

� Translates any single ended input signal to

LVDS levels with resistor bias on nPCLKx input

� Part-to-part skew: TBD

� Propagation delay: 595ps (typical)

� Supply voltage range: 3.135V to 3.465V

� -40�C to 85�C ambient operating temperature

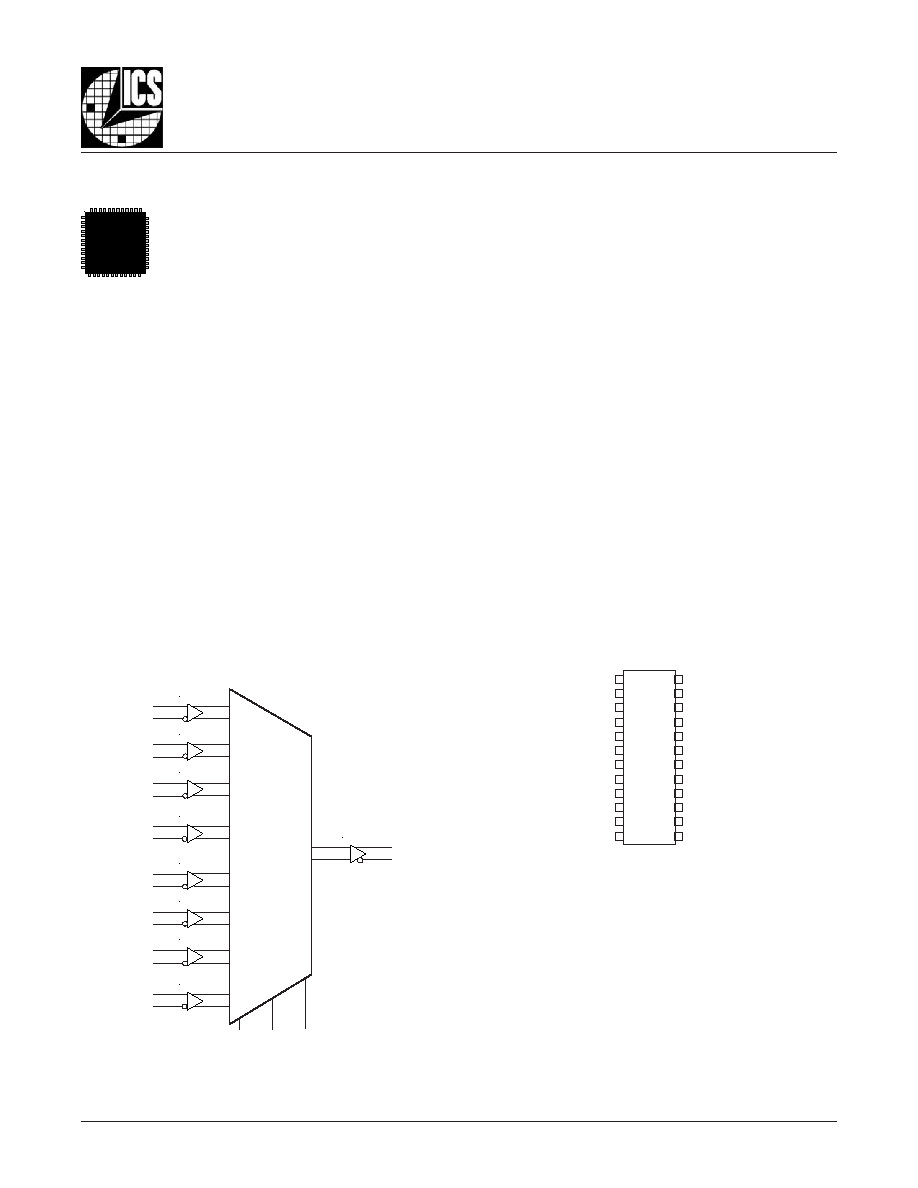

B

LOCK

D

IAGRAM

P

IN

A

SSIGNMENT

HiPerClockSTM

ICS

ICS854058

24-Lead, 173-MIL TSSOP

4.4mm x 7.8mm x 0.92mm body package

G Package

Top View

PCLK0

nPCLK0

PCLK1

nPCLK1

V

DD

SEL0

SEL1

SEL2

PCLK2

nPCLK2

PCLK3

nPCLK3

PCLK7

nPCLK7

PLCK6

nPCLK6

V

DD

Q0

nQ0

GND

PCLK5

nPCLK5

PCLK4

nPCLK4

PCLK0

nPCLK0

PCLK1

nPCLK1

PCLK2

nPCLK2

PCLK3

nPCLK3

000

011

001

010

SEL1 SEL0

Q0

nQ0

PCLK4

nPCLK4

PCLK5

nPCLK5

PCLK6

nPCLK6

PCLK7

nPCLK7

SEL2

100

111

101

110

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

854058AG

www.icst.com/products/hiperclocks.html

REV. A APRIL 8, 2004

4

Integrated

Circuit

Systems, Inc.

ICS854058

8:1

D

IFFERENTIAL

-

TO

-LVDS C

LOCK

M

ULTIPLEXER

PRELIMINARY

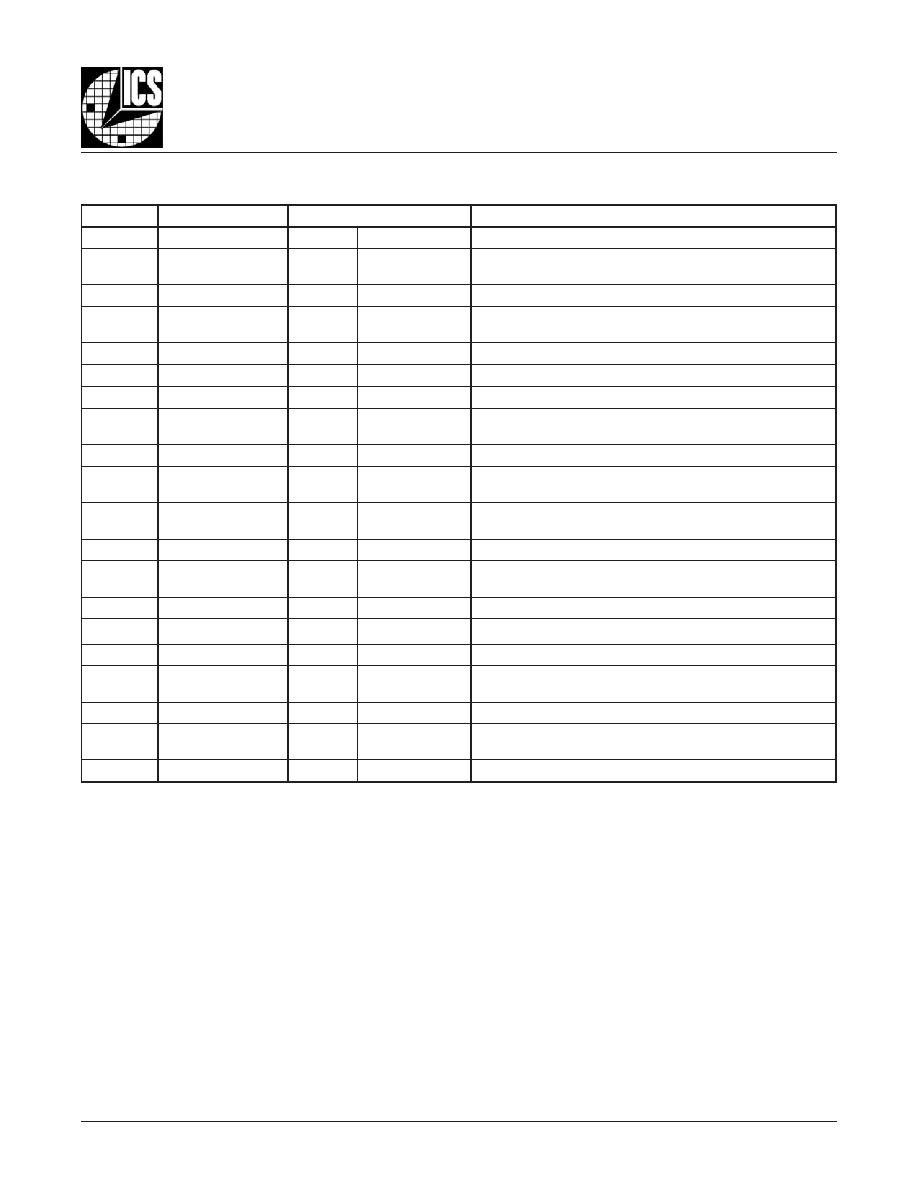

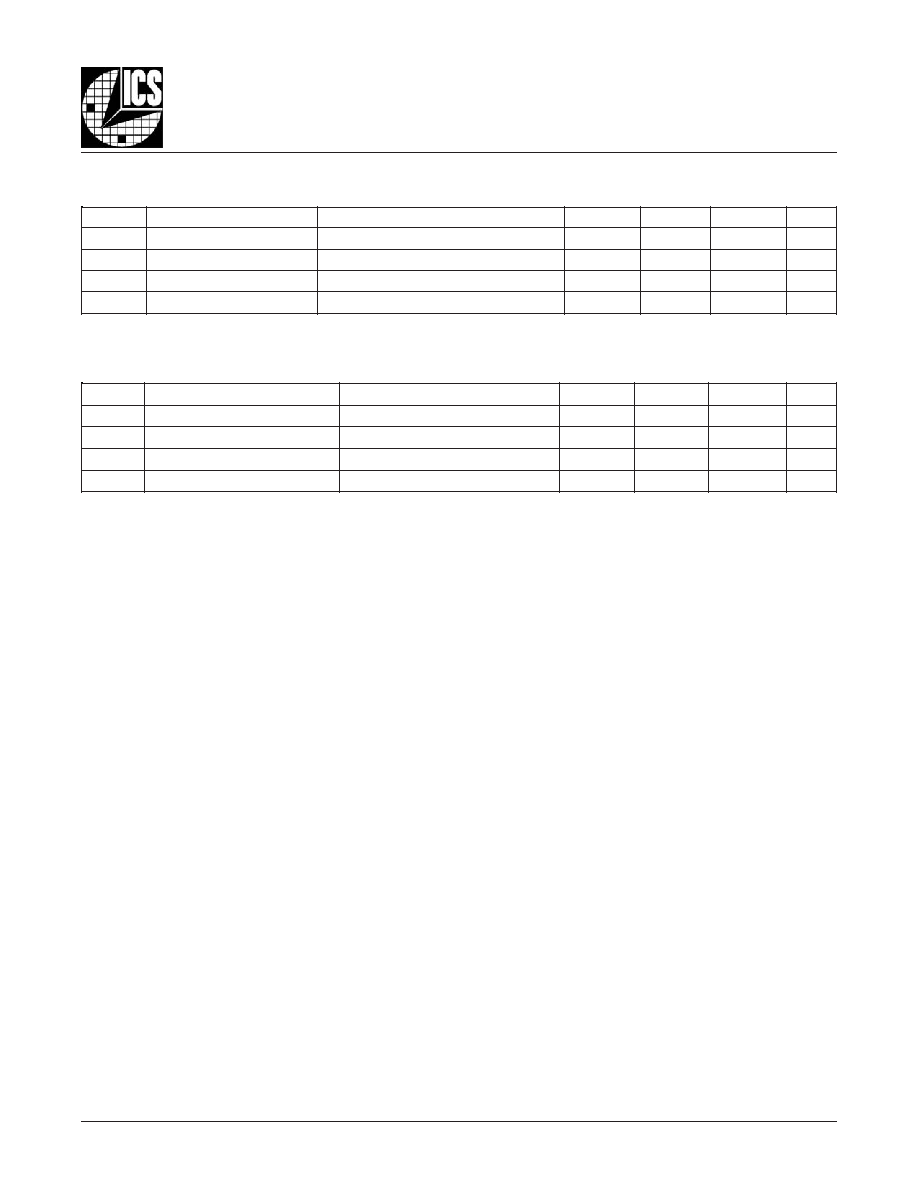

T

ABLE

4A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DD

= 3.3V � 5%

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

e

v

i

t

i

s

o

P

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

8

6

A

m

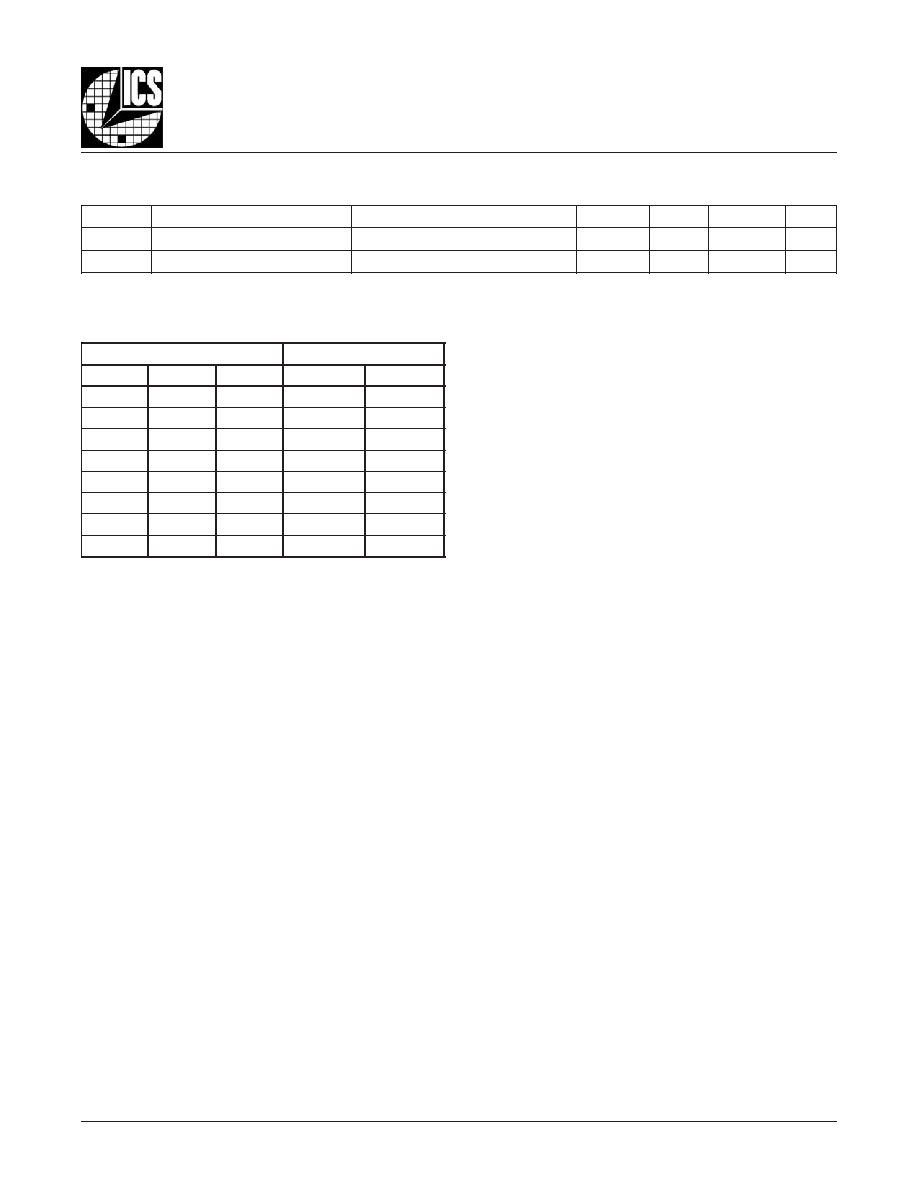

T

ABLE

4C. LVPECL DC C

HARACTERISTICS

,

V

DD

= 3.3V � 5%

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

7

K

L

C

P

:

0

K

L

C

P

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

7

K

L

C

P

n

:

0

K

L

C

P

n

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

7

K

L

C

P

:

0

K

L

C

P

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

1

-

A

�

7

K

L

C

P

n

:

0

K

L

C

P

n

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

5

1

-

A

�

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

5

1

.

0

V

V

R

M

C

2

,

1

E

T

O

N

;

e

g

a

t

l

o

V

t

u

p

n

I

e

d

o

M

n

o

m

m

o

C

2

.

1

+

D

N

G

V

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

1

E

T

O

N

H

I

.

V

s

i

x

K

L

C

P

n

,

x

K

L

C

P

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

e

l

g

n

i

s

r

o

F

:

2

E

T

O

N

D

D

.

V

3

.

0

+

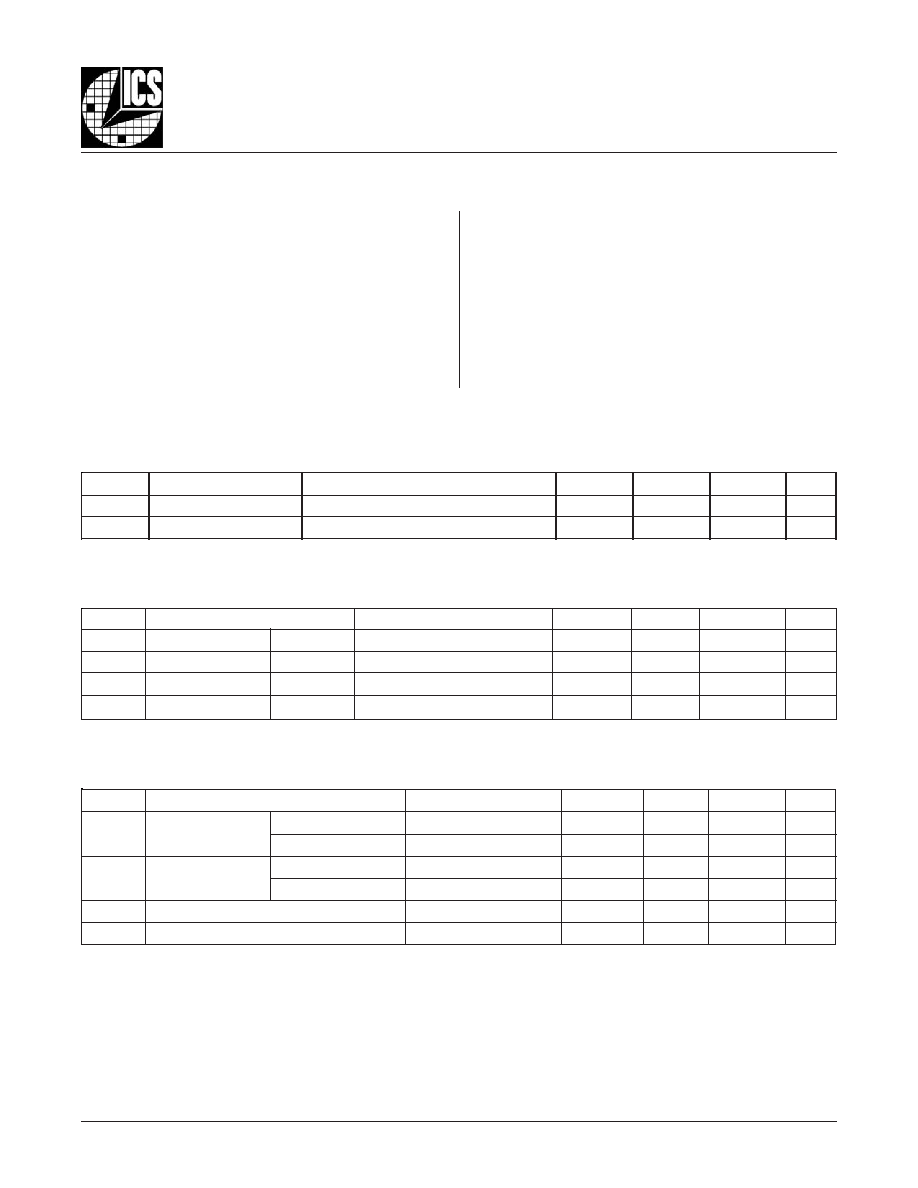

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DD

4.6V

Inputs, V

I

-0.5V to V

DD

+ 0.5 V

Outputs, I

O

Continuous Current

10mA

Surge Current

15mA

Package Thermal Impedance,

JA

70�C/W (0 lfpm)

Storage Temperature, T

STG

-65�C to 150�C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

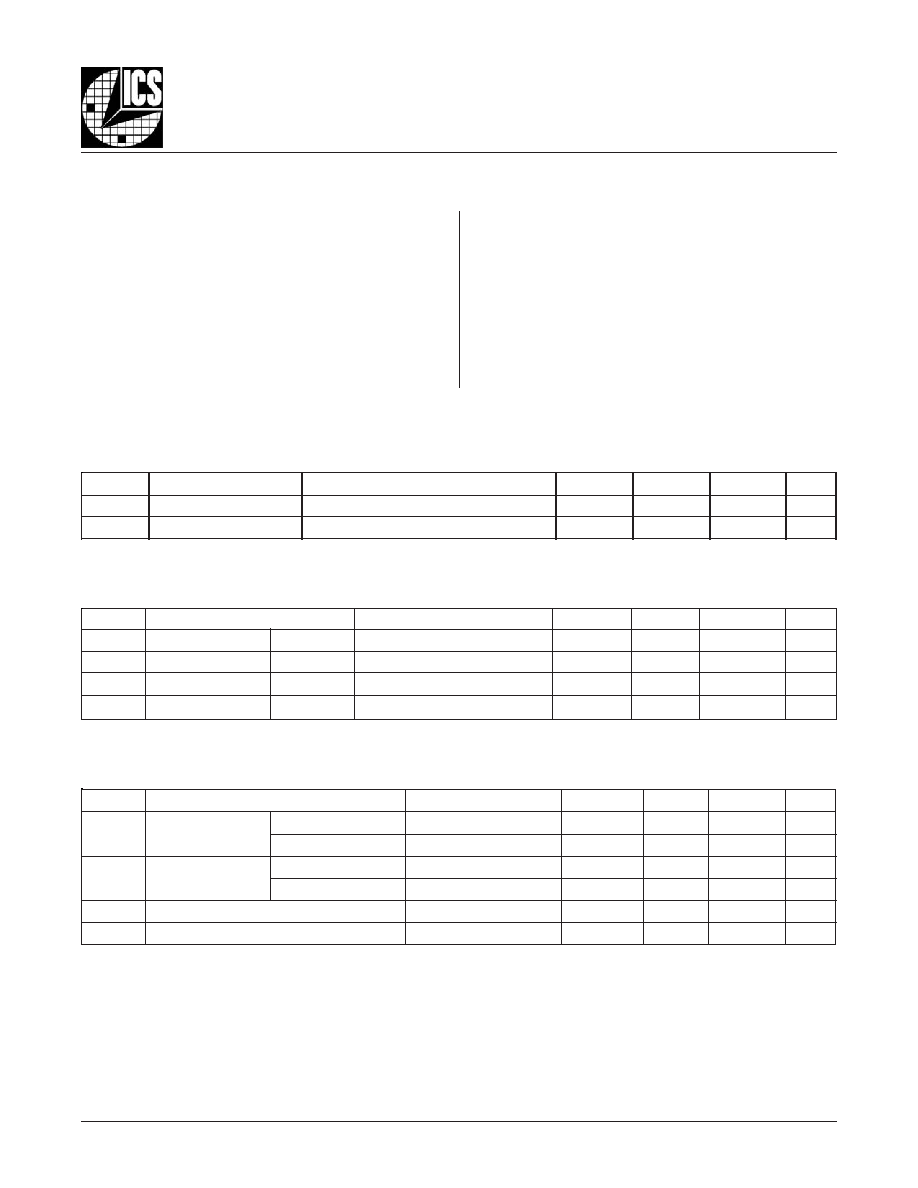

T

ABLE

4B. LVCMOS/LVTTL DC C

HARACTERISTICS

,

V

DD

= 3.3V�5%, T

A

= -40�C

TO

85�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

2

L

E

S

:

0

L

E

S

2

V

D

D

3

.

0

+

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

2

L

E

S

:

0

L

E

S

3

.

0

-

8

.

0

V

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

2

L

E

S

:

0

L

E

S

V

D

D

V

=

N

I

V

5

6

4

.

3

=

0

5

1

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

2

L

E

S

:

0

L

E

S

V

D

D

V

,

V

5

6

4

.

3

=

N

I

V

0

=

0

1

-

A

�