87931BYI

www.icst.com/products/hiperclocks.html

REV. A JUNE 23, 2003

1

Integrated

Circuit

Systems, Inc.

ICS87931I

L

OW

S

KEW

, 1-

TO

-6

LVCMOS/LVTTL C

LOCK

M

ULTIPLIER

/Z

ERO

D

ELAY

B

UFFER

G

ENERAL

D

ESCRIPTION

The ICS87931I is a low voltage, low skew

LVCMOS/LVTTL Clock Multiplier/ Zero Delay

Buffer and a member of the HiPerClockSTM family

of High Performance Clock Solutions from ICS.

With output frequencies up to 150MHz, the

ICS87931I is targeted for high performance clock applications.

Along with a fully integrated PLL, the ICS87931I contains fre-

quency configurable outputs and an external feedback input for

regenerating clocks with "zero delay".

Selectable clock inputs, CLK1 and differential CLK0, nCLK0

support redundant clock applications. The CLK_SEL input de-

termines which reference clock is used. The output divider val-

ues of Bank A, B and C are controlled by the DIV_SELA,

DIV_SELB and DIV_SELC, respectively.

For test and system debug purposes, the PLL_SEL input al-

lows the PLL to be bypassed. When LOW, the nMR input re-

sets the internal dividers and forces the outputs to the high im-

pedance state.

The effective fanout of the ICS87931I can be increased to 12

by utilizing the ability of each output to drive two series termi-

nated transmission lines.

F

EATURES

·

Fully integrated PLL

·

6 LVCMOS/LVTTL outputs, 7

typical output impedance

·

Selectable differential CLK0, nCLK0 or LVCMOS/LVTTL clock

for redundant clock applications

·

Maximum output frequency: 150MHz

·

VCO range: 220MHz to 480MHz

·

External feedback for "zero delay" clock regeneration

·

Output skew, Same Frequency: 300ps (maximum)

·

Output skew, Different Frequency: 400ps (maximum)

·

Cycle-to-cycle jitter: 100ps (maximum)

·

3.3V supply voltage

·

-40°C to 85°C ambient operating temperature

·

Pin compatible with MPC931

HiPerClockSTM

,&6

P

IN

A

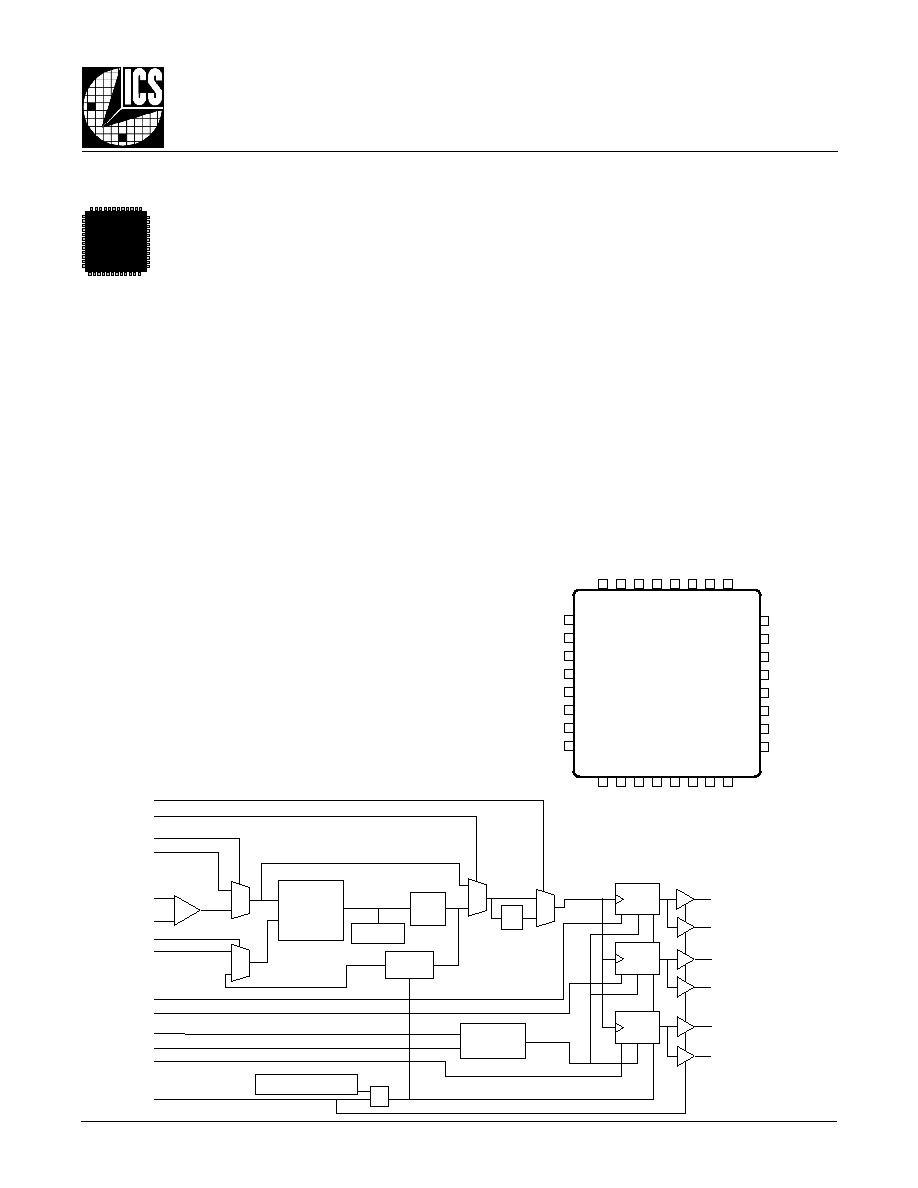

SSIGNMENT

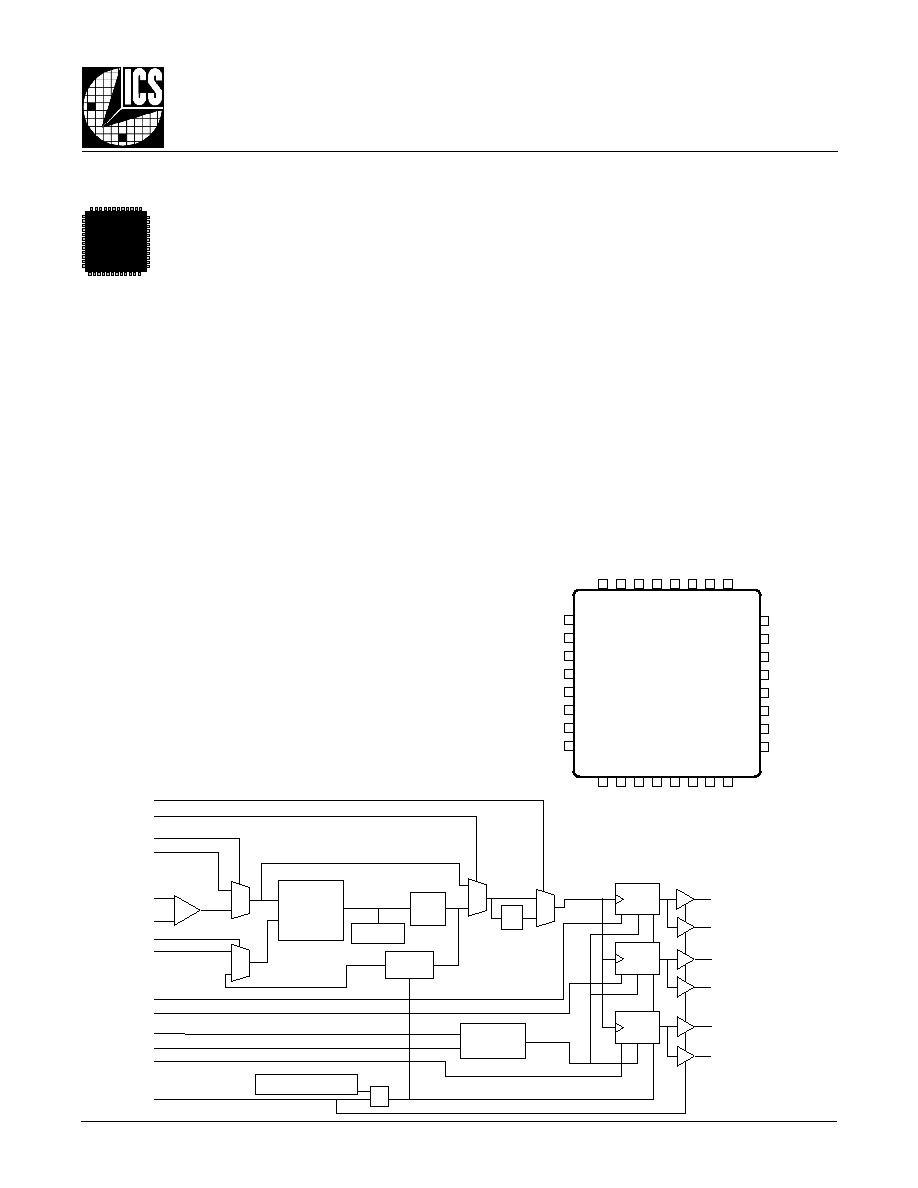

32 31 30 29 28 27 26 25

9 10 11 12 13 14 15 16

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

GND

QB0

QB1

V

DDO

EXTFB_SEL

CLK_SEL

PLL_SEL

nc

nc

V

DDA

POWER_DN

CLK1

nMR

CLK0

nCLK0

GND

GND

QC1

QC0

V

DDO

EXT_FB

CLK_EN1

CLK_EN0

nc

GND

QA1

QA0

V

DDO

DIV_SELA

DIV_SELB

DIV_SELC

nc

ICS87931I

32-Lead LQFP

7mm x 7mm x 1.4mm

package body

Y package

Top View

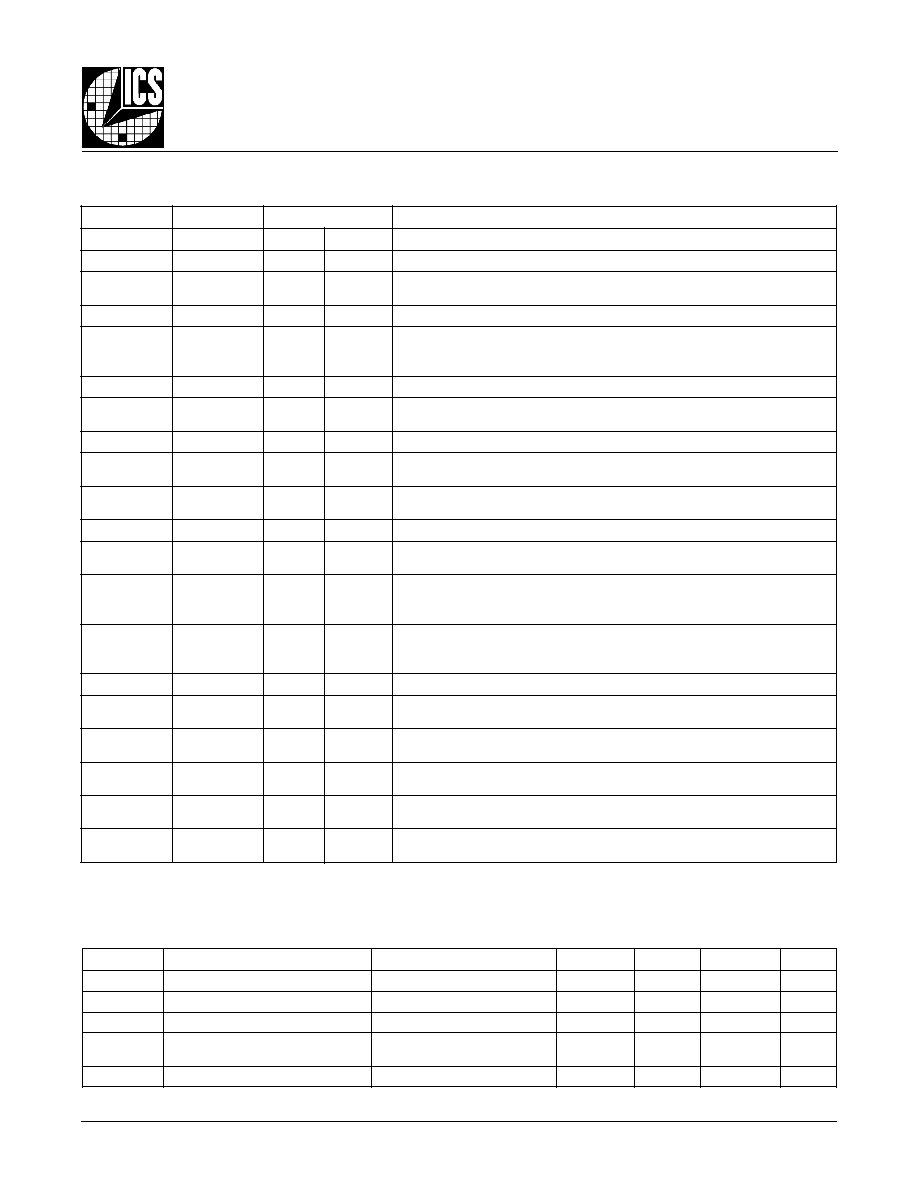

POWER_DN

PLL_SEL

CLK_SEL

CLK1

CLK0

nCLK0

EXTFB_SEL

EXT_FB

DIV_SELA

DIV_SELB

CLK_EN0

CLK_EN1

DIV_SELC

nMR

QA0

QA1

QB0

QB1

QC0

QC1

Pullup

Pulldown

Pullup

Pullup

Pullup

Pullup

Pullup

Pullup

Pullup

Pulldown

Pulldown

Pulldown

Pulldown

None

0

1

0

1

1

0

1

0

POWER-ON RESET

PHASE

DETECTOR

LPF

DISABLE

LOGIC

VCO

÷8

÷4/÷6

÷2/÷4

÷2/÷4

÷2

B

LOCK

D

IAGRAM

87931BYI

www.icst.com/products/hiperclocks.html

REV. A JUNE 23, 2003

5

Integrated

Circuit

Systems, Inc.

ICS87931I

L

OW

S

KEW

, 1-

TO

-6

LVCMOS/LVTTL C

LOCK

M

ULTIPLIER

/Z

ERO

D

ELAY

B

UFFER

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

I

N

I

t

n

e

r

r

u

C

t

u

p

n

I

0

2

1

±

A

µ

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

5

1

.

0

3

.

1

V

V

R

M

C

;

e

g

a

t

l

o

V

t

u

p

n

I

e

d

o

M

n

o

m

m

o

C

2

,

1

E

T

O

N

5

.

0

+

D

N

G

V

D

D

5

8

.

0

-

V

s

n

o

i

t

a

c

il

p

p

a

d

e

d

n

e

e

l

g

n

i

s

r

o

F

:

1

E

T

O

N

,

V

s

i

0

K

L

C

n

,

0

K

L

C

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

A

D

D

.

V

3

.

0

+

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

2

E

T

O

N

V

s

a

d

e

n

i

f

e

d

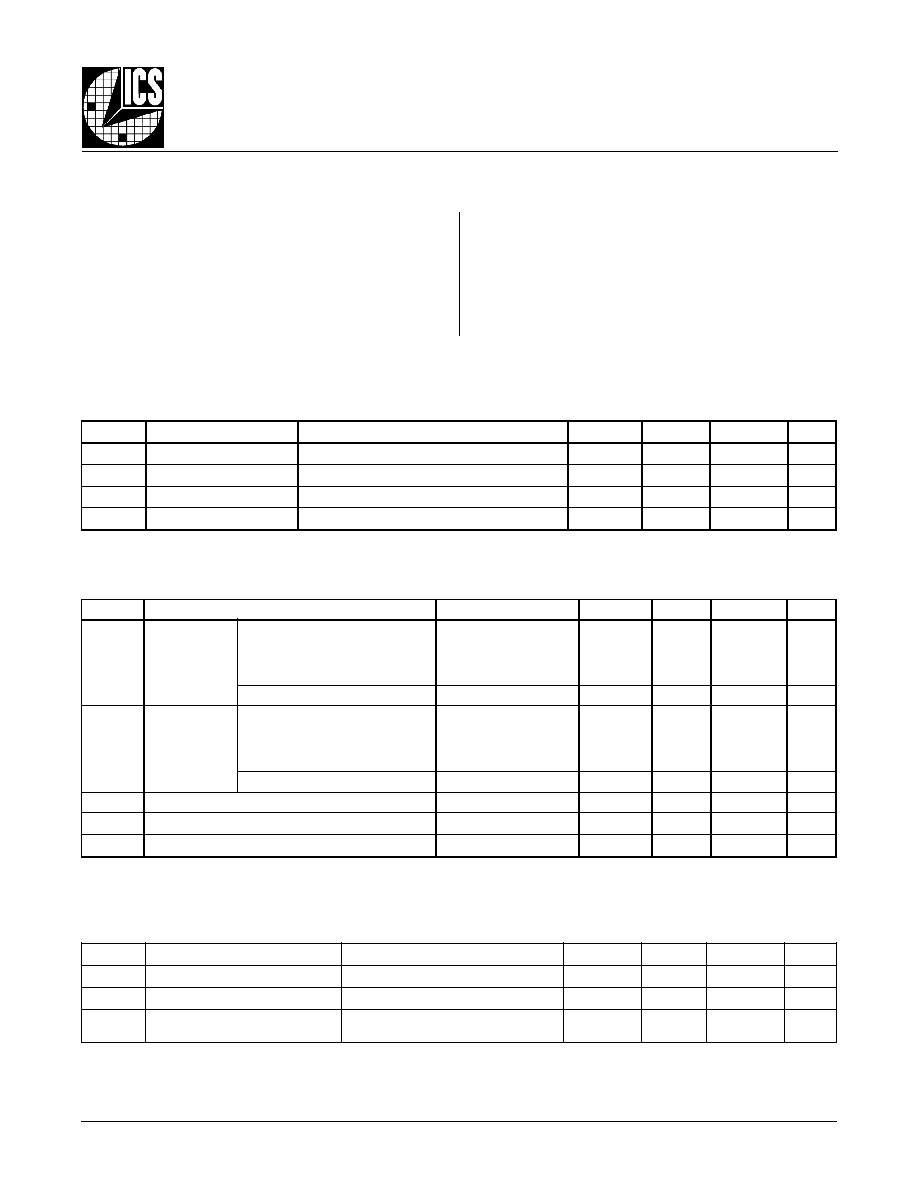

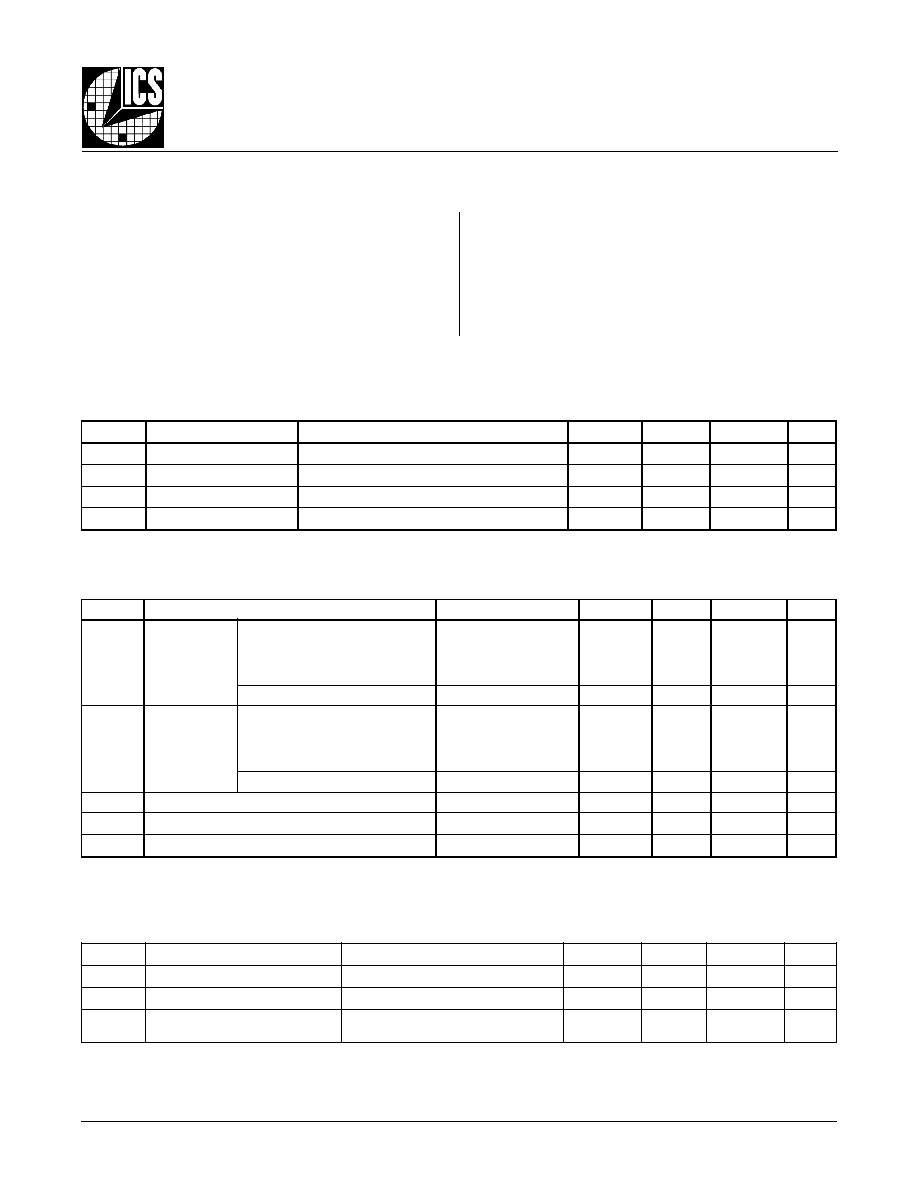

H

I

.

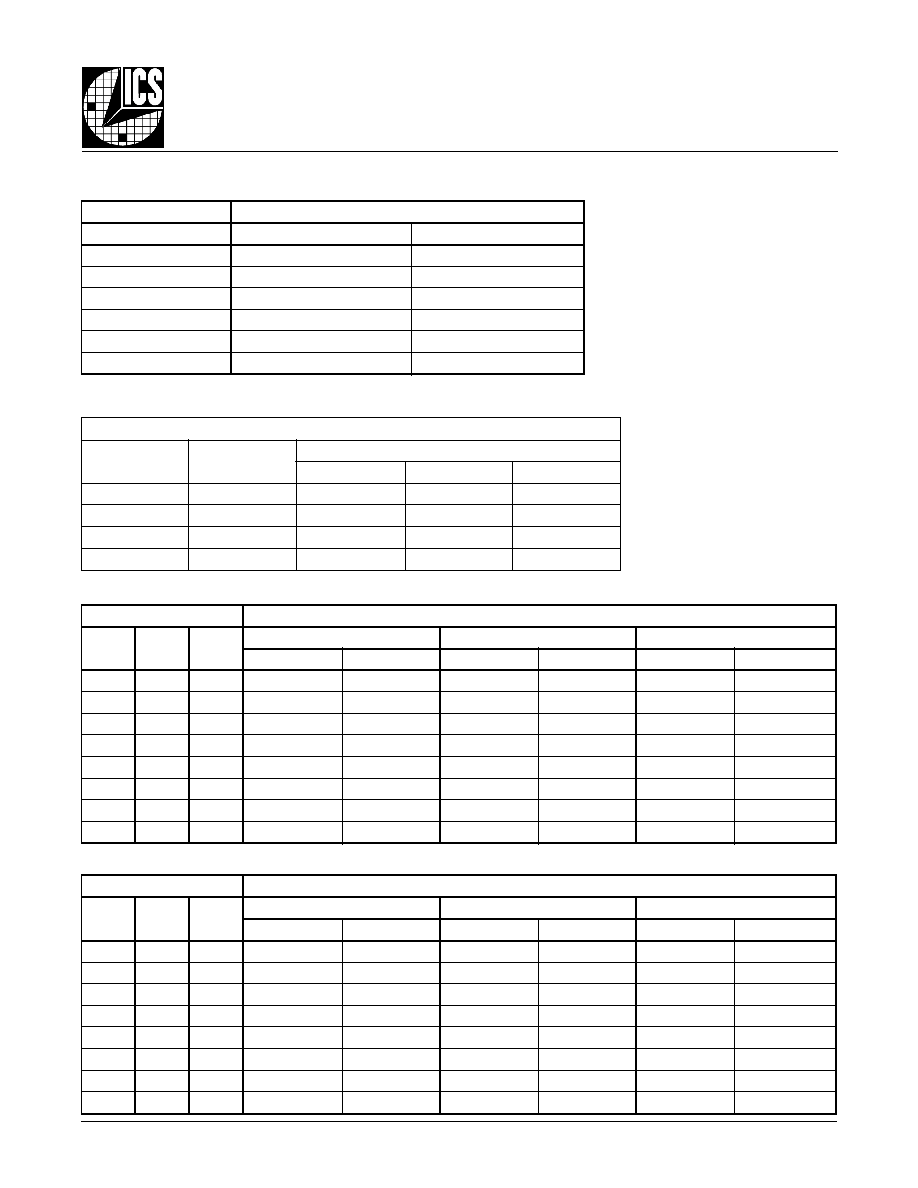

T

ABLE

5C. D

IFFERENTIAL

DC C

HARACTERISTICS

,

V

DDA

= V

DDO

= 3.3V±5%, T

A

= -40°C

TO

85°C

T

ABLE

5B. LVCMOS/LVTTL DC C

HARACTERISTICS

,

V

DDA

= V

DDO

= 3.3V±5%, T

A

= -40°C

TO

85°C

T

ABLE

5A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

DDA

= V

DDO

= 3.3V±5%, T

A

= -40°C

TO

85°C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

A

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

g

o

l

a

n

A

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

O

D

D

e

g

a

t

l

o

V

y

l

p

p

u

S

t

u

p

t

u

O

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

A

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

g

o

l

a

n

A

0

2

A

m

I

O

D

D

t

n

e

r

r

u

C

y

l

p

p

u

S

t

u

p

t

u

O

0

0

1

A

m

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

t

u

p

n

I

e

g

a

t

l

o

V

h

g

i

H

,

C

L

E

S

_

V

I

D

:

A

L

E

S

_

V

I

D

,

0

N

E

_

K

L

C

N

E

_

K

L

C

,

1

n

,

N

D

_

R

E

W

O

P

,

L

E

S

_

K

L

C

,

R

M

L

E

S

_

B

F

T

X

E

,

L

E

S

_

L

L

P

2

V

D

D

3

.

0

+

V

B

F

_

T

X

E

,

1

K

L

C

2

V

D

D

3

.

0

+

V

V

L

I

t

u

p

n

I

e

g

a

t

l

o

V

w

o

L

,

C

L

E

S

_

V

I

D

:

A

L

E

S

_

V

I

D

,

1

N

E

_

K

L

C

,

0

N

E

_

K

L

C

,

L

E

S

_

K

L

C

,

R

M

n

,

N

D

_

R

E

W

O

P

L

E

S

_

B

F

T

X

E

,

L

E

S

_

L

L

P

3

.

0

-

8

.

0

V

B

F

_

T

X

E

,

1

K

L

C

3

.

0

-

3

.

1

V

I

N

I

t

n

e

r

r

u

C

t

u

p

n

I

0

2

1

±

A

µ

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

I

H

O

A

m

0

2

-

=

4

.

2

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

I

L

O

A

m

0

2

=

5

.

0

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

O

D

D

.

t

i

u

c

r

i

C

t

s

e

T

d

a

o

L

t

u

p

t

u

O

V

3

.

3

,

n

o

i

t

c

e

s

t

n

e

m

e

r

u

s

a

e

M

r

e

t

e

m

a

r

a

P

e

e

S

.

2

/

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

DD

4.6V

Inputs, V

I

-0.5V to V

DDA

+ 0.5 V

Outputs, V

O

-0.5V to V

DDO

+ 0.5V

Package Thermal Impedance,

JA

47.9°C/W (0 lfpm)

Storage Temperature, T

STG

-65°C to 150°C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.