87993AYI

www.icst.com/products/hiperclocks.html

REV. B May 21, 2003

1

Integrated

Circuit

Systems, Inc.

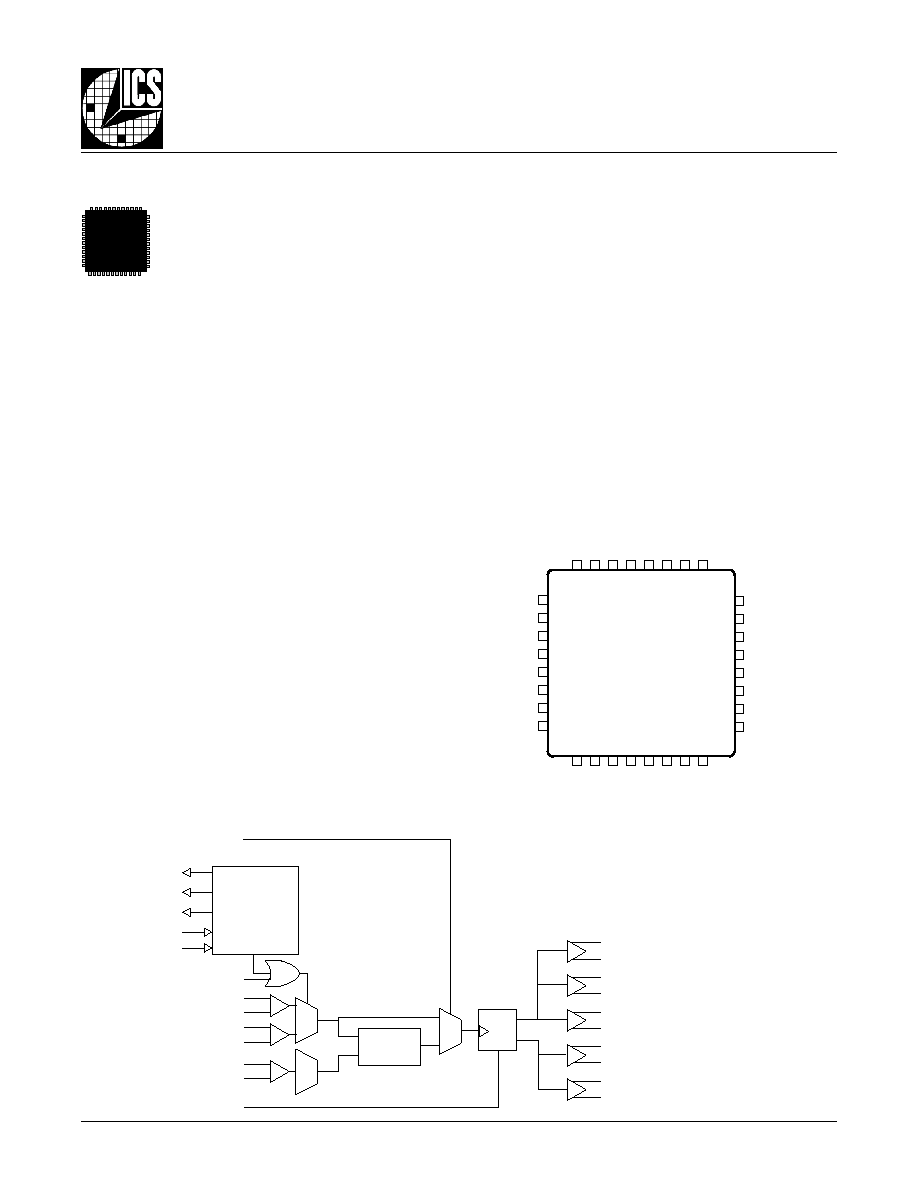

ICS87993I

1-

TO

-5 D

IFFERENTIAL

-

TO

-3.3V LVPECL

PLL C

LOCK

D

RIVER

W

/D

YNAMIC

C

LOCK

S

WITCH

G

ENERAL

D

ESCRIPTION

The ICS87993I is a PLL clock driver designed

specifically for redundant clock tree designs. The

device receives two differential LVPECL clock

signals from which it generates 5 new differen-

tial LVPECL clock outputs. Two of the output pairs

regenerate the input signal frequency and phase while the

other three pairs generate 2x, phase aligned clock outputs.

External PLL feedback is used to also provide zero delay

buffer performance.

The ICS87993I Dynamic Clock Switch (DCS) circuit continu-

ously monitors both input CLK signals. Upon detection of a

failure (CLK stuck HIGH or LOW for at least 1 period), the

INP_BAD for that CLK will be latched (H). If that CLK is the

primary clock, the DCS will switch to the good secondary

clock and phase/frequency alignment will occur with minimal

output phase disturbance. The typical phase bump caused

by a failed clock is eliminated.

HiPerClockSTM

,&6

F

EATURES

�

5 differential 3.3V LVPECL outputs

�

Selectable differential clock inputs

�

CLKx, nCLKx pair can accept the following differential

input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

�

VCO range: 200MHz to 500MHz

�

External feedback for "zero delay" clock regeneration

with configurable frequencies

�

Cycle-to-cycle jitter (RMS): 20ps (maximum)

�

Output skew: 70ps (maximum), within one bank

�

3.3V supply voltage

�

-40�C to 85�C ambient operating temperature

�

Pin compatible with MPC993

32-Lead QFP (LQFP)

7mm x 7mm x 1.4mm

package body

Y Package

Top View

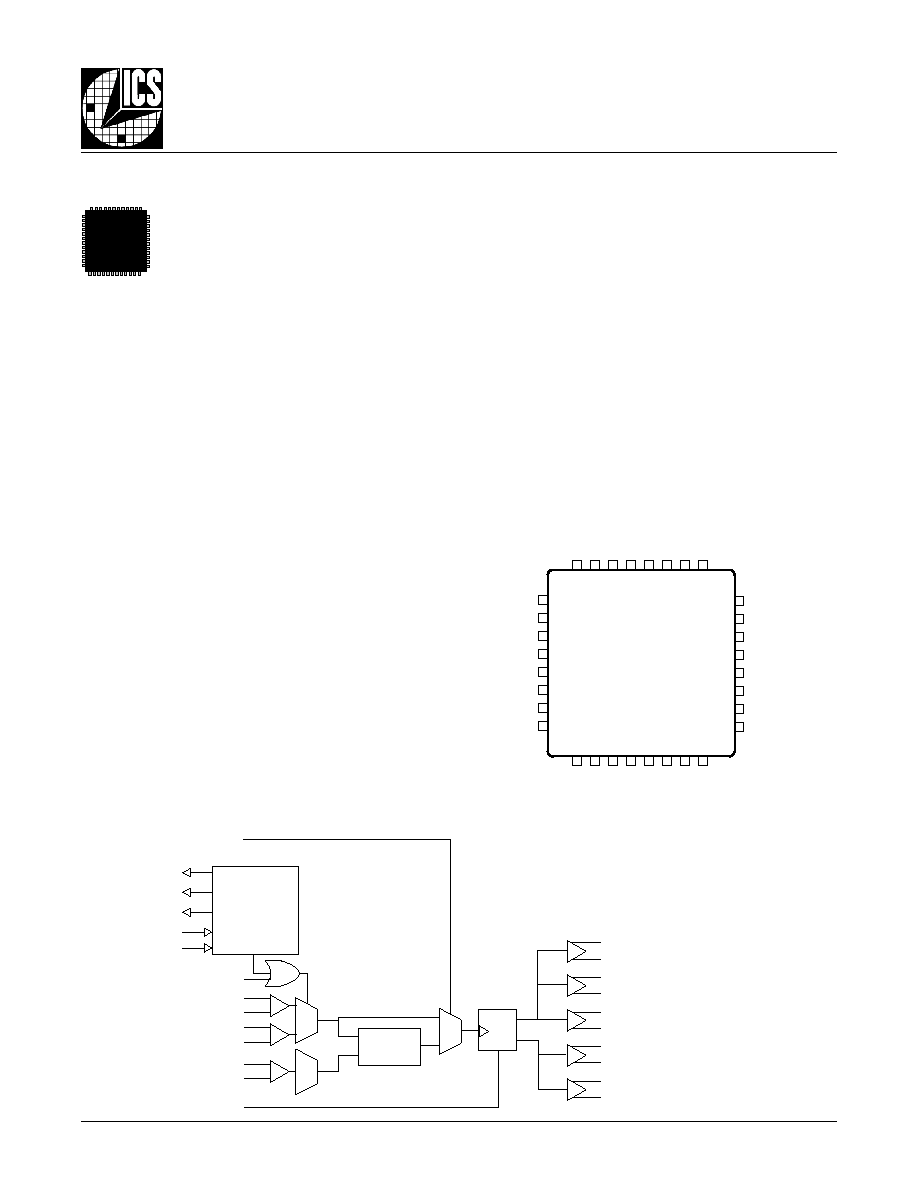

24 23 22 21 20 19 18 17

1 2 3 4 5 6 7 8

25

26

27

28

29

30

31

32

16

15

14

13

12

11

10

9

V

CC

INP0BAD

INP1BAD

CLK_SELECTED

V

EE

nEXT_FB

EXT_FB

V

EE

nQA1

QA1

nQA0

QA0

V

CC

V

CCA

MAN_OVERRIDE

PLL_SEL

V

EE

nCLK1

CLK1

CLK_SEL

nCLK0

CLK0

nALARM_RESET

nMR

V

CC

nQB2

QB2

nQB1

QB1

nQB0

QB0

V

CC

ICS87993I

P

IN

A

SSIGNMENT

B

LOCK

D

IAGRAM

PLL

�2

�4

Dynamic Switch

Logic

nQB0

QB0

nQB1

QB1

nQB2

QB2

nQA0

QA0

nQA1

QA1

PLL_SEL

CLK_SELECTED

INP1BAD

INP0BAD

MAN_OVERRIDE

ALARM_RESET

SEL_CLK

nCLK0

CLK0

nCLK1

CLK1

nEXT_FB

EXT_FB

nMR

87993AYI

www.icst.com/products/hiperclocks.html

REV. B May 21, 2003

3

Integrated

Circuit

Systems, Inc.

ICS87993I

1-

TO

-5 D

IFFERENTIAL

-

TO

-3.3V LVPECL

PLL C

LOCK

D

RIVER

W

/D

YNAMIC

C

LOCK

S

WITCH

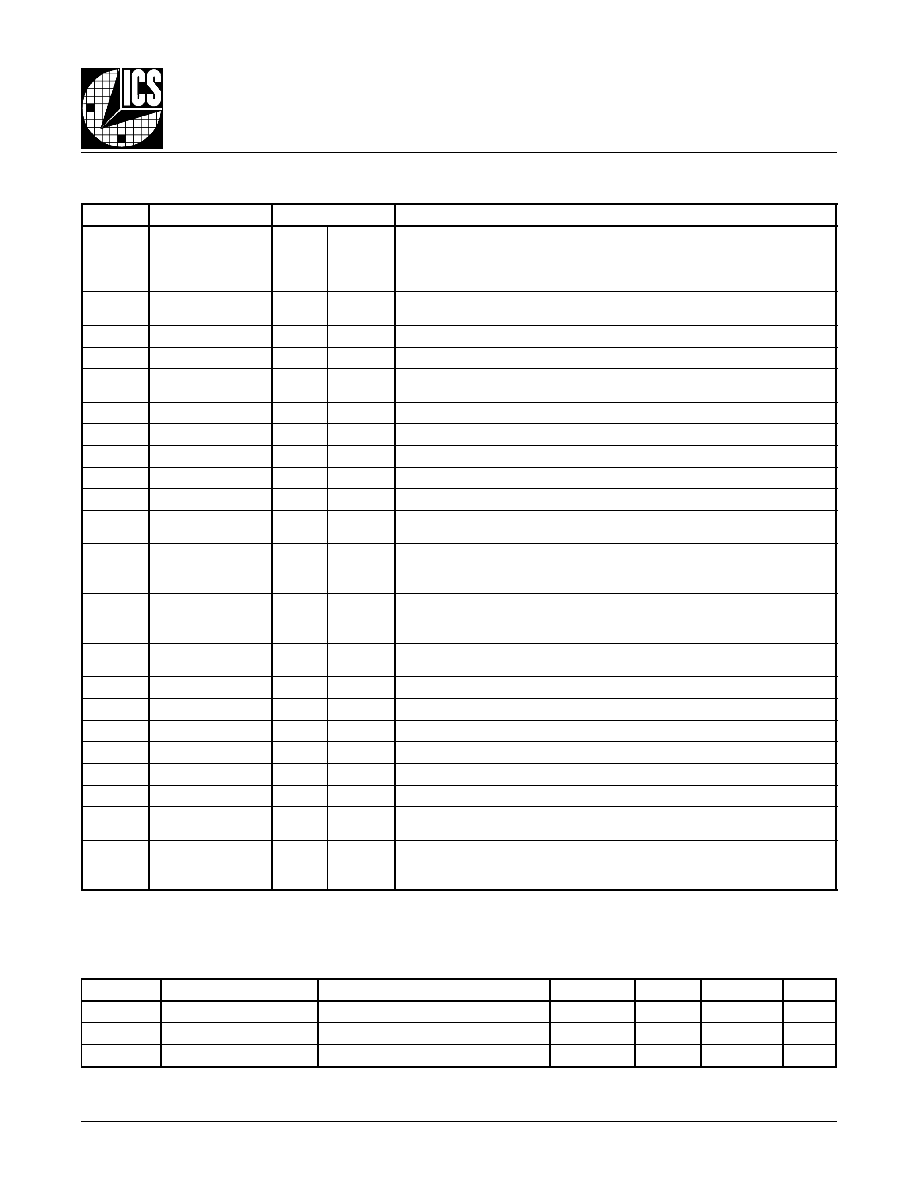

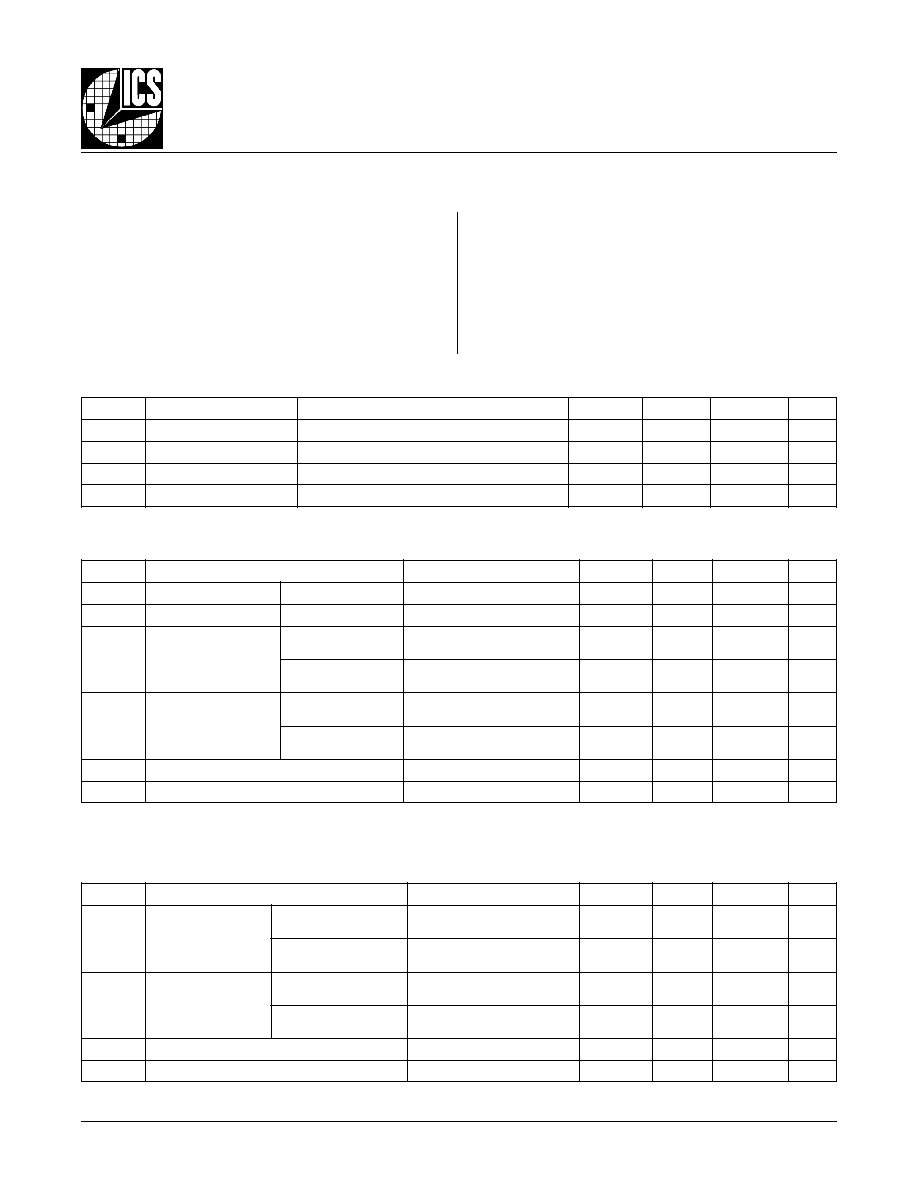

T

ABLE

3C. D

IFFERENTIAL

DC C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, T

A

= -40�C

TO

85�C

T

ABLE

3A. P

OWER

S

UPPLY

DC C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, T

A

= -40�C

TO

85�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

e

r

o

C

5

3

1

.

3

3

.

3

5

6

4

.

3

V

V

A

C

C

e

g

a

t

l

o

V

y

l

p

p

u

S

g

o

l

a

n

A

5

3

1

.

3

3

.

3

5

6

4

.

3

V

I

E

E

t

n

e

r

r

u

C

y

l

p

p

u

S

r

e

w

o

P

0

8

0

8

1

A

m

I

A

C

C

t

n

e

r

r

u

C

y

l

p

p

u

S

g

o

l

a

n

A

5

1

0

2

A

m

T

ABLE

3B. LVCMOS/LVTTL DC C

HARACTERISTICS

,

V

CC

= V

CCA

= 3.3V�5%, T

A

= -40�C

TO

85�C

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

V

H

I

e

g

a

t

l

o

V

h

g

i

H

t

u

p

n

I

s

t

u

p

n

I

S

O

M

C

V

L

2

3

.

3

V

V

L

I

e

g

a

t

l

o

V

w

o

L

t

u

p

n

I

s

t

u

p

n

I

S

O

M

C

V

L

3

.

0

-

8

.

0

V

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

,

K

L

C

_

L

E

S

E

D

I

R

R

E

V

O

_

N

A

M

V

N

I

V

=

C

C

V

5

6

4

.

3

=

5

A

�

,

T

E

S

E

R

_

M

R

A

L

A

n

R

M

n

,

L

E

S

_

L

L

P

V

N

I

V

=

C

C

V

5

6

4

.

3

=

0

2

1

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

,

K

L

C

_

L

E

S

E

D

I

R

R

E

V

O

_

N

A

M

V

N

I

V

,

V

0

=

C

C

V

5

6

4

.

3

=

5

-

A

�

,

T

E

S

E

R

_

M

R

A

L

A

n

R

M

n

,

L

E

S

_

L

L

P

V

N

I

V

,

V

0

=

C

C

V

5

6

4

.

3

=

0

2

1

-

A

�

V

H

O

1

E

T

O

N

;

e

g

a

t

l

o

V

h

g

i

H

t

u

p

t

u

O

4

.

2

V

V

L

O

1

E

T

O

N

;

e

g

a

t

l

o

V

w

o

L

t

u

p

t

u

O

5

.

0

V

0

5

h

t

i

w

d

e

t

a

n

i

m

r

e

t

s

t

u

p

t

u

O

:

1

E

T

O

N

V

o

t

C

C

,

n

o

i

t

c

e

S

n

o

i

t

a

m

r

o

f

n

I

t

n

e

m

e

r

u

s

a

e

M

r

e

t

e

m

a

r

a

P

e

e

S

.

2

/

.

"

m

a

r

g

a

i

d

t

i

u

c

r

i

C

t

s

e

T

C

A

d

a

o

L

t

u

p

t

u

O

V

3

.

3

"

l

o

b

m

y

S

r

e

t

e

m

a

r

a

P

s

n

o

i

t

i

d

n

o

C

t

s

e

T

m

u

m

i

n

i

M

l

a

c

i

p

y

T

m

u

m

i

x

a

M

s

t

i

n

U

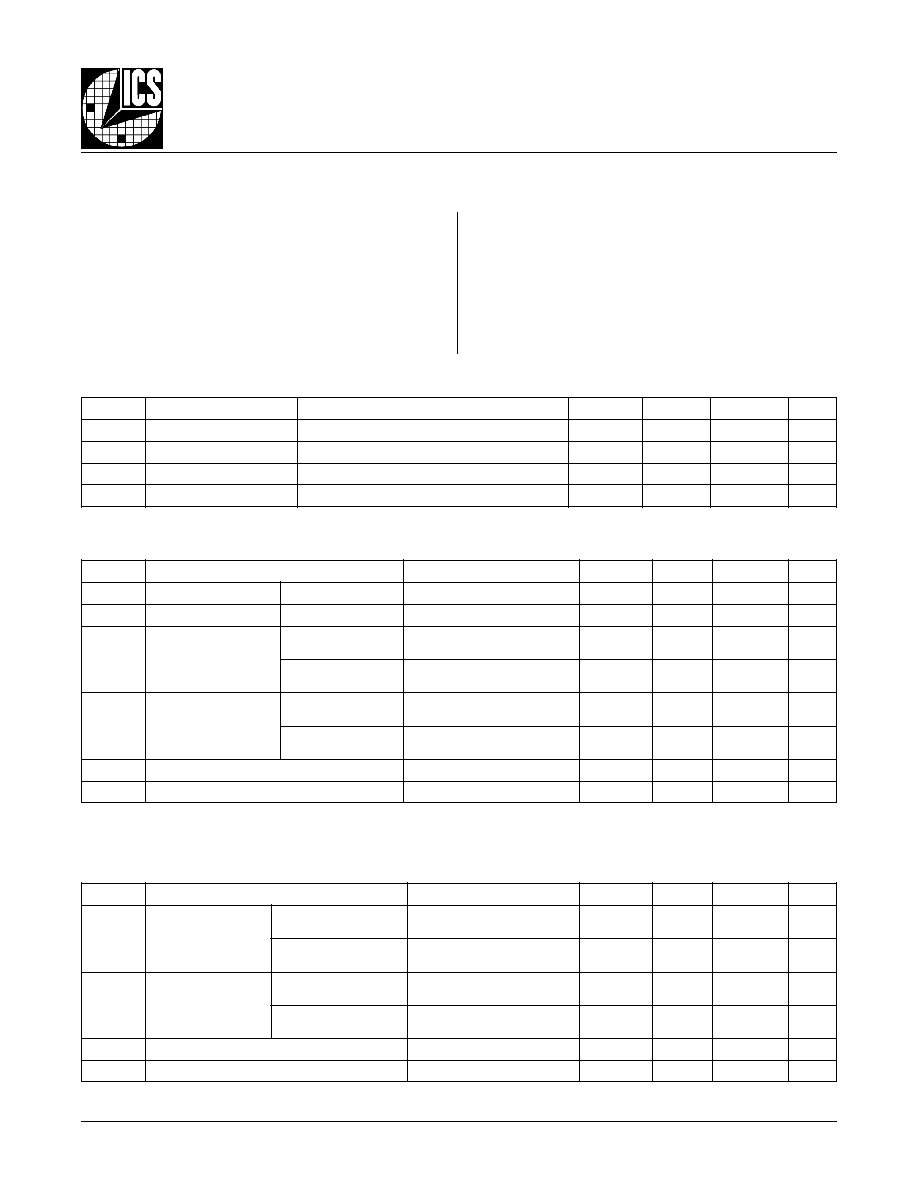

I

H

I

t

n

e

r

r

u

C

h

g

i

H

t

u

p

n

I

,

1

K

L

C

,

0

K

L

C

B

F

_

T

X

E

V

N

I

V

=

C

C

V

5

6

4

.

3

=

5

A

�

,

1

K

L

C

n

,

0

K

L

C

n

B

F

_

T

X

E

n

V

N

I

V

=

C

C

V

5

6

4

.

3

=

0

2

1

A

�

I

L

I

t

n

e

r

r

u

C

w

o

L

t

u

p

n

I

,

1

K

L

C

,

0

K

L

C

B

F

_

T

X

E

V

N

I

V

,

V

0

=

C

C

V

5

6

4

.

3

=

5

-

A

�

,

1

K

L

C

n

,

0

K

L

C

n

B

F

_

T

X

E

n

V

N

I

V

,

V

0

=

C

C

V

5

6

4

.

3

=

0

2

1

-

A

�

V

P

P

e

g

a

t

l

o

V

t

u

p

n

I

k

a

e

P

-

o

t

-

k

a

e

P

5

1

.

0

3

.

1

V

V

R

M

C

2

,

1

E

T

O

N

;

e

g

a

t

l

o

V

t

u

p

n

I

e

d

o

M

n

o

m

m

o

C

V

E

E

5

.

0

+

V

C

C

5

8

.

0

-

V

V

s

a

d

e

n

i

f

e

d

s

i

e

g

a

t

l

o

v

e

d

o

m

n

o

m

m

o

C

:

1

E

T

O

N

H

I

.

V

s

i

K

L

C

n

,

K

L

C

r

o

f

e

g

a

t

l

o

v

t

u

p

n

i

m

u

m

i

x

a

m

e

h

t

,

s

n

o

i

t

a

il

p

p

a

d

e

d

n

e

e

l

g

n

i

s

r

o

F

:

2

E

T

O

N

C

C

.

V

3

.

0

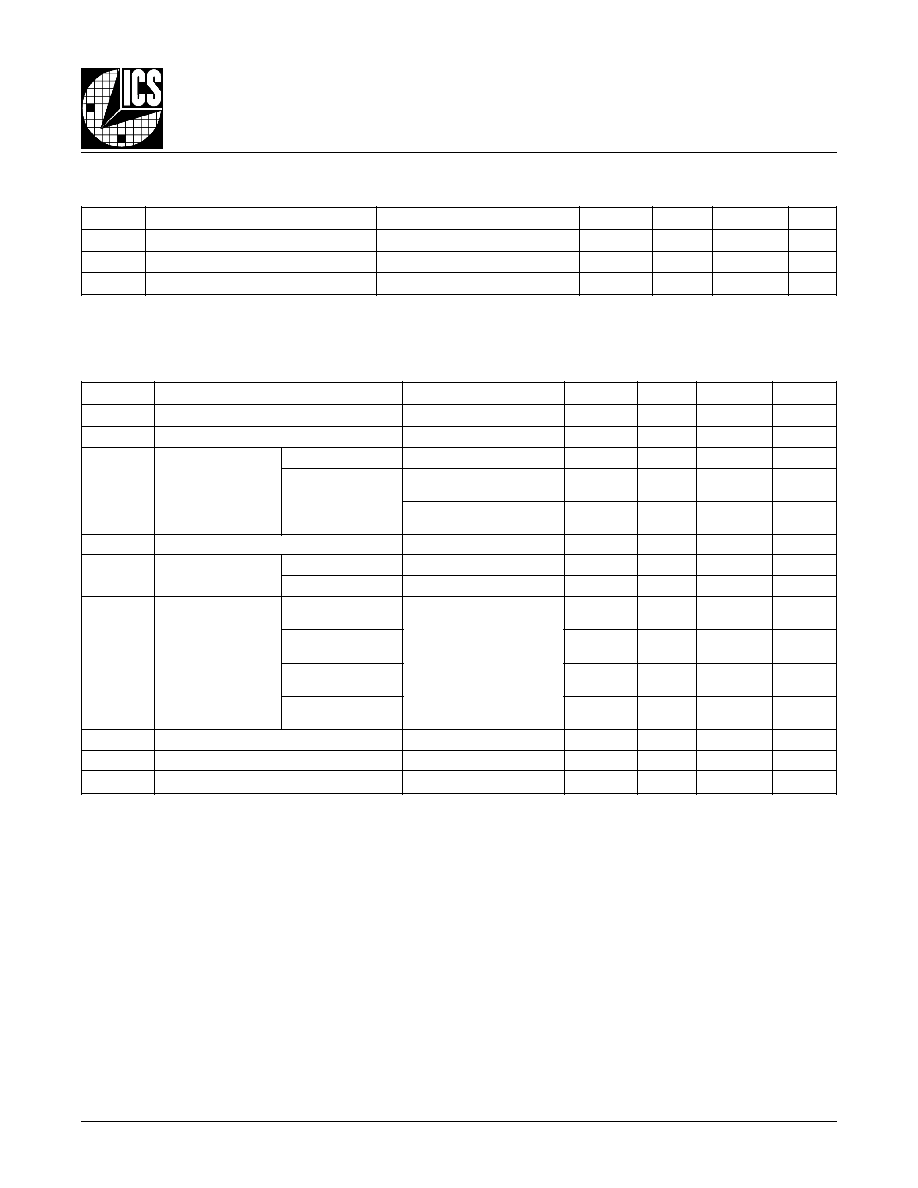

+

A

BSOLUTE

M

AXIMUM

R

ATINGS

Supply Voltage, V

CC

4.6V

Inputs, V

I

-0.5V to V

CC

+ 0.5 V

Outputs, I

O

Continuous Current

50mA

Surge Current

100mA

Package Thermal Impedance,

JA

47.9�C/W (0 lfpm)

Storage Temperature, T

STG

-65�C to 150�C

NOTE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent damage to the

device. These ratings are stress specifications only. Functional

operation of product at these conditions or any conditions be-

yond those listed in the

DC Characteristics or AC Character-

istics is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.