1

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

COMMERCIAL TEMPERATURE RANGE

NOVEMBER 2000

1999 Integrated Device Technology, Inc.

DSC-2552/9

c

IDT49C465

IDT49C465A

COMMERCIAL TEMPERATURE RANGE

64-BIT FLOW-THRU

ERROR DETECTION

AND CORRECTION UNIT

DESCRIPTION:

The IDT49C465/A is a 32-bit, two-data bus, Flow-thruEDC unit. The

chip provides single-error correction and two and three bit error detec-

tion of both hard and soft memory errors. It can be expanded to 64-bit

widths by cascading two units, without the need for additional external

logic. The Flow-thruEDC has been optimized for speed and simplicity

of control.

The EDC unit has been designed for use in either of two configura-

tions in an error correcting memory system. The bidirectional configu-

ration is most appropriate for systems using bidirectional memory

buses. A second system configuration utilizes external octal buffers,

and is well-suited for systems using memory with separate I/O buses.

The IDT49C465/A supports partial word writes, pipelining, and error

diagnostics. It also provides parity protection for data on the system

side.

SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

CBO

0-7

M em ory

C heckbit

Generator

S

y

n

d

r

o

m

e

G

e

n

e

r

a

t

o

r

Correct

Logic

E

x

p

a

n

s

i

o

n

L

o

g

i

c

Detect

Logic

M ux

System

Checkbit

Generator

Byte

M ux

P

i

p

e

l

i

n

e

L

a

t

c

h

M ux

C heckbit

Latch

M D

Latch

M LE

SD

0-31

ER R

M E R R

C BI

0-7

PC B I

0-7

PLE

M D

0-31

SLE

C ON TROL

CON TR OL

SD

Latch

C ONTR OL

C ON TR OL

FEATURES:

- 32-bit wide Flow-thruEDCTM unit, cascadable to 64 bits

- Single-chip 64-bit Generate Mode

- Separate system and memory buses

- On-chip pipeline latch with external control

- Supports bidirectional and common I/O memories

- Corrects all single-bit errors

- Detects all double-bit errors and some multiple bit errors

- Error Detection Time -- 12ns

- Error Correction Time -- 14ns

- On chip diagnostic registers

- Parity generation and checking on system data bus

-

Low power CMOS -- 100mA typical at 20MHz

-

144-pin PGA and PQFP packages

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

2

COMMERCIAL TEMPERATURE RANGE

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

SD

18

SD

19

BE

2

SD

20

SD

21

Vcc

Vcc

SD

28

BE

3

SD

27

SD

26

SD

25

SD

24

SD

23

G ND

SD

22

SD

17

SD

16

G ND

SO E

PL E

SL E

SD

15

SD

14

SD

12

BE

1

G ND

SD

11

SD

10

SD

9

SD

8

SD

7

SD

6

SD

5

Vcc

SD

13

73

72

49C465Y

PQ 144-2

108

109

144

1

36

37

M D

17

M D

18

M D

19

M D

20

M D

21

Vcc

M D

30

M D

29

M D

28

M D

27

M D

26

M D

25

M D

24

G ND

M D

23

M D

22

M D

16

G ND

M O E

M LE

M D

15

M D

14

M D

13

M D

12

M D

10

G ND

M D

9

M D

8

M D

7

M D

6

M D

5

M D

4

M D

3

Vcc

Vcc

M D

11

P

0

M

O

D

E

2

S

Y

N

C

L

K

S

C

L

K

E

N

C

L

E

A

R

V

c

c

M

D

3

1

C

B

I

7

C

B

I

6

C

B

I

5

C

B

I

4

G

N

D

C

B

I

3

C

B

I

2

C

B

I

1

C

B

I

0

P

1

G

N

D

G

N

D

P

2

P

3

P

E

R

R

P

S

E

L

C

B

O

7

C

B

O

5

C

B

O

4

C

B

O

E

C

B

O

3

C

B

O

2

C

B

O

1

C

B

O

0

S

D

3

1

S

D

3

0

S

D

2

9

V

c

c

C

B

O

6

M

O

D

E

0

M

E

R

R

E

R

R

S

Y

O

7

S

Y

O

6

V

c

c

M

D

2

M

D

1

M

D

0

S

Y

O

0

S

Y

O

1

S

Y

O

2

S

Y

O

3

G

N

D

S

Y

O

4

S

Y

O

5

M

O

D

E

1

G

N

D

G

N

D

C

O

D

E

I

D

2

C

O

D

E

I

D

1

P

C

B

I

0

P

C

B

I

1

P

C

B

I

2

P

C

B

I

4

P

C

B

I

5

P

C

B

I

6

P

C

B

I

7

S

D

0

S

D

1

S

D

2

S

D

3

B

E

0

S

D

4

V

c

c

P

C

B

I

3

PIN CONFIGURATION

PQFP

TOP VIEW

3

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

COMMERCIAL TEMPERATURE RANGE

PGA (CAVITY UP)

TOP VIEW

PIN CONFIGURATION

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

Vcc

SD

2

SD

6

SD

4

SD

9

SD

5

SD

1

BE

0

PC BI

6

SD

11

SD

7

SD

12

S D

10

SD

15

BE

1

SLE

S D

13

SO E

P LE

S D

19

SD

17

SD

18

BE

2

SD

21

S D

22

S D

24

G ND

S D

26

SD

23

Vcc

SD

27

Vcc

S D

30

G ND

SD

14

G ND

SD

16

SD

20

SD

25

BE

3

SD

28

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

SY O

1

M D

1

M D

2

Vcc

M D

3

M D

6

M D

4

M D

8

M D

7

M D

10

M D

12

M O E M D

14

G ND

M D

28

Vcc

Vcc

M D

5

M D

9

G ND

M D

11

M LE

M D

24

Vcc

SD

8

SD

29

CB 0

1

SD

3

SD

0

PC BI

2

G ND

G ND

SY O

6

SY O

5

M D

0

Vcc

SY O

3

Vcc

NC*

PC BI

5

PC BI

3

COD E

ID 1

CO D E

ID 2

M OD E

1

M E RR ER R

PC BI

7

PC BI

4

PC BI

1

PC BI

0

M OD E

0

S Y O

4

SY O

2

G ND

SY O

7

SY O

0

M D

13

M D

15

M D

17

M D

16

M D

20

M D

21

M D

16

G ND M D

23

M D

19

M D

27

M D

25

M D

22

SD

31

C B 0

3

CB 0

5

CB 0

2

CB 0

0

CBO E

CB 0

4

PS EL PE RR

C B 0

6

C B 0

7

G ND

GND

P

3

P

2

P

1

P

0

M O D E

2

SC LK

EN

SYN -

CLK

G ND

C B 1

0

C LE A R

C B 1

6

C B 1

3

C B 1

1

C B 1

7

C B 1

4

C B 1

2

M D

30

M D

31

M D

26

M D

29

Vcc

C B 1

5

M D

18

G 144-2

* = Tied to Vcc internally

4

COMMERCIAL TEMPERATURE RANGE

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

DETAILED FUNCTIONAL BLOCK DIAGRAM

PAR IT Y

CHE CK

PAR IT Y

GEN

1 O F 4

BYT ES

PLE

SO E

BE

0-3

SD

0-31

SL E

PS EL

P

0-3

PE RR

SD

LAT CH

4

4

4

M

U

X

ERR

M ERR

SYO

0-7

SYN CLK

SC LKE N

CLEAR

COD E ID

0,1

M O DE

0-2

CONT RO L

LO G IC

2

3

/ER R

INTERN AL SYN CLK

ER RO R

DET ECT

8

M

U

X

INT ERNAL

FINA L

SYN DR O M E

SYN DR OM E

G ENERATO R

CH ECK

BIT

LATC H

M D

C HECKBIT

G ENE RAT O R

ERRO R

CO RR ECT

ERRO R D AT A LAT CH

DIAG NO STIC

LAT CH ES

M D

LAT CH

CLEAR

INTERN AL SYN CL K

BYTE M U X

BE

0-3

SD

CHE CKB IT

GENERAT OR

D ash ed L ine = Diagnostic path

PCB I

0-7

CBI

0-7

M LE

M D

0-31

M O E

CBO

0-7

CBO E

PCBI

0-7

SD

C HECKBIT

G ENE RAT O R

M

U

X

M

U

X

M

U

X

M

U

X

8

8

8

8

8

4

PIPE

LAT CH

M

U

X

8

8

8

8

8

8

8

8

8

8

5

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

COMMERCIAL TEMPERATURE RANGE

SD

M D

ED C

C BI

C BO

M EM OR Y

I/O

CPU

I/O

C HEC KBITS

EXT. BUFFER

M D

EDC

CBI

CBO

M E M OR Y

IN PU T BU S

C HEC KBIT

I/O

M E M OR Y

OUTPUT BUS

C PU BUS

SD

EXT. BU FFER

Figure 1. Common I/O Configuration

Figure 3. Bypassed Separate I/O Configuration

SYSTEM CONFIGURATIONS

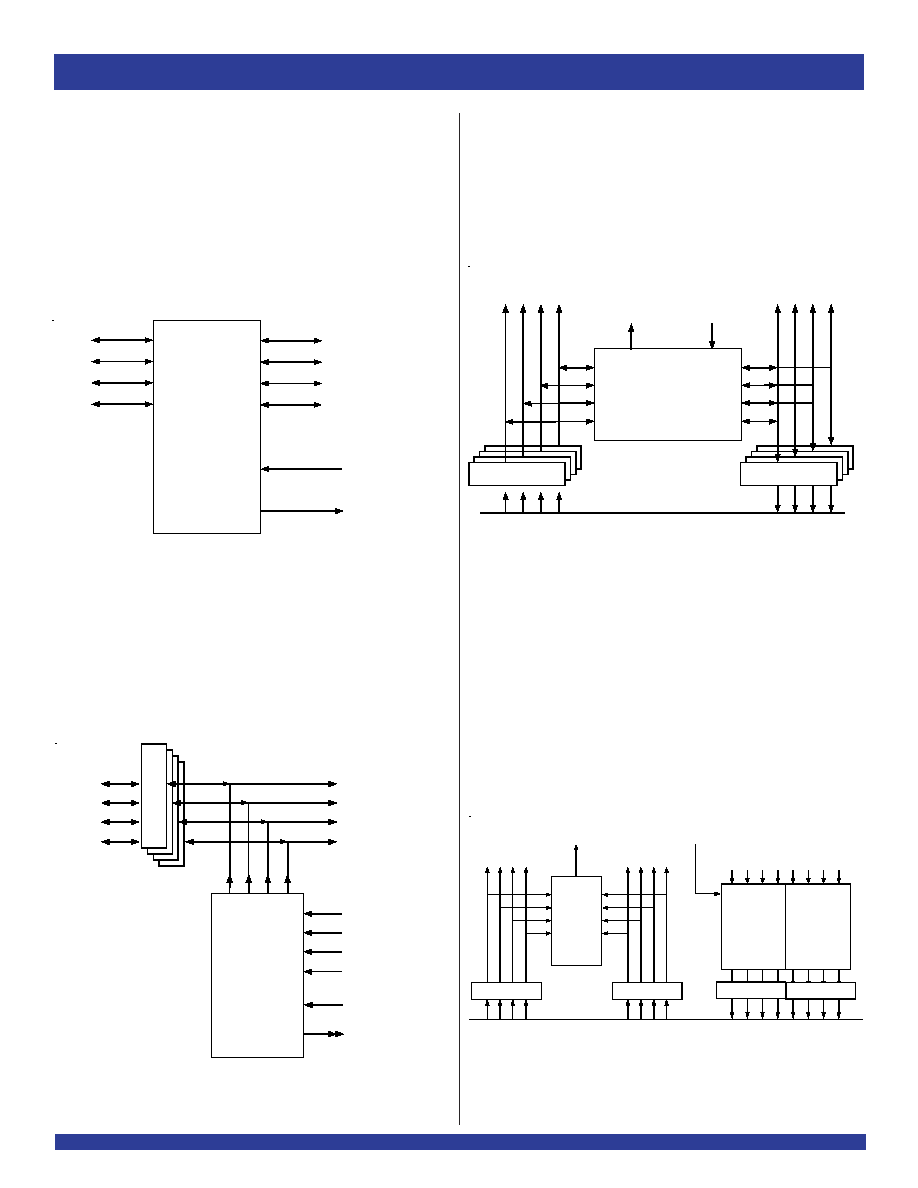

The IDT49C465 EDC unit can be used in various configurations in an

EDC system. The basic configurations are shown below.

Figure 1 illustrates a bidirectional configuration, which is most appropriate

for systems using bidirectional memory buses. It is the simplest

configuration to understand and use. During a correction cycle, the

corrected data word can be simultaneously output on both the system

bus and memory bus. During partial-word-write operations, the new

bytes are internally combined with the corrected old bytes for checkbit

generation and writing to memory.

Figure 2 illustrates a separate I/O configuration. This is appropriate

for systems using separate I/O memory buses. This configuration

allows separate input and output memory buses to be used. Corrected

data is output on the SD outputs for the system and for re-write to

memory. Partial word-write bytes are combined externally for writing

and checkbit generation.

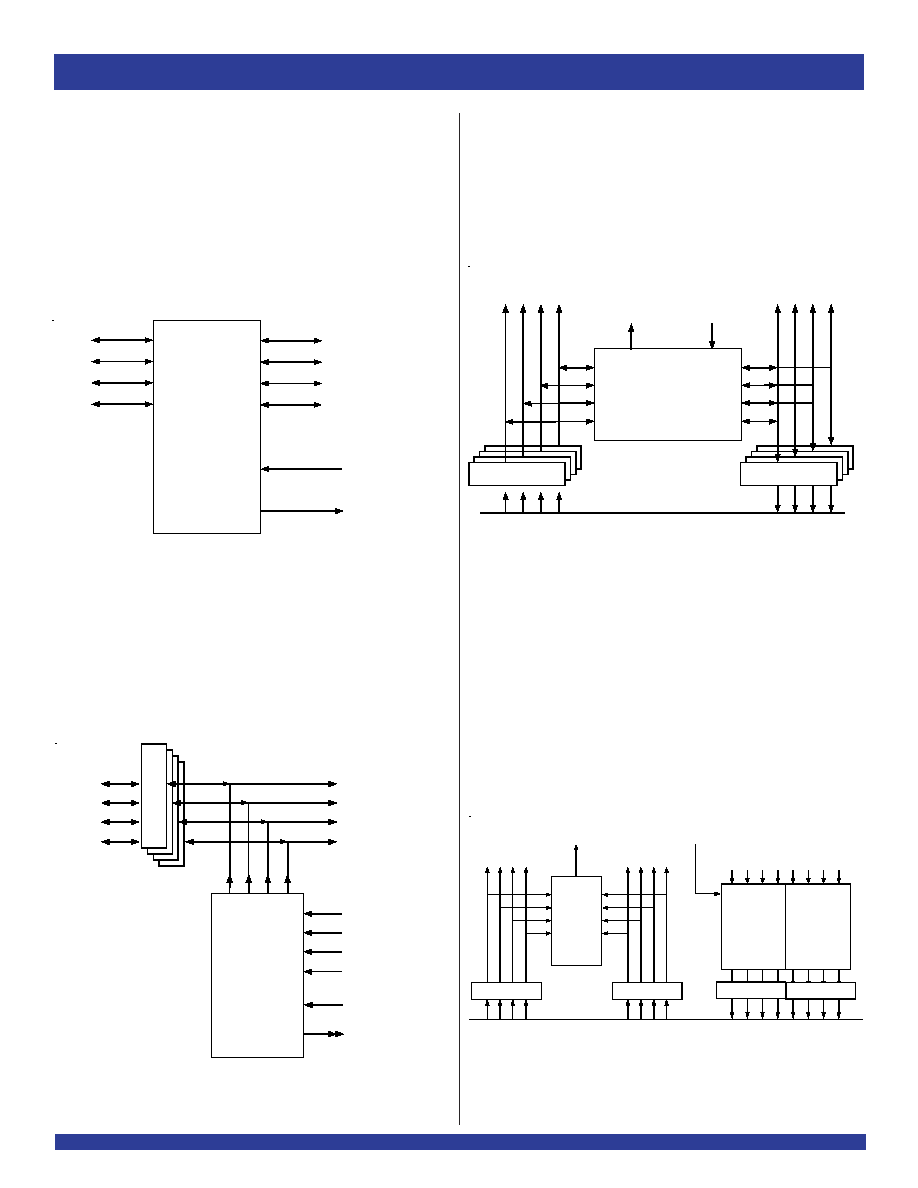

Figure 3 illustrates a third configuration which uses external buffers

and is also well-suited for systems using memory with separate I/O

buses. Since data from memory does not need to pass through the part

on every cycle, the EDC system may operate in "bus-watch" mode. As

in the separate I/O configuration, corrected data is output on the SD

outputs.

Figure 4 illustrates the single-chip generate-only mode for the very

fast 64-bit checkbit generation in systems that use separate checkbit-

generate and detect-correct units. If this is not desired, 64-checkbit

generation and correction can be done with just two EDC units. 64-bit

correction is also straightforward, fast, and requires no extra hardware

for the expansion.

EXT.

BU

F

F

E

R

SD

M D

ED C

C BI

C BO

M EM O R Y

INP UTS

C HE C KBITS

M EM O R Y

O UTP UTS

CP U

ED C

C BO

64-BIT

G EN .

ON LY

M E M O RY

IN PUT BU S

CH ECK

BITS OU T

C PU BU S

BUFFER

BUFFER

M E M O RY

IN PUT BU S

BUFFER

BU FFER

C BI

LOW ER

DATA

U PPER

D ATA

ED C

EDC

C HEC K

BITS IN

M E M O RY

OUTPUT BUS

Figure 2. Separate I/O Configuration

Figure 4. Separate generate/Correction Units with 64-Bit Checkbit Generation