| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 70T659 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

©2003 Integrated Device Technology, Inc.

1

APRIL 2003

DSC-5632/1

CE

0R

R/

W

R

CE

1R

BE

0R

BE

1R

BE

2R

BE

3R

256/128K x 36

MEMORY

ARRAY

Address

Decoder

A

17R(1)

A

0R

Address

Decoder

CE

0L

R/

W

L

CE

1L

BE

0L

BE

1L

BE

2L

BE

3L

Dout0-8_L

Dout9-17_L

Dout18-26_L

Dout27-35_L

Dout0-8_R

Dout9-17_R

Dout18-26_R

Dout27-35_R

B

E

0

L

B

E

1

L

B

E

2

L

B

E

3

L

B

E

3

R

B

E

2

R

B

E

1

R

B

E

0

R

I/O

0L-

I/O

35L

A

17L(1)

A

0L

I/O

0R -

I/O

35R

Di n_L

ADDR_L

Di n_R

ADDR_R

OE

R

OE

L

ARBITRATION

INTERRUPT

SEMAPHORE

LOGIC

SEM

L

INT

L(3)

BUSY

L(2,3)

M/

S

R/

W

L

OE

L

R/

W

R

OE

R

CE

0L

CE

1L

CE

0R

CE

1R

BUSY

R(2,3)

SEM

R

INT

R(3)

4869 drw 01

ZZ

CONTROL

LOGIC

ZZ

L

(4)

ZZ

R

(4)

JTAG

TC K

TRST

TMS

TDI

TD O

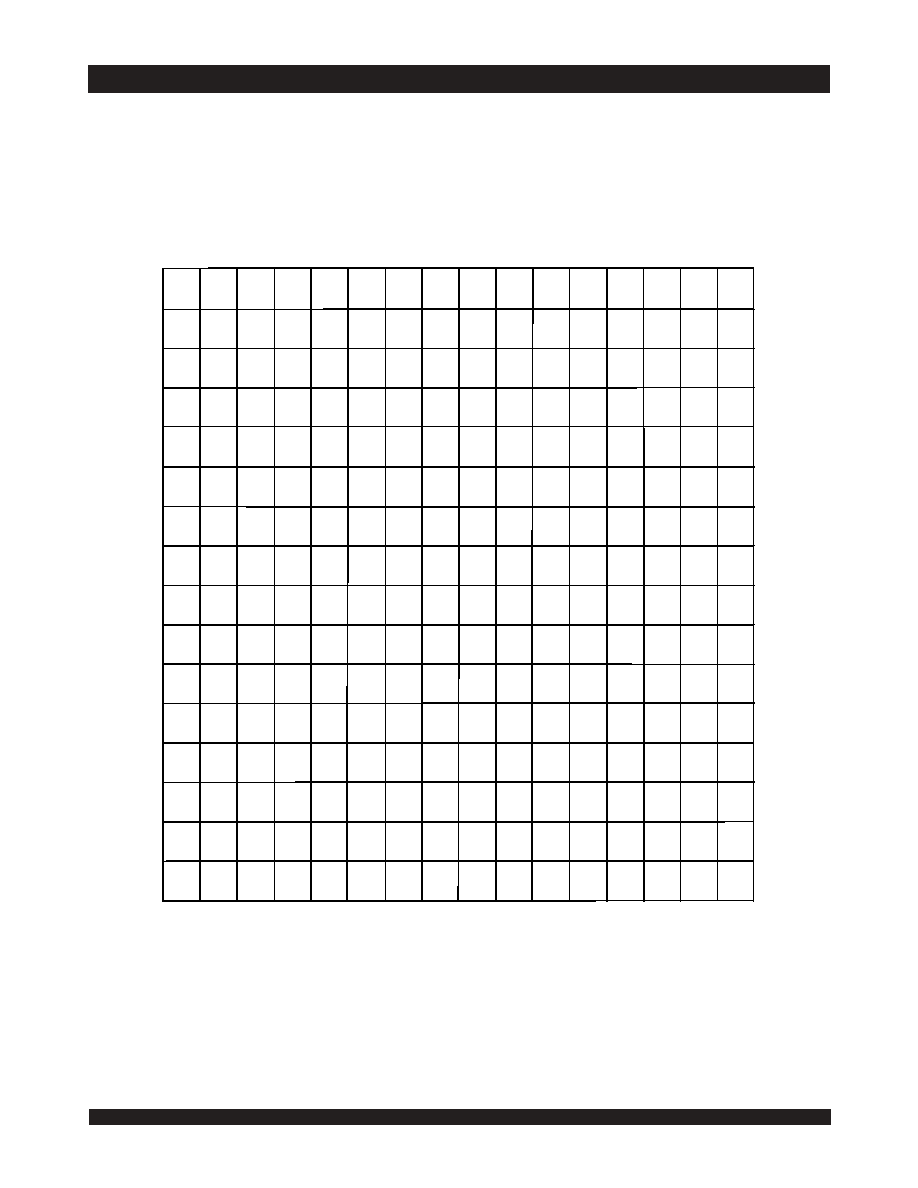

Functional Block Diagram

Full on-chip hardware support of semaphore signaling

between ports

Fully asynchronous operation from either port

Separate byte controls for multiplexed bus and bus

matching compatibility

Sleep Mode Inputs on both ports

Supports JTAG features compliant to IEEE 1149.1

Single 2.5V (±100mV) power supply for core

LVTTL-compatible, selectable 3.3V (±150mV)/2.5V (±100mV)

power supply for I/Os and control signals on each port

Available in a 256-ball Ball Grid Array, 208-pin Plastic Quad

Flatpack and 208-ball fine pitch Ball Grid Array.

Industrial temperature range (≠40∞C to +85∞C) is available

for selected speeds

Features

True Dual-Port memory cells which allow simultaneous

access of the same memory location

High-speed access

≠ Commercial: 10/12/15ns (max.)

≠ Industrial: 12ns (max.)

Dual chip enables allow for depth expansion without

external logic

IDT70T651/9 easily expands data bus width to 72 bits or

more using the Master/Slave select when cascading more

than one device

M/S = V

IH

for BUSY output flag on Master,

M/S = V

IL

for BUSY input on Slave

Busy and Interrupt Flags

On-chip port arbitration logic

HIGH-SPEED 2.5V

256/128K x 36

ASYNCHRONOUS DUAL-PORT

STATIC RAM

WITH 3.3V 0R 2.5V INTERFACE

PRELIMINARY

IDT70T651/9S

NOTES:

1. Address A

17x

is a NC for IDT70T659.

2. BUSY is an input as a Slave (M/S=V

IL

) and an output when it is a Master (M/S=V

IH

).

3. BUSY and INT are non-tri-state totem-pole outputs (push-pull).

4. The sleep mode pin shuts off all dynamic inputs, except JTAG inputs, when asserted. OPTx, BUSYx, INTx, M/S

and the sleep mode pins themselves (ZZx) are not affected during sleep mode.

IDT70T651/9S Preliminary

High-Speed 2.5V 256/128K x 36 Asynchronous Dual-Port Static RAM Industrial and Commercial Temperature Ranges

2

Description

The IDT70T651/9 is a high-speed 256/128K x 36 Asynchronous

Dual-Port Static RAM. The IDT70T651/9 is designed to be used as a

stand-alone 9216/4608K-bit Dual-Port RAM or as a combination MAS-

TER/SLAVE Dual-Port RAM for 72-bit-or-more word system. Using the

IDT MASTER/SLAVE Dual-Port RAM approach in 72-bit or wider

memory system applications results in full-speed, error-free operation

without the need for additional discrete logic.

This device provides two independent ports with separate control,

address, and I/O pins that permit independent, asynchronous access for

reads or writes to any location in memory. An automatic power down

feature controlled by the chip enables (either CE

0

or CE

1

) permit the

on-chip circuitry of each port to enter a very low standby power mode.

The 70T651/9 can support an operating voltage of either 3.3V or 2.5V

on one or both ports, controlled by the OPT pins. The power supply for

the core of the device (V

DD

) is at 2.5V.

3

IDT70T651/9S Preliminary

High-Speed 2.5V 256/128K x 36 Asynchronous Dual-Port Static RAM Industrial and Commercial Temperature Ranges

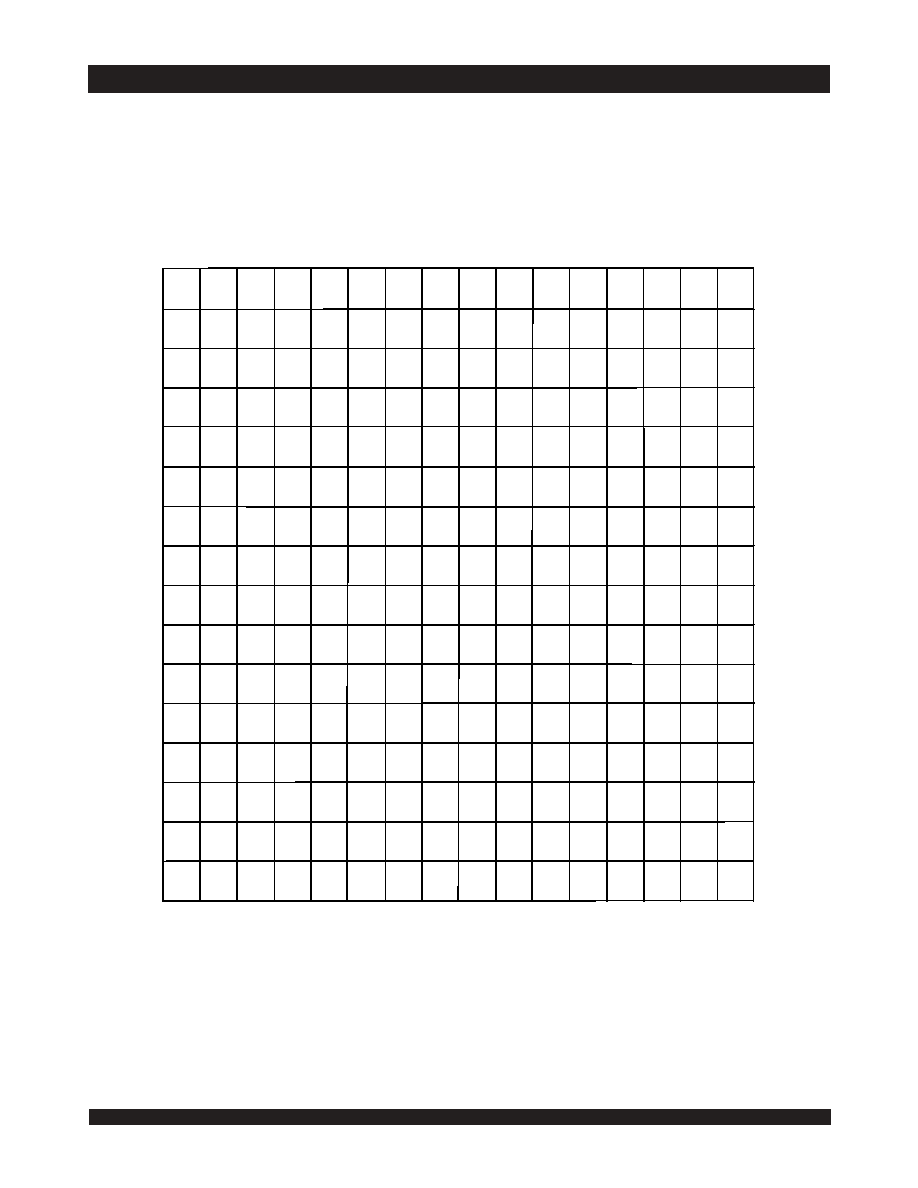

Pin Configuration

(1,2,3)

NOTES:

1. All V

DD

pins must be connected to 2.5V power supply.

2. All V

DDQ

pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to V

DD

(2.5V), and 2.5V if OPT pin for that port is

set to V

SS

(0V).

3. All V

SS

pins must be connected to ground supply.

4. A

17X

is a NC for IDT70T659.

5. Package body is approximately 17mm x 17mm x 1.4mm, with 1.0mm ball-pitch.

6. This package code is used to reference the package diagram.

70T651/9BC

BC-256

(5,6)

256-Pin BGA

Top View

E16

I/O

14R

D16

I/O

16R

C16

I/O

16L

B16

NC

A16

NC

A15

NC

B15

I/O

17L

C15

I/O

17R

D15

I/O

15L

E15

I/O

14L

E14

I/O

13L

D14

I/O

15R

D13

V

DD

C12

A

6L

C14

OPT

L

B14

NC

A14

A

0L

A12

A

5L

B12

A

4L

C11

BUSY

L

D12

V

DDQR

D11

V

DDQR

C10

SEM

L

B11

NC

A11

INT

L

D8

V

DDQR

C8

BE

1L

A9

CE

1L

D9

V

DDQL

C9

BE

0L

B9

CE

0L

D10

V

DDQL

C7

A

7L

B8

BE

3L

A8

BE

2L

B13

A

1L

A13

A

2L

A10

OE

L

D7

V

DDQR

B7

A

9L

A7

A

8L

B6

A

12L

C6

A

10L

D6

V

DDQL

A5

A

14L

B5

A

15L

C5

A

13L

D5

V

DDQL

A4

A

17L(4)

B4

NC

C4

A

16L

D4

V

DD

A3

NC

B3

TDO

C3

V

SS

D3

I/O

20L

D2

I/O

19R

C2

I/O

19L

B2

NC

A2

TDI

A1

NC

B1

I/O

18L

C1

I/O

18R

D1

I/O

20R

E1

I/O

21R

E2

I/O

21L

E3

I/O

22L

E4

V

DDQL

F1

I/O

23L

F2

I/O

22R

F3

I/O

23R

F4

V

DDQL

G1

I/O

24R

G2

I/O

24L

G3

I/O

25L

G4

V

DDQR

H1

I/O

26L

H2

I/O

25R

H3

I/O

26R

H4

V

DDQR

J1

I/O

27L

J2

I/O

28R

J3

I/O

27R

J4

V

DDQL

K1

I/O

29R

K2

I/O

29L

K3

I/O

28L

K4

V

DDQL

L1

I/O

30L

L2

I/O

31R

L3

I/O

30R

L4

V

DDQR

M1

I/O

32R

M2

I/O

32L

M3

I/O

31L

M4

V

DDQR

N1

I/O

33L

N2

I/O

34R

N3

I/O

33R

N4

V

DD

P1

I/O

35R

P2

I/O

34L

P3

TMS

P4

A

16R

R1

I/O

35L

R2

NC

R3

TRST

R4

NC

T1

NC

T2

TCK

T3

NC

T4

A

17R(4)

P5

A

13R

R5

A

15R

P12

A

6R

P8

BE

1R

P9

BE

0R

R8

BE

3R

T8

BE

2R

P10

SEM

R

T11

INT

R

P11

BUSY

R

R12

A

4R

T12

A

5R

P13

A

3R

P7

A

7R

R13

A

1R

T13

A

2R

R6

A

12R

T5

A

14R

T14

A

0R

R14

OPT

R

P14

I/O

0L

P15

I/O

0R

R15

NC

T15

NC

T16

NC

R16

NC

P16

I/O

1L

N16

I/O

2R

N15

I/O

1R

N14

I/O

2L

M16

I/O

4L

M15

I/O

3L

M14

I/O

3R

L16

I/O

5R

L15

I/O

4R

L14

I/O

5L

K16

I/O

7L

K15

I/O

6L

K14

I/O

6R

J16

I/O

8L

J15

I/O

7R

J14

I/O

8R

H16

I/O

10R

H15

IO

9L

H14

I/O

9R

G16

I/O

11R

G15

I/O

11L

G14

I/O

10L

F16

I/O

12L

F14

I/O

12R

F15

I/O

13R

R9

CE

0R

R11

M/

S

T6

A

11R

T9

CE

1R

A6

A

11L

B10

R/

W

L

C13

A

3L

P6

A

10R

R10

R/

W

R

R7

A

9R

T10

OE

R

T7

A

8R

,

E5

V

DD

E6

V

DD

E7

V

SS

E8

V

SS

E9

V

SS

E10

V

SS

E11

V

DD

E12

V

DD

E13

V

DDQR

F5

V

DD

F6

NC

F8

V

SS

F9

V

SS

F10

V

SS

F12

V

DD

F13

V

DDQR

G5

V

SS

G6

V

SS

G7

V

SS

G8

V

SS

G9

V

SS

G10

V

SS

G11

V

SS

G12

V

SS

G13

V

DDQL

H5

V

SS

H6

V

SS

H7

V

SS

H8

V

SS

H9

V

SS

H10

V

SS

H11

V

SS

H12

V

SS

H13

V

DDQL

J5

ZZ

R

J6

V

SS

J7

V

SS

J8

V

SS

J9

V

SS

J10

V

SS

J11

V

SS

J12

ZZ

L

J13

V

DDQR

K5

V

SS

K6

V

SS

K7

V

SS

K8

V

SS

L5

V

DD

L6

NC

L7

V

SS

L8

V

SS

M5

V

DD

M6

V

DD

M7

V

SS

M8

V

SS

N5

V

DDQR

N6

V

DDQR

N7

V

DDQL

N8

V

DDQL

K9

V

SS

K10

V

SS

K11

V

SS

K12

V

SS

L9

V

SS

L10

V

SS

L11

V

SS

L12

V

DD

M9

V

SS

M10

V

SS

M11

V

DD

M12

V

DD

N9

V

DDQR

N10

V

DDQR

N11

V

DDQL

N12

V

DDQL

K13

V

DDQR

L13

V

DDQL

M13

V

DDQL

N13

V

DD

F7

V

SS

F11

V

SS

5632 drw 02f

,

03/18/03

IDT70T651/9S Preliminary

High-Speed 2.5V 256/128K x 36 Asynchronous Dual-Port Static RAM Industrial and Commercial Temperature Ranges

4

NOTES:

1. All V

DD

pins must be connected to 2.5V power supply.

2. All V

DDQ

pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to V

DD

(2.5V) and 2.5V if OPT pin for that port is

set to V

SS

(0V).

3. All V

SS

pins must be connected to ground.

4. A

17X

is a NC for IDT70T659.

5. Package body is approximately 28mm x 28mm x 3.5mm.

6. This package code is used to reference the package diagram.

7. This text does not indicate orientation of the actual part-marking.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

5

3

5

4

5

5

5

6

5

7

5

8

5

9

6

0

6

1

6

2

6

3

6

4

6

5

6

6

6

7

6

8

6

9

7

0

7

1

7

2

7

3

7

4

7

5

7

6

7

7

7

8

7

9

8

0

8

1

8

2

8

3

8

4

8

5

8

6

8

7

8

8

8

9

9

0

9

1

9

2

9

3

9

4

9

5

9

6

9

7

9

8

9

9

1

0

0

1

0

1

1

0

2

1

0

3

1

0

4

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

2

0

8

2

0

7

2

0

6

2

0

5

2

0

4

2

0

3

2

0

2

2

0

1

2

0

0

1

9

9

1

9

8

1

9

7

1

9

6

1

9

5

1

9

4

1

9

3

1

9

2

1

9

1

1

9

0

1

8

9

1

8

8

1

8

7

1

8

6

1

8

5

1

8

4

1

8

3

1

8

2

1

8

1

1

8

0

1

7

9

1

7

8

1

7

7

1

7

6

1

7

5

1

7

4

1

7

3

1

7

2

1

7

1

1

7

0

1

6

9

1

6

8

1

6

7

1

6

6

1

6

5

1

6

4

1

6

3

1

6

2

1

6

1

1

6

0

1

5

9

1

5

8

1

5

7

70T651/9DR

DR-208

(5,6)

208-Pin

PQFP

Top View

(7)

I/O

19L

I/O

19R

I/O

20L

I/O

20R

V

DDQL

V

SS

I/O

21L

I/O

21R

I/O

22L

I/O

22R

V

DDQR

V

SS

I/O

23L

I/O

23R

I/O

24L

I/O

24R

V

DDQL

V

SS

I/O

25L

I/O

25R

I/O

26L

I/O

26R

V

DDQR

ZZ

R

V

DD

V

DD

V

SS

V

SS

V

DDQL

V

SS

I/O

27R

I/O

27L

I/O

28R

I/O

28L

V

DDQR

V

SS

I/O

29R

I/O

29L

I/O

30R

I/O

30L

V

DDQL

V

SS

I/O

31R

I/O

31L

I/O

32R

I/O

32L

V

DDQR

V

SS

I/O

33R

I/O

33L

I/O

34R

I/O

34L

V

S

S

V

D

D

Q

L

I

/

O

3

5

R

I

/

O

3

5

L

V

D

D

T

M

S

T

C

K

T

R

S

T

N

C

N

C

A

1

7

R

(

4

)

A

1

6

R

A

1

5

R

A

1

4

R

A

1

3

R

A

1

2

R

A

1

1

R

A

1

0

R

A

9

R

A

8

R

A

7

R

B

E

3

R

B

E

2

R

B

E

1

R

B

E

0

R

C

E

1

R

C

E

0

R

V

D

D

V

D

D

V

S

S

V

S

S

S

E

M

R

O

E

R

R

/

W

R

B

U

S

Y

R

I

N

T

R

M

/

S

A

6

R

A

5

R

A

4

R

A

3

R

A

2

R

A

1

R

A

0

R

V

D

D

V

S

S

V

S

S

O

P

T

R

I

/

O

0

L

I

/

O

0

R

V

D

D

Q

L

V

S

S

I/O

16L

I/O

16R

I/O

15L

I/O

15R

V

SS

V

DDQL

I/O

14L

I/O

14R

I/O

13L

I/O

13R

V

SS

V

DDQR

I/O

12L

I/O

12R

I/O

11L

I/O

11R

V

SS

V

DDQL

I/O

10L

I/O

10R

I/O

9L

I/O

9R

V

SS

V

DDQR

V

DD

V

DD

V

SS

V

SS

ZZ

L

V

DDQL

I/O

8R

I/O

8L

I/O

7R

I/O

7L

V

SS

V

DDQR

I/O

6R

I/O

6L

I/O

5R

I/O

5L

V

SS

V

DDQL

I/O

4R

I/O

4L

I/O

3R

I/O

3L

V

SS

V

DDQR

I/O

2R

I/O

2L

I/O

1R

I/O

1L

V

S

S

V

D

D

Q

R

I

/

O

1

8

R

I

/

O

1

8

L

V

S

S

V

D

D

T

D

I

T

D

O

N

C

N

C

A

1

7

L

(

4

)

A

1

6

L

A

1

5

L

A

1

4

L

A

1

3

L

A

1

2

L

A

1

1

L

A

1

0

L

A

9

L

A

8

L

A

7

L

B

E

3

L

B

E

2

L

B

E

1

L

B

E

0

L

C

E

1

L

C

E

0

L

V

D

D

V

D

D

V

S

S

V

S

S

S

E

M

L

O

E

L

R

/

W

L

B

U

S

Y

L

I

N

T

L

N

C

A

6

L

A

5

L

A

4

L

A

3

L

A

2

L

A

1

L

A

0

L

V

D

D

V

D

D

V

S

S

O

P

T

L

I

/

O

1

7

L

I

/

O

1

7

R

V

D

D

Q

R

V

S

S

5632 drw 02d

03/18/03

Pin Configurations

(1,2,3)

(con't.)

5

IDT70T651/9S Preliminary

High-Speed 2.5V 256/128K x 36 Asynchronous Dual-Port Static RAM Industrial and Commercial Temperature Ranges

Pin Configurations

(1,2,3)

(con't.)

NOTES:

1. All V

DD

pins must be connected to 2.5V power supply.

2. All V

DDQ

pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to V

DD

(2.5V) and 2.5V if OPT pin for that port is

set to V

SS

(0V).

3. All V

SS

pins must be connected to ground.

4. A

17X

is a NC for IDT70T659.

5. Package body is approximately 15mm x 15mm x 1.4mm with 0.8mm ball pitch.

6. This package code is used to reference the package diagram.

7. This text does not indicate orientation of the actual part-marking.

17

16

15

14

12

13

10

9

8

7

6

5

4

3

2

1

11

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

I/O

19L

I/O

18L

V

SS

A4

L

INT

L

SEM

L

BE

1L

A

8L

A

12L

A

16L

V

S S

I/O

17L

OPT

L

A

0L

I/O

20R

V

SS

I/O

18R

NC

A

1L

A5

L

BUSY

L

V

SS

CE

0L

CE

1L

BE

2L

A

9 L

A

13L

A

17L (4)

I/O16L

V

DD QR

V

S S

V

DD QL

I/O

19R

V

DD QR

V

DD

A

2L

A6

L

R/

W

L

V

SS

BE

3L

A

1 0L

A

14 L

NC

I/O

15L

I/O

16R

V

DD

I/O

22L

V

SS

I/O

21L

I/O

20L

V

D D

A

3

L

NC

OE

L

I/O

23L

I/O

22R

V

D DQ R

I/O

21R

V

DD QL

I/O

23R

I/O

24L

V

S S

I/O

26L

V

SS

I/O

25L

I/O

24R

V

DD

I/O

26R

V

DD QR

I/O

25R

V

DD QL

V

D D

V

SS

ZZ

R

I/O

29R

I/O

28L

V

D DQ R

V

DD QL

I/O

29L

I/O

30R

V

S S

I/O

14R

V

D DQ L

I/O

14L

A

15L

A

11L

A

7 L

BE

0L

I/O

12L

I/O

13R

V

S S

I/O

13L

V

S S

I/O

12R

I/O

11L

I/O

9L

V

DD QL

I/O

10L

I/O

11R

V

D D

I/O

9R

V

SS

I/O

10R

ZZ

L

V

DD QR

I/O

7R

V

D DQL

I/O8R

V

S S

I/O

8L

V

SS

I/O

7L

I/O

6R

A

0R

A

1R

A

2R

A

3R

A

4R

A

5 R

A

6R

I/O

3R

I/O

31L

V

SS

I/O

31R

I/O

30L

A

16R

A

12R

A

8R

BE

1R

V

DD

SEM

R

INT

R

V

DD QR

I/O

2L

I/O

3L

I/O

4L

V

S S

I/O

33L

I/O

34R

NC

A

13R

A

9R

BE

2R

CE

0

R

CE

1R

V

DD

V

SS

BUSY

R

V

S S

V

DD

V

S S

V

D DQ L

I/O

1R

V

DD QR

I/O

33R

I/O

34L

V

DD QL

NC

A

17R(4)

A

14R

A

1 0R

BE

3R

V

S S

I/O

4R

I/O

6L

V

S S

I/O

5R

I/O

2R

V

S S

I/O

35L

V

D D

A

15R

A

11R

A

7 R

BE

0R

OE

R

M/

S

R/

W

R

V

DD QL

I/O

5L

OPT

R

I/O

0L

I/O

1L

70T651/9BF

BF-208

(5,6)

208-Ball

fpBGA

Top View

(7)

5632 drw 02e

I/O

27L

I/O

28R

V

S S

I/O

27R

V

S S

I/O

32R

I/O

32L

V

D DQ R

I/O

3 5R

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

S S

I/O

0R

I/O

17R

V

DD QR

V

SS

V

DD

V

S S

I/O

15R

V

D D

V

DD

TDO

TDI

TCK

TMS

TRST

V

SS

03/18/03