| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 70V7339 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

©2002 Integrated Device Technology, Inc.

DECEMBER 2002

DSC 5628/6

1

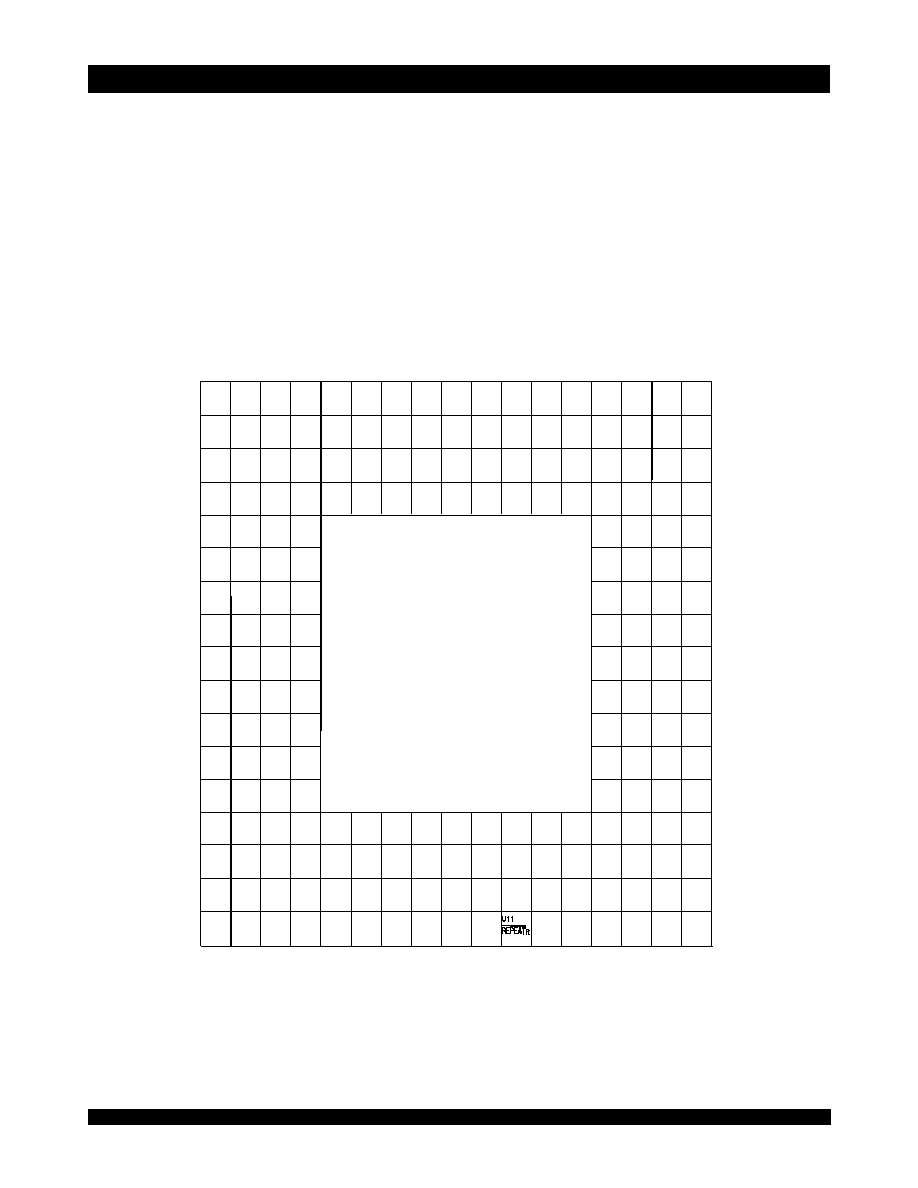

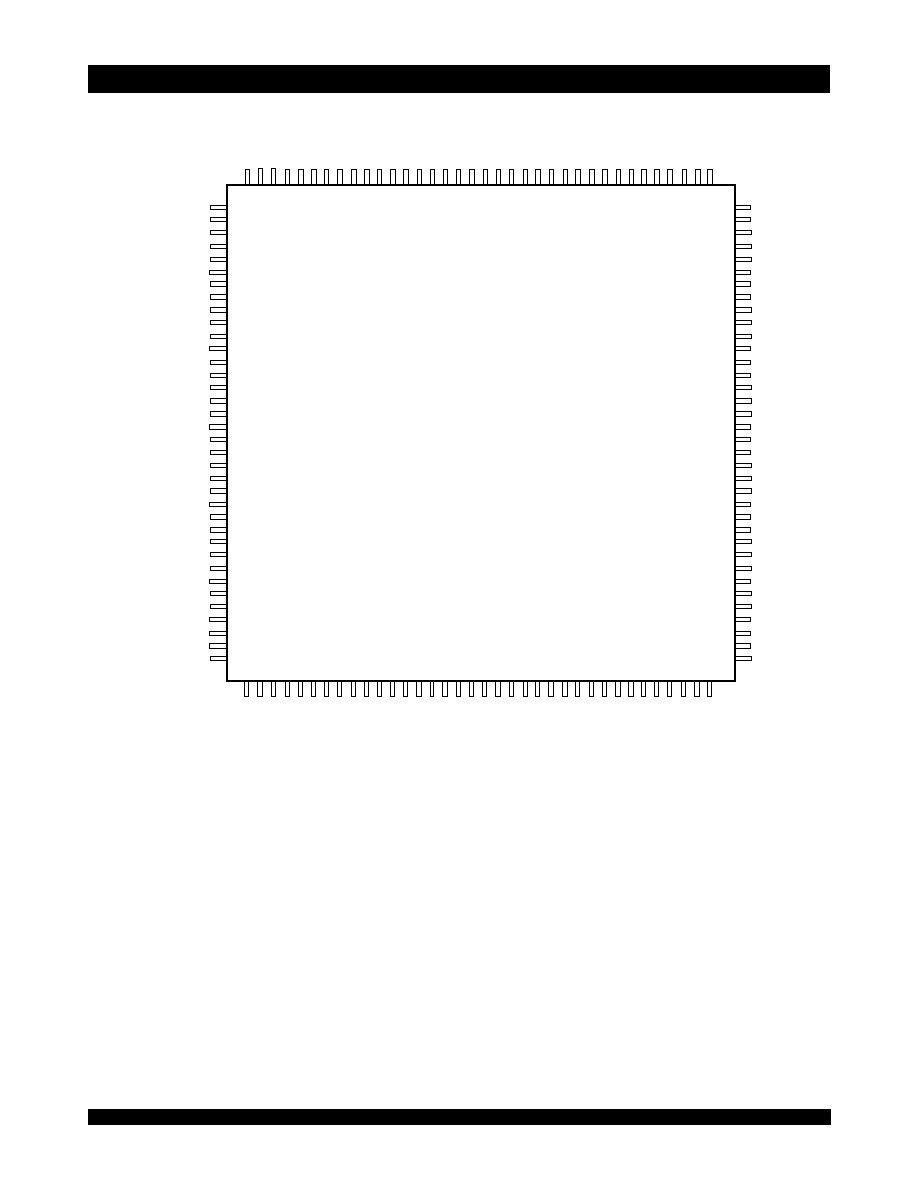

Functional Block Diagram

Features:

x

512K x 18 Synchronous Bank-Switchable Dual-ported

SRAM Architecture

≠ 64 independent 8K x 18 banks

≠ 9 megabits of memory on chip

x

Bank access controlled via bank address pins

x

High-speed data access

≠ Commercial: 3.4ns (200MHz)/3.6ns (166MHz)/

4.2ns (133MHz) (max.)

≠ Industrial: 3.6ns (166MHz)/4.2ns (133MHz) (max.)

x

Selectable Pipelined or Flow-Through output mode

x

Counter enable and repeat features

x

Dual chip enables allow for depth expansion without

additional logic

x

Full synchronous operation on both ports

≠ 5ns cycle time, 200MHz operation (14Gbps bandwidth)

≠ Fast 3.4ns clock to data out

≠ 1.5ns setup to clock and 0.5ns hold on all control, data, and

address inputs @ 200MHz

≠ Data input, address, byte enable and control registers

≠ Self-timed write allows fast cycle time

x

Separate byte controls for multiplexed bus and bus

matching compatibility

x

LVTTL- compatible, 3.3V (±150mV) power supply

for core

x

LVTTL compatible, selectable 3.3V (±150mV) or 2.5V

(±100mV) power supply for I/Os and control signals on

each port

x

Industrial temperature range (-40∞C to +85∞C) is

available at 166MHz and 133MHz

x

Available in a 144-pin Thin Quad Flatpack (TQFP),

208-pin fine pitch Ball Grid Array (fpBGA), and 256-pin Ball

Grid Array (BGA)

x

Supports JTAG features compliant with IEEE 1149.1

≠ Due to limited pin count, JTAG is not supported on the

144-pin TQFP package.

HIGH-SPEED 3.3V 512K x 18

SYNCHRONOUS

BANK-SWITCHABLE

DUAL-PORT STATIC RAM

WITH 3.3V OR 2.5V INTERFACE

IDT70V7339S

8Kx18

MEMORY

ARRAY

(BANK 63)

MUX

MUX

PL/

FT

L

OPT

L

CLK

L

ADS

L

CNTEN

L

REPEAT

L

R/

W

L

CE

0L

CE

1L

UB

L

LB

L

OE

L

I/O

0L-17L

A

12L

A

0L

JTAG

8Kx18

MEMORY

ARRAY

(BANK 1)

MUX

MUX

8Kx18

MEMORY

ARRAY

(BANK 0)

MUX

MUX

CONTROL

LOGIC

I/O

CONTROL

BANK

DECODE

ADDRESS

DECODE

I/O

0R-17R

A

12R

A

0R

CONTROL

LOGIC

I/O

CONTROL

BANK

DECODE

ADDRESS

DECODE

5628 drw 01

BA

5R

BA

4R

BA

3R

BA

2R

BA

1R

BA

0R

BA

5L

BA

4L

BA

3L

BA

2L

BA

1L

BA

0L

,

PL/

FT

R

OPT

R

CLK

R

ADS

R

CNTEN

R

REPEAT

R

R/

W

R

CE

0R

CE

1R

UB

R

LB

R

OE

R

TMS

TCK

TRST

TDI

TDO

NOTE:

1. The Bank-Switchable dual-port uses a true SRAM

core instead of the traditional dual-port SRAM core.

As a result, it has unique operating characteristics.

Please refer to the functional description on page 19

for details.

6.42

2

IDT70V7339S

High-Speed 512K x 18 Synchronous Bank-Switchable Dual-Port Static RAM Industrial and Commercial Temperature Ranges

Description:

The IDT70V7339 is a high-speed 512Kx18 (9Mbit) synchronous

Bank-Switchable Dual-Ported SRAM organized into 64 independent

8Kx18 banks. The device has two independent ports with separate

control, address, and I/O pins for each port, allowing each port to access

any 8Kx18 memory block not already accessed by the other port.

Accesses by the ports into specific banks are controlled via the bank

address pins under the user's direct control.

Registers on control, data, and address inputs provide minimal setup

and hold times. The timing latitude provided by this approach allows

systems to be designed with very short cycle times. With an input data

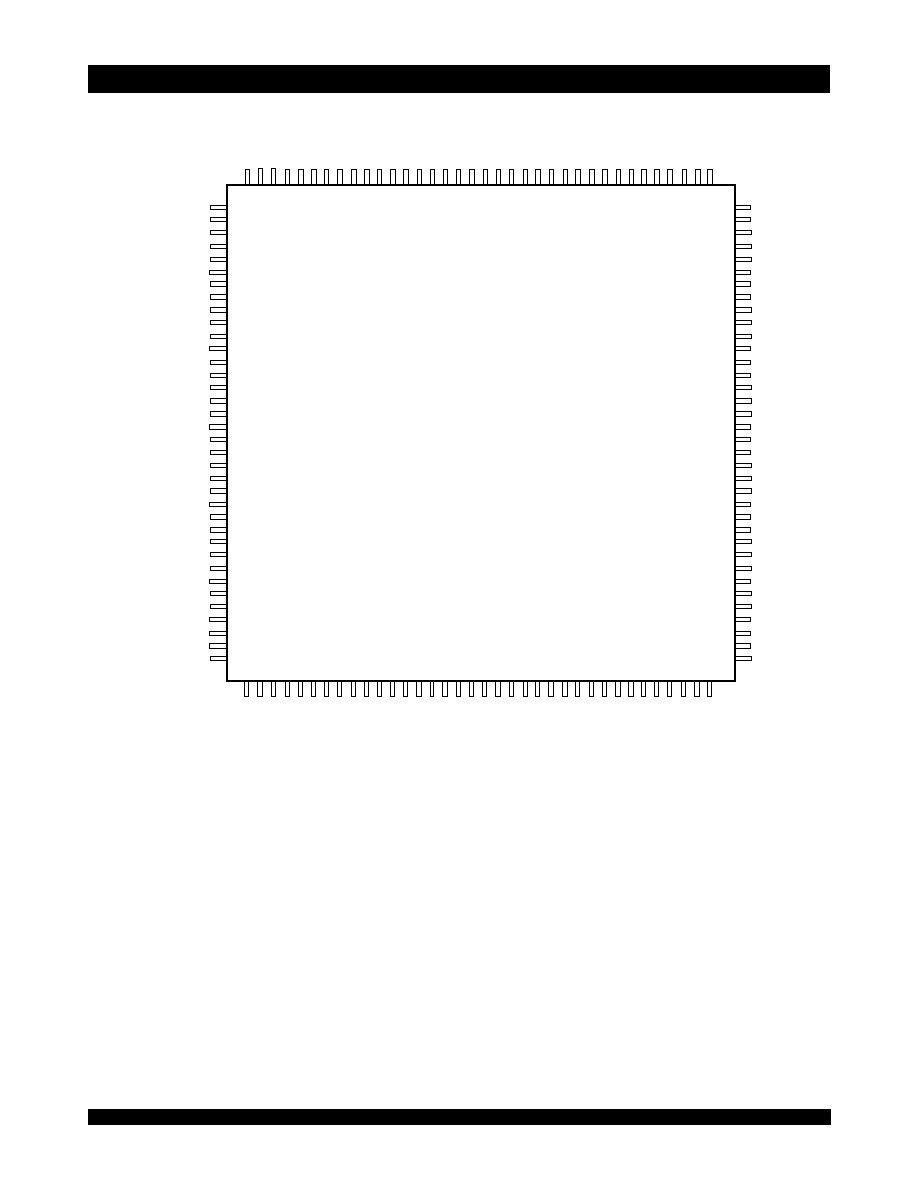

Pin Configuration

(1,2,3,4)

NOTES:

1. All V

DD

pins must be connected to 3.3V power supply.

2. All V

DDQ

pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to V

IH

(3.3V), and 2.5V if OPT pin for that port is

set to V

IL

(0V).

3. All V

SS

pins must be connected to ground supply.

4. Package body is approximately 15mm x 15mm x 1.4mm with 0.8mm ball pitch.

5. This package code is used to reference the package diagram.

6. This text does not indicate orientation of the actual part-marking.

A17

V

SS

B17

NC

C17

V

SS

D17

I/O

7R

E16

V

SS

E17

NC

D16

I/O

7L

C16

NC

B16

I/O

8L

A16

NC

A15

OPT

L

B15

V

DDQR

C15

I/O

8R

D15

V

DDQL

E15

NC

E14

I/O

6L

D14

NC

D13

V

DD

C12

A

6L

C14

V

DD

B14

V

SS

A14

A

0L

A12

CNTEN

L

B12

A

5L

C11

R/

W

L

D12

A

3L

D11

REPEAT

L

C10

V

SS

B11

ADS

L

A11

CLK

L

D8

LB

L

C8

UB

L

A9

NC

D9

V

DD

C9

CE

1L

B9

CE

0L

D10

OE

L

C7

A

10L

B8

NC

A8

A

8L

B13

A

1L

A13

A

4L

A10

V

DD

D7

A

7L

B7

A

9L

A7

A

12L

B6

BA

0L

C6

BA

1L

D6

A

11L

A5

NC

B5

BA

4L

C5

BA

5L

D5

BA

2L

A4

TDO

B4

TDI

C4

PL/

FT

L

D4

NC

A3

V

SS

B3

NC

C3

V

DDQR

D3

I/O

10L

D2

V

SS

C2

I/O

9R

B2

V

SS

A2

NC

A1

IO

9L

B1

NC

C1

V

DDQL

D1

NC

E1

I/O

11L

E2

NC

E3

V

DDQR

E4

I/O

10R

F1

V

DDQL

F2

I/O

11R

F3

NC

F4

V

SS

G1

NC

G2

V

SS

G3

I/O

12L

G4

NC

H1

V

DD

H2

NC

H3

V

DDQR

H4

I/O

12R

J1

V

DDQL

J2

V

DD

J3

V

SS

J4

V

SS

K1

I/O

14R

K2

V

SS

K3

I/O

13R

K4

V

SS

L1

NC

L2

I/O

14L

L3

V

DDQR

L4

I/O

13L

M1

V

DDQL

M2

NC

M3

I/O

15R

M4

V

SS

N1

NC

N2

V

SS

N3

NC

N4

I/O

15L

P1

I/O

16R

P2

I/O

16L

P3

V

DDQR

P4

NC

R1

V

SS

R2

NC

R3

I/O

17R

R4

TCK

T1

NC

T2

I/O

17L

T3

V

DDQL

T4

TMS

U1

V

SS

U2

NC

U3

PL/

FT

R

U4

NC

P5

TRST

R5

BA

4R

U6

A

11R

P12

CNTEN

R

P8

A

8R

U10

OE

R

P9

NC

R8

NC

T8

UB

R

U9

V

DD

P10

V

DD

T11

R/

W

R

U8

LB

R

P11

CLK

R

R12

A

5R

T12

A

6R

U12

A

3R

P13

A

4R

P7

A

12R

R13

A

1R

T13

A

2R

U13

A

0R

R6

BA

0R

T5

BA

5R

U7

A

7R

U14

V

DD

T14

V

SS

R14

V

SS

P14

NC

P15

I/O

1L

R15

V

DDQL

T15

NC

U15

OPT

R

U16

NC

U17

I/O

0L

T16

V

SS

T17

NC

R17

V

DDQR

R16

I/O

0R

P17

NC

P16

V

SS

N17

I/O

2L

N16

NC

N15

V

DDQL

N14

I/O

1R

M17

V

DDQR

M16

I/O

2R

M15

NC

M14

V

SS

L17

I/O

4L

L16

V

SS

L15

I/O

3L

L14

NC

K17

V

SS

K16

I/O

4R

K15

V

DDQL

K14

I/O

3R

J17

V

DDQR

J16

V

SS

J15

V

DD

J14

V

SS

H17

I/O

5R

H16

V

SS

H15

NC

H14

V

DD

G17

NC

G16

I/O

5L

G15

V

DDQL

G14

NC

F17

V

DDQR

F16

NC

F14

V

SS

70V7339BF

BF-208

(5)

208-Pin fpBGA

Top View

(6)

F15

I/O

6R

R9

CE

0R

R11

ADS

R

T6

BA

1R

T9

CE

1R

A6

BA

3L

B10

V

SS

C13

A

2L

P6

BA

3R

R10

V

SS

R7

A

9R

T10

V

SS

T7

A

10R

U5

BA

2R

5628 drw 02c

,

1 1 /2 0 /0 1

register, the IDT70V7339 has been optimized for applications having

unidirectional or bidirectional data flow in bursts. An automatic power down

feature, controlled by CE

0

and CE

1

, permits the on-chip circuitry of each

port to enter a very low standby power mode. The dual chip enables also

facilitate depth expansion.

The 70V7339 can support an operating voltage of either 3.3V or 2.5V

on one or both ports, controllable by the OPT pins. The power supply for

the core of the device(V

DD

) remains at 3.3V. Please refer also to the

functional description on page 19.

6.42

IDT70V7339S

High-Speed 512K x 18 Synchronous Bank-Switchable Dual-Port Static RAM Industrial and Commercial Temperature Ranges

3

Pin Configuration

(1,2,3,4)

(con't.)

NOTES:

1. All V

DD

pins must be connected to 3.3V power supply.

2. All V

DDQ

pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to V

IH

(3.3V), and 2.5V if OPT pin for that port is

set to V

IL

(0V).

3. All V

SS

pins must be connected to ground supply.

4. Package body is approximately 17mm x 17mm x 1.4mm, with 1.0mm ball-pitch.

5. This package code is used to reference the package diagram.

6. This text does not indicate orientation of the actual part-marking.

70V7339BC

BC-256

(5)

256-Pin BGA

Top View

(6)

E16

I/O

7R

D16

I/O

8R

C16

I/O

8L

B16

NC

A16

NC

A15

NC

B15

NC

C15

NC

D15

NC

E15

I/O

7L

E14

NC

D14

NC

D13

V

DD

C12

A

6L

C14

OPT

L

B14

V

DD

A14

A

0L

A12

A

5L

B12

A

4L

C11

ADS

L

D12

V

DDQR

D11

V

DDQR

C10

CLK

L

B11

REPEAT

L

A11

CNTEN

L

D8

V

DDQR

C8

NC

A9

CE

1L

D9

V

DDQL

C9

LB

L

B9

CE

0L

D10

V

DDQL

C7

A

7L

B8

UB

L

A8

NC

B13

A

1L

A13

A

2L

A10

OE

L

D7

V

DDQR

B7

A

9L

A7

A

8L

B6

A

12L

C6

A

10L

D6

V

DDQL

A5

BA1

L

B5

BA

2L

C5

BA

0L

D5

V

DDQL

A4

BA

4L

B4

BA

5L

C4

BA

3L

D4

PL/

FT

L

A3

NC

B3

TDO

C3

V

SS

D3

NC

D2

I/O

9R

C2

I/O

9L

B2

NC

A2

TDI

A1

NC

B1

NC

C1

NC

D1

NC

E1

I/O

10R

E2

I/O

10L

E3

NC

E4

V

DDQL

F1

I/O

11L

F2

NC

F3

I/O

11R

F4

V

DDQL

G1

NC

G2

NC

G3

I/O

12L

G4

V

DDQR

H1

NC

H2

I/O

12R

H3

NC

H4

V

DDQR

J1

I/O

13L

J2

I/O

14R

J3

I/O

13R

J4

V

DDQL

K1

NC

K2

NC

K3

I/O

14L

K4

V

DDQL

L1

I/O

15L

L2

NC

L3

I/O

15R

L4

V

DDQR

M1

I/O

16R

M2

I/O

16L

M3

NC

M4

V

DDQR

N1

NC

N2

I/O

17R

N3

NC

N4

PL/

FT

R

P1

NC

P2

I/O

17L

P3

TMS

P4

BA

3R

R1

NC

R2

NC

R3

TRST

R4

BA

5R

T1

NC

T2

TCK

T3

NC

T4

BA

4R

P5

BA

0R

R5

BA

2R

P12

A

6R

P8

NC

P9

LB

R

R8

UB

R

T8

NC

P10

CLK

R

T11

CNTEN

R

P11

ADS

R

R12

A

4R

T12

A

5R

P13

A

3R

P7

A

7R

R13

A

1R

T13

A

2R

R6

A

12R

T5

BA

1R

T14

A

0R

R14

OPT

R

P14

NC

P15

NC

R15

NC

T15

NC

T16

NC

R16

NC

P16

I/O

0L

N16

NC

N15

I/O

0R

N14

NC

M16

NC

M15

I/O

1L

M14

I/O

1R

L16

I/O

2R

L15

NC

L14

I/O

2L

K16

I/O

3L

K15

NC

K14

NC

J16

I/O

4L

J15

I/O

3R

J14

I/O

4R

H16

I/O

5R

H15

NC

H14

NC

G16

NC

G15

NC

G14

I/O

5L

F16

I/O

6L

F14

I/O

6R

F15

NC

R9

CE

0R

R11

REPEAT

R

T6

A

11R

T9

CE

1R

A6

A

11L

B10

R/

W

L

C13

A

3L

P6

A

10R

R10

R/

W

R

R7

A

9R

T10

OE

R

T7

A

8R

,

E5

V

DD

E6

V

DD

E7

V

SS

E8

V

SS

E9

V

SS

E10

V

SS

E11

V

DD

E12

V

DD

E13

V

DDQR

F5

V

DD

F6

V

SS

F8

V

SS

F9

V

SS

F10

V

SS

F12

V

DD

F13

V

DDQR

G5

V

SS

G6

V

SS

G7

V

SS

G8

V

SS

G9

V

SS

G10

V

SS

G11

V

SS

G12

V

SS

G13

V

DDQL

H5

V

SS

H6

V

SS

H7

V

SS

H8

V

SS

H9

V

SS

H10

V

SS

H11

V

SS

H12

V

SS

H13

V

DDQL

J5

V

SS

J6

V

SS

J7

V

SS

J8

V

SS

J9

V

SS

J10

V

SS

J11

V

SS

J12

V

SS

J13

V

DDQR

K5

V

SS

K6

V

SS

K7

V

SS

K8

V

SS

L5

V

DD

L6

V

SS

L7

V

SS

L8

V

SS

M5

V

DD

M6

V

DD

M7

V

SS

M8

V

SS

N5

V

DDQR

N6

V

DDQR

N7

V

DDQL

N8

V

DDQL

K9

V

SS

K10

V

SS

K11

V

SS

K12

V

SS

L9

V

SS

L10

V

SS

L11

V

SS

L12

V

DD

M9

V

SS

M10

V

SS

M11

V

DD

M12

V

DD

N9

V

DDQR

N10

V

DDQR

N11

V

DDQL

N12

V

DDQL

K13

V

DDQR

L13

V

DDQL

M13

V

DDQL

N13

V

DD

F7

V

SS

F11

V

SS

5628 drw 02d

,

11/20/01

6.42

4

IDT70V7339S

High-Speed 512K x 18 Synchronous Bank-Switchable Dual-Port Static RAM Industrial and Commercial Temperature Ranges

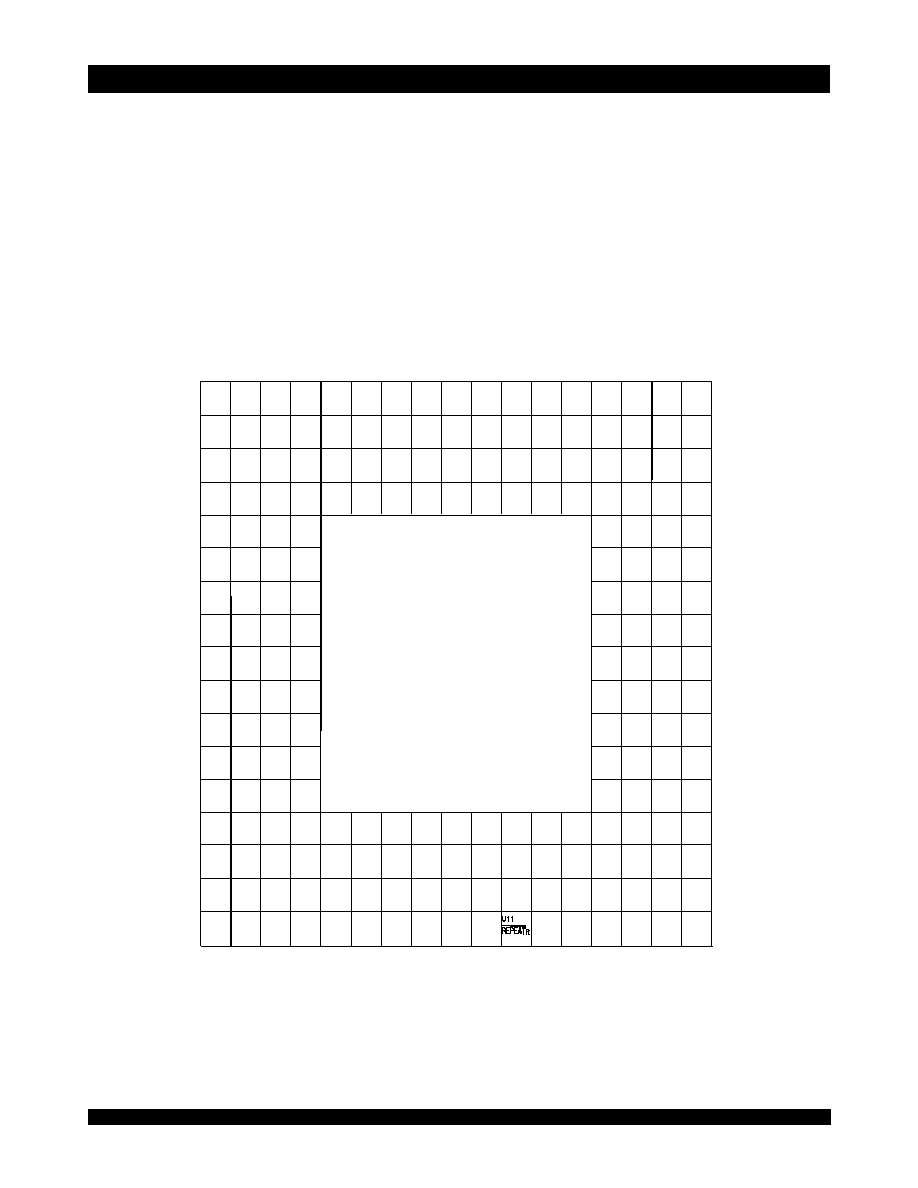

Pin Configuration

(1,2,3,4,7)

(con't.)

NOTES:

1. All V

DD

pins must be connected to 3.3V power supply.

2. All V

DDQ

pins must be connected to appropriate power supply: 3.3V if OPT pin for that port is set to V

IH

(3.3V), and 2.5V if OPT pin for that port is set to V

IL

(0V).

3. All V

SS

pins must be connected to ground supply.

4. Package body is approximately 20mm x 20mm x 1.4mm.

5. This package code is used to reference the package diagram.

6. This text does not indicate orientation of the actual part-marking.

7. Due to the limited pin count, JTAG is not supported in the DD-144 package.

V

SS

V

DDQR

V

SS

I/O

9L

I/O

9R

I/O

10L

I/O

10R

I/O

11L

I/O

11R

V

DDQL

V

SS

I/O

12L

I/O

12R

V

DDQR

V

SS

V

DD

V

DD

V

SS

V

SS

V

DDQL

V

SS

I/O

13R

I/O

13L

I/O

14R

I/O

14L

V

DDQR

V

SS

I/O

15R

I/O

15L

I/O

16R

I/O

16L

I/O

17R

I/O

17L

V

SS

V

DDQL

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

1

44

1

43

1

42

1

41

1

40

1

39

1

38

1

37

1

36

1

35

1

34

1

33

1

32

1

31

1

30

1

29

1

28

1

27

1

26

1

25

1

24

1

23

1

22

1

21

1

20

1

19

1

18

1

17

1

16

1

15

1

14

1

13

1

12

1

11

1

10

1

09

P

L/

FT

R

N

C

N

C

B

A

5R

B

A

4R

B

A

3R

B

A

2R

B

A

1R

B

A

0R

A

12R

A

11R

A

10R

A

9R

A

8R

A

7R

U

B

R

LB

R

C

E

1R

C

E

0R

V

D

D

V

S

S

C

LK

R

O

E

R

R

/

W

R

A

D

S

R

C

N

T

E

N

R

R

E

P

E

A

T

R

A

6R

A

5R

A

4R

A

3R

A

2R

A

1R

A

0R

V

D

D

V

S

S

OPT

L

V

DDQR

V

SS

I/O

8L

I/O

8R

I/O

7L

I/O

7R

I/O

6L

I/O

6R

V

SS

V

DDQL

I/O

5L

I/O

5R

V

SS

V

DDQR

V

DD

V

DD

V

SS

V

SS

V

SS

V

DDQL

I/O

4R

I/O

4L

I/O

3R

I/O

3L

V

SS

V

DDQR

I/O

2R

I/O

2L

I/O

1R

I/O

1L

I/O

0R

I/O

0L

V

SS

V

DDQL

OPT

R

P

L

/

FT

L

N

C

N

C

B

A

5L

B

A

4L

B

A

3L

B

A

2L

B

A

1L

B

A

0L

A

1

2L

A

1

1L

A

1

0L

A

9

L

A

8

L

A

7

L

U

B

L

L

B

L

C

E

1L

C

E

0L

V

D

D

V

S

S

C

LK

L

O

E

L

R

/

W

L

A

D

S

L

C

N

T

E

N

L

R

E

P

E

A

T

L

A

6

L

A

5

L

A

4

L

A

3

L

A

2

L

A

1

L

A

0

L

V

D

D

V

S

S

70V7339DD

DD-144

(5)

144-Pin TQFP

Top View

(6)

5628 drw 02a

11/20/01

6.42

IDT70V7339S

High-Speed 512K x 18 Synchronous Bank-Switchable Dual-Port Static RAM Industrial and Commercial Temperature Ranges

5

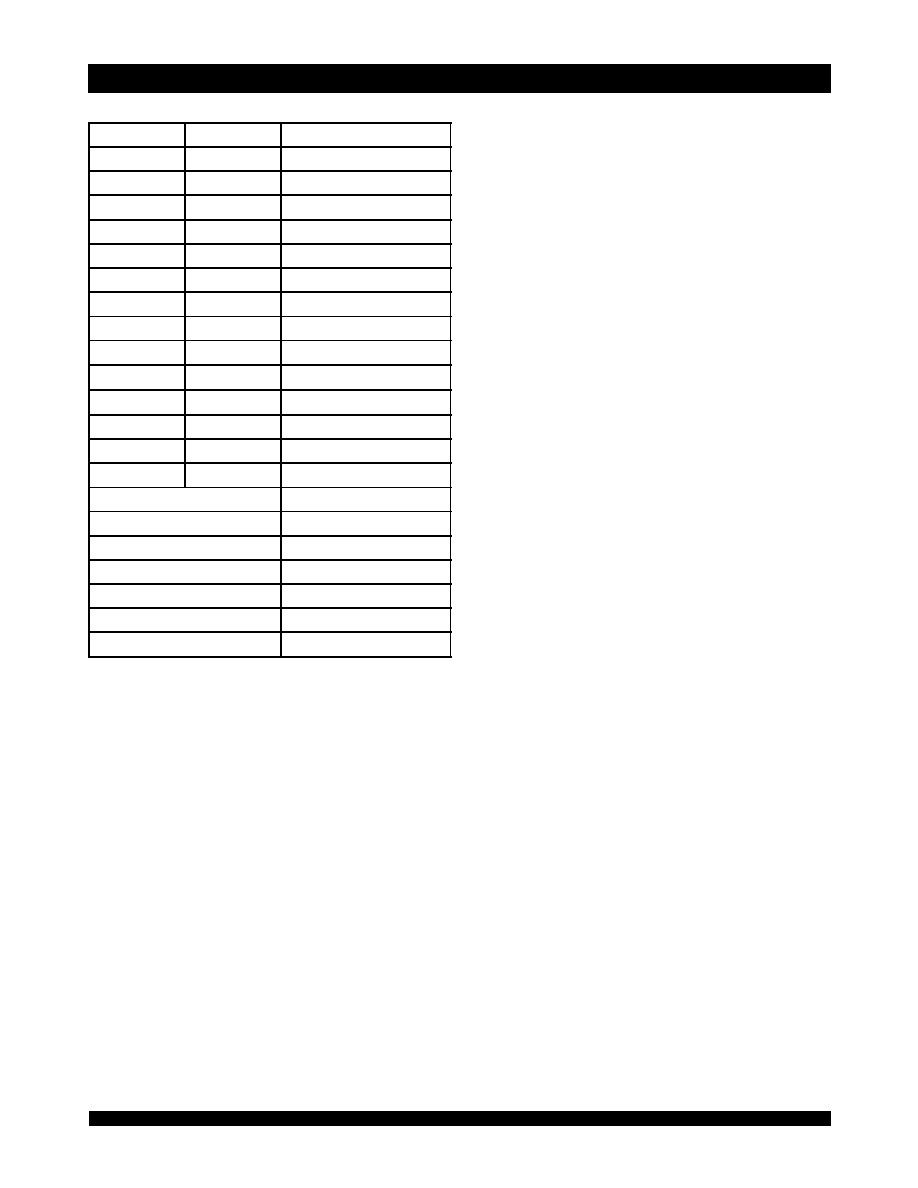

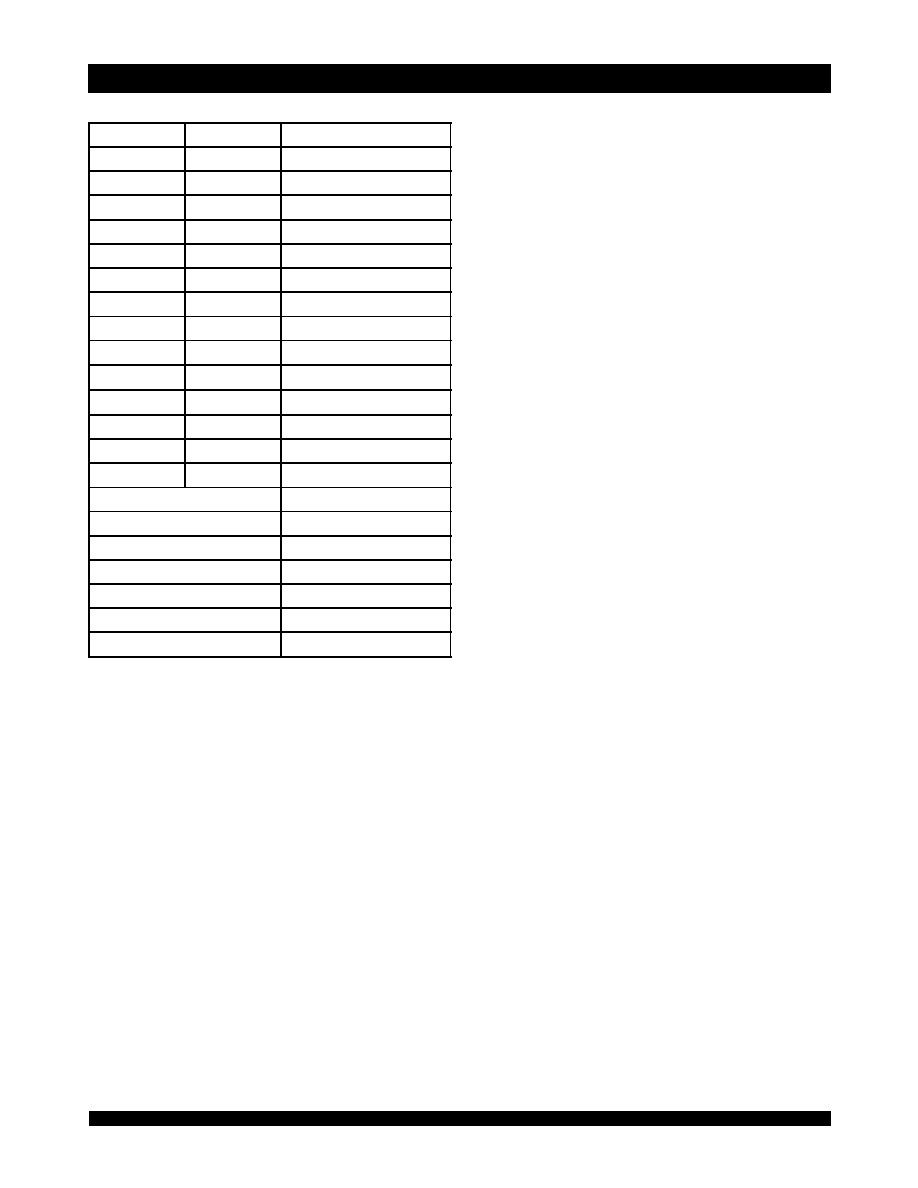

Pin Names

Left Port

Right Port

Names

CE

0L

,

CE

1L

CE

0R

,

CE

1R

Chip Enables

R/

W

L

R/

W

R

Read/Write Enable

OE

L

OE

R

Output Enable

BA

0L

- BA

5L

BA

0R

- BA

5R

Bank Address

(4)

A

0L

- A

12L

A

0R

- A

12R

Address

I/O

0L

- I/O

17L

I/O

0R

- I/O

17R

Data Input/Output

CLK

L

CLK

R

Clock

PL/

FT

L

PL/

FT

R

Pipeline/Flow-Through

ADS

L

ADS

R

Address Strobe Enable

CNTEN

L

CNTEN

R

Counter Enable

REPEAT

L

REPEAT

R

Counter Repeat

(3)

LB

L

,

UB

L

LB

R

,

UB

R

Byte Enables (9-bit bytes)

V

DDQL

V

DDQR

Power (I/O Bus) (3.3V or 2.5V)

(1)

OPT

L

OPT

R

Option for selecting V

DDQX

(1,2)

V

DD

Power (3.3V)

(1)

V

SS

Ground (0V)

TDI

Test Data Input

TDO

Test Data Output

TCK

Test Logic Clock (10MHz)

TMS

Test Mode Select

TRST

Reset (Initialize TAP Controller)

5628 tbl 01

NOTES:

1. V

DD

, OPT

X

, and V

DDQX

must be set to appropriate operating levels prior to

applying inputs on the I/Os and controls for that port.

2. OPT

X

selects the operating voltage levels for the I/Os and controls on that port.

If OPT

X

is set to VIH (3.3V), then that port's I/Os and controls will operate at 3.3V

levels and V

DDQX

must be supplied at 3.3V. If OPT

X

is set to VIL (0V), then that

port's I/Os and address controls will operate at 2.5V levels and V

DDQX

must be

supplied at 2.5V. The OPT pins are independent of one another--both ports can

operate at 3.3V levels, both can operate at 2.5V levels, or either can operate

at 3.3V with the other at 2.5V.

3. When

REPEAT

X

is asserted, the counter will reset to the last valid address loaded

via

ADS

X

.

4. Accesses by the ports into specific banks are controlled by the bank address

pins under the user's direct control: each port can access any bank of memory

with the shared array that is not currently being accessed by the opposite port

(i.e., BA

0L

- BA

5L

BA

0R

- BA

5R

). In the event that both ports try to access the

same bank at the same time, neither access will be valid, and data at the two

specific addresses targeted by the ports within that bank may be corrupted (in

the case that either or both ports are writing) or may result in invalid output (in

the case that both ports are trying to read).