HYS72T[64/128]3x0HP≠3S≠A

HYS72T[64/128]3x0HP≠3.7≠A

240-Pin Registered DDR2 SDRAM Modules

DDR2 SDRAM

RDIMM SDRAM

RoHs Compliant

Data Sheet, Rev. 1.11, Dec. 2005

Memory Products

Edition 2005-12

Published by Infineon Technologies AG,

St.-Martin-Strasse 53,

81669 M¸nchen, Germany

©

Infineon Technologies AG 2005.

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding

circuits, descriptions and charts stated herein.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office (

www.infineon.com

).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

Template: mp_a4_s_rev321 / 3 / 2005-10-05

HYS72T[64/128]3x0HP≠3S≠A, HYS72T[64/128]3x0HP≠3.7≠A

Revision History: 2005-12, Rev. 1.11

Page

Subjects (major changes since last revision)

Removed "Preliminary" from data sheet.

Previous Version: 2005-12 Rev. 1.1

All

Product portfolio changed - HR products replaced by HP (Parity)

Chapter 2 Pin Configuration updated for parity

Chapter 4 SPD Codes updated

Chapter 5 Replaced Package Outline L-DIM 240-52

Previous Version: 2005-06 Rev. 1.0

Initial revision

SPD Code Rev. 1.2

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send us your proposal (including a reference to this document) to:

techdoc.mp@infineon.com

Data Sheet

4

Rev. 1.11, 2005-12

04212005-MF7V-DNO1

HYS72T[64/128]3x0HP≠[3S/3.7]≠A

Registered DDR2 SDRAM Modules

Table of Contents

1

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.2

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2

Pin Configuration and Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.1

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.2

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.1

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.2

DC Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.3

AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.3.1

Speed Grades Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.3.2

AC Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.3.3

ODT AC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.4

Currents Specifications and Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

3.4.1

I

DD

Test Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.4.2

On Die Termination (ODT) Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4

SPD Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5

Package Outlines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

6

Product Type Nomenclature (DDR2 DRAMs and DIMMs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table of Contents

Data Sheet

5

Rev. 1.11, 2005-12

04212005-MF7V-DNO1

240-Pin Registered DDR2 SDRAM Modules

DDR2 SDRAM

HYS72T[64/128]3x0HP≠3S≠A

HYS72T[64/128]3x0HP≠3.7≠A

1

Overview

This chapter gives an overview of the 240-pin Registered DDR2 SDRAM Modules product family and describes

its main characteristics.

1.1

Features

∑

240-pin PC2-5300 and PC2-4200 DDR2 SDRAM

memory modules for PC, Workstation and Server

main memory applications

∑

One rank 64M x 72, 128M x 72 and two ranks

64M x 72, 128M

◊ 72 module organization and

64M

◊ 8, 128M ◊ 4 chip organization

∑

512 MByte and 1GByte module built with 512-Mbit

DDR2 SDRAMs in P-TFBGA-60 chipsize

packages.

∑

Standard Double-Data-Rate-Two Synchronous

DRAMs (DDR2 SDRAM) with a single + 1.8 V

(

± 0.1 V) power supply

∑

All speed grades faster than DDR2-400 comply with

DDR2-400 timing specifications as well.

∑

VLP (Very Low Profile) Registered DIMM Parity bit

for address and control bus

∑

Programmable CAS Latencies (3, 4 & 5), Burst

Length (4 & 8) and Burst Type

∑

Auto Refresh (CBR) and Self Refresh

∑

All inputs and outputs SSTL_18 compatible

∑

Off-Chip Driver Impedance Adjustment (OCD) and

On-Die Termination (ODT)

∑

Serial Presence Detect with E

2

PROM

∑

Based on standard reference layouts Raw Card "R",

"T" and "U"

∑

RDIMM with parity Dimensions (nominal):

17.80 mm high, 133.35 mm wide

∑

RoHS compliant products

1)

1) RoHS Compliant Product: Restriction of the use of certain hazardous substances (RoHS) in electrical and electronic

equipment as defined in the directive 2002/95/EC issued by the European Parliament and of the Council of 27 January

2003. These substances include mercury, lead, cadmium, hexavalent chromium, polybrominated biphenyls and

polybrominated biphenyl ethers.

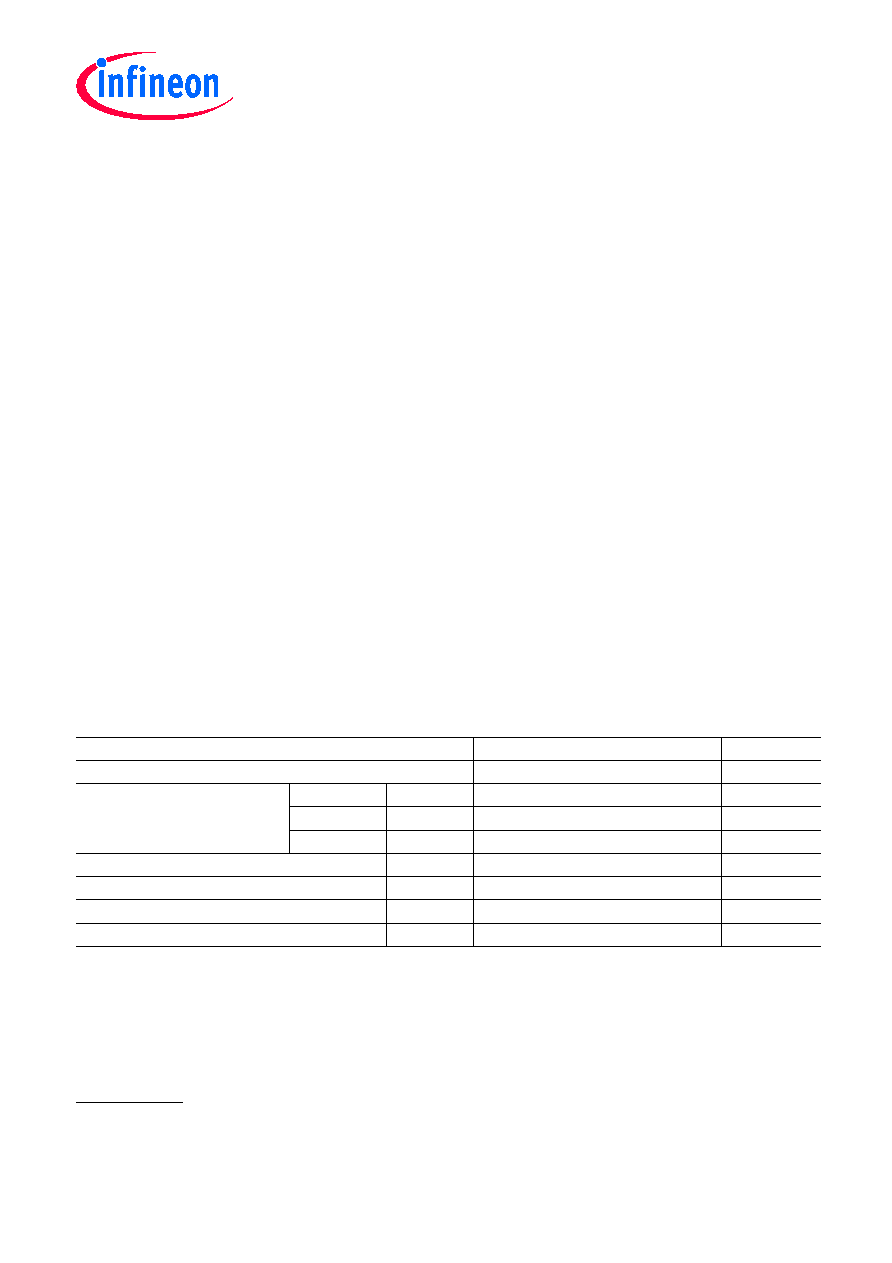

Table 1

Performance for DDR2≠667

Product Type Speed Code

≠3S

Unit

Speed Grade

PC2≠5300 5≠5≠5

--

max. Clock Frequency

@CL5

f

CK5

333

MHz

@CL4

f

CK4

266

MHz

@CL3

f

CK3

200

MHz

min. RAS-CAS-Delay

t

RCD

15

ns

min. Row Precharge Time

t

RP

15

ns

min. Row Active Time

t

RAS

45

ns

min. Row Cycle Time

t

RC

60

ns