Data Sheet

1

2002-03-22

3.3 V, 4-Line LVDS Parallel

2.5 GBd Transponder

OC-48 SONET/SDH

Short Reach (SR) up to 2 km

V23816-N1018-C312-A

V23816-N1018-L312-A

Preliminary Data

Part Number

Connector Type

Fiber Length

V23816-N1018-C312-A

SC

24.1 ±0.8 "

V23816-N1018-L312-A

LC

24.1 ±0.8 "

Fiber Optics

Features

∑ Compliant with existing standards

∑ Compact integrated transponder unit with

≠ FP laser diode transmitter

≠ InGaAs PIN photodiode receiver

≠ Pigtailed optical connections

≠ Integrated Mux, Demux and Clock Recovery

∑ Class 1 FDA and IEC laser safety compliant

∑ Single +3.3 V power supply

∑ OC-48 optical transmit and receive at

2488.32 Mbit/s

∑ 4-line LVDS differential interface at 622.08 Mbit/s

∑ External control for laser shutoff

∑ Loss of optical signal and Loss of synch indicators (Rx)

∑ Loss of lock indicator for Tx high speed clock

∑ Laser bias monitor

∑ Rx power monitor output

∑ Loopback operating modes

∑ 155.520 MHz LVPECL input Tx reference clock

∑ 2.8 W Typical Power Consumption

∑ Tx Fault output indicator

V23816-N1018-C312-A

V23816-N1018-L312-A

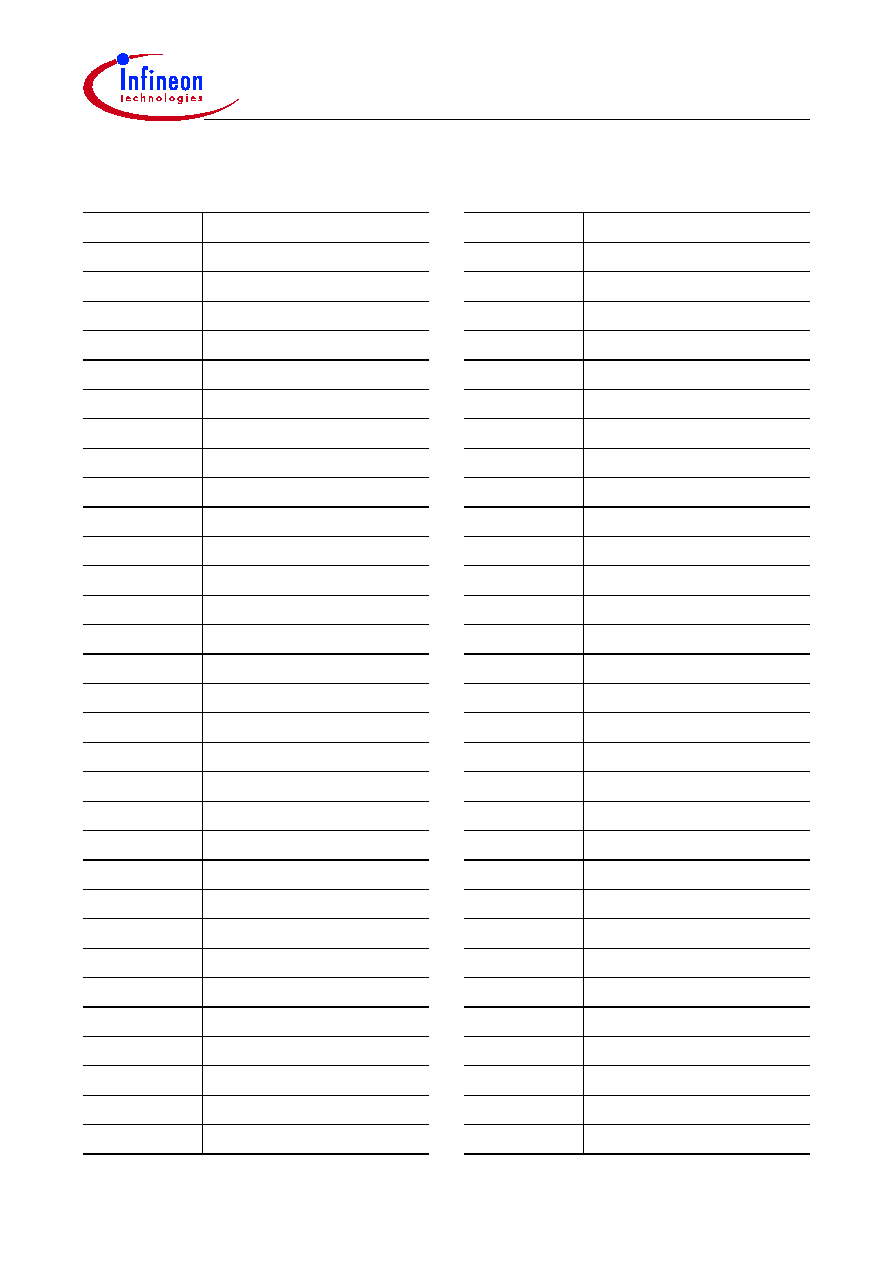

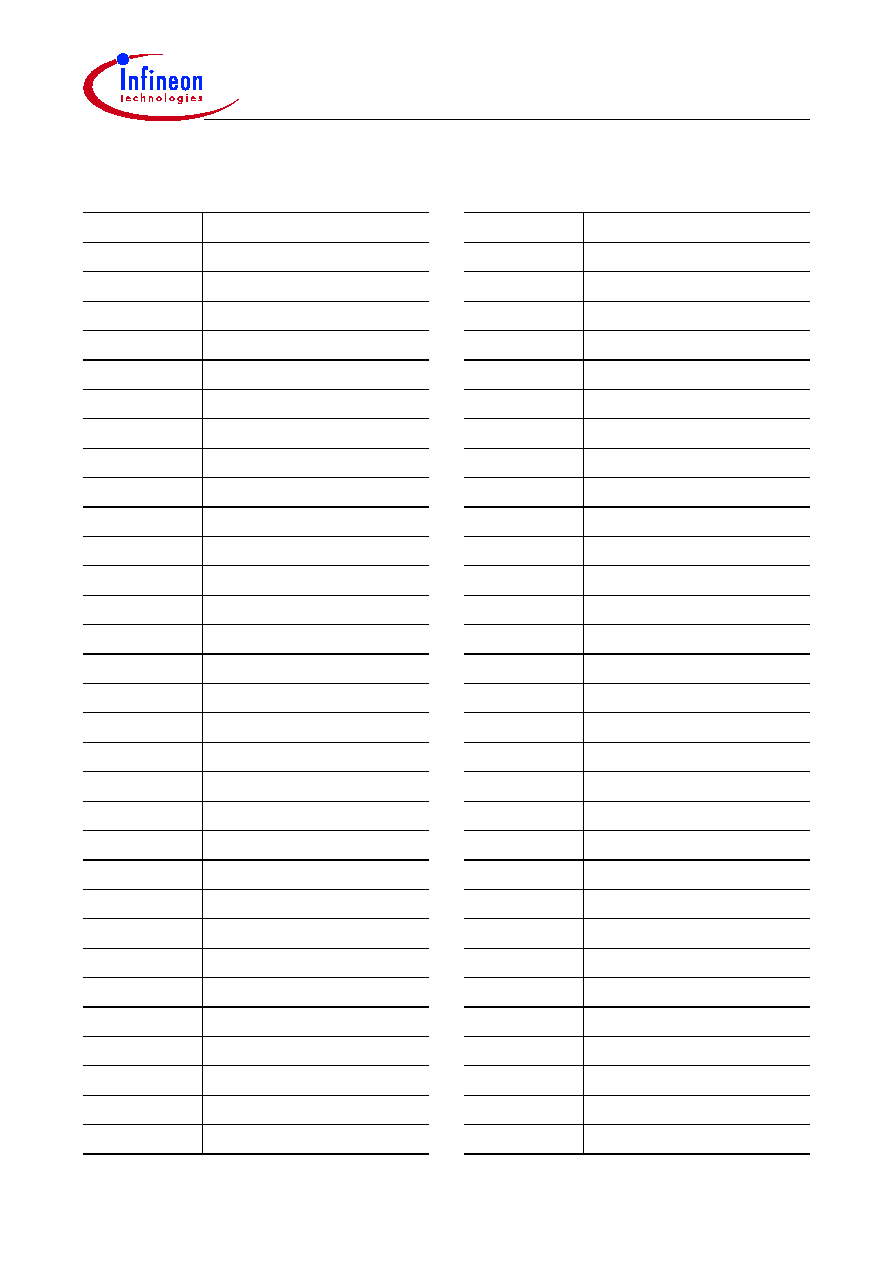

Connector Pin Assignments

Data Sheet

2

2002-03-22

Connector Pin Assignments

Pin No.

Signal Name

Pin No.

Signal Name

1

TxDATAP0

2

SLPTIME

3

TxDATAN0

4

RLPTIME

5

GND

6

GND

7

TxDATAP1

8

PCLKN

9

TxDATAN1

10

PCLKP

11

GND

12

GND

13

TxDATAP2

14

SDSCLKP

15

TxDATAN2

16

SDSCLKN

17

GND

18

GND

19

TxDATAP3

20

RxDATAN3

21

TxDATAN3

22

RxDATAP3

23

GND

24

GND

25

TxCLKN

26

RxDATAN2

27

TxCLKP

28

RxDATAP2

29

GND

30

GND

31

REFCLKP

32

RxDATAN1

33

REFCLKN

34

RxDATAP1

35

GND

36

GND

37

No connect

38

LLEB_L

39

No connect

40

DLEB_L

41

V

CC

42

RxDATAN0

43

No connect

44

RxDATAP0

45

No connect

46

V

CC

47

V

CC

48

V

CC

49

LASER_DISABLE

50

V

CC

51

TxLOCK

52

V

CC

53

Tx_FAULT

54

V

CC

55

Rx_LOS

56

RESET_L

57

Rx_LOSYNC

58

Rx_MON

59

Tx_BIASALM

60

SPARE

BLADE

GND

V23816-N1018-C312-A

V23816-N1018-L312-A

Functional Signal Description

Data Sheet

3

2002-03-22

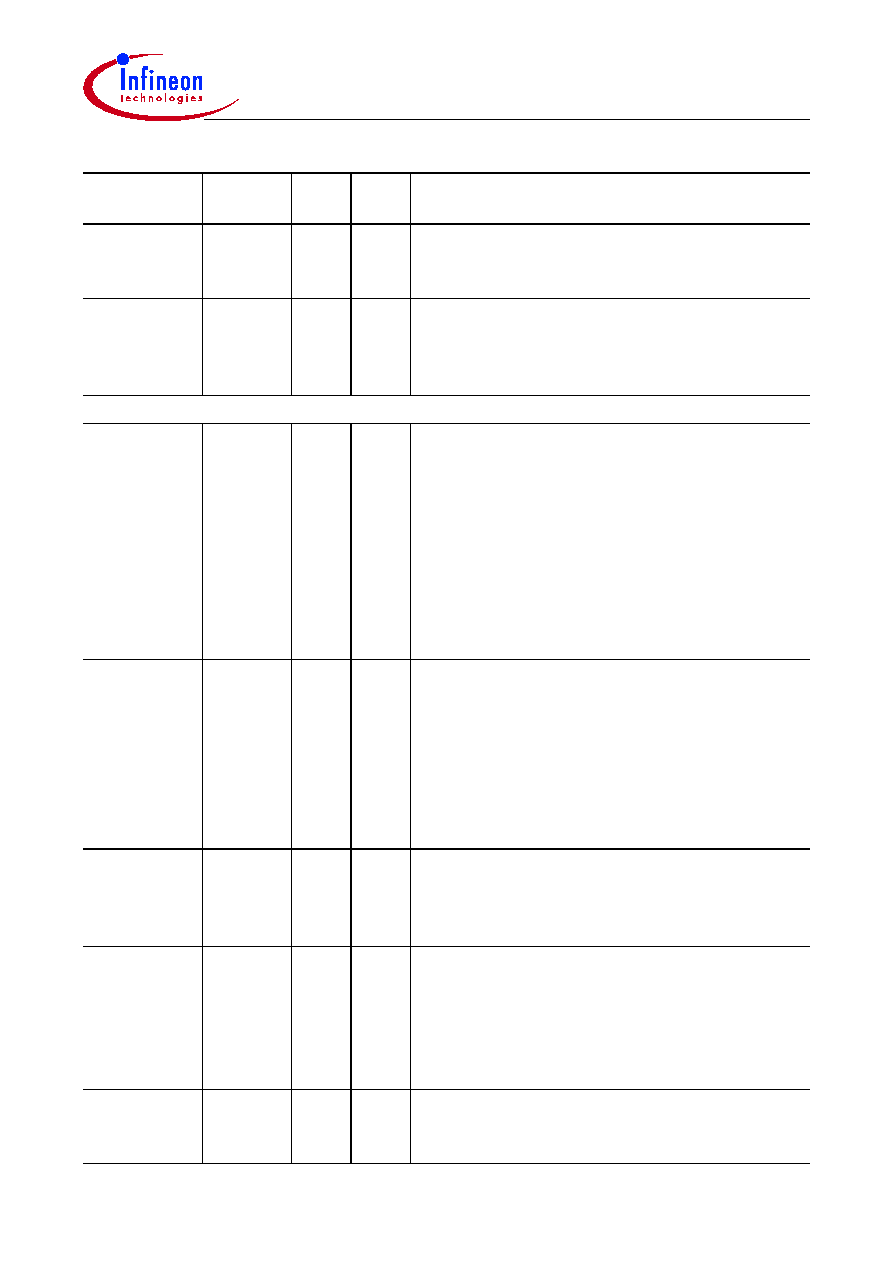

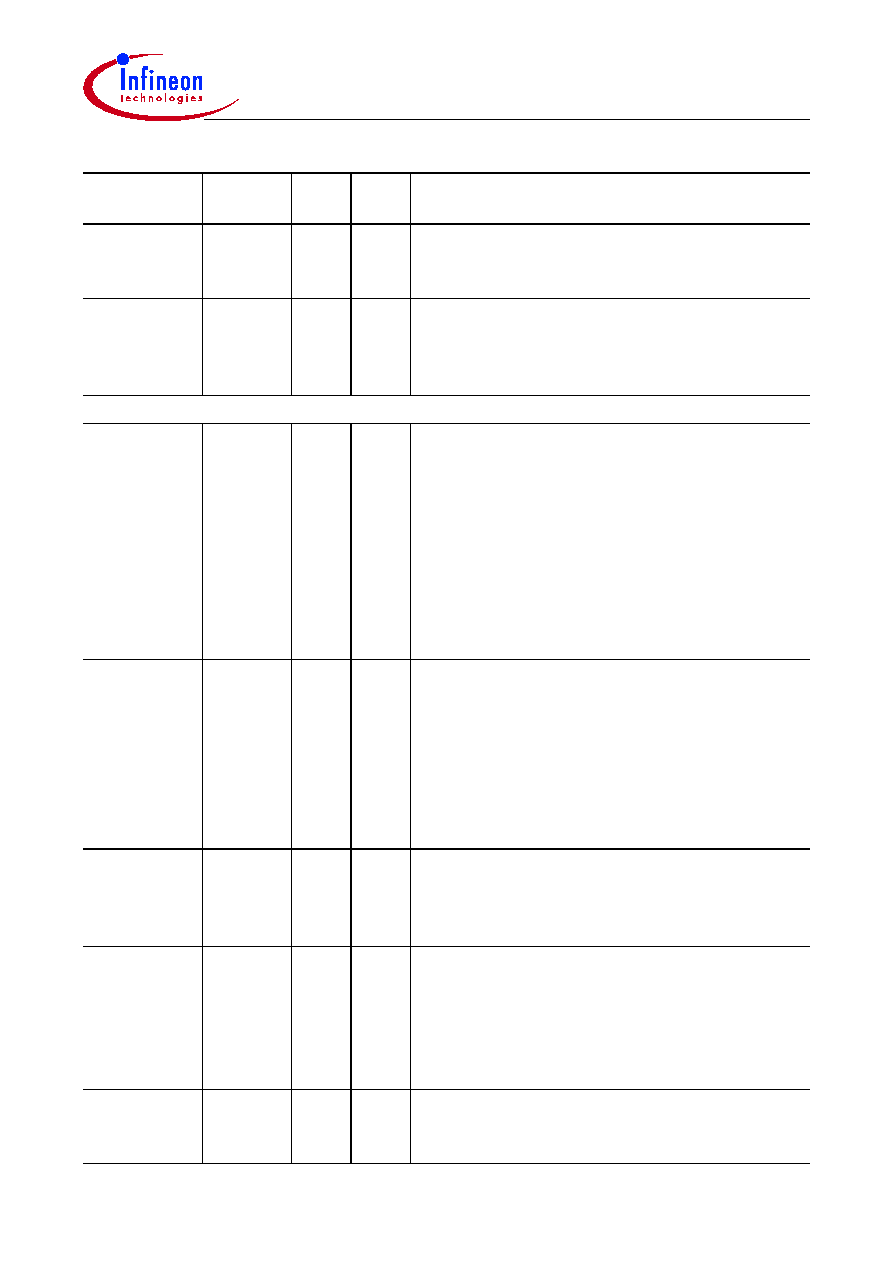

Functional Signal Description

Signal Name Level

I/O

Pin

No.

Description

Transmit Functions

TxDATAP0

TxDATAN0

TxDATAP1

TxDATAN1

TxDATAP2

TxDATAN2

TxDATAP3

TxDATAN3

LVDS

I

1

3

7

9

13

15

19

21

Transmit Parallel input data at 622.08 Mb/s,

aligned to the TxCLKP/N parallel input clock.

TxDATAP/N[3] is the most significant bit

(MSB), and is the first bit transmitted in the

outgoing OC-48 serial data stream.

TxDATAP/N[3:0] is sampled on the rising edge

of TxCLKP. DC coupled and internally

terminated.

TxCLKP

TxCLKN

LVDS

I

27

25

Transmit Parallel input clock, 622.08 MHz, to

which TxDATAP/N[3:0] is aligned. TxCLK

transfers the data on the TxDATAP/N inputs

into a 4-bit wide latch in the Transceiver IC.

Data is sampled on the rising edge of TxCLKP.

DC coupled and internally terminated.

REFCLKP

REFCLKN

LVPECL I

31

33

155.52 MHz Transmit Reference Clock input to

the bit clock frequency synthesizer of the

Transceiver IC. DC coupled and internally

biased.

No connect

37

39

Do not connect.

LASER_

DISABLE

LVTTL

I

49

Laser Disable. Control input to disable

Transmit laser. High = Disable laser. Pulled

low through 1 k

resistor.

TxLOCK

LVTTL

O

51

Loss Of Lock alarm for Tx PLL of the

Transceiver IC. High = Locked. Asynchronous

output.

No connect

45,43 Do not connect.

Tx_FAULT

LVTTL

O

53

Transmit Fault alarm output. Indicates that the

laser has been automatically shut off due to a

fault in the Tx laser circuit. High = Tx Fault.

Fault may be cleared by cycling DC power, or

by strobing the RESET_L input.

Tx_BIASALM LVTTL

O

59

Transmit Bias Alarm output. Indicates that the

bias current of the Tx laser is currently outside

normal operating limits. High = Tx Bias outside

limits.

V23816-N1018-C312-A

V23816-N1018-L312-A

Functional Signal Description

Data Sheet

4

2002-03-22

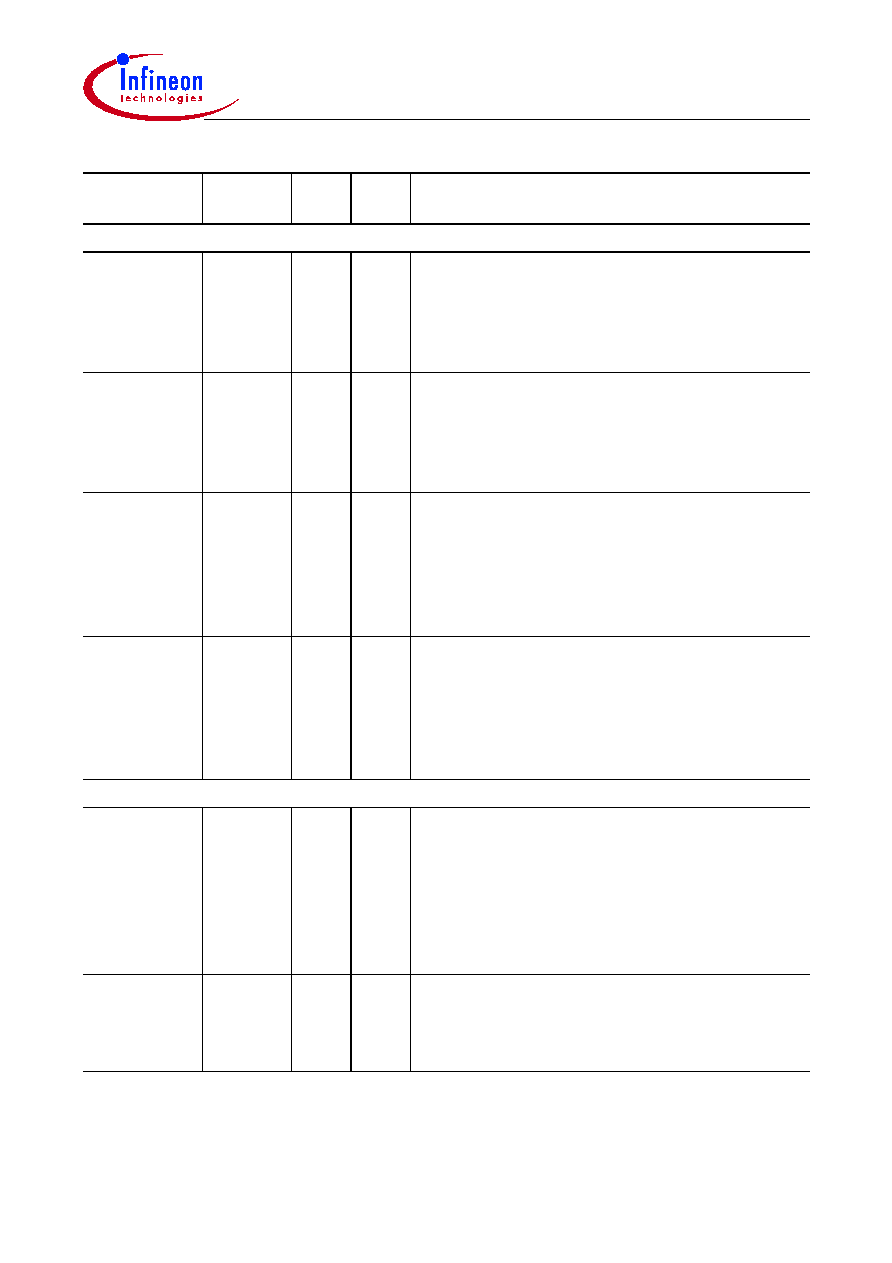

PCLKP

PCLKN

LVDS

O

10

8

622.08 MHz Parallel Clock output. Generated

by dividing the internal high-speed Tx clock

by 4.

RESET_L

LVTTL

I

56

Master Reset input. A Low level resets the Tx

Mux and Laser Driver. RESET_L must be held

low for at least 6 millisec. Pulled high through a

1 k

resistor.

Receive Functions

RxDATAP0

RxDATAN0

RxDATAP1

RxDATAN1

RxDATAP2

RxDATAN2

RxDATAP3

RxDATAN3

LVDS

O

44

42

34

32

28

26

22

20

Parallel Output Data at 622.08 Mb/s from the

Receiver, aligned to the Parallel Output Clock

(RxCLKP/N). RxDATAP/N[3] is the Most

Significant Bit, and is the first bit received in the

incoming OC-48 serial data stream.

RxDATAP/N[3:0] is clocked out on the falling

edge of SDSCLKP. All data outputs are forced

to zero level under Loss Of Signal or Loss Of

Synchronization conditions. DC coupled

outputs. Internally terminated.

SDSCLKN

SDSCLKP

LVDS

O

16

14

Parallel Output Clock from the Receiver at

622.08 MHz. This clock is aligned to the

RxDATAP/N[3:0] parallel output data.

RxDATAP/N[3:0] is clocked out on the falling

edge of SDSCLKP. Clock output is continuous

under Loss Of Signal or Loss Of

Synchronization conditions. DC coupled

output. Internally terminated.

Rx_LOS

LVTTL

O

55

Receive Loss Of Signal alarm output. A High

output level indicates Rx input power is below

the sensitivity level of the receiver (high BER

condition).

Rx_LOSYNC LVTTL

O

57

Receive Loss Of Synchronization alarm

output. A High output level indicates that the

receive Clock Recovery unit has lost

synchronization, due to either very low Rx

input power level, or input data rate outside of

frequency tolerance.

Rx_MON

Analog

O

58

Receive power monitor output. A voltage

output which is directly proportional to the

optical Rx input power.

Signal Name Level

I/O

Pin

No.

Description

V23816-N1018-C312-A

V23816-N1018-L312-A

Functional Signal Description

Data Sheet

5

2002-03-22

Loopback Modes

LLEB_L

LVTTL

I

38

Line Loopback Enable input. A Low level

enables Line Loopback mode. When active,

the Rx inputs to the Transceiver IC will be

routed directly to the Tx outputs. Pulled high

through a 1 k

resistor.

DLEB_L

LVTTL

I

40

Diagnostic Loopback Enable input. A Low level

enables Diagnostic Loopback mode. When

active, the Tx outputs of the Transceiver IC are

routed directly to the Rx inputs. Pulled high

through a 1 k

resistor.

RLPTIME

LVTTL

I

4

Reference Loop Time Enable input. A High

level enables Reference Loop Time. When

active, a divide-by-4 version of the POCLKP/N

output of the Rx is used as the reference clock

input to the Tx. Pulled low through a 1 k

resistor.

SLPTIME

LVTTL

I

2

Serial Loop Time Enable input. A High level

enables Serial Loop Time. When active, the

recovered high-speed clock (RSCLKP/N) from

the Rx section is used in place of the

synthesized transmit clock. Pulled low through

a 1 k

resistor.

DC Power

GROUND

0 V DC

I

5,6,

11,12,

17,18,

23,24,

29,30,

35,36,

Blade

Ground connection for both signal and chassis

ground on the transponder. The blade contact

of the 60 pin interface connector is tied to

ground in the transponder. Therefore, the

blade of the user's mating connector should be

connected to ground, as well.

V

CC

+3.3 V

DC

I

41,47,

46,48,

50,52,

54

DC Power Input. +3.3 V DC, nominal.

Signal Name Level

I/O

Pin

No.

Description