8XC196KB/8XC196KB16

PROCESS INFORMATION

This device is manufactured on P629. 0 and 629.1, a

CHMOS III-E process. Additional process and reli-

ability information is available in the

Intel Æ Quality

System Handbook:

http://developer.intel.com/design/quality/quality.htm

270909≠2

NOTE:

1. EPROMs are available as One Time Programmable

(OTPROM) only.

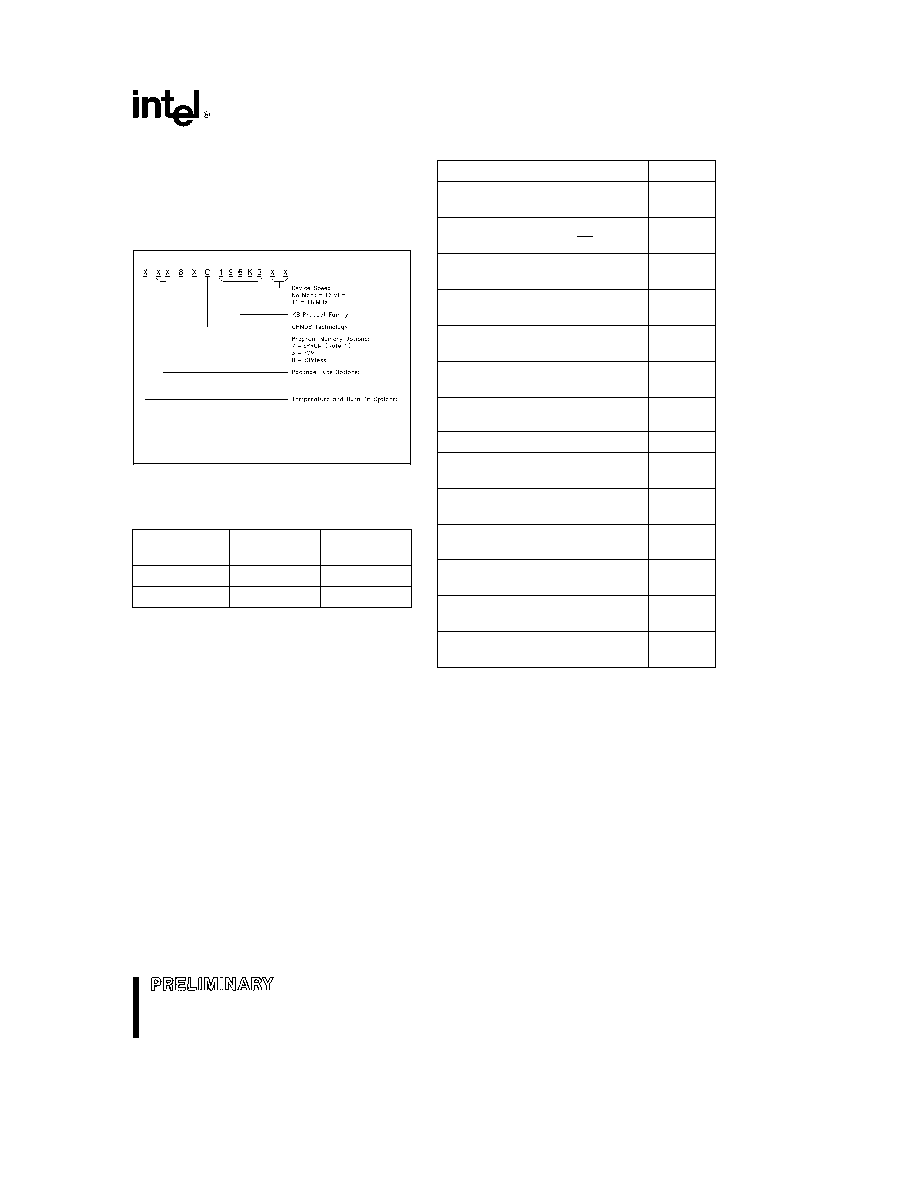

Figure 2. The 8XC196KB Nomenclature

Table 1. Thermal Characteristics

Package

ja

jc

Type

PLCC

35

∞

C/W

13

∞

C/W

QFP

70

∞

C/W

4

∞

C/W

All thermal impedance data is approximate for static air

conditions at 1W of power dissipation. Values will change

depending on operation conditions and application. See

the Intel

Packaging Handbook (order number 240800) for a

description of Intel's thermal impedance test methodology.

Table 2. 8XC196KB Memory Map

Description

Address

External Memory or I/O

04000H

Internal ROM/EPROM or External

Memory (Determined by EA)

2080H

Reserved. Must contain FFH.

(Note 5)

2040H

Upper Interrupt Vectors

203FH

2030H

ROM/EPROM Security Key

202FH

2020H

Reserved. Must contain FFH.

(Note 5)

201AH

Reserved. Must Contain 20H.

(Note 5)

CCB

2018H

Reserved. Must contain FFH.

(Note 5)

2014H

Lower Interrupt Vectors

2013H

2000H

Port 3 and Port 4

1FFFH

1FFEH

External Memory

1FFDH

0100H

232 Bytes Register RAM (Note 1)

00FFH

0018H

CPU SFR's (Notes 1, 3)

0017H

0000H

NOTES:

1. Code executed in locations 0000H to 00FFH will be

forced external.

2. Reserved memory locations must contain 0FFH unless

noted.

3. Reserved SFR bit locations must contain 0.

4. Refer to 8XC196KB quick reference for SFR descrip-

tions.

5. WARNING: Reserved memory locations must not be

written or read. The contents and/or function of these lo-

cations may change with future revisions of the device.

Therefore, a program that relies on one or more of these

locations may not function properly.

3

207FH

201FH

2019H

2017H

0FFFFH

3FFFH

8XC196KB/8XC196KB16

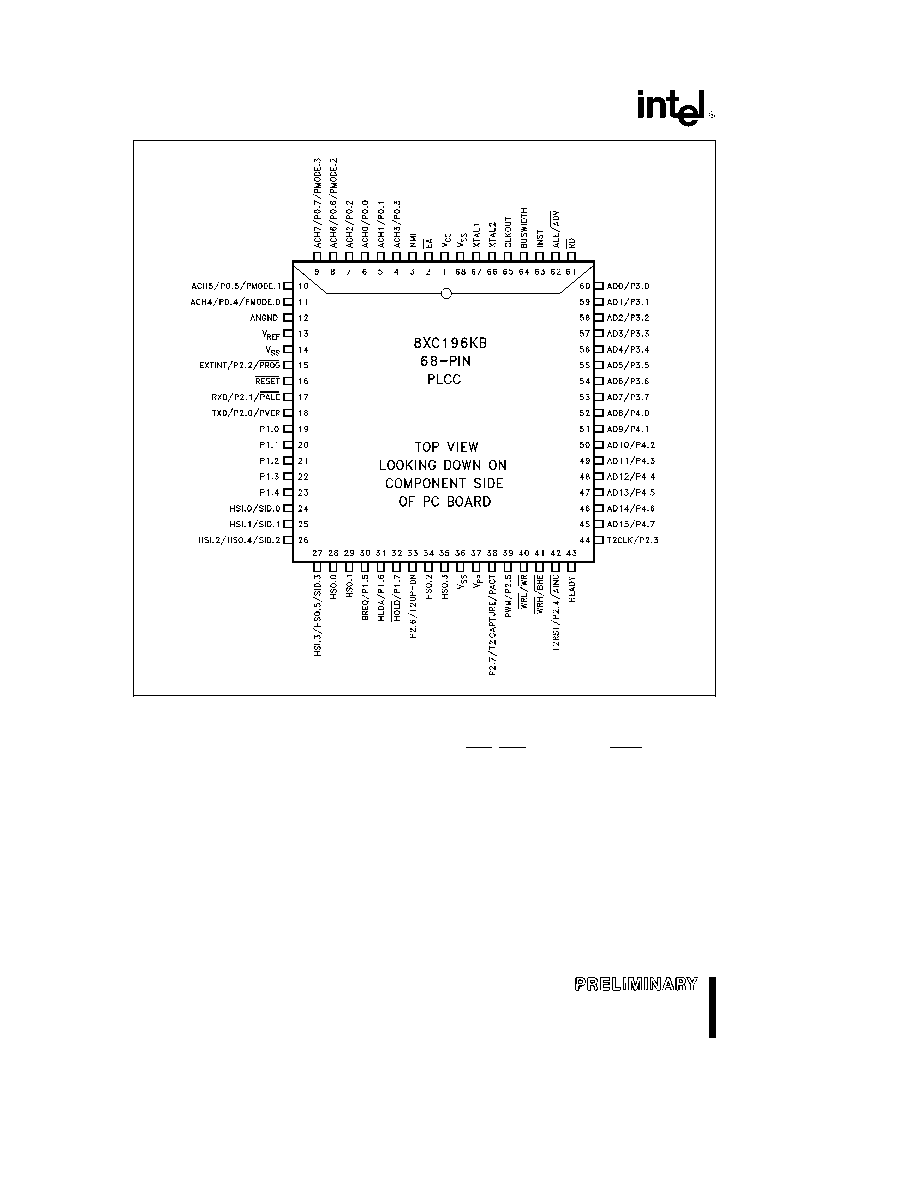

270909≠3

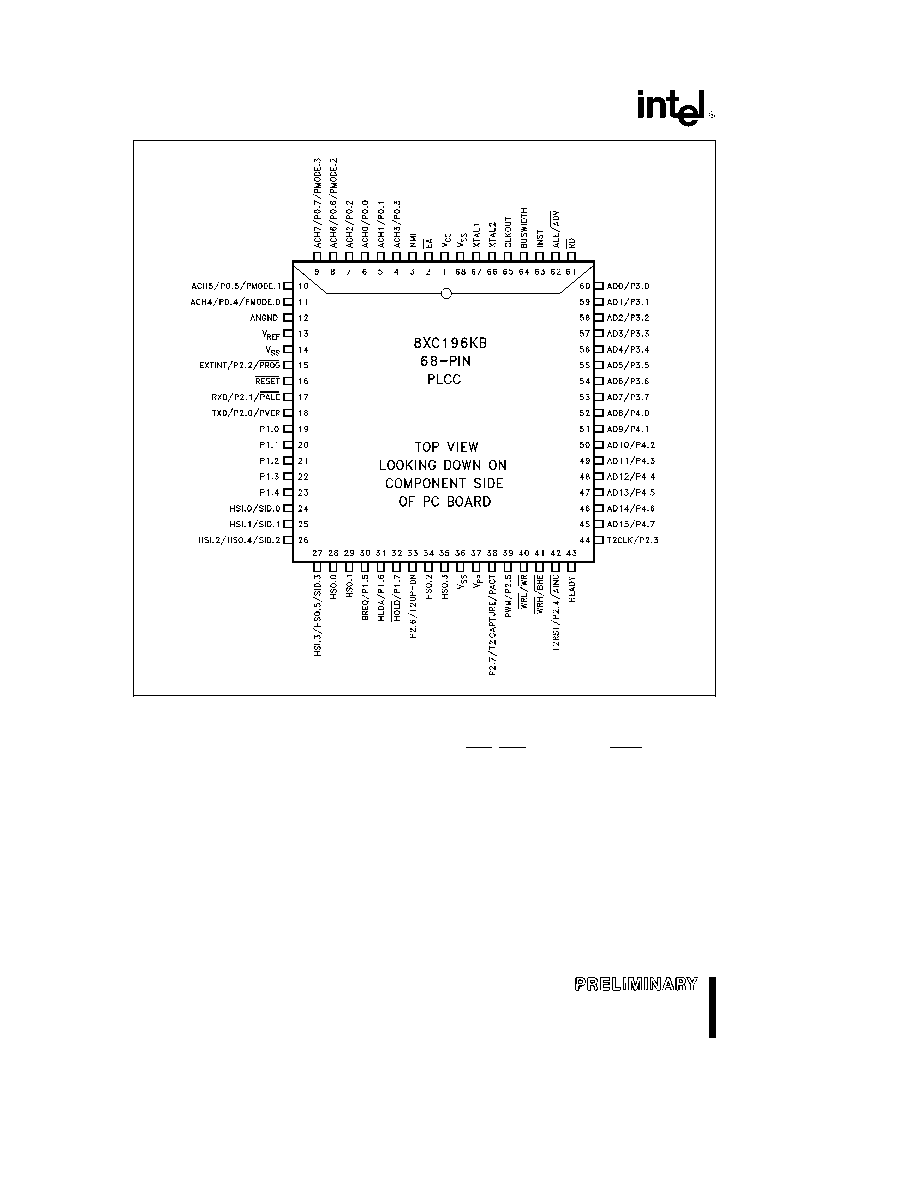

Figure 3. 68-Pin Package (PLCC Top View)

NOTE:

The above pin out diagram applies to the OTP (87C196KB) device. The OTP device uses all of the programming pins shown

above. The ROM (83C196KB) device only uses programming pins: AINC, PALE, PMODE.n, and PROG. The ROMless

(80C196KB) doesn't use any of the programming pins.

4

8XC196KB/8XC196KB16

270909≠4

NOTE

:

N.C. means No Connect (do not connect these pins).

Figure 4. 80-Pin QFP Package

NOTE

:

The above pin out diagram applies to the OTP (87C196KB) device. The OTP device uses all of the programming pins shown

above. The ROM (83C196KB) device only uses programming pins: AINC, PALE, PMODE.n, and PROG. The ROMless

(80C196KB) doesn't use any of the programming pins.

5