Other brands and names are the property of their respective owners

Information in this document is provided in connection with Intel products Intel assumes no liability whatsoever including infringement of any patent or

copyright for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products Intel retains the right to make

changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata

October 1995

COPYRIGHT

INTEL CORPORATION 1996

Order Number 290475-004

82078 64 PIN

CHMOS SINGLE-CHIP FLOPPY DISK CONTROLLER

Y

Small Footprint and Low Height

Packages

Y

Supports Standard 5 0V as well as Low

Voltage 3 3V Platforms

Selectable 3 3V and 5 0V

Configuration

5 0V Tolerant Drive Interface

Y

Enhanced Power Management

Application Software Transparency

Programmable Powerdown

Command

Save and Restore Commands for

Zero-Volt Powerdown

Auto Powerdown and Wakeup

Modes

Two External Power Management

Pins

Consumes no Power when in

Powerdown

Y

Integrated Analog Data Separator

250 Kbps

300 Kbps

500 Kbps

1 Mbps

2 Mbps

Y

Programmable Internal Oscillator

Y

Floppy Drive Support Features

Drive Specification Command

Media ID Capability Provides Media

Recognition

Drive ID Capability Allows the User

to Recognize the Type of Drive

Selectable Boot Drive

Standard IBM and ISO Format

Features

Format with Write Command for

High Performance in Mass Floppy

Duplication

Y

Integrated Tape Drive Support

Standard 1 Mbps 500 Kbps

250 Kbps Tape Drives

New 2 Mbps Tape Drive Mode

Y

Perpendicular Recording Support for

4 MB Drives

Y

Integrated Host Disk Interface Drivers

Y

Fully Decoded Drive Select and Motor

Signals

Y

Programmable Write Precompensation

Delays

Y

Addresses 256 Tracks Directly

Supports Unlimited Tracks

Y

16 Byte FIFO

Y

Single-Chip Floppy Disk Controller

Solution for Portables and Desktops

100% PC AT Compatible

100% PS 2 Compatible

100% PS 2 Model 30 Compatible

Fully Compatible with Intel386

TM

SL

Microprocessor SuperSet

Y

Integrated Drive and Data Bus Buffers

Y

Available in 64 Pin QFP Package

The 82078 a 24 MHz crystal a resistor package and a device chip select implements a complete solution All

programmable options default to 82078 compatible values The dual PLL data separator has better perform-

ance than most board level discrete PLL implementations The FIFO allows better system performance in

multi-master (e g Microchannel EISA)

The 82078 maintains complete software compatibility with the 82077SL 82077AA 8272A floppy disk control-

lers It contains programmable power management features while integrating all of the logic required for floppy

disk control The power management features are transparent to any application software There are two

versions of 82078 floppy disk controllers the 82078SL and 82078-1

The 82078 is fabricated with Intel's advanced CHMOS III technology and is also available in a 44-lead QFP

package

Other brands and names are the property of their respective owner

82078 64 Pin CHMOS Single-Chip Floppy Disk Controller

CONTENTS

PAGE

1 0 INTRODUCTION

8

2 0 MICROPROCESSOR INTERFACE

9

2 1 Status Data and Control

Registers

9

2 1 1 Status Register A (SRA PS 2

Mode)

9

2 1 2 Status Register A (SRA

Model 30 Mode)

10

2 1 3 Status Register B (SRB

Enhanced AT EISA)

10

2 1 4 Status Register B (SRB PS 2

Mode)

11

2 1 5 Status Register B (SRB

Model 30 Mode)

11

2 1 6 Digital Output Register

(DOR)

11

2 1 7 Tape Drive Register (TDR

AT EISA PS 2 Model 30)

12

2 1 8 Enhanced Tape Drive

Register (TDR AT PS 2 Model

30 EREG EN

e

1)

12

2 1 9 Datarate Select Register

(DSR)

13

2 1 10 Main Status Register

(MSR)

15

2 1 11 FIFO (DATA)

15

2 1 12 Digital Input Register (DIR

PC-AT MODE)

16

2 1 13 Digital Input Register (DIR

PS 2 MODE)

16

2 1 14 Digital Input Register (DIR

MODEL 30 MODE)

16

2 1 15 Configuration Control

Register (CCR PS 2 MODES)

17

2 1 16 Configuration Control

Register (CCR MODEL 30

MODE)

17

2 2 Reset

18

2 2 1 Reset Pin (``HARDWARE'')

Reset

18

2 2 2 DOR Reset vs DSR Reset

(``SOFTWARE'' RESET)

18

2 3 DMA Transfers

18

CONTENTS

PAGE

3 0 DRIVE INTERFACE

18

3 1 Cable Interface

18

3 2 Data Separator

19

3 2 1 Jitter Tolerance

20

3 2 2 Locktime (tLOCK)

20

3 2 3 Capture Range

20

3 3 Write Precompensation

20

4 0 POWER MANAGEMENT

FEATURES

21

4 1 Power Management Scheme

21

4 2 3 3V Support for Portable

Platforms

21

4 3 Oscillator Power Management

21

4 4 Part Power Management

22

4 4 1 Direct Powerdown

22

4 4 2 Auto Powerdown

22

4 4 3 Wake Up Modes

22

4 4 3 1 Wake Up from DSR

Powerdown

22

4 4 3 2 Wake Up from Auto

Powerdown

23

4 5 Register Behavior

23

4 6 Pin Behavior

24

4 6 1 System Interface Pins

24

4 6 2 FDD Interface Pins

25

5 0 CONTROLLER PHASES

26

5 1 Command Phase

26

5 2 Execution Phase

26

5 2 1 Non-DMA Mode Transfers

from the FIFO to the Host

26

5 2 2 Non-DMA Mode Transfers

from the Host to the FIFO

26

5 2 3 DMA Mode Transfers from

the FIFO to the Host

26

5 2 4 DMA Mode Transfers from

the Host to the FIFO

27

5 2 5 Data Transfer Termination

27

5 3 Result Phase

27

2

CONTENTS

PAGE

6 0 COMMAND SET DESCRIPTIONS

27

6 1 Data Transfer Commands

40

6 1 1 Read Data

40

6 1 2 Read Deleted Data

41

6 1 3 Read Track

41

6 1 4 Write Data

42

6 1 5 Write Deleted Data

42

6 1 6 Verify

42

6 1 7 Format Track

44

6 1 7 1 Format Fields

44

6 2 Control Commands

45

6 2 1 Read ID

45

6 2 2 Recalibrate

45

6 2 3 Drive Specification

Command

45

6 2 4 Seek

47

6 2 5 Scan Commands

47

6 2 6 Sense Interrupt Status

48

6 2 7 Sense Drive Status

48

6 2 8 Specify

48

6 2 9 Configure

49

6 2 10 Version

49

6 2 11 Relative Seek

49

6 2 12 DUMPREG

50

6 2 13 Perpendicular Mode

Command

50

6 2 13 1 About Perpendicular

Recording Mode

50

6 2 13 2 The Perpendicular

Mode Command

50

6 2 14 Powerdown Mode

Command

51

6 2 15 Part ID Command

51

6 2 16 Option Command

51

6 2 17 Save Command

52

6 2 18 Restore Command

52

6 2 19 Format and Write

Command

52

6 2 20 Lock

52

CONTENTS

PAGE

7 0 STATUS REGISTER ENCODING

53

7 1 Status Register 0

53

7 2 Status Register 1

53

7 3 Status Register 2

54

7 4 Status Register 3

54

8 0 COMPATIBILITY

55

8 1 PS 2 vs AT vs Model 30 Mode

55

8 2 Compatibility with the FIFO

55

8 3 Drive Polling

55

9 0 PROGRAMMING GUIDELINES

55

9 1 Command and Result Phase

Handshaking

55

9 2 Initialization

56

9 3 Recalibrates and Seeks

58

9 4 Read Write Data Operations

58

9 5 Formatting

60

9 6 Save and Restore

61

9 7 Verifies

62

9 8 Powerdown State and Recovery

62

9 8 1 Oscillator Power

Management

62

9 8 2 Part Power Management

62

9 8 2 1 Powerdown Modes

62

9 8 2 2 Wake Up Modes

63

10 0 DESIGN APPLICATIONS

63

10 1 Operating the 82078SL in a 3 3V

Design

63

10 2 Selectable Boot Drive

65

10 3 How to Disable the Native Floppy

Controller on the Motherboard

66

10 4 Replacing the 82077SL with an

82078 in a 5 0V Design

66

11 0 D C SPECIFICATIONS

69

11 1 Absolute Maximum Ratings

69

11 2 D C Characteristics

69

11 3 Oscillator

71

12 0 A C SPECIFICATIONS

72

12 1 Package Outline for the 64 QFP

Part

78

13 0 REVISION HISTORY

78

3

82078 64 PIN

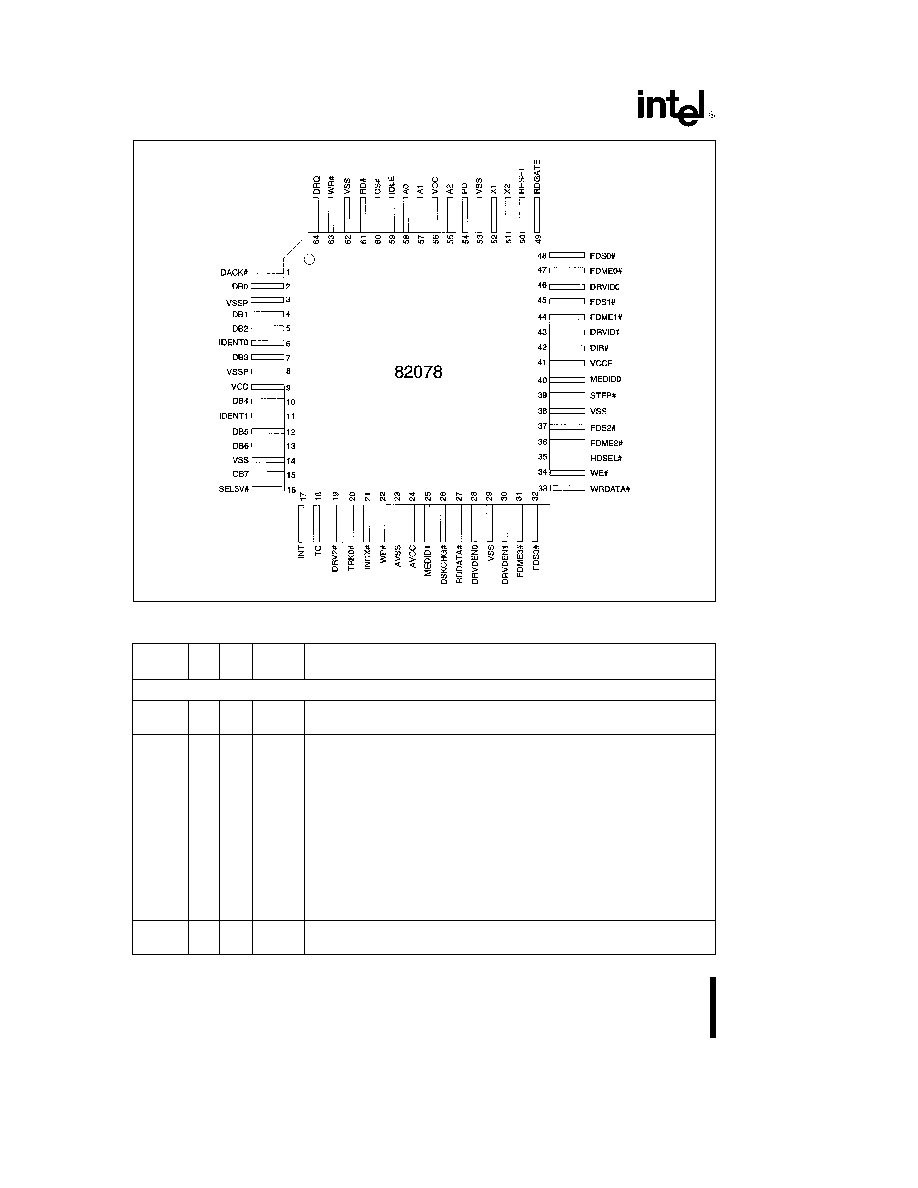

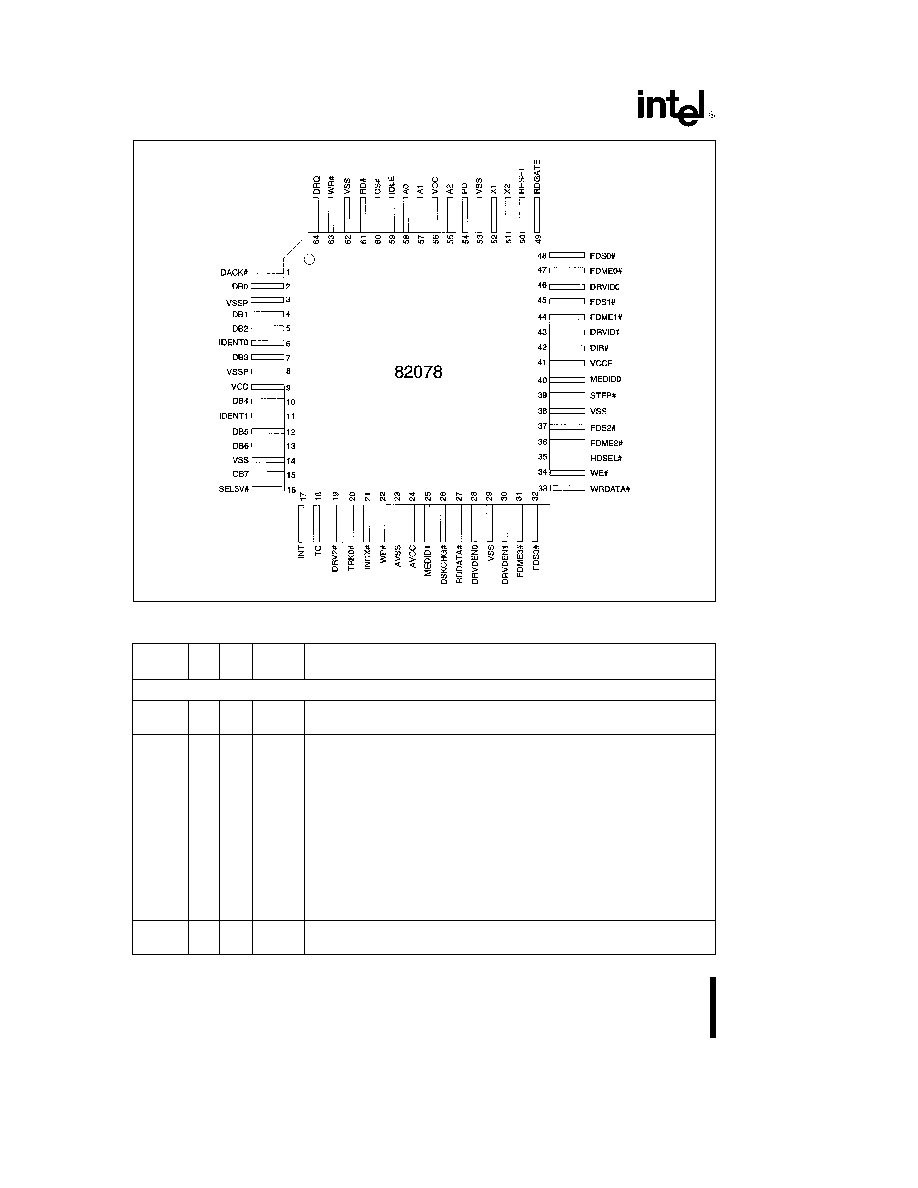

290475 � 1

Figure 1-0 82078 Pinout

Table 1-0 82078 (64 Pin) Description

Symbol

Pin

I O

H W

Description

Reset

HOST INTERFACE

RESET

50

I

N A

RESET

A high level places the 82078 in a known idle state All registers

are cleared except those set by the Specify command

A0

58

I

N A

ADDRESS

Selects one of the host interface registers

A1

57

A2

A1

A0

Access

Register

A2

55

0

0

0

R

Status Register A

SRA

0

0

1

R W

Status Register B

SRB

0

1

0

R W

Digital Output Register

DOR

0

1

1

R W

Tape Drive Register

TDR

1

0

0

R

Main Status Register

MSR

1

0

0

W

Data Rate Select Register

DSR

1

0

1

R W

Data Register (FIFO)

FIFO

1

1

0

Reserved

1

1

1

R

Digital Input Register

DIR

1

1

1

W

Configuration Control Register

CCR

CS

60

I

N A

CHIP SELECT

Decodes the base address range and qualifies RD

and

WR

4

82078 64 PIN

Table 1-0 82078 (64 Pin) Description

(Continued)

Symbol

Pin

I O

H W

Description

Reset

HOST INTERFACE

(Continued)

RD

61

I

N A

READ

Read control signal for data transfers from the floppy drive to the

system

WR

63

I

N A

WRITE

Write control signal for data transfers to the floppy drive from the

system

DRQ

64

O

DMA REQUEST

Requests service from a DMA controller Normally active

high but will go to high impedance in AT and Model 30 modes when the

appropriate bit is set in the DOR

DACK

1

I

N A

DMA ACKNOWLEDGE

Control input that qualifies the RD

WR

inputs

in DMA cycles Normally active low but is disabled in AT and Model 30

modes when the appropriate bit is set in the DOR

DB0

2

I O

DATA BUS

12 mA data bus

DB1

4

DB2

5

DB3

7

DB4

10

DB5

12

DB6

13

DB7

15

IDENT0

6

I

N A

IDENTITY

These inputs decode between the several operation modes

available to the user These pins have no effect on the DRVDEN pins

IDENT1

11

IDENT0

IDENT1

INTERFACE

1

1

AT mode

1

0

ILLEGAL

0

1

PS 2 mode

0

0

Model 30

AT MODE

Major options are enables DMA gate logic TC is active high

Status Register B is available based on a bit the powerdown command

PS 2 MODE

Major options are no DMA gate logic TC is active low Status

Registers A

B are available

MODEL 30 MODE

Major options are enable DMA gate logic TC is active

high Status Registers A

B are available

INT

17

O

INTERRUPT

Signals a data transfer in non-DMA mode and when status is

valid Normally active high but goes to high impedance when the

appropriate bit is set in the DOR

TC

18

I

N A

TERMINAL COUNT

Control line from a DMA controller that terminates the

current disk transfer TC is effective only when qualified by DACK

This

input is active high in the AT and Model 30 modes when the appropriate bit

is set in the DOR

X1

52

N A

EXTERNAL CLOCK OR CRYSTAL

Connection for a 24 MHz fundamental

mode parallel resonant crystal X1 can also be driven by an external clock

X2

51

(external oscillator) which can be either at 48 MHz or 24 MHz If external

oscillator is used then the PDOSC bit can be set to turn off the internal

oscillator Also if a 48 MHz exernal oscillator is used then the CLK48 bit

must be set in the enhanced CONFIGURE command

5