Other brands and names are the property of their respective owners

Information in this document is provided in connection with Intel products Intel assumes no liability whatsoever including infringement of any patent or

copyright for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products Intel retains the right to make

changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata

March 1996

COPYRIGHT

INTEL CORPORATION 1996

Order Number 290476-004

82374EB 82374SB EISA

SYSTEM COMPONENT (ESC)

Y

Integrates EISA Compatible Bus

Controller

Translates Cycles Between EISA and

ISA Bus

Supports EISA Burst and Standard

Cycles

Supports ISA Zero Wait-State Cycles

Supports Byte Assembly

Disassembly for 8- 16- and 32-Bit

Transfers

Supports EISA Bus Frequency of up

to 8 33 MHz

Y

Supports Eight EISA Slots

Directly Drives Address Data and

Control Signals for Eight Slots

Decodes Address for Eight Slot

Specific AENs

Y

Provides Enhanced DMA Controller

Provides Scatter-Gather Function

Supports Type A Type B Type C

(Burst) and Compatible DMA

Transfer

Provides Seven Independently

Programmable Channels

Integrates Two 82C37A Compatible

DMA Controllers

Y

Integrates the Functionality of two

82C59 Interrupt Controllers and two

82C54 Timers

Provides 14 Programmable Channels

for Edge or Level Interrupts

Provides 4 PCI Interrupts Routible to

any of 11 Interrupt Channels

Supports Timer Function for Refresh

Request System Timer Speaker

Tone Fail Safe Timer and CPU

Speed Control

Y

Advanced Programmable Interrupt

Controller (APIC)

Multiprocessor Interrupt

Management

Separate Bus For Interrupt Messages

Y

5V CMOS Technology

Y

Provides High Performance Arbitration

Supports Eight EISA Masters and

PCEB

Supports ISA Masters DMA

Channels and Refresh

Provides Programmable Arbitration

Scheme for Fixed Rotating or

Combination Priority

Y

Integrates Support Logic for X-Bus

Peripherals

Generates Chip Selects Encoded

Chip Selects for Floppy and

Keyboard Controller IDE Parallel

Serial Ports

and General Purpose

Peripherals

Provides Interface for Real Time

Clock

Generates Control Signals for X-Bus

Data Transceiver

Integrates Port 92 Mouse Interrupt

and Coprocessor Error Reporting

Y

Generates Non-Maskable Interrupts

(NMI)

PCI System Errors

PCI Parity Errors

EISA Bus Parity Errors

Fail Safe Timer

Bus Timeout

Via Software Control

Y

Provides BIOS Interface

Supports 512K Bytes of Flash or

EPROM BIOS on the X-Bus

Allows BIOS on PCI

Supports Integrated VGA BIOS

Y

82374SB System Power Management

(Intel SMM Support)

Fast On Off Support via SMI

GenerationHardware Events

Software Events EXTSMI

Fast Off

Timer System Events

Programmable CPU Clock Control

Enables Energy Efficient Desktop

Systems

Y

Only Available as Part of a Supported

Kit

Y

208-Pin QFP Package

82374EB 82374SB

This document describes both the 82374EB and 82374SB components Unshaded areas describe the

82374EB Shaded areas like this one describe the 82374SB operations that differ from the 82374EB

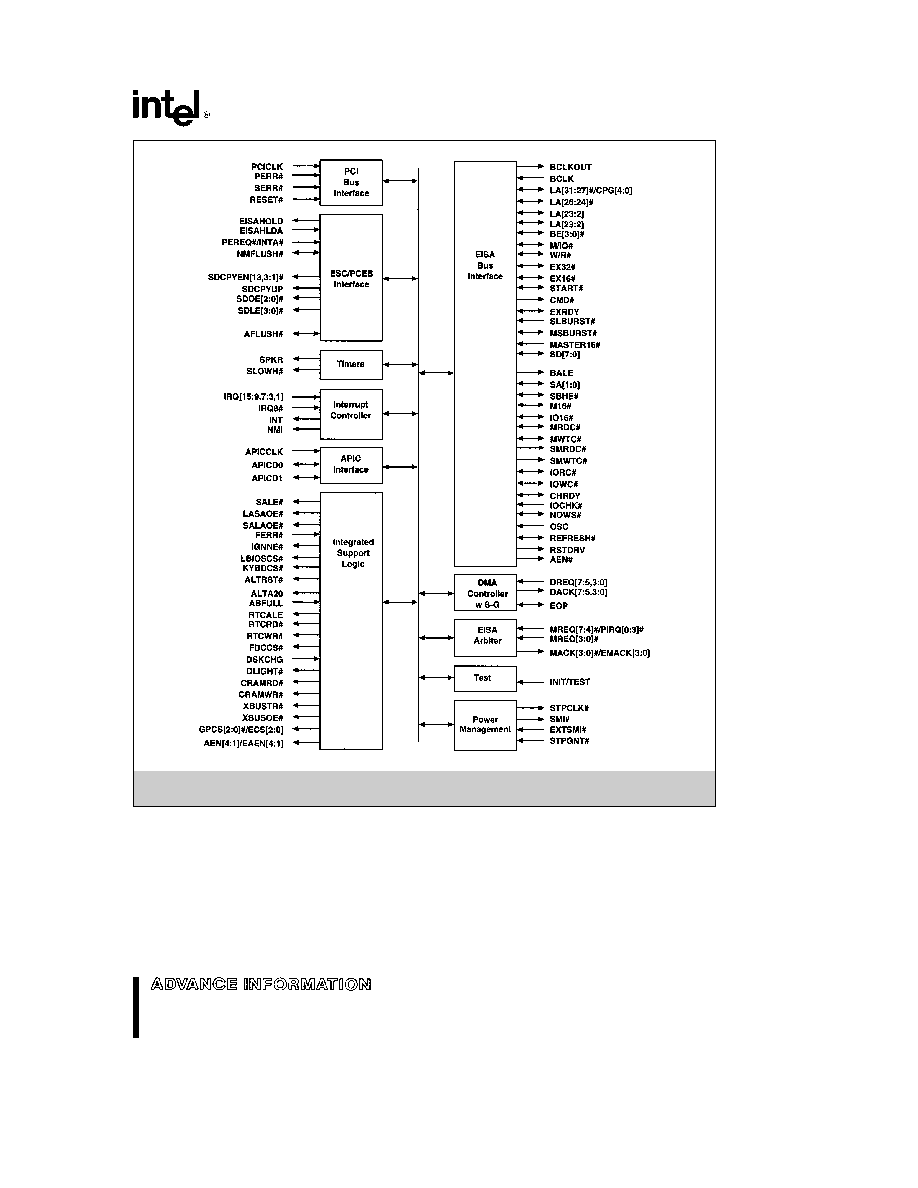

The 82374EB SB EISA System Component (ESC) provides all the EISA system compatible functions The

ESC with the PCEB provide all the functions to implement an EISA-to-PCI bridge and EISA I O subsystem

The ESC integrates the common I O functions found in today's EISA-based PC systems The ESC incorp-

orates the logic for an EISA (master and slave) interface EISA bus controller enhanced seven channel DMA

controller with scatter-gather support EISA arbitration 14 channel interrupt controller Advanced Programma-

ble Interrupt Controller (APIC) five programmable timer counters and non-maskable-interrupt (NMI) control

logic The ESC also integrates support logic to decode peripheral devices such as the Flash BIOS real time

clock keyboard mouse controller floppy controller two serial ports one parallel port and IDE hard disk drive

The 82374SB also contains support for SMM power management

2

82374EB 82374SB EISA

SYSTEM COMPONENT (ESC)

CONTENTS

PAGE

1 0 ARCHITECTURAL OVERVIEW

11

1 1 PCEB Overview

14

1 2 ESC Overview

16

2 0 SIGNAL DESCRIPTION

17

2 1 PCI Local Bus Interface Signals

18

2 2 EISA Bus Interface Signals

18

2 3 ISA Bus Signals

21

2 4 DMA Signal Description

24

2 5 EISA Arbitration Signals

25

2 6 Timer Unit Signal

26

2 7 Interrupt Controller Signals

27

2 8 APIC Bus Signals

27

2 9 System Power Management Signals (82374SB Only)

27

2 10 ESC PCEB Interface Signals

28

2 10 1 ARBITRATION AND INTERRUPT ACKNOWLEDGE CONTROL

28

2 10 2 PCEB BUFFER COHERENCY CONTROL

29

2 11 Integrated Logic Signals

30

2 11 1 EISA ADDRESS BUFFER CONTROL

30

2 11 2 COPROCESSOR INTERFACE

30

2 11 3 BIOS INTERFACE

30

2 11 4 KEYBOARD CONTROLLER INTERFACE

31

2 11 5 REAL TIME CLOCK INTERFACE

31

2 11 6 FLOPPY DISK CONTROLLER INTERFACE

32

2 11 7 CONFIGURATION RAM INTERFACE

33

2 11 8 X-BUS CONTROL AND GENERAL PURPOSE DECODE

33

2 12 Test Signal

35

3 0 REGISTER DESCRIPTION

35

3 1 Configuration Registers

35

3 1 1 ESCID

ESC ID REGISTER

36

3 1 2 RID

REVISION ID REGISTER

36

3 1 3 MS

MODE SELECT REGISTER

36

3 1 4 BIOSCSA

BIOS CHIP SELECT A REGISTER

38

3 1 5 BIOSCSB

BIOS CHIP SELECT B REGISTER

39

4

CONTENTS

PAGE

3 1 6 CLKDIV

EISA CLOCK DIVISOR REGISTER

40

3 1 7 PCSA

PERIPHERAL CHIP SELECT A REGISTER

41

3 1 8 PCSB

PERIPHERAL CHIP SELECT B REGISTER

42

3 1 9 EISAID 4 1

EISA ID REGISTERS

43

3 1 10 SGRBA

SCATTER GATHER RELOCATE BASE ADDRESS REGISTER

43

3 1 11 APICBASE

APIC BASE ADDRESS RELOCATION

44

3 1 12 PIRQ 0 3

PIRQ ROUTE CONTROL REGISTERS

44

3 1 13 GPCSLA 2 0

GENERAL PURPOSE CHIP SELECT LOW ADDRESS

REGISTER

45

3 1 14 GPCSHA 2 0

GENERAL PURPOSE CHIP SELECT HIGH ADDRESS

REGISTER

45

3 1 15 GPCSM 2 0

GENERAL PURPOSE CHIP SELECT MASK REGISTER

46

3 1 16 GPXBC

GENERAL PURPOSE PERIPHERAL X-BUS CONTROL REGISTER

46

3 1 17 PAC

PCI APIC CONTROL REGISTER

47

3 1 18 TESTC

TEST CONTROL REGISTER

47

3 1 19 SMICNTL

SMI CONTROL REGISTER

47

3 1 20 SMIEN

SMI ENABLE REGISTER

48

3 1 21 SEE

SYSTEM EVENT ENABLE REGISTER

49

3 1 22 FTMR

FAST OFF TIMER REGISTER

50

3 1 23 SMIREQ

SMI REQUEST REGISTER

50

3 1 24 CTLTMR

CLOCK SCALE STPCLK

LOW TIMER

52

3 1 25 CTLTMRH

CLOCK SCALE STPCLK

HIGH TIMER

52

3 2 DMA Register Description

52

3 2 1 DCOM

COMMAND REGISTER

52

3 2 2 DCM

DMA CHANNEL MODE REGISTER

54

3 2 3 DCEM

DMA CHANNEL EXTENDED MODE REGISTER

55

3 2 4 DR

DMA REQUEST REGISTER

58

3 2 5 MASK REGISTER

WRITE SINGLE MASK BIT

58

3 2 6 WAMB

WRITE ALL MASK BITS REGISTER

59

3 2 7 DS

DMA STATUS REGISTER

60

3 2 8 DB CA

DMA BASE AND CURRENT ADDRESS REGISTER (8237

COMPATIBLE SEGMENT)

61

3 2 9 DB CBW

DMA BASE AND CURRENT BYTE WORD COUNT REGISTER

(8237 COMPATIBLE SEGMENT)

62

3 2 10 DMA BASE AND CURRENT HIGH BYTE WORD COUNT REGISTER DMA

BASE HIGH BYTE WORD COUNT REGISTER

63

3 2 11 DMA MEMORY LOW PAGE REGISTER DMA MEMORY BASE LOW PAGE

REGISTER

64

3 2 12 DMAP

DMA PAGE REGISTER

64

5