| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: 82433NX | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

December 1995

Order Number 290478-004

82433LX 82433NX

LOCAL BUS ACCELERATOR (LBX)

Y

Supports the Full 64-bit Pentium

Processor Data Bus at Frequencies up

to 66 MHz (82433LX and 82433NX)

Y

Drives 3 3V Signal Levels on the CPU

Data and Address Buses (82433NX)

Y

Provides a 64-Bit Interface to DRAM

and a 32-Bit Interface to PCI

Y

Five Integrated Write Posting and Read

Prefetch Buffers Increase CPU and PCI

Performance

CPU-to-Memory Posted Write Buffer

4 Qwords Deep

PCI-to-Memory Posted Write Buffer

Two Buffers 4 Dwords Each

PCI-to-Memory Read Prefetch Buffer

4 Qwords Deep

CPU-to-PCI Posted Write Buffer

4 Dwords Deep

CPU-to-PCI Read Prefetch Buffer

4 Dwords Deep

Y

CPU-to-Memory and CPU-to-PCI Write

Posting Buffers Accelerate Write

Performance

Y

Dual-Port Architecture Allows

Concurrent Operations on the Host and

PCI Buses

Y

Operates Synchronously to the CPU

and PCI Clocks

Y

Supports Burst Read and Writes of

Memory from the Host and PCI Buses

Y

Sequential CPU Writes to PCI

Converted to Zero Wait-State PCI

Bursts with Optional TRDY

Connection

Y

Byte Parity Support for the Host and

Memory Buses

Optional Parity Generation for Host

to Memory Transfers

Optional Parity Checking for the

Secondary Cache

Parity Checking for Host and PCI

Memory Reads

Parity Generation for PCI to Memory

Writes

Y

160-Pin QFP Package

Two 82433LX or 82433NX Local Bus Accelerator (LBX) components provide a 64-bit data path between the

host CPU Cache and main memory a 32-bit data path between the host CPU bus and PCI Local Bus and a

32-bit data path between the PCI Local Bus and main memory The dual-port architecture allows concurrent

operations on the host and PCI Buses The LBXs incorporate three write posting buffers and two read prefetch

buffers to increase CPU and PCI performance The LBX supports byte parity for the host and main memory

buses The 82433NX is intended to be used with the 82434NX PCI Cache Memory Controller (PCMC) The

82433LX is intended to be used with the 82434LX PCMC During bus operations between the host main

memory and PCI the PCMC commands the LBXs to perform functions such as latching address and data

merging data and enabling output buffers Together these three components form a ``Host Bridge'' that

provides a full function dual-port data path interface linking the host CPU and PCI bus to main memory

This document describes both the 82433LX and 82433NX Shaded areas like this one describe the

82433NX operations that differ from the 82433LX

82433LX 82433NX

290478 ≠ 1

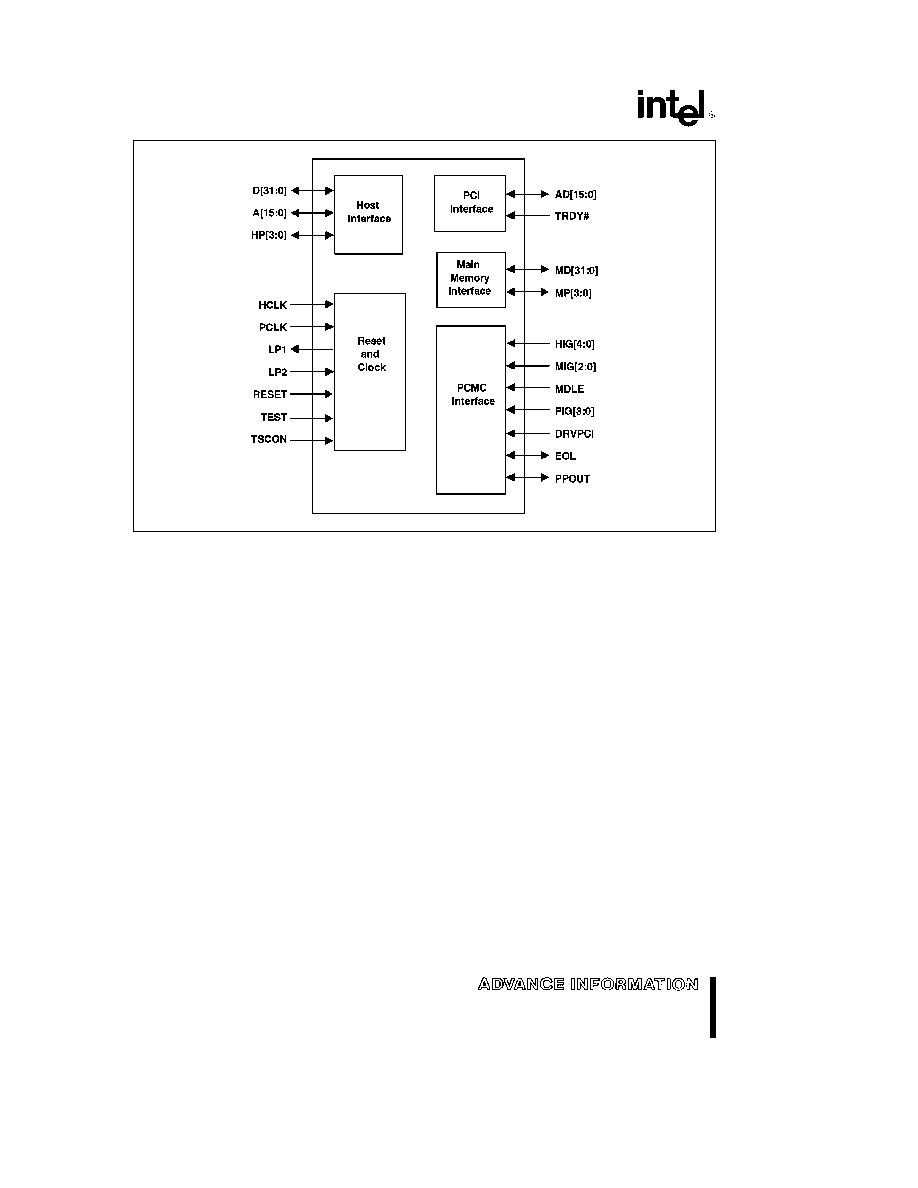

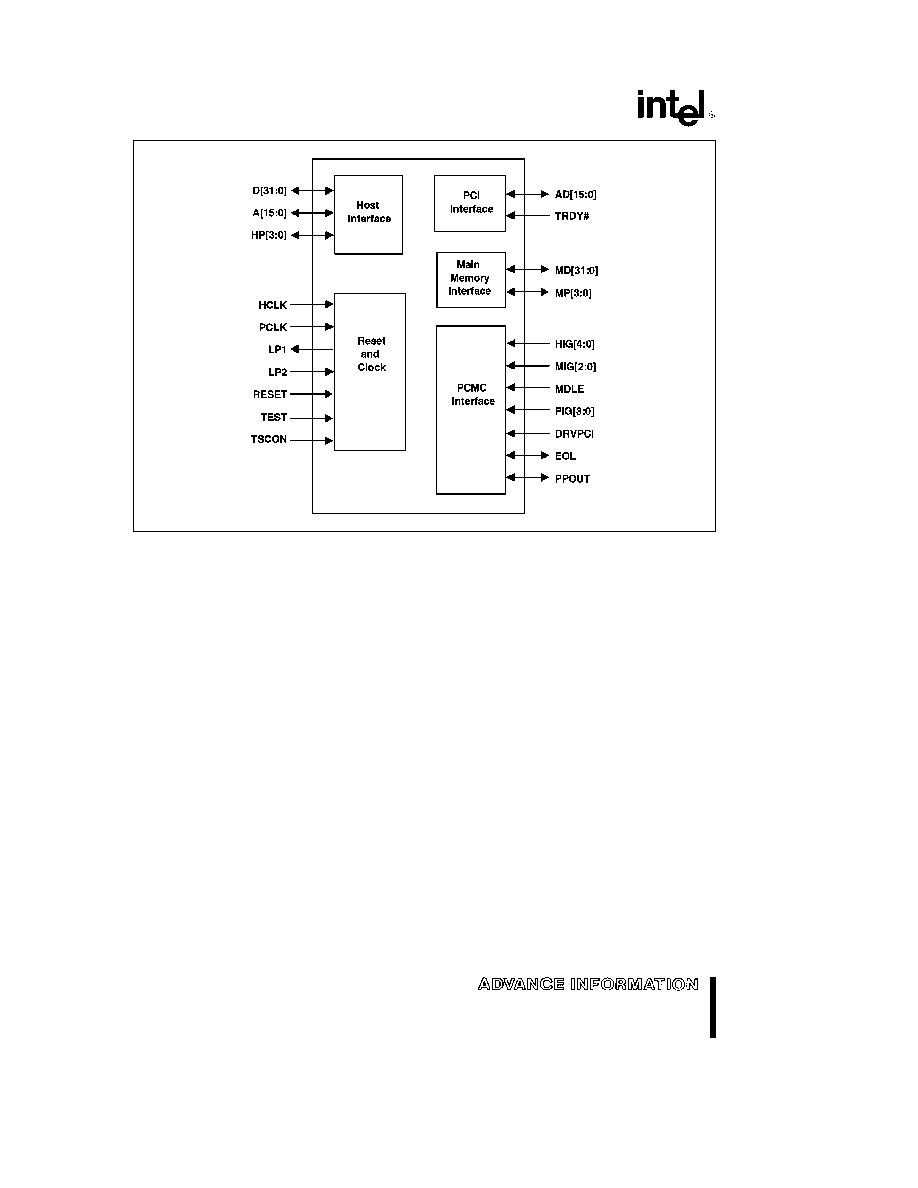

LBX Simplified Block Diagram

2

82433LX 82433NX

LOCAL BUS ACCELERATOR (LBX)

CONTENTS

PAGE

1 0 ARCHITECTURAL OVERVIEW

5

1 1 Buffers in the LBX

5

1 2 Control Interface Groups

7

1 3 System Bus Interconnect

7

1 4 PCI TRDY

Interface

8

1 5 Parity Support

8

2 0 SIGNAL DESCRIPTIONS

8

2 1 Host Interface Signals

9

2 2 Main Memory (DRAM) Interface Signals

10

2 3 PCI Interface Signals

10

2 4 PCMC Interface Signals

10

2 5 Reset and Clock Signals

11

3 0 FUNCTIONAL DESCRIPTION

12

3 1 LBX Post and Prefetch Buffers

12

3 1 1 CPU-TO-MEMORY POSTED WRITE BUFFER

12

3 1 2 PCI-TO-MEMORY POSTED WRITE BUFFER

12

3 1 3 PCI-TO-MEMORY READ PREFETCH BUFFER

12

3 1 4 CPU-TO-PCI POSTED WRITE BUFFER

13

3 1 5 CPU-TO-PCI READ PREFETCH BUFFER

14

3 2 LBX Interface Command Descriptions

14

3 2 1 HOST INTERFACE GROUP HIG 4 0

14

3 2 2 MEMORY INTERFACE GROUP MIG 2 0

18

3 2 3 PCI INTERFACE GROUP PIG 3 0

19

3 3 LBX Timing Diagrams

21

3 3 1 HIG 4 0 COMMAND TIMING

21

3 3 2 HIG 4 0 MEMORY READ TIMING

22

3 3 3 MIG 2 0 COMMAND

23

3 3 4 PIG 3 0 COMMAND DRVPCI AND PPOUT TIMING

24

3 3 5 PIG 3 0 READ PREFETCH BUFFER COMMAND TIMING

25

3 3 6 PIG 3 0 END-OF-LINE WARNING SIGNAL EOL

27

3 4 PLL Loop Filter Components

29

3 5 PCI Clock Considerations

30

3

CONTENTS

PAGE

4 0 ELECTRICAL CHARACTERISTICS

31

4 1 Absolute Maximum Ratings

31

4 2 Thermal Characteristics

31

4 3 DC Characteristics

32

4 3 1 82433LX LBX DC CHARACTERISTICS

32

4 3 2 82433NX LBX DC CHARACTERISTICS

33

4 4 82433LX AC Characteristics

35

4 4 1 HOST AND PCI CLOCK TIMING 66 MHz (82433LX)

35

4 4 2 COMMAND TIMING 66 MHz (82433LX)

36

4 4 3 ADDRESS DATA TRDY

EOL TEST TSCON AND PARITY TIMING 66 MHz

(82433LX)

37

4 4 4 HOST AND PCI CLOCK TIMING 60 MHz (82433LX)

38

4 4 5 COMMAND TIMING 60 MHz (82433LX)

38

4 4 6 ADDRESS DATA TRDY

EOL TEST TSCON AND PARITY TIMING 60 MHz

(82433LX)

39

4 4 7 TEST TIMING (82433LX)

40

4 5 82433NX AC Characteristics

40

4 5 1 HOST AND PCI CLOCK TIMING (82433NX)

40

4 5 2 COMMAND TIMING (82433NX)

41

4 5 3 ADDRESS DATA TRDY

EOL TEST TSCON AND PARITY TIMING

(82433NX)

41

4 5 4 TEST TIMING (82433NX)

42

4 5 5 TIMING DIAGRAMS

43

5 0 PINOUT AND PACKAGE INFORMATION

45

5 1 Pin Assignment

45

5 2 Package Information

50

6 0 TESTABILITY

51

6 1 NAND Tree

51

6 1 1 TEST VECTOR TABLE

51

6 1 2 NAND TREE TABLE

51

6 2 PLL Test Mode

53

4

82433LX 82433NX

1 0 ARCHITECTURAL OVERVIEW

The 82430 PCIset consists of the 82434LX PCMC

and 82433LX LBX components plus either a PCI

ISA bridge or a PCI EISA bridge The 82430NX PCI-

set consists of the 82434NX PCMC and 82433NX

LBX components plus either a PCI ISA bridge or a

PCI EISA bridge The PCMC and LBX provide the

core cache and main memory architecture and

serves as the Host PCI bridge An overview of the

PCMC follows the system overview section

The Local Bus Accelerator (LBX) provides a high

performance

data

and

address

path

for

the

82430LX 82430NX PCIset The LBX incorporates

five integrated buffers to increase the performance

of the Pentium processor and PCI master devices

Two LBXs in the system support the following areas

1 64-bit data and 32-bit address bus of the Pentium

processor

2 32-bit multiplexed address data bus of PCI

3 64-bit data bus of the main memory

In addition the LBXs provide parity support for the

three areas noted above (discussed further in Sec-

tion 1 4)

1 1 Buffers in the LBX

The LBX components have five integrated buffers

designed to increase the performance of the Host

and PCI Interfaces of the 82430LX 82430NX

PCIset

With the exception of the PCI-to-Memory write buffer

and the CPU-to-PCI write buffer the buffers in the

LBX store data only addresses are stored in the

PCMC component

5