Other brands and names are the property of their respective owners

Information in this document is provided in connection with Intel products Intel assumes no liability whatsoever including infringement of any patent or

copyright for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products Intel retains the right to make

changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata

October 1995

COPYRIGHT

INTEL CORPORATION 1996

Order Number 281630-001

82595TX

ISA PCMCIA HIGH INTEGRATION

ETHERNET CONTROLLER

Y

Optimal Integration for Lowest Cost

Solution

Glueless 8-Bit 16-Bit ISA PCMCIA 2 0

Bus Interface

Provides Fully 802 3 Compliant AUI

and TPE Serial Interface

Local DRAM Support up to

64 Kbytes

FLASH EPROM Boot Support up to

1 Mbyte for Diskless Workstations

Hardware and Software Portable

between Motherboard Adapter and

PCMCIA LAN Card Solution

Y

High Performance Networking

Functions

Concurrent Processing Functionality

for Enhanced Performance

16-Bit 32-Bit IO Accesses to Local

DRAM with Zero Added Wait-States

Ring Buffer Structure for Continuous

Frame Reception and Transmit

Chaining

Automatic Retransmission on

Collision

Automatically Corrects TPE Polarity

Switching Problems

Y

Low Power CHMOS IV Technology

Y

Ease of Use

Integrated Plug N' Play

TM

Hardware

Functionality

EEPROM Interface to Support

Jumperless Designs

Software Structures Optimized to

Reduce Processing Steps

Automatically Maps into Unused PC

IO Locations to Help Eliminate LAN

Setup Problems

All Software Structures Contained in

One 16-Byte IO Space

JTAG Port for Reduced Board

Testing Times

Automatic or Manual Switching

between TPE and AUI Ports

Y

Power Management

SL Compatible SMOUT Power Down

Input

Software Power Down Command for

Non-SL Systems

Y

144-Lead tQFP Package Provides

Smallest Available Form Factor

Y

100% Backwards Hardware Software

Compatible to 82595

281630 ≠ 1

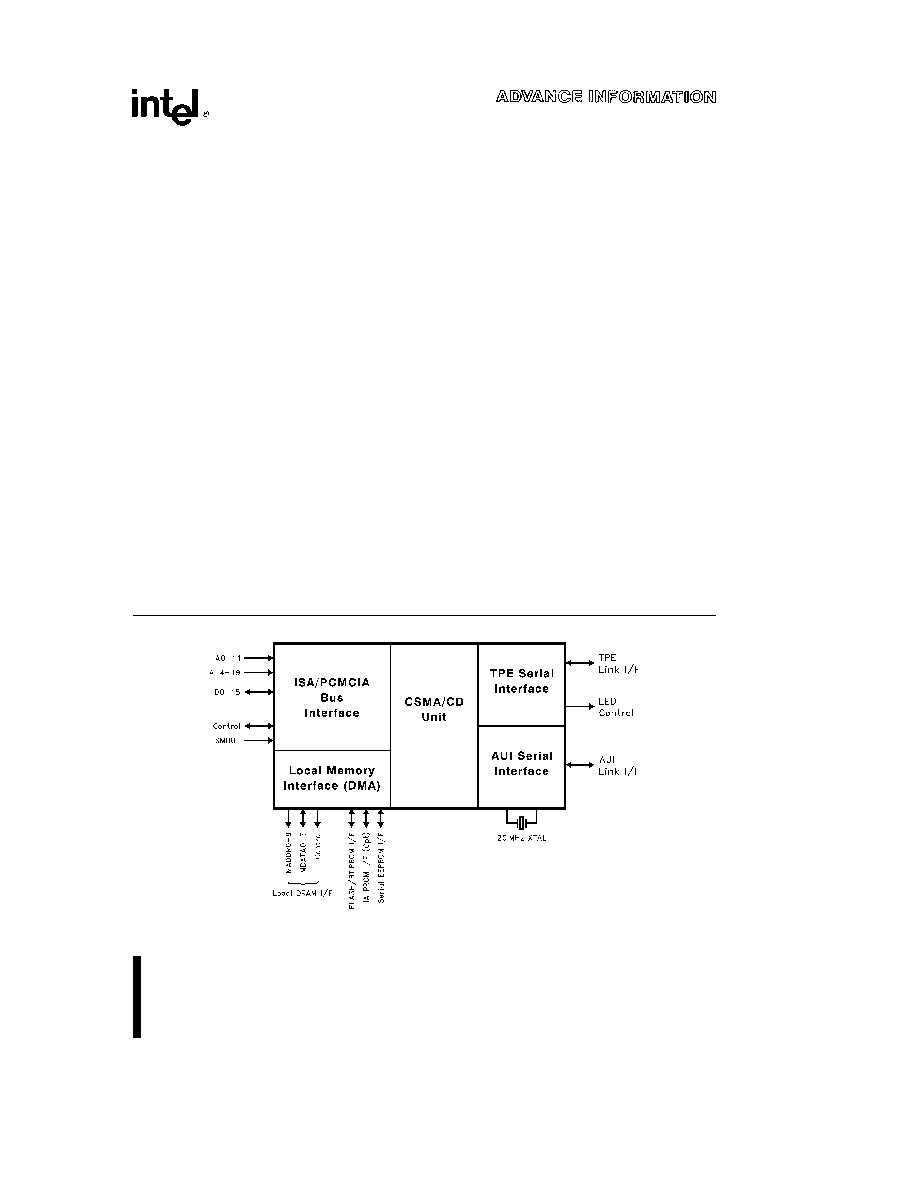

Figure 1 82595TX Block Diagram

82595TX

ISA PCMCIA High Integration ETHERNET Controller

CONTENTS

PAGE

1 0 INTRODUCTION

5

1 1 82595TX Overview

5

1 2 Enhancements to the 82595

5

1 3 Compliance to Industry

Standards

5

1 3 1 Bus Interface

ISA IEEE

P996 PCMCIA 2 0

6

1 3 2 ETHERNET Twisted Pair

Ethernet Interface

IEEE 802 36

Specification

6

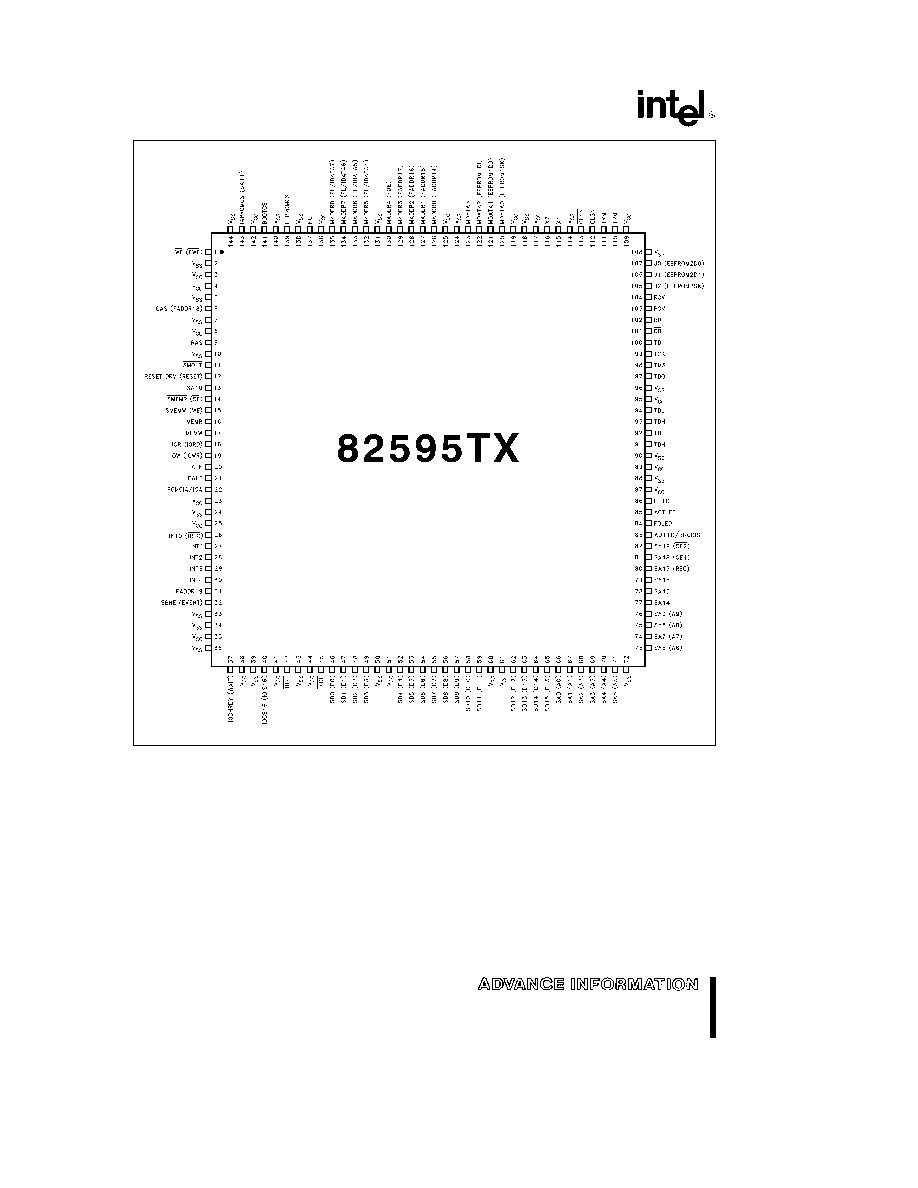

2 0 82595TX PIN DEFINITIONS

6

2 1 ISA Bus Interface

6

2 2 PCMCIA Bus Interface

8

2 3 Local Memory Interface

9

2 4 Miscellaneous Control

11

2 5 JTAG Control

11

2 6 Serial Interface

12

2 7 Power and Ground

13

2 8 82595TX Pin Summary

14

3 0 82595TX INTERNAL

ARCHITECTURE OVERVIEW

15

3 1 System Interface Overview

15

3 1 1 Concurrent Processing

Functionality

15

3 2 Local Memory Interface

15

3 3 CSMA CD Unit

16

3 4 Serial Interface

16

4 0 ACCESSING THE 82595TX

16

4 1 82595TX Register Map

16

4 1 1 IO Bank 0

17

4 1 2 IO Bank 1

18

4 1 3 IO Bank 2

19

4 2 Writing to the 82595TX

19

4 3 Reading from the 82595TX

20

CONTENTS

PAGE

4 4 Local DRAM Accesses

20

4 4 1 Writing to Local Memory

20

4 4 2 Reading from Local

Memory

20

4 5 Serial EEPROM Interface

21

4 6 Boot EPROM FLASH Interface

22

4 7 IA PROM Interface

22

4 8 PCMCIA CIS Structures

22

4 9 PCMCIA Decode Functions

22

5 0 COMMAND AND STATUS

INTERFACE

23

5 1 Command OP Code Field

23

5 2 ABORT (Bit 5)

23

5 3 Pointer Field (Bits 6 and 7)

23

5 4 82595TX Status Interface

24

6 0 INITIALIZATION

24

7 0 FRAME TRANSMISSION

25

7 1 82595TX XMT Block Memory

Format

25

7 2 XMT Chaining

27

7 3 Automatic Retransmission on

Collision

30

8 0 FRAME RECEPTION

30

8 1 82595TX RCV Memory

Structure

30

8 2 RCV Ring Buffer Operation

33

9 0 SERIAL INTERFACE

34

10 0 APPLICATION NOTES

35

10 1 Bus Interface

35

10 2 Local Memory Interface

35

10 3 EEPROM Interface (ISA Only)

35

10 4 Serial Interface

35

10 4 1 AUI Circuit

35

10 4 2 TPE Circuit

35

10 4 3 LED Circuit

36

2

CONTENTS

PAGE

10 5 Layout Guidelines

36

10 5 1 General

36

10 5 2 Crystal

36

10 5 3 82595TX Analog Differential

Signals

36

10 5 4 Decoupling

Considerations

36

11 0 ELECTRICAL SPECIFICATIONS

AND TIMINGS

37

11 1 Absolute Maximum Ratings

37

11 1 1 Package Thermal

Specifications

38

CONTENTS

PAGE

11 2 A C Timing Characteristics

38

11 3 A C Measurement Conditions

38

11 4 ISA Interface Timing

39

11 5 PCMCIA Interface Timing

44

11 6 Local Memory Timings

47

11 6 1 DRAM Timings

47

11 6 2 FLASH EPROM Timings

49

11 6 3 IA PROM Timings

51

11 7 Interrupt Timing

52

11 8 RESET and SMOUT Timing

52

11 9 JTAG Timing

53

11 10 Serial Timings

54

3

82595TX

1 0

INTRODUCTION

1 1 82595TX Overview

The 82595TX is a highly integrated high perform-

ance LAN controller which provides a cost effective

LAN solution for ISA compatible Personal Computer

(PC) motherboards (both desktop and portable)

add-on ISA adapter boards and PCMCIA cards The

82595TX integrates all of the major functions of a

buffered LAN solution into one chip with the excep-

tion of the local buffer memory which is implement-

ed by adding one DRAM component to the LAN so-

lution The 82595TX's new Concurrent Processing

feature significantly enhances throughput perform-

ance Both system bus and serial link activities occur

concurrently allowing the 82595TX to maximize net-

work bandwidth by minimizing delays associated

with transmit or receiving frames The 82595TX's

bus interface is a glueless attachment to either an

ISA or PCMCIA version 2 0 bus Its serial interface

provides a Twisted Pair Ethernet (TPE) and an At-

tachment Unit Interface (AUI) connection By inte-

grating the majority of the LAN solution functions

into one cost effective component production cost

saving can be achieved as well as significantly de-

creasing the design time for a solution This level of

integration also allows an 82595TX solution to be

ported between different applications (PC mother-

boards adapters and PCMCIA IO cards) while

maintaining a compatible hardware and software

base This results in further savings in both hardware

and software development costs for manufacturers

expanding into different applications i e

an ISA

adapter vendor producing PCMCIA IO cards etc

The 82595TX's software interface is optimized to re-

duce the number of processing steps that are re-

quired to interface to the 82595TX solution The

82595TX's initialization and control registers are di-

rectly addressable within one 16-byte IO address

block The 82595TX can automatically resolve any

conflicts to an IO block by moving its IO offset to an

unused location in the case that a conflict occurs

The 82595TX's local memory is arranged in a simple

ring buffer structure for efficient transfer of transmit

and receive packets

The local memory

up to

64 Kbytes of DRAM resides as either a 16-bit or 32-

bit IO port in the host systems IO map programma-

ble through configuration The 82595TX provides di-

rect control over the local DRAM including refresh

The 82595TX performs a prefetch to the DRAM

memory allowing CPU IO cycles to this data with no

added wait-states The 82595TX also provides an

interface to up to 1 Mbyte of FLASH or EPROM

memory An interface to an EEPROM which holds

solution configuration values and can also contain

the Node ID allows for the implementation of a

``jumperless'' design In addition the 82595TX con-

tains full hardware support for the implementation of

the ISA Plug N' Play specification Plug N' Play elimi-

nates jumpers and complicated setup utilities by al-

lowing peripheral functions to be added to a PC au-

tomatically (such as adapter cards) without the need

to individually configure each parameter (e g Inter-

rupt IO Address etc) This allows for configuration

ease-of-use which results in minimal time associat-

ed with installation

The 82595TX's packaging and power management

features are designed to consume minimal board

real estate and system power This is required for

applications such as portable PC motherboard de-

signs and PCMCIA cards which require a solution

with very low real estate and power consumption

The 82595TX package is a 144-lead tQFP (thin

Quad Flat Pack) Its dimensions are 20 mm by

20 mm and 1 7 mm in height (roughly the same area

as a US Nickel and the same height as a US Dime)

The 82595TX contains two power down modes an

SL compatible power down mode which utilizes the

SL SMOUT input and a POWER DOWN command

for non-SL systems

1 2 Enhancements to the 82595

The 82595TX is fully backwards compatible to the

82595 both in pinout and software However the

82595TX contains several advanced functions from

the 82595 which increase performance and ease of

use The following is a list of the major enhance-

ments to the 82595TX

Concurrent Processing Functionality

32-Bit Local Memory IO Port

Integrated Plug N' Play support

Added EEPROM Interface for Plug N' Play

Flash addressing up to 1 Mbyte (versus 256K for

82595)

For further information on these enhancements

and a description of all the differences between

the 82595 and 82595TX please consult the

82595TX User's Manual available through your

local sales representative

1 3 Compliance to Industry Standards

The 82595TX has two interfaces the host system

interface which is an ISA or PCMCIA bus interface

and the serial or network interface Both interfaces

have been standardized by the IEEE

5