Document Outline

- TITLE PAGE

- CONTENTS

- REVISION HISTORY

- 1.0 INTRODUCTION

- 2.0 DEVICE PINOUT

- 3.0 MEMORY MAPS

- 3.1 Extended Status Registers Memory Map

- 4.0 BUS OPERATIONS, COMMANDS AND STATUS REGISTER DEFINITIONS

- 4.1 Bus Operations

- 4.2 28F008SAÑCompatible Mode Command Bus Definitions

- 4.3 28F016XDÑEnhanced Command Bus Definitions

- 4.4 Compatible Status Register

- 4.5 Global Status Register

- 4.6 Block Status Register

- 5.0 ELECTRICAL SPECIFICATIONS

- 5.1 Absolute Maximum Ratings

- 5.2 Capacitance

- 5.3 Transient Input/Output Reference Waveforms

- 5.4 DC Characteristics VCC = 3.3V

- 5.5 DC Characteristics vcc = 5.0V

- 5.6 AC Characteristics VCC = 3.3V

- Read, Program, Read-Modify-Program and Refresh Cycles

- Read Cycle

- Write Cycle

- Read-Modify-Write Cycle

- Fast Page Mode Cycle

- Fast Page Mode Read-Modify-Write Cycle

- Refresh Cycle

- Refresh

- Misc. Specifications

- 5.7 AC Characteristics VCC -5.0V

- Read, Write, Read-Modify-Write and Refresh Cycles (Common Parameters)

- Read Cycle

- Write Cycle

- Read-Modify-Write Cycle

- Fast Page Mode Cycle

- Fast Page Mode Read-Modify-Write Cycle

- Refresh Cycle

- Refresh

- Misc. Specifications

- 5.8 AC Waveforms

- 5.9 Power-Up and Reset Timings

- 5.10 Erase and Word Program Performance

- 6.0 MECHANICAL SPECIFICATIONS

- APPENDIX A: Device Nomenclature and Ordering Information

- APPENDIX B: Additional Information

- FIGURES

- Figure 1. 28F016XD Block Diagram

- Figure 2. 28F016XD 56-Lead TSOP Type I Pinout Configuration

- Figure 3. 28F016XD Memory Map

- Figure 4. Extended Status Registers Memory Map

- Figure 5. Transient Input/Output Reference Waveform for V CC = 5.0V ± 0.5V

- Figure 6. Transient Input/Output Reference Waveform for V CC = 3.3V ± 0.3V

- Figure 7. AC Waveforms for Read Operations

- Figure 8. AC Waveforms for Early Write Operations

- Figure 9. AC Waveforms for Delayed Write Operations

- Figure 10. AC Waveforms for Read-Modify-Write Operations

- Figure 11. AC Waveforms for Fast Page Mode Read Operations

- Figure 12. AC Waveforms for Fast Page Mode Early Write Operations

- Figure 13. AC Waveforms for Fast Page Mode Delayed Write Operations

- Figure 14. AC Waveforms for Fast Page Mode Read-Modify-Write Operations

- Figure 15. AC Waveforms for RAS#-Only Refresh Operations

- Figure 16. AC Waveforms for CAS#-before-RAS# Refresh Operations

- Figure 17. AC Waveforms for Hidden Refresh Operations

- Figure 18. AC Waveforms for Self-Refresh Operations

- Figure 19. V CC Power-Up and RP# Reset Waveforms

- Figure 20. Mechanical Specifications of the 28F016XD 56-Lead TSOP Type I Package

E

December 1996

Order Number: 290533-004

n

85 ns Access Time (t

RAC

)

Supports both Standard and Fast-

Page-Mode Accesses

n

Multiplexed Address Bus

RAS# and CAS# Control Inputs

n

No-Glue Interface to Many Memory

Controllers

n

SmartVoltage Technology

User-Selectable 3.3V or 5V V

CC

User-Selectable 5V or 12V V

PP

n

0.33 MB/sec Write Transfer Rate

n

x16 Architecture

n

56-Lead TSOP Type I Package

n

Backwards-Compatible with 28F008SA

Command Set

n

2 µA Typical Deep Power-Down Current

n

1 mA Typical I

CC

Active Current in Static

Mode

n

32 Separately-Erasable/Lockable

64-Kbyte Blocks

n

1 Million Erase Cycles per Block

n

State-of-the-Art 0.6 µm ETOXTM IV Flash

Technology

Intel's 28F016XD 16-Mbit flash memory is a revolutionary architecture which is the ideal choice for designing

truly revolutionary high-performance products. Combining its DRAM-like read performance and interface with

the intrinsic nonvolatility of flash memory, the 28F016XD eliminates the traditional redundant memory

paradigm of shadowing code from a slow nonvolatile storage source to a faster execution memory, such as

DRAM, for improved system performance. The innovative capabilities of the 28F016XD enable the design of

direct-execute code and mass storage data/file flash memory systems.

The 28F016XD's DRAM-like interface with a multiplexed address bus, flexible V

CC

and V

PP

voltages, power

saving features, extended cycling, fast program and read performance, symmetrically-blocked architecture,

and selective block locking provide a highly flexible memory component suitable for resident flash component

arrays on the system board or SIMMs. The DRAM-like interface with RAS# and CAS# control inputs allows

for easy migration to flash memory in existing DRAM-based systems. The 28F016XD's dual read voltage

allows the same component to operate at either 3.3V or 5.0V V

CC

. Programming voltage at 5.0V V

PP

minimizes external circuitry in minimal-chip, space critical designs, while the 12.0V V

PP

option maximizes

program/erase performance. The x16 architecture allows optimization of the memory-to-processor interface.

Its high read performance combined with flexible block locking enable both storage and execution of

operating systems/application software and fast access to large data tables. The 28F016XD is manufactured

on Intel's 0.6 µm ETOX IV process technology.

28F016XD

16-MBIT (1 MBIT x 16)

DRAM-INTERFACE FLASH MEMORY

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of

Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to

sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or

infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life

saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The 28F016XD may contain design defects or errors known as errata. Current characterized errata are available upon request.

*Third-party brands and names are the property of their respective owners.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

CG-041493

E

28F016XD FLASH MEMORY

3

CONTENTS

PAGE

PAGE

1.0

INTRODUCTION ......................................... 5

1.1

Product Overview...................................... 5

2.0

DEVICE PINOUT......................................... 6

2.1

Lead Descriptions ..................................... 9

3.0

MEMORY MAPS ....................................... 11

3.1

Extended Status Registers

Memory Map ........................................ 12

4.0

BUS OPERATIONS, COMMANDS AND

STATUS REGISTER DEFINITIONS.......... 13

4.1

Bus Operations ....................................... 13

4.2

28F008SA--Compatible Mode

Command Bus Definitions.................... 14

4.3

28F016XD--Enhanced Command

Bus Definitions ..................................... 15

4.4

Compatible Status Register .................... 16

4.5

Global Status Register ............................ 17

4.6

Block Status Register.............................. 18

5.0

ELECTRICAL SPECIFICATIONS ............. 19

5.1

Absolute Maximum Ratings..................... 19

5.2

Capacitance ............................................ 20

5.3

Transient Input/Output Reference

Waveforms........................................... 21

5.4

DC Characteristics

(V

CC

= 3.3V

±

0.3V).............................. 22

5.5

DC Characteristics

(V

CC

= 5.0V

±

0.5V).............................. 25

5.6

AC Characteristics

(V

CC

= 3.3V

±

0.3V).............................. 28

Read, Write, Read-Modify-Write and

Refresh Cycles (Common Parameters) .... 28

Read Cycle............................................... 28

Write Cycle ............................................... 29

Read-Modify-Write Cycle.......................... 30

Fast Page Mode Cycle ............................. 30

Fast Page Mode Read-Modify-Write

Cycle ........................................................ 30

Refresh Cycle........................................... 31

Misc. Specifications .................................. 31

5.7

AC Characteristics

(V

CC

= 5.0V

±

0.5V).............................. 33

Read, Write, Read-Modify-Write and

Refresh Cycles (Common Parameters) .... 33

Read Cycle............................................... 34

Write Cycle ............................................... 35

Read-Modify-Write Cycle.......................... 35

Fast Page Mode Cycle ............................. 35

Fast Page Mode Read-Modify-Write

Cycle ........................................................ 36

Refresh Cycle........................................... 36

Misc. Specifications .................................. 37

5.8

AC Waveforms ........................................ 38

5.9

Power-Up and Reset Timings.................. 50

5.10 Erase and Word Program Performance .. 51

6.0

MECHANICAL SPECIFICATIONS ............ 52

APPENDIX A: Device Nomenclature and

Ordering Information ..................................... 53

APPENDIX B: Additional Information............... 54

28F016XD FLASH MEMORY

E

4

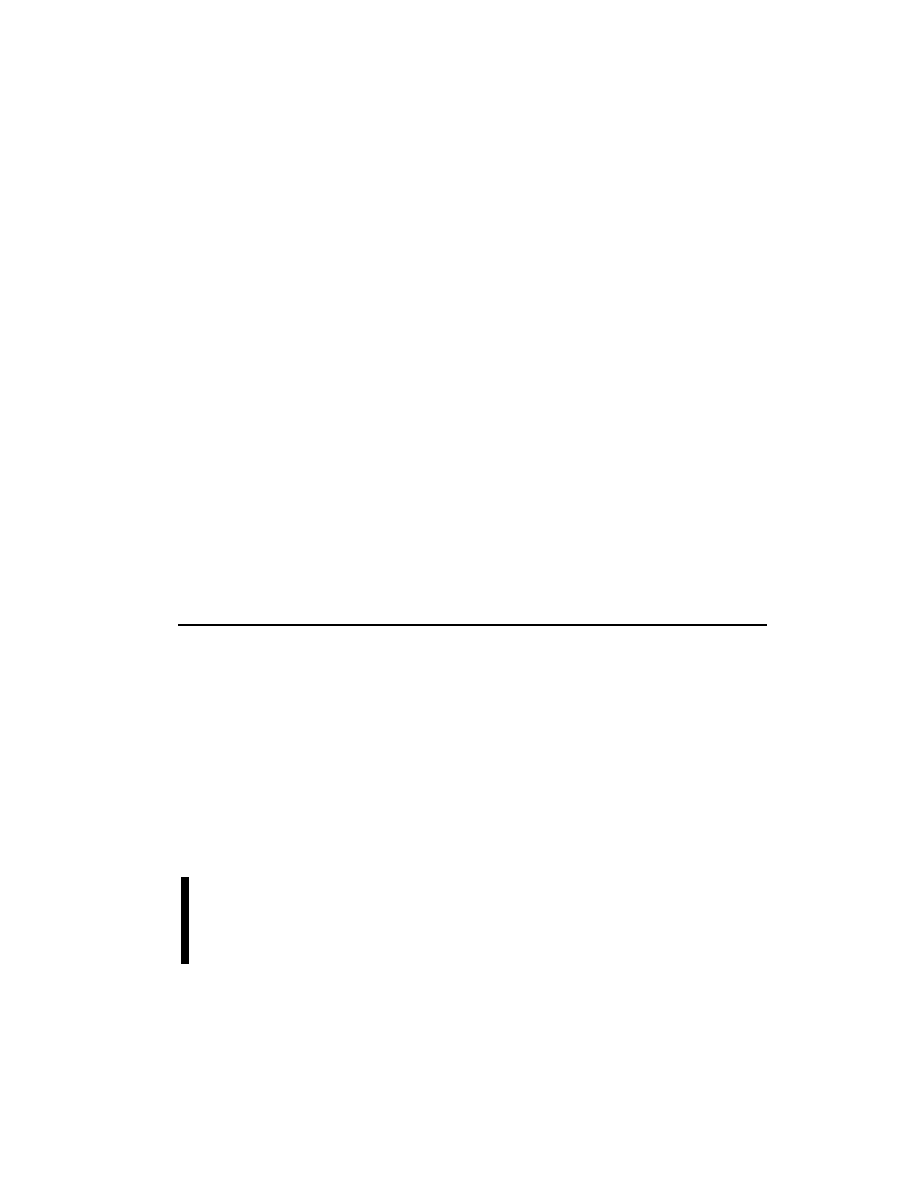

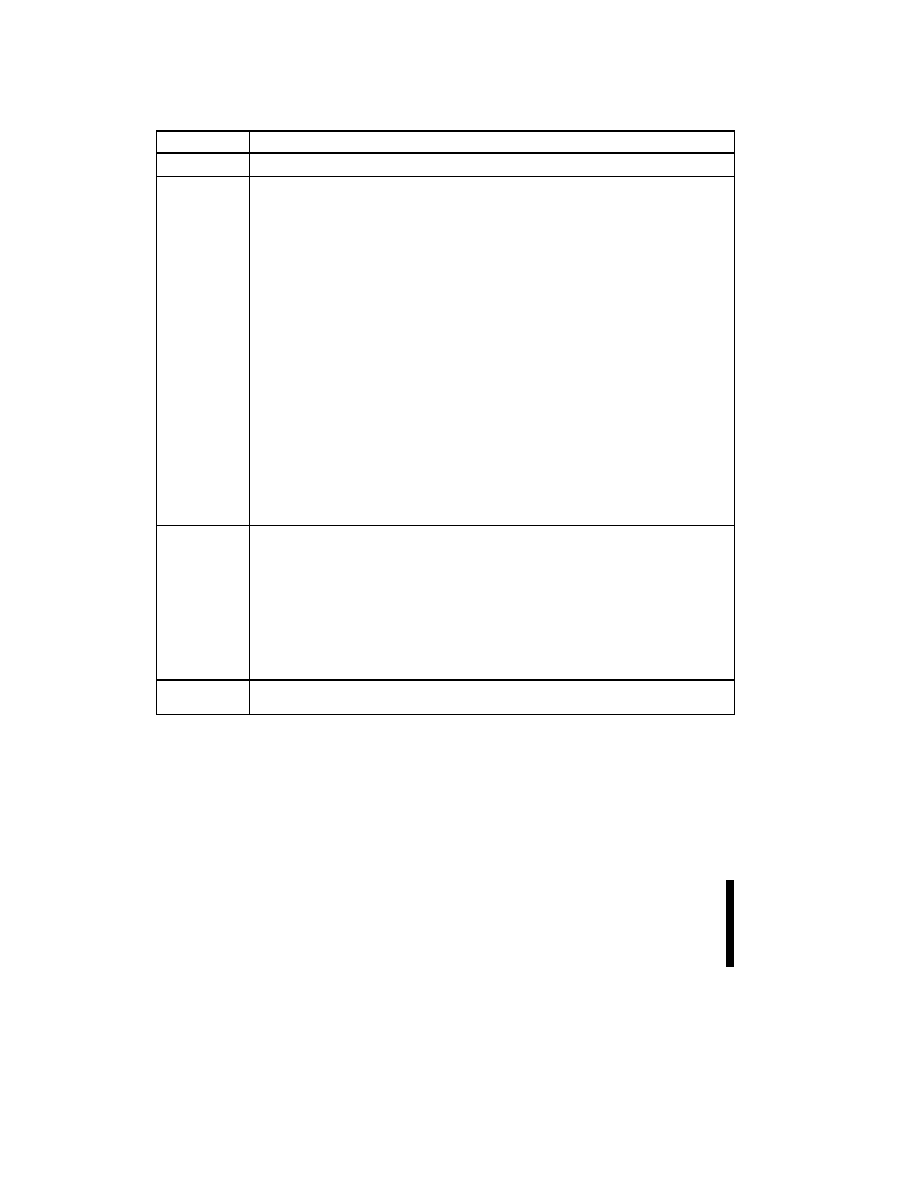

REVISION HISTORY

Number

Description

-001

Original Version

-002

Removed support of the following features:

∑

All page buffer operations (read, write, programming, Upload Device Information)

∑

Command queuing

∑

Software Sleep and Abort

∑

Erase All Unlocked Blocks

∑

Device Configuration command

Changed definition of "NC." Removed "No internal connection to die" from description.

Added "xx" to Upper Byte of Command (Data) Definition in Sections 4.2 and 4.3.

Modified parameters "V" and "I" of Section 5.1 to apply to "NC" pins.

Increased I

PPS

(V

PP

Read Current) for V

PP

> V

CC

to 200 µA at V

CC

= 3.3V/5.0V.

Changed V

CC

= 5.0V DC Characteristics (Section 5.5) marked with Note 1 to indicate

that these currents are specified for a CMOS rise/fall time (10% to 90%) of <5 ns

and a TTL rise/fall time of <10 ns.

Corrected "RP# high to RAS# going low" to be a "Min" specification at V

CC

= 3.3V/5.0V.

Increased Typical "Word/Block Program Times" (t

WHRH1

/t

WHRH3

) for V

PP

= 5.0V:

t

WHRH1

from 24.0 µs to 35.0 µs and t

WHRH3

from 0.8 sec to 1.2 sec at V

CC

= 3.3V

t

WHRH1

from 16.0 µs to 25.0 µs and t

WHRH3

from 0.6 sec to 0.85 sec at V

CC

= 5.0V

Changed "Time from Erase Suspend Command to WSM Ready" spec name to "Erase

Suspend Latency Time to Read;" modified typical values and added Min/Max

values at V

CC

=3.3/5.0V and V

PP

=5.0/12.0V (Section 5.10).

Minor cosmetic changes throughout document.

-003

Added 3/5# pin to Pinout Configuration (Figure 2), Product Overview (Section 1.1) and

Lead Descriptions (Section 2.1)

Modified Block Diagram (Figure 1): Removed Address/Data Queues, Page Buffers, and

Address Counter; Added 3/5# pin

Added 3/5# pin to Test Conditions of I

CC

2 and I

CC

5 Specifications

Modified Power-Up and Reset Timings (Section 5.9) to include 3/5# pin: Removed t

5VPH

and t

3VPH

specifications; Added t

PLYL

, t

PLYH

, t

YLPH

, and t

YHPH

specifications

Corrected TSOP Mechanical Specification A1 from 0.50 mm to 0.050 mm (Section 6.0)

Minor cosmetic changes throughout document.

-004

Updated DC Specifications I

CC

3, I

CC

4, I

CC

6, I

CC

7, I

CCD

and I

PPES

Updated AC Specifications t

CAS

(min), t

RCD

(max) and t

CWD

(min)

E

28F016XD FLASH MEMORY

5

1.0 INTRODUCTION

The documentation of the Intel 28F016XD flash

memory device includes this datasheet, a detailed

user's manual, and a number of application notes

and design tools, all of which are referenced in

Appendix B.

The datasheet is intended to give an overview of

the chip feature-set and of the operating AC/DC

specifications.

The 16-Mbit Flash Product Family

User's Manual provides complete descriptions of

the user modes, system interface examples and

detailed descriptions of all principles of operation.

It also contains the full list of software algorithm

flowcharts, and a brief section on compatibility

with the Intel 28F008SA.

Significant 28F016XD feature revisions occurred

between datasheet revisions 290533-001 and

290533-002. These revisions center around

removal of the following features:

∑

All page buffer operations (read, write,

programming, Upload Device Information)

∑

Command queuing

∑

Software Sleep and Abort

∑

Erase all Unlocked Blocks

∑

Device Configuration command

In addition, a significant 28F016XD change

occurred between datasheet revisions 290532-002

and 290532-003. This change centers around the

addition of a 3/5# pin to the device's pinout

configuration. Figure 2 shows the 3/5# pin

assignment for the TSOP Type 1 package.

Intel recommends that all customers obtain the

latest revisions of 28F016XD documentation.

1.1 Product Overview

The 28F016XD is a high-performance, 16-Mbit

(16,777,216-bit) block erasable, nonvolatile

random access memory, organized as

1 Mword x 16. The 28F016XD includes thirty-two

32-KW (32,768 word) blocks. A chip memory map

is shown in Figure 3.

The implementation of a new architecture, with

many enhanced features, will improve the device

operating characteristics and result in greater

product reliability and ease-of-use as compared to

other flash memories. Significant features of the

28F016XD include:

∑

No-Glue Interface to Memory Controllers

∑

Improved Word Program Performance

∑

SmartVoltage Technology

Selectable 3.3V or 5.0V V

CC

Selectable 5.0V or 12.0V V

PP

∑

Block Program/Erase Protection

The 28F016XD's multiplexed address bus with

RAS# and CAS# inputs allows for a "No Glue"

interface to many existing in-system memory

controllers. As such, 28F016XD-based SIMMs

(72-pin JEDEC Standard) offer attractive

advantages over their DRAM counterparts in many

applications. For more information on 28F016XD-

based SIMM designs, see the application note

referenced at the end of this datasheet.

The 28F016XD incorporates SmartVoltage

technology, providing V

CC

operation at both 3.3V

and 5.0V and program and erase capability at V

PP

= 12.0V or 5.0V. Operating at V

CC

= 3.3V, the

28F016XD consumes less than 60% of the power

consumption at 5.0V V

CC

, while 5.0V V

CC

provides

the highest read performance capability. V

PP

=

5.0V operation eliminates the need for a separate

12.0V converter, while V

PP

= 12.0V maximizes

program/erase performance. In addition to the

flexible program and erase voltages, the dedicated

V

PP

gives complete code protection with V

PP

V

PPLK

.

A 3/5# input pin configures the device's internal

circuitry for optimal 3.3V or 5.0V read/program

operation.

A Command User Interface (CUI) serves as the

system interface between the microprocessor or

microcontroller and the internal memory operation.

Internal Algorithm Automation allows word

programs and block erase operations to be

executed using a Two-Write command sequence

to the CUI in the same way as the 28F008SA 8-

Mbit FlashFileTM memory.

Software Locking of Memory Blocks is an added

feature of the 28F016XD as compared to the

28F008SA. The 28F016XD provides selectable

block locking to protect code or data such as

direct-executable operating systems or application

code. Each block has an associated nonvolatile

lock-bit which determines the lock status of the