Other brands and names are the property of their respective owners

Information in this document is provided in connection with Intel products Intel assumes no liability whatsoever including infringement of any patent or

copyright for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products Intel retains the right to make

changes to these specifications at any time without notice Microcomputer Products may have minor variations to this specification known as errata

October 1995

COPYRIGHT

INTEL CORPORATION 1996

Order Number 290421-004

82503

DUAL SERIAL TRANSCEIVER (DST)

82503 PRODUCT FEATURE SET OVERVIEW

Y

Single Component Ethernet Interface

to Both 802 3 10BASE-T and AUI

Y

Automatic or Manual Port Selection

Y

Manchester Encoder Decoder and

Clock Recovery

Y

No Glue Interface to Industry-Standard

LAN Controllers

Intel 82586 82590 82593 and 82596

AMD 7990 (LANCE )

National Semiconductor 8390 and

83932 (SONIC )

Western Digital 83C690

Fujitsu 86950 (Etherstar )

Y

Diagnostic Loopback

Y

Reset Low Power Modes

Y

Network Status Indicators

Y

Defeatable Jabber Timer

Y

User Test Modes

Y

10 MHz Transmit Clock Generator

Y

One Micron CHMOS

IV (Px48)

Technology

Y

Single 5-V Supply

INTERFACE FEATURES

TPE

Y

Complies with 10BASE-T IEEE Std

802 3i-1990 for Twisted Pair Ethernet

Y

Selectable Polarity Switching

Y

Direct Interface to TPE Analog Filters

Y

On-Chip TPE Squelch

Y

Defeatable Link Integrity (LI)

Y

Support of Cable Lengths

l

100m

AUI

Y

Complies with IEEE 802 3 AUI Standard

Y

Direct Interface to AUI Transformers

Y

On-Chip AUI Squelch

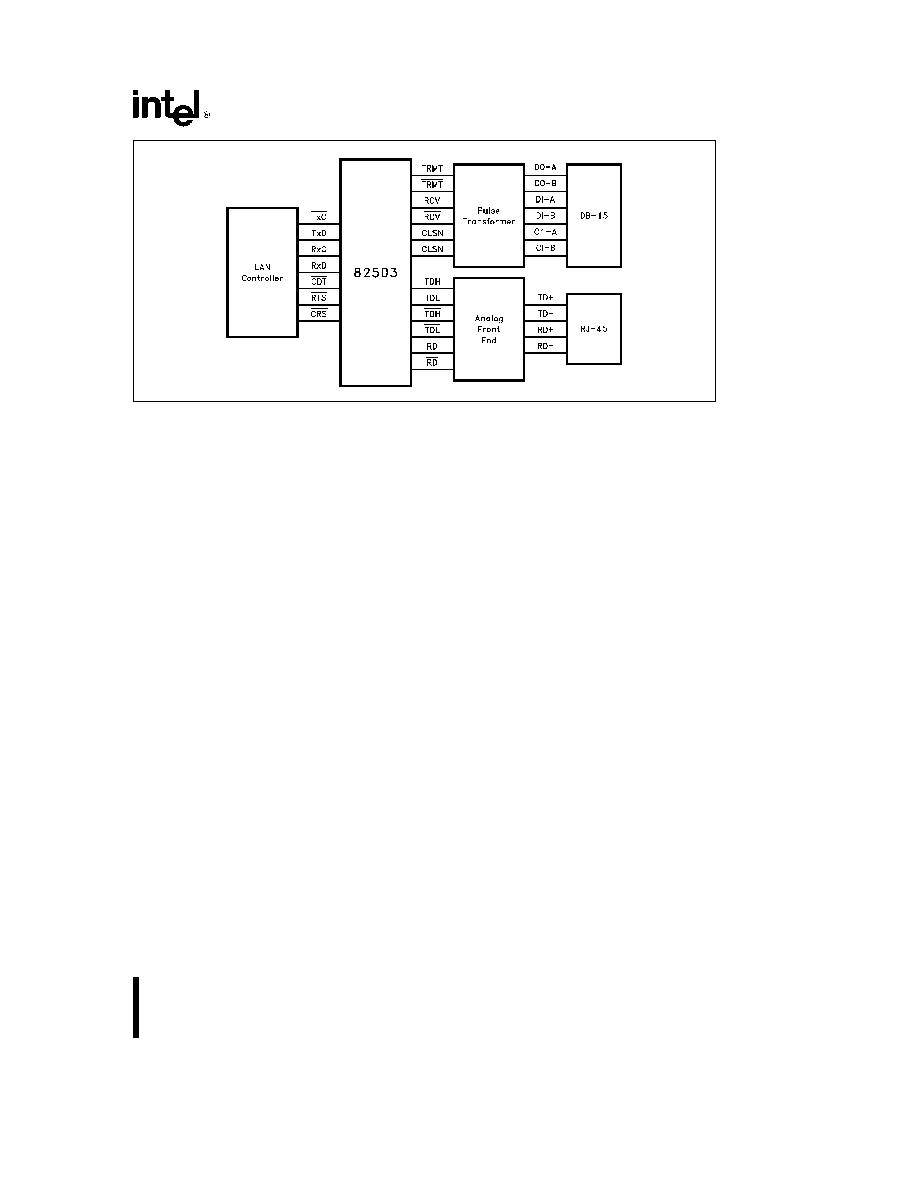

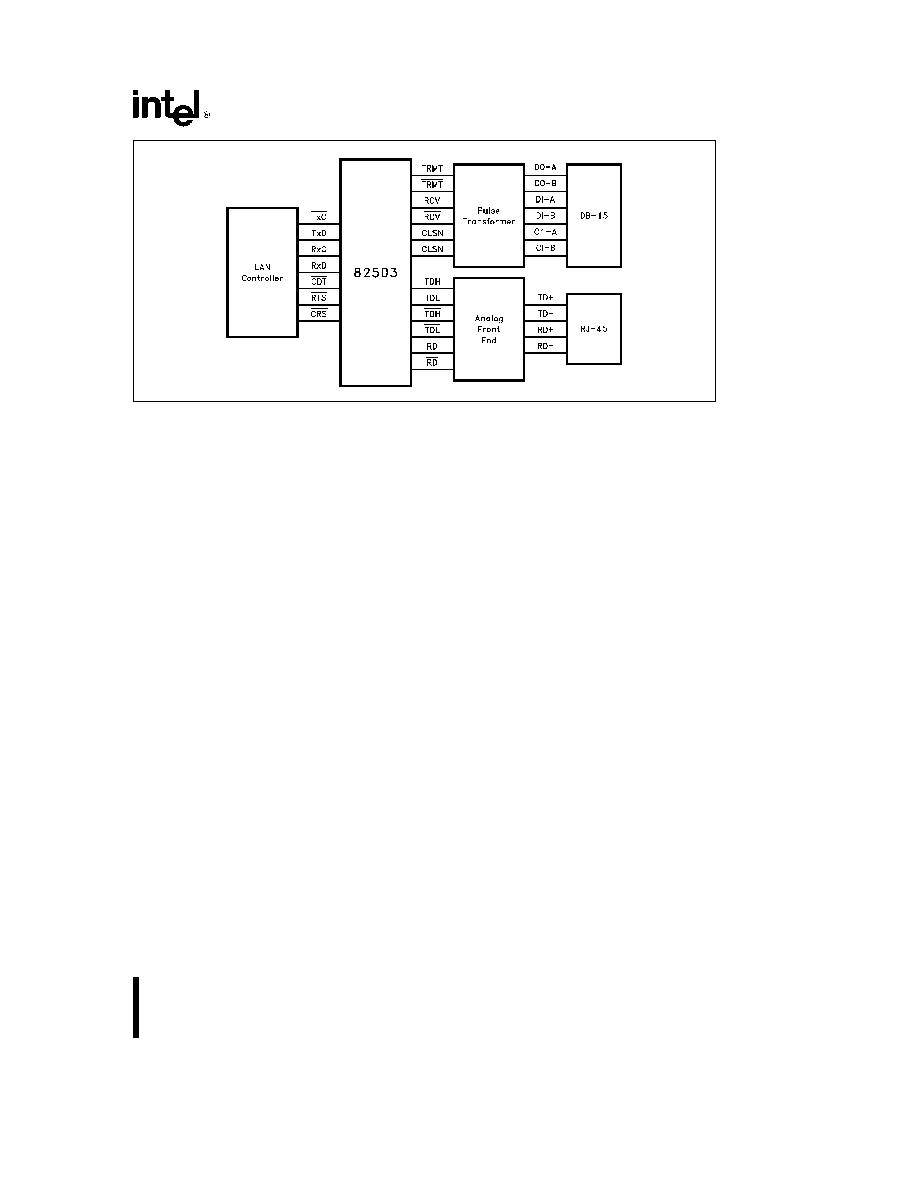

A block diagram of a typical application is shown in Figure 1 The 82503 Dual Serial Transceiver is a high-inte-

gration CMOS device designed to simplify interfacing industry standard Ethernet LAN Controllers to IEEE

802 3 local area network applications (10BASE5 10BASE2 and 10BASE-T) The component supports both

an attachment unit interface (AUI) and a Twisted Pair Ethernet interface (TPE) It allows OEMs to design a

state-of-the-art media interface that is jumperless and fully automatic The 82503 includes on-chip AUI and

TPE drivers and receivers it offers designers a cost-effective integrated solution for interfacing LAN control-

lers to the wire medium

CHMOS is a patented process of Intel Corporation

Ethernet is a registered trademark of Xerox Corporation

LANCE is a registered trademark of Advanced Micro Devices

Etherstar is a registered trademark of Fujitsu Electronics

Sonic is a registered trademark of National Semiconductor Corporation

82503 Dual Serial Transceiver (DST)

CONTENTS

PAGE

1 0 82503 PRODUCT FEATURES

3

2 0 PIN DEFINITION

5

2 1 Power Pins

6

2 2 Clock Pins

6

2 3 AUI Pins

6

2 4 TPE Pins

7

2 5 Controller Interface Pins

7

2 6 Mode Pins

8

2 7 LED Pins

9

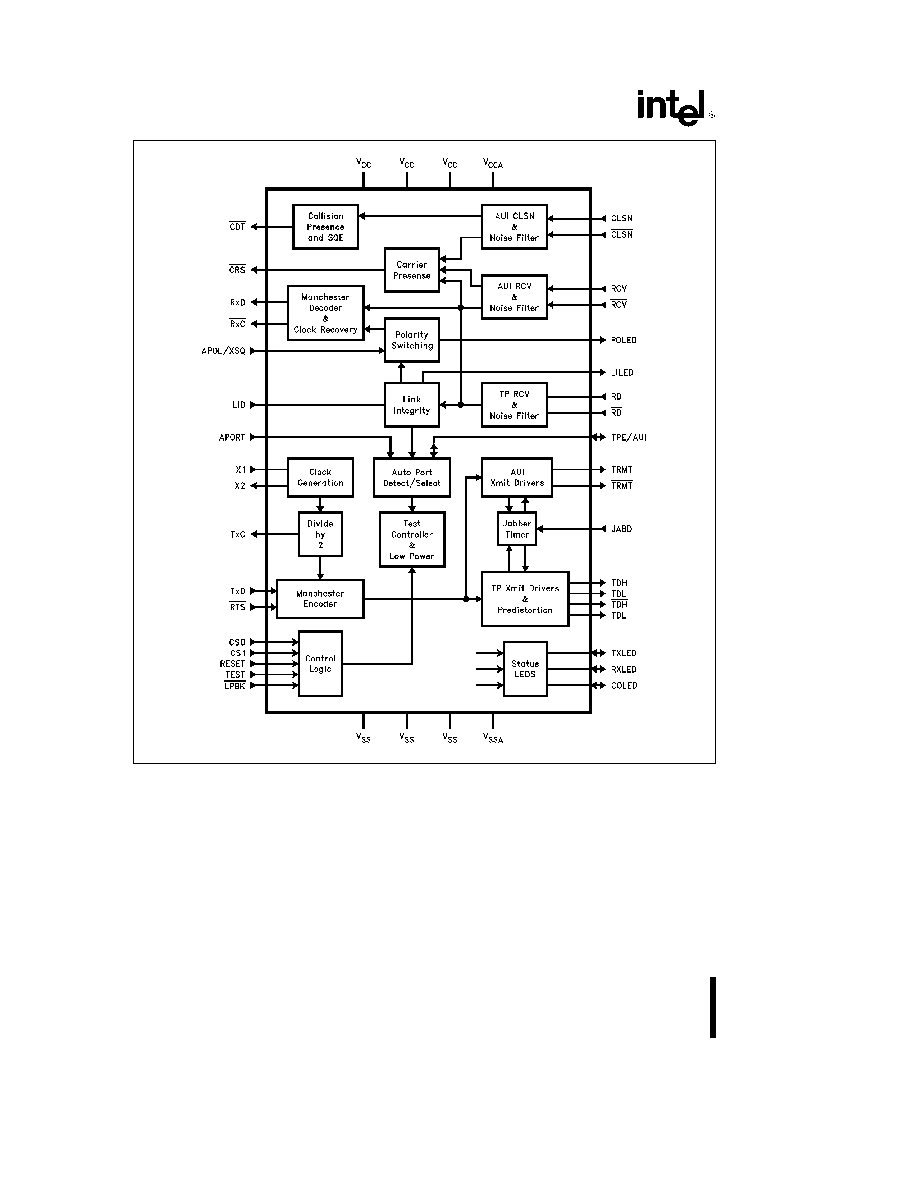

3 0 82503 ARCHITECTURE

10

3 1 Clock Generation

10

3 2 Transmit Blocks

10

3 3 Receive Blocks

11

3 4 Collision Detection

13

3 5 Link Integrity

13

3 6 Jabber Function

13

3 7 TPE Loopback

13

3 8 SQE Test Function

14

3 9 Port Selection

14

3 10 LED Description

14

3 11 Polarity Switching

14

3 12 Controller Interface

15

CONTENTS

PAGE

4 0 RESET LOW POWER AND TEST

MODES

16

4 1 Reset

16

4 2 Low Power and High Impedance

Modes

16

4 3 Diagnostic Loopback

16

4 4 Customer Test Modes (Continuous

AUI TPE Transmit)

16

5 0 APPLICATION EXAMPLE

17

5 1 Introduction

17

5 2 Design Guidelines

17

5 3 Layout Guidelines

17

6 0 PACKAGE THERMAL

SPECIFICATIONS

19

7 0 ELECTRICAL SPECIFICATIONS

AND TIMINGS

20

2

82503

290421 ≠ 1

Figure 1 Application Block Diagram

1 0

82503 PRODUCT FEATURES

The 82503 incorporates all the active circuitry re-

quired to interface Ethernet controllers to 10BASE-T

networks or the attachment unit interface (AUI) It

supports a direct no-glue interface to Intel's family of

high-performance LAN controllers (82586 82590

82593 and 82596) The 82503 also provides a di-

rect no-glue interface to the National Semiconductor

8390 and 83932 (SONIC)

the Western Digital

83C690

the

Advanced

Micro

Devices

7990

(LANCE) and 79C900 (ILACC)

and the Fujitsu

86950 (Etherstar) controllers

This component includes three advanced features

jumperless two-port design capability automatic port

selection and polarity switching The jumperless

TPE or AUI port selection capability allows design-

ers maximum ease-of-use and network flexibility Au-

tomatic port selection ensures complete software

compatibility with existing 10BASE2 and 10BASE5

software drivers The 82503's polarity switching fea-

ture will detect and correct polarity errors on the

twisted pair

the most common wiring fault in twist-

ed pair networks

The 82503 contains all the circuitry needed to meet

the 10BASE-T specification including link integrity a

jabber timer and internal predistortion Deselecting

link integrity allows the component to be used in

some prestandard networks The 82503's jabber

timer prevents the station from continuously trans-

mitting and is defeatable for simple design charac-

terization The predistortion circuitry eliminates line

overcharge and reduces jitter on 10BASE-T links

The 82503 can also support twisted pair cable

lengths of up to 200m when placed in TPE Extended

Squelch Mode (XSQ)

This component incorporates six LED drivers to dis-

play transmit data receive data collision link integri-

ty polarity faults and port selections allowing for

complete network monitoring by the user The trans-

mit receive and collision LEDs indicate the rate of

activity by the frequency of flashing The 82503 also

has a low power mode During low power many of

the 82503's pins are in a high-impedance state to

facilitate board-level testing

The 82503's diagnostic loopback control enables it

to route a transmission signal from the LAN control-

ler through its Manchester encoder-decoder circuitry

and back to the LAN controller This provides effec-

tive network node fault detection and isolation capa-

bilities In addition the 82503 supports diagnostic

test modes that generate continuous tranmission of

data through the twisted pair port allowing design-

ers to measure the analog performance of their de-

sign

The 82503 is available in 44-lead PLCC and 44-lead

QFP packages and is fabricated with Intel's low-

power high-speed CHMOS IV technology using a

single 5-V supply

3