10-1

Features

∑ Throughput Rate . . . . . . . . . . . . . . . . . . . . . . . . 160MHz

∑ 8-Bit (HI20203) Resolution

∑ Differential Linearity Error . . . . . . . . . . . . . . . . 0.5 LSB

∑ Low Glitch Noise

∑ Analog Multiplying Function

∑ Low Power Consumption . . . . . . . . . . . . . . . . . .420mW

∑ Evaluation Board Available

∑ Direct Replacement for the Sony CX20201-3, CX20202-3

Applications

∑ Wireless Communications

∑ Signal Reconstruction

∑ Direct Digital Synthesis

∑ High Definition Video Systems

∑ Digital Measurement Systems

∑ Radar

Description

The HI20203 is an 8-bit, 160MHz ultra high speed D/A con-

verter. The converter is based on an R2R switched current

source architecture that includes an input data register with

a complement feature and is Emitter Coupled Logic (ECL)

compatible.

The HI20203 is an 8-bit accurate D/A with a linearity error of

0.5 LSB.

For 10-bit resolution, please refer to the HI20201 data sheet.

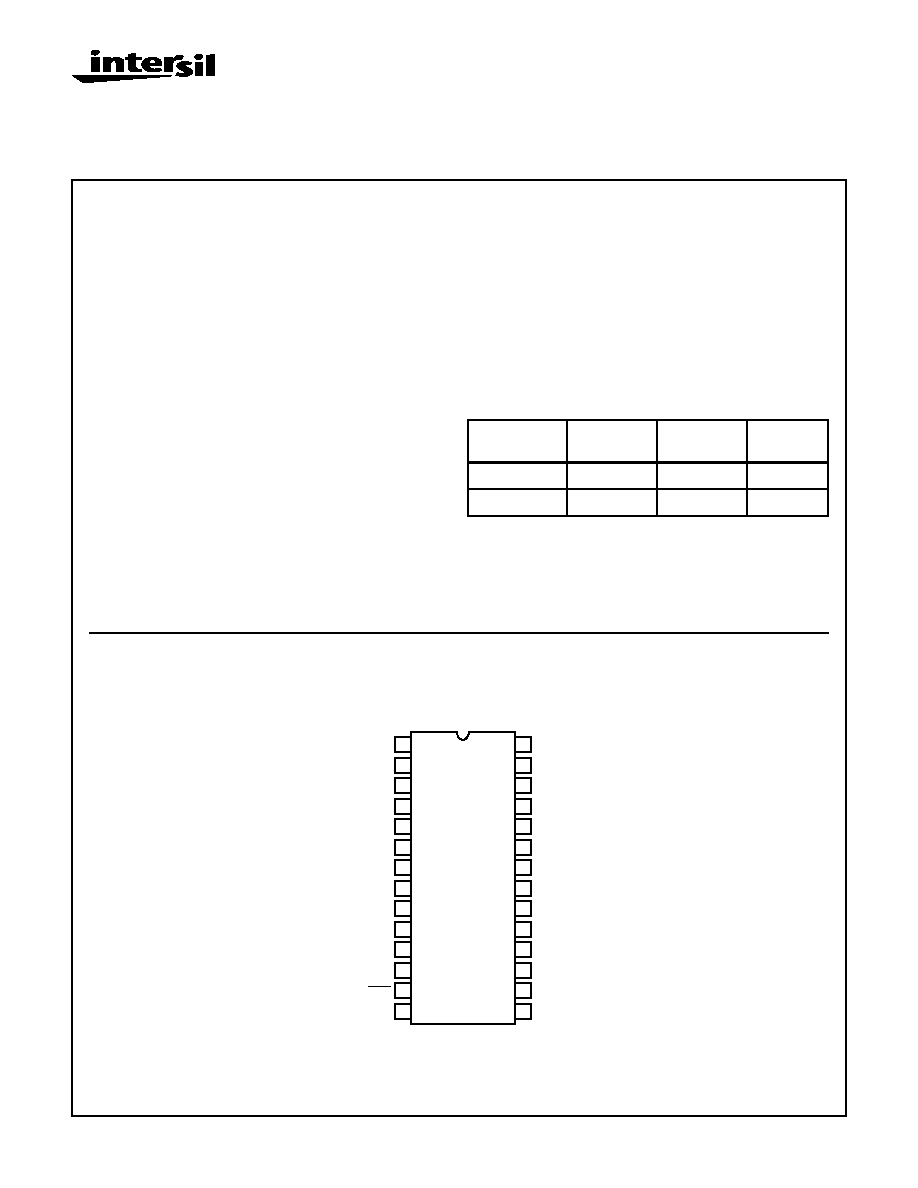

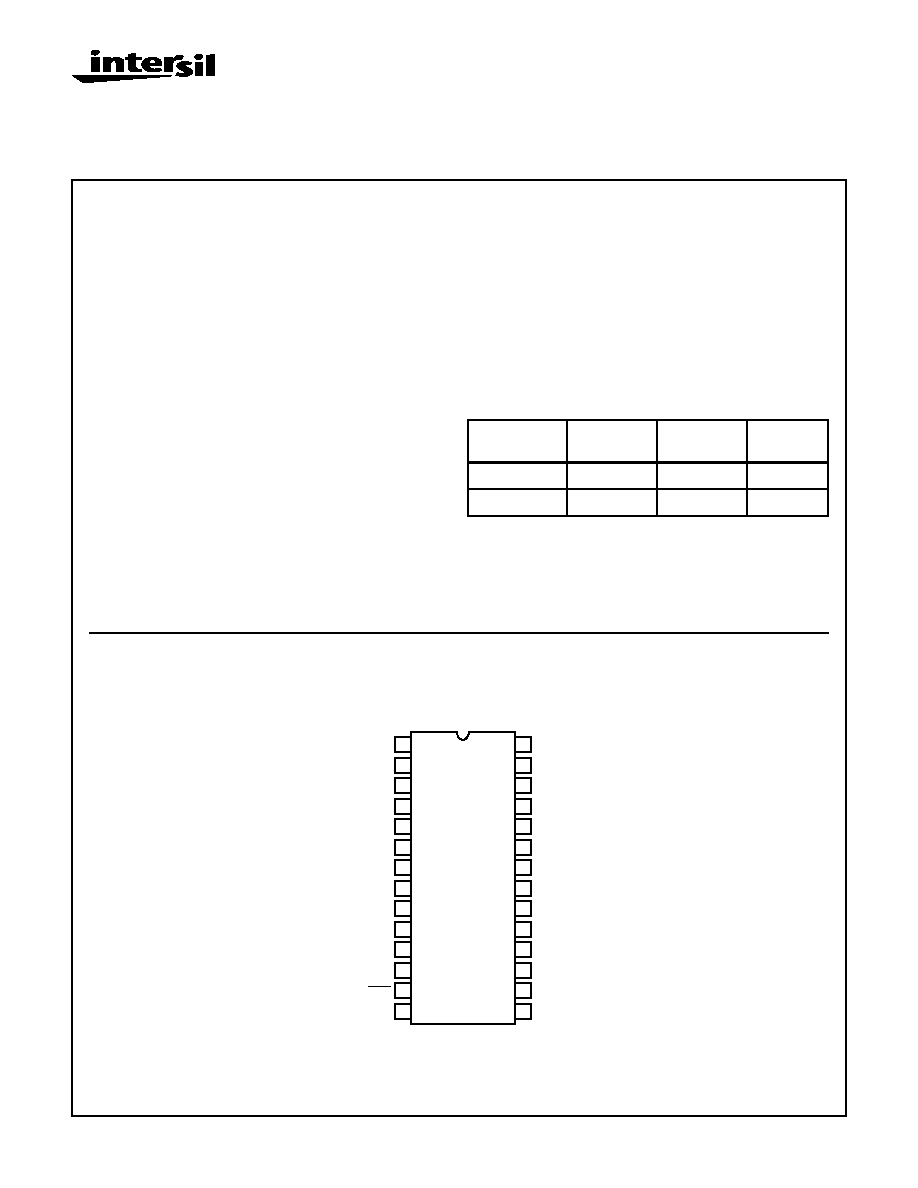

Pinout

HI20203

(PDIP, SOIC)

TOP VIEW

Ordering Information

PART

NUMBER

TEMP.

RANGE (

o

C)

PACKAGE

PKG. NO.

HI20203JCB

-20 to 75

28 Ld SOIC

M28.3A-S

HI20203JCP

-20 to 75

28 Ld PDIP

E28.6A-S

(MSB) D7

D6

D5

D4

D3

D2

D1

D0

NC

NC

NC

NC

CLK

CLK

AV

SS

AV

EE

NC

NC

NC

NC

NC

AV

SS

DV

SS

COMPL

DV

EE

V

REF

NC

I

OUT

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

August 1997

File Number

4096.1

HI20203

8-Bit, 160 MSPS,

Ultra High-Speed D/A Converter

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

|

Copyright

©

Intersil Corporation 1999

10-2

Typical Application Circuit

Functional Block Diagram

D7 (MSB) (1)

D4 (4)

D3 (5)

D2 (6)

D1 (7)

D0 (8)

D7

D4

D3

D2

D1

D0

CLK (14)

0.047

µ

F

(28) AV

SS

(18, 19, 21-25) NC

D/A OUT

(20) I

OUT

0.047

µ

F

3.6k

1.0

µ

F

(26) AV

EE

(27) V

REF

D6 (2)

D5

D5 (3)

D6

DIGITAL

DATA

(ECL)

CLK (13)

82

131

131

-5.2V

-1.3V

CLK

75

COAX CABLE

(15) DV

EE

(16) COMPL

1.0

µ

F

(17) DV

SS

1.5k

1k

TL431CP

.

-5.2V

-5.2V

2k

82

(11)

(12)

~

2.7V

(10)

(9)

HI20203

UPPER

8-BIT

REGISTER

CLOCK

BUFFER

4 LSBs

CURRENT

CELLS

BIAS CURRENT

GENERATOR

V

REF

I

OUT

(LSB) D0

D1

D2

D3

D4

D5

D6

COMPL

CLK

AV

EE

AV

SS

DV

EE

DV

SS

CLK

(MSB) D7

INPUT

BUFFER

4-BIT

ENCODER

15

SWITCHED

CURRENT

CELLS

R2R

NETWORK

15

HI20203

10-3

Absolute Maximum Ratings

T

A

= 25

o

C

Thermal Information

Digital Supply Voltage DV

EE

to DV

SS

. . . . . . . . . . . . . . . . . . . -7.0V

Analog Supply Voltage AV

DD

to AV

SS

. . . . . . . . . . . . . . . . . . -7.0V

Digital Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . +0.3 to DV

EE

V

Reference Input Voltage . . . . . . . . . . . . . . . . . . . . . . +0.3 to AV

EE

V

Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20mA

Thermal Resistance (Typical, Note 5)

JA

(

o

C/W)

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

67

PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

58

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150

o

C

Maximum Storage Temperature Range . . . . . . . . . .-65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300

o

C

(SOIC - Lead Tips Only)

Operating Conditions

Supply Voltage

AV

EE

, DV

EE

. . . . . . . . . . . . . . . . . . . . . . . . . . . . -4.75V to -5.45V

AV

EE

- DV

EE

. . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.05V to +0.05V

Digital Input Voltage

V

IH

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.0V to -0.7V

V

IL

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1.9V to -1.6V

Reference Input Voltage, V

REE

. . . . . . . . V

EE

+ 0.5V to V

EE

+ 1.4V

Load Resistance, R

L

. . . . . . . . . . . . . . . . . . . . . . . . . . . . Above 75

Output Voltage, V

O(FS)

. . . . . . . . . . . . . . . . . . . . . . . . . 0.8V to 1.2V

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . .-20

o

C to 75

o

C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1.

JA

is measured with the component mounted on an evaluation PC board in free air.

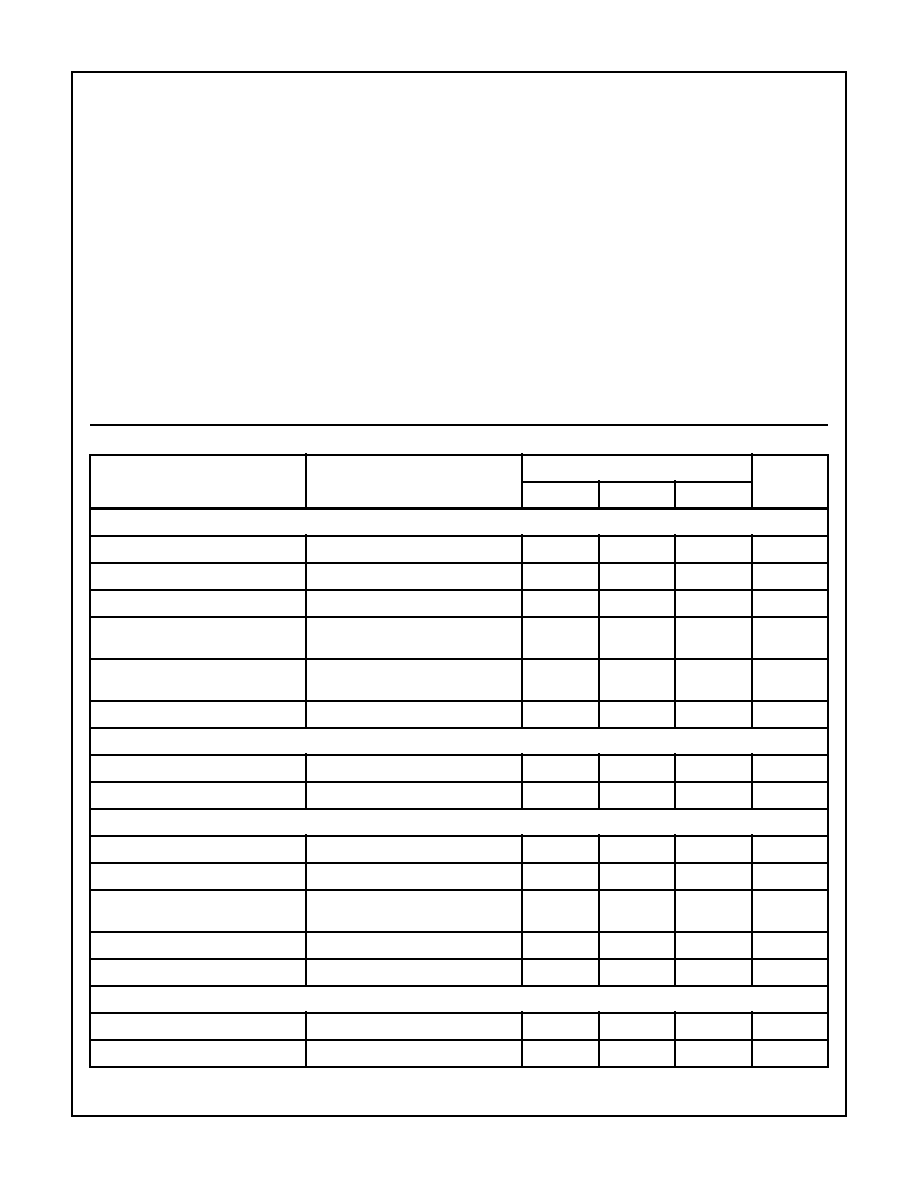

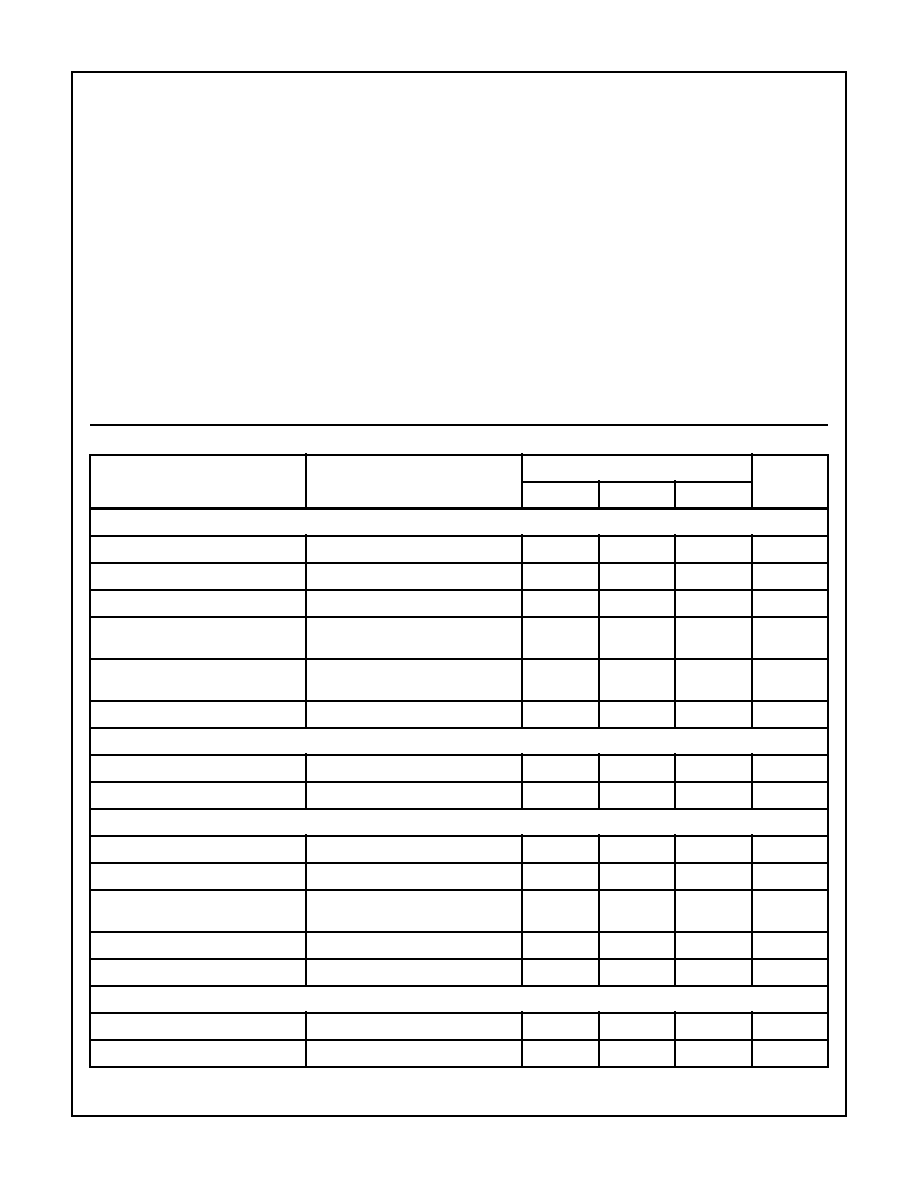

Electrical Specifications

AV

EE

= -5.2V, DV

EE

= -5.2V, AGND = 0V, DGND = 0V, R

L

=

, V

OUT

= -1V, T

A

= 25

o

C

PARAMETER

TEST CONDITION

HI20203JCB/JCP

UNITS

MIN

TYP

MAX

SYSTEM PERFORMANCE

Resolution

8

-

-

Bits

Integral Linearity Error, INL

f

S

= 160MHz (End Point)

-

-

±

0.5

LSB

Differential Linearity Error, DNL

f

S

= 160MHz

-

-

±

0.50

LSB

Offset Error, V

OS

(Adjustable to Zero)

(Note 3)

-

1.8

-

LSB

Full Scale Error, FSE

(Adjustable to Zero)

(Note 3)

-

-

±

26

LSB

Full Scale Output Current, I

FS

-

-

20

mA

DYNAMIC CHARACTERISTICS

Throughput Rate

See Figure 11

160

-

-

MHz

Glitch Energy, GE

R

OUT

= 75

-

15

-

pV/s

REFERENCE INPUT

Voltage Reference Input Range

With respect to AV

EE

+0.5

-

+1.4

V

Reference Input Current

V

REF

= -4.58V

-0.1

-0.4

-3.0

µ

A

Voltage Reference to Output Small

Signal Bandwidth

-3dB point 1V

P-P

Input

-

14.0

-

MHz

Output Rise Time, t

r

R

LOAD

= 75

-

1.5

-

ns

Output Fall Time, t

f

R

LOAD

= 75

-

1.5

-

ns

DIGITAL INPUTS

Input Logic High Voltage, V

IH

(Note 2)

-1.0

-0.89

V

Input Logic Low Voltage, V

IL

(Note 2)

-1.75

-1.6

V

HI20203

10-4

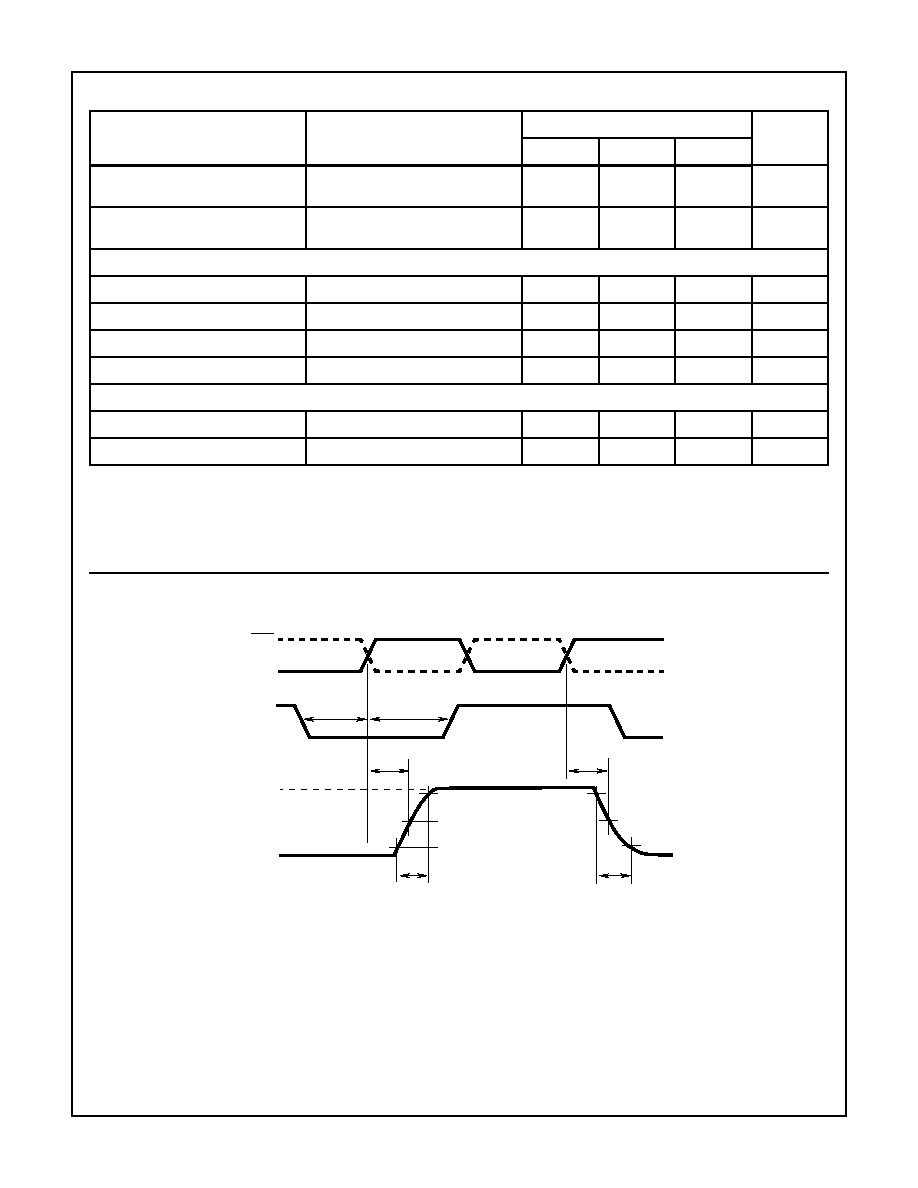

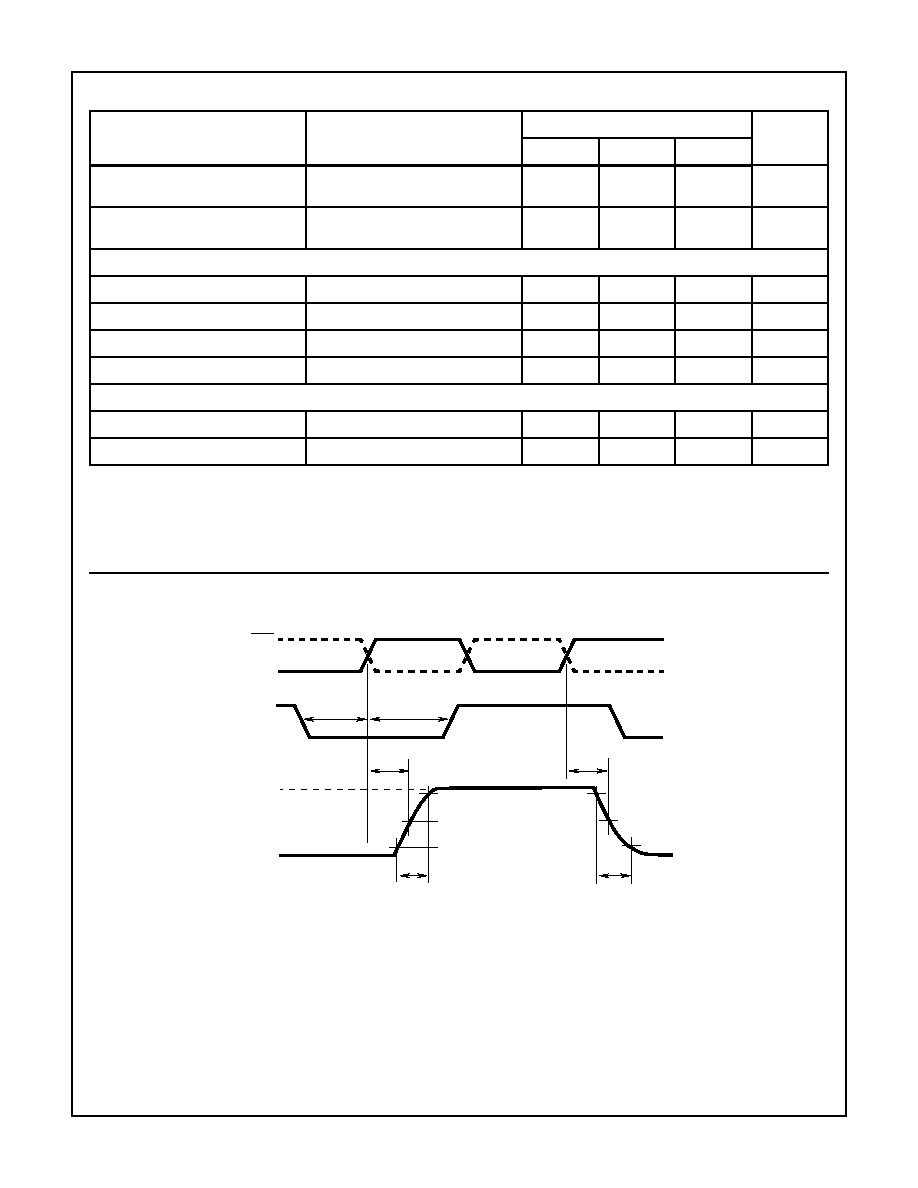

Timing Diagram

Input Logic Current, I

IL

, I

IH

(For D9 thru D6, COMPL)

V

IH

= -0.89V, V

IL

= -1.75V

(Note 2)

0.1

1.5

6.0

µ

A

Input Logic Current, I

IL

, I

IH

(For D5 thru D0)

V

IH

= -0.89V, V

IL

= -1.75V

(Note 2)

0.1

0.75

3.0

µ

A

TIMING CHARACTERISTICS

Data Setup Time, t

SU

See Figure 11

5

-

-

ns

Data Hold Time, t

HLD

See Figure 11

1

-

-

ns

Propagation Delay Time, t

PD

See Figure 11

-

3.8

-

ns

Settling Time, t

SET

(to

1

/

2

LSB)

See Figure 11

-

4.3

-

ns

POWER SUPPLY CHARACTERISITICS

I

EE

-60

-75

-90

mA

Power Dissipation

75

load

-

420

470

mW

NOTES:

2. Parameter guaranteed by design or characterization and not production tested.

3. Excludes error due to reference drift.

4. Electrical specifications guaranteed only under the stated operating conditions.

Electrical Specifications

AV

EE

= -5.2V, DV

EE

= -5.2V, AGND = 0V, DGND = 0V, R

L

=

, V

OUT

= -1V, T

A

= 25

o

C (Continued)

PARAMETER

TEST CONDITION

HI20203JCB/JCP

UNITS

MIN

TYP

MAX

CLK

CLK

DATA

0V

D/A OUT

-1V

90%

50%

10%

N + 1

N + 1

N

t

SU

t

HD

t

D

N

t

r

t

f

t

D

FIGURE 1. LADDER SETTLING TIME FULL POWER BANDWIDTH (LS)

HI20203

10-5

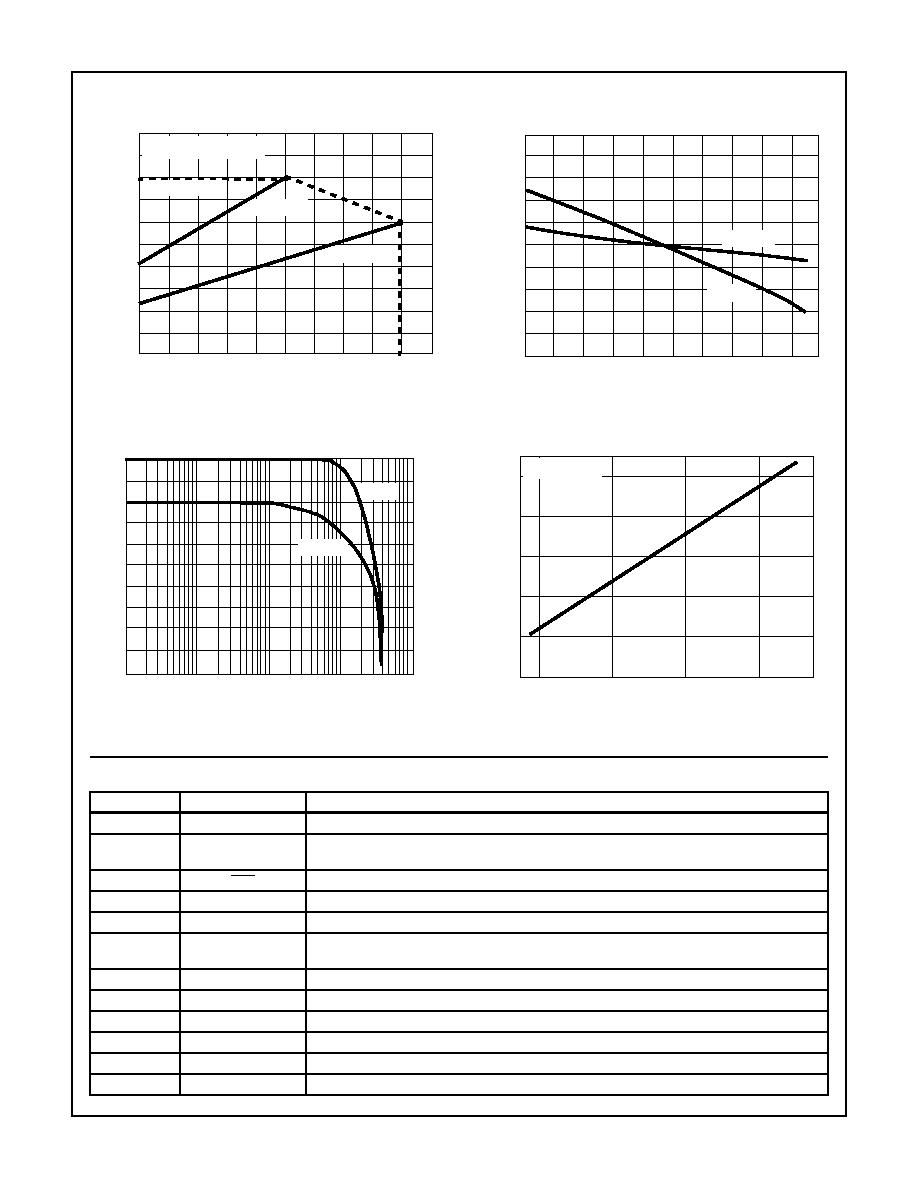

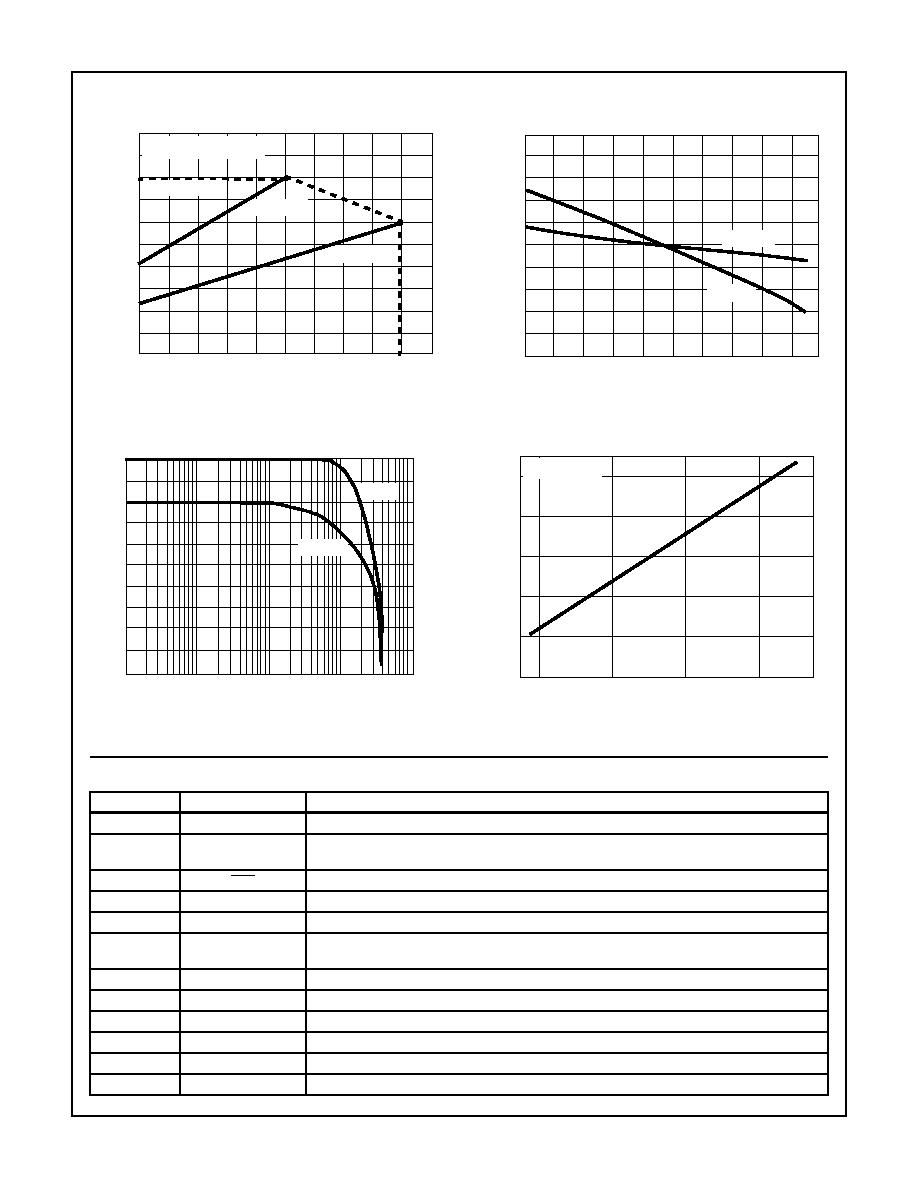

Typical Performance Curves

FIGURE 2. V

O(FS)

RATIO vs (V

REF

- V

EE

)

FIGURE 3. FULL SCALE OUTPUT VOLTAGE vs AMBIENT

TEMPERATURE

FIGURE 4. OUTPUT CHARACTERISTICS vs MULTIPLYING

INPUT SIGNAL FREQUENCY

FIGURE 5. GLITCH ENERGY vs CASE TEMPERATURE

(FULL SCALE - 1023mV)

V

REF

- V

EE

(V)

0.5

1.0

1.5

-2.0

-1.0

0

LINEAR AREA

R

L

= 10k

R

L

= 75

T

A

= 25

o

C, V

EE

= -5.2V

FULL SCALE OUTPUT V

O

L

T

A

GE (V)

80

60

40

20

0

-20

AMBIENT TEMPERATURE (

o

C)

1.05

1.00

0.95

R

L

= 75

R

L

= 10k

FULL SCALE OUTPUT V

O

L

T

A

GE (RELA

TIVE

V

ALUE) V

O(FS)

/(

V

O(FS)

AT

T

A

= 25

o

C)

100K

10K

1M

10M

100M

MULTIPLYING INPUT SIGNAL FREQUENCY (Hz)

GAIN (dB)

0

-10

-20

PHASE (DEGREE)

0

-90

-180

GAIN

PHASE

-50

0

50

100

10.0

8.0

6.0

4.0

2.0

CASE TEMPERATURE (

o

C)

GLITCH ENERGY (pV/s)

f

CLK

= 100MHz

Pin Descriptions

28 PIN SOIC

PIN NAME

PIN DESCRIPTION

1-8

D0 (LSB) - D7 (MSB)

Digital Data Bit 0, the Least Significant Bit thru Digital Data Bit 7, the Most Significant Bit.

11, 12, 19,

21-25

NC

No connect, not used.

13

CLK

Negative Differential Clock Input.

14

CLK

Positive Differential Clock Input

15

DV

EE

Digital (ECL) Power Supply -4.75V to -7V.

16

COMPL

Data Complement Pin. When set to a (ECL) logic High the input data is complemented in the input

buffer. When cleared to a (ECL) logic Low the input data is not complemented.

17

DV

SS

Digital Ground.

18

AV

SS

Analog Ground.

20

I

OUT

Current Output Pin.

26

AV

EE

Analog Supply -4.75V to -7V.

27

V

REF

Input Reference Voltage used to set the output full scale range.

28

AV

SS

Analog Ground

HI20203